Изобретение относится к вычислительной технике и может быть использовано для электрического и алгоритмического согласования микроЭВМ, имеющих магистральный параллельный интерфейс МПИ (Электроника-60, ДВК), с периферийными устройствами ввода- вывода, например, с дисплеем или с накопителем на гибких магнитных рисках (НГМД).

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности увеличения числа внешних устройств, подключаемых к первому интерфейсу.

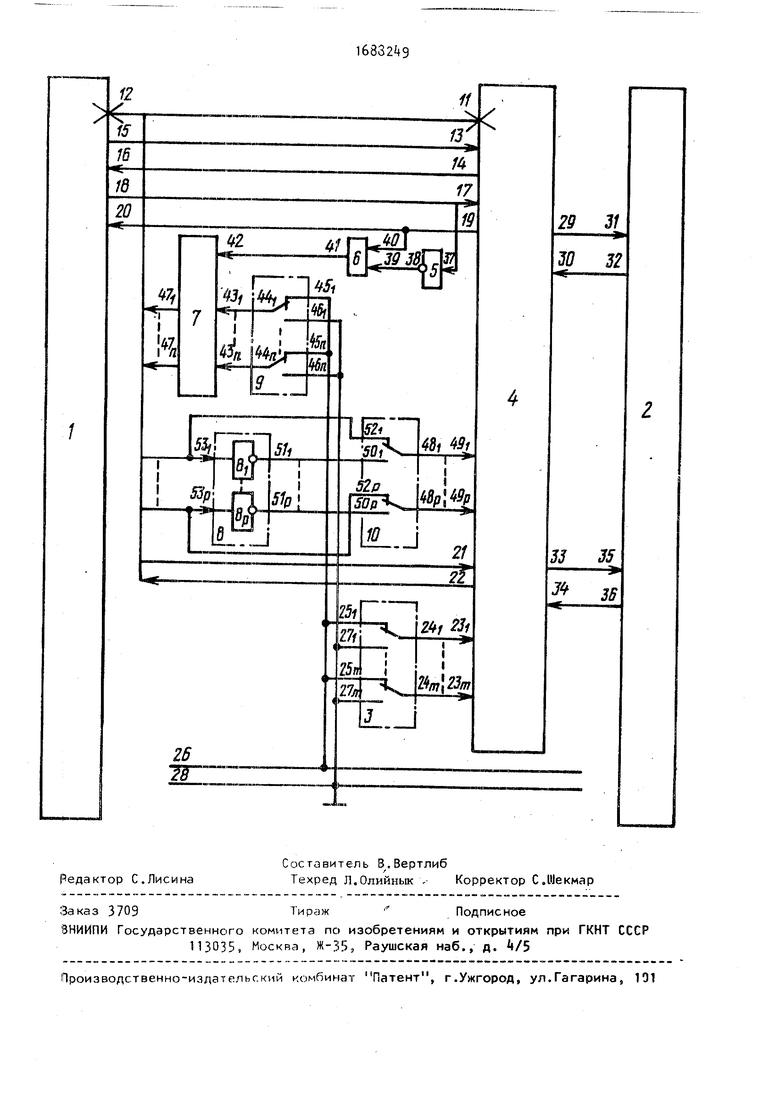

На чертеже представлена структурная схема устройства,

Устройство содержит блок 1 усиления первого интерфейса блок 2 усиления второго интерфейса, первый узел 3 переключателей, блок k обратимого преобразования параллельного кода в последовательный, элемент НЕ 5, элемент И 6, блок 7 канальных передатчиков, блок 8 элементов НЕ (инверторов), третий 9 и второй 10 узлы переключателей.

Группа информационных входов-выхо- дов 11 младших восьми разрядов адреса данных блока k подключена к группе информационных входов-выходов 12 шестнадцати разрядов адреса данных блока 1. Вход 13 и выход управления прерыванием блока k подключены к соот- |ветствующим выходам 15 и входам 16

О

00

оо

IsD

4.

Ј

управления прерыванием блока 1. Группа входов 17 синхронизации блока 4 подключена к соответствующим выходам группы выходов 18 блока 1. Выход 19 ответа блока 4 подключен к входу 20 сигнала ответа блока 1, Группы информационных входов 21 и выходов 22 записи и считывания блока 4 подключены к группе входов-выходов 12 блока 1„ Группа входов 23 режима блока 4 подключена к подвижным контактам 2 переключателей узпа ;. Неподвижные нормально замкнутые контакты 25 переключателей узла 3 подлкючены к шине Плюс источника питания 26 устройства. Неподвижные нормально разомкнутые контакты 27 переключателей узла 4 подключены к шине Общий провод 28 устройства. Информационные выход 25 и вход 30 вывода и последовательного кода блока 4 подключены к соответствующим входам и выходам группы входов 31 и выходом 3 данных вывода и ввода блока 2„ Синхронизирующие вы- ход 33 и вход внода и вывода блока 4 подключены к иходу 35 и выходу 36 блока 2. Вход 37 элемента НЕ 5 подключен к выходу синхроимпульса адреса группы выходок 18 синхронизации ввода-вывода блока 1. Выход 38 элемента НЕ 5 подключен к вт орому входу 39 элемента И 6, первый вход 4 О которого подключен к выходу 19 синхроимпульса ответа блок.з 4, Выход 41 зле- мента И 6 подключен к управляющему входу 42 блока 1 канальных передатчиков. К информационным входам 43 блока 7 подключены подвижные контакты 44 переключателей узла 9. Неподвижные нормально замкнутые контакты 45 переключателей узлэ Э подключены к шине 26 Плюс источника питания устройства, а неподвижны-; нормально разомкнутые контакты 46 переключателей узла 9 подключены к шине 28 Общий провод устройства.

Выходы 47 бпока 7 подключены к группе входов-выходов 12 шестнадцати разрядов адреса данных блока 1. Под- вижные контакты 48 переключателей узла 10 подключены к соответствующим входам группы адресных входоз 49 блока 4„ Неподвижные нормально разомкнутые контакты 50 переключателей УЗ ла 10 подключены к выходам 51 соответствующих инверторов блока 8, а неподвижные нормально замкнутые ион- такты 52 переключателей узла 10 соединены с входами 53 соответствующих инверторов блока 8 и подключены к соответствующим входам-выходам групп входов-выходов 12 шестнадцати разрядов адреса данных блока 1. В качестве блока 4 может быть использована БИС типа 1801ВП1-35.

Устройство при помощи блока 1 подключается к интерфейсу МПИ микроЭВМ (не показана). К блоку 2 подключаются периферийные устройства ввода-вывода (УВВ) (не показаны).

Устройство работает следующим обра зом.

I

Ввод данных от УВВ в микроЭВМ и вывод данных от микроЭВМ на УВВ осуществляется при помощи регистров данных (РД) и регистров состояния (PC) устройства, заключенных внутри блока 4, в циклах программного обмена интефейса МПИ: ВВОД, ВЫВОП, ВВОД-ПДУЗА- ВЫВОД. Эти регистры блока 4 имеют свои определенные адреса в адресном пространстве микроЭВМ. В адресной части указанных циклов микроЭВМ выставляет на шинах адреса данных интефейса МГ.И адрес того или иного регистра устройства, стробируя его фротом синхроимпульса адреса группы выходов 18 управления обменом, а затем производит считывание данных из адресованного регистра или запись данных в адресованный регистр, стробируя вводимые данные синхроимпульсом ввода, а выводимые данные - синхроимпульсов вывода группы сигналов управления обменом. Если адрес, выставленный микроЭВМ на шинах адреса данных интерфейса МПИ, в адресной части указанных циклов совпадает с адресом какого-либо регистра устройства, то, приняв1 этот адрес на группе входов 49 и нэ группе входов- выходов 11, стробированный фронтом синхроимпульса адреса,и приняв синхроимпульс ввода или вывода (синхроимпульсы адреса, ввода и вывода поступают на соответствующие входы группы входов 17 блока 4 от блока 1) блок 4 вырабатывает на выходе 19 синхроимпульс ответа, который через блок 1 поступает в интерфейс МПИ микроЭВМ, сопровождая вводимые или выводимые данные. Вводимые в микро- ЭВМ данные из адресованного регистра PC или РД с выходов 22, а также входов-выходов 11 поступают на группу

516

входов-выходов 12 блока 1, а с блока 1 - на интерфейс МПИ микроЭВМ.

Данные, считываемые из PC, интерпретируются как состояния периферийного УВВ, поступающие с группы выходов 36 блока 2 на группу входов 3 блока 4, а данные, считываемые из РД интерпретируются как информация, передаваемая периферийным УВВ и поступающая с группы выходов 32 блока на группу входов 30 блока 4. Выводимые из микроЭВМ данные с группы входов-выходов 12 блока 1 поступают на группу входов 21 и на группу входов- выходов 11 блока Ц, и производится запись данных в PC или РД.

Данные, записываемые в PC, интерпретируются как команды управления периферийным УВВ. Эти команды вызывают появления определенных сигналов управления на соответствующих выходах группы выходов 33 блока k, которые через блок 2 поступают на УВВ. Данные, записываемые в РД, интерпретируются как информация, передаваемая в периферийное УВВ. Эта информация с группы выходов 29 поступает на группу входов 31 блока 2, а оттуда - на УВВ.

Если ни один из переключателей узла 10 не включен, группа адресных входов 9 подключена непосредственно к соответствующим входам-выходам 12 блока 1 через подвижные контакты k& и неподвижные нормально замкнутые контакты 52 переключателей группы 10, а блок 8 не оказывает влияния на работу устройства. Задание адресов регистров PC и РД устройства осуществляется подачей на группу входов 23 блока 4 высоких и низких уровней напряжения с шин 26 и 28 через преключатели узла 3. Максимально возможное количество групп адресов регистров устройства в адресном пространстве микроЭВМ определяется формулой

N 2т,(1)

2

где m - количество входов 23 режима блока k, участвующих в переадресации регистров.

Практически возможное количество групп адресов регистров блока 4 мень ше, чем 2т , и как правило, не превы цвет трех-четырех групп. Это означает, что к интерфейсу МПИ микроЭВМ мо

0

жет оыть одновременно подключено не более трех-четырех таких устройств. Если включен хотя бы один переключатель узла 10, соответствующий вход, например 9 группы адресных входов блока Ц через подвижный контакт, .например 81( включенного перереклю- чателя узла 10, подключен к выходу

соответствующего инвертора блока 8, например 51 ( через контакт 50 . Таким образом, уровень сигнала соответствующего разряда как адреса, так и данных, поступающего на вход 9

5 блока 4, будет иметь инверсное, по сравнению с предыдущим примером, зна-1 чение, т.е. адреса группы регистров устройства в данном случае уже будут иными, они будут отличаться от адресов регистров предыдущего примера инверсным значением разряда адреса, поступающего на вход k3 блока k с группы входов-выходов 12 блока 1 через инвертор блока 8 и замкнутые кон5 такты 504, 8 узла 10. По окончании -адресной части циклов ВВОД, ВЫВОД или ВВОД-ПАУЗА-ВЫВОД происходит обмен данными с микроЭВМ. В этой части циклов разряд данных на входе 9-

0 блока k будет иметь также инверсное значение, однако это не искажает работу устройства, так как в этой части циклов информация на адресных входах J+9 блока k не анализируется и, следо5 вательно, не имеет значения. Максимально возможное количество групп адресов регистров устройства в адресном пространстве микроЭВМ с учетом введенных блока 8 и группы переклю0 чателей 10 будет определяться по формуле

N N 2

(2)

где N-максимально возможное количество групп адресов регистров устройства в адресном пространстве микроЭВМ; N - возмжное количество групп адресов циклов регистров устройства, задаваемое переключателями узла 3; р - количество адресных входов kS блока Ь, участвующих в переадресации.

Таким образом работает устройство в программном режиме.

S режиме прерываний в соответствующий бит регистров состояний

устройства записыеаз ся условие разрешения прерывания и далее центральный процессор (ЦП) ммкроЭВМ может заниматься другой задачей, не свя- за иной с обслуживание данного УВБ. По какому-либо состоянию УВВ (например, по готовности) на соответствующем выходе группы выходов 1 блока 4 активируется сигнал

требоЕзания прерывания, поступающий Через вход 16 блока 1 через интерфейс МПИ в ЦП. Последний, получив этот сигнал, завер-naer выполнение текущей крманды и выполняет цикл

ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ (BROfl АВП). ЦП посылает по соответствующим шинам интерфейса МПИ синхроимпульс авода и синхроимпульс предоставления прерывания, Синхроим- пульс ввода поступает с соответствующего выхода 18 блока 1 на вход 17 блока . Синхроимпульс предоставления прерывания поступает с выхода 15 блока 1 на вход 13 блока Ц. Если прерывания требовало не данное устройство, а другое, подключенное к интерфейсу МПИ и имеющее более низ- кий приоритет по сравнению с данные устройством, данное устройство рет- ранслирует синхроимпульс с предоставлением прерывания.

Ретранслируемый синхроимпульс предоставления прерывания с выхода И управления прерыванием блока t посту- haeT на вход 16 бгока 1 , а оттуда на интерфейс МПИ. Если прерывания требует данное устройство, синхроимпульс предоставления прерывание не ретранслируется данным устройством, На вы- сде И блока и далее на входе 16 блока 1 будет пассивный уровень напряжения. ПОЛУЧИВ СИНХРОИМПУЛЬСЫ ВЕЮ

да и предоставления прерывания,|блок выставляет на своих входах-выходах ; 11 восьмиразрядный адрес вектора прерывания (АВП), а на выходе 19 вырабатывает синхроимпульс ответа, поступающий на вход 20 блока 1 и сопровождающий вводимый в микроЭВМ АВП,

В отличие от циклов программного обмена в цикле ВВОД ЛВП синхроимпульс адреса не выоабатшзается, и н.э соответствующем входи 17 и на входе J элемента НЕ 5 будет IB течение всего этого цикла пассивный уровень напряжения. АВП„ введенный в микроЭВМ, указывает на ячейку па мят1/ микроЭВК, в которой указан калвлэный адрес подпрограммы обслуживания прерывания от данного устройства. Управление передается этой подпрограмме, в конце которой в соответствующий бит PC устройства вновь записывается условие разрешения прерывания, и осуществляется выход из прерывания. Возобновляется выполнение прерванной программы с того места, где она была прервана. ЦП может заниматься этой.программой до прихода очередного требования прерывания от устройства и т.д. Если ни один из переключателей узла 9 не включен, на информационных выходах блока 7 канальных передатииков е цикле ВВОД АВП будут пассивные уров- . ни напряжения и блок 7 не оказывает влияния на вводимый устройством АВП, Задание адресов векторов прерываний устройства осуществляется таким же образом, как и задание адресов регистров PC и РД, т.е. подачей на входы 23 блока 4 высоких и низких уровней напряжений с шин 26 и 28 через переключатели узла 3. Иными словами,, одновременно с заданием этими переключателями определенной группы адресов регистров °С и РД задается и определенная группа АВП устройства. Максимально возможное количество групп АВП в адресном пространстве микроЗВМ в этом случае определяется формулой (1), а практически возможное количество групп АВП БИС 4 не превышает трех-четырех групп, что делает невозможным одновременное подключение большего, чем три-четыре количества таких устройств, работающих в режиме прерываний, к интерфейсу МПИ микроЭВМ.

I

Если включен хотл бы один из переключателей узла Э, на соответствующий информационный вход блока 7 канальных передатчиков поступает активный низкий уровень напряжения. 8 этом случае устройство работает з цикле ВВОД АВП следующим образом. В момент появления на выходе 19 блока 4 синхроимпульса ответа на выходе k элемента И 6 активируется импульс разрешения, поступающий на управляющий вход k2 блока 7. Этот импульс будет активен до конца текущзго цикла ВВОД А8П, Информация с входов k3 поступает на ВЫХОДУ kl блока 7, т.е. на входы-выходы 12 блока 1. При этом АВП, формируемый Г на группе входов-выходов 12 блока 1, явпяется поразрядной дизъюнкцией сигналов группы входов-выходов 11 младших восьми разрядов адреса данных блока Ц и сигналов выходов kj блока 7, причем ABA может быть, как и раньше,с восьмиразрядным или, при необходимости, может иметь большую разрядность. Максимально возможное количество групп АВП устройства в адресном пространстве микроЭВМ определяется фор- JQ мулой ().

ч . п

N

N2

(3)

где N - максимально возможное количество групп АВП устройства в адресном пространстве мик- роЭВМ

N - возможное количество групп АВП устройства, задаваемое переключателями узла 3;

п - количество выходов 7...7П блока 7 канальных передатчиков.

Формула изобретения

Устройство для согласования интерфейсов, содержащее блоки усиления первого и второго интерфейсов, блок обратимого преобразования параллель- ного кода в последовательный, группы информационных входов-выходов, входов и выходов соединены соответственно с группами информационно-адресных вхо дов-выходов, выходов и входов блока усиления первого интерфейса, а информационные вход и выход и синхронизирующие вход и выход - соответ- . ственно с информационными выходом и входом и синхронизирующими выходом и входом блока усиления второго интерфейса, и три узла переключателей, причем группы выходов первого и вто

Q

5

0

5

о о

5

рого узлов переключателей подключены соответственно к группам входов режима и адреса блока обратимого преобразования параллельного кода в последовательный, вход разрешения прерывания, выход сигнала прерывания, tгруппа входов синхронизации и выход ответа которого подключены соответственно к выходу сигнала разрешения прерывания, входу сигнала прерывания, группе выходов сигналов синхронизации ввода-вывода и входу сигнала ответа блока усиления первого интерфейса, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности увеличения числа внешних устройств, подключаемых к первому интерфейсу, в устройство введены блок канальных передатчиков,блок элементов НЕ, элемент И и элемент НЕ, причем группа выходов блока канальных передатчиков и группа входов блока элементов НЕ соединены с группой информационных входов-выходов блока усиления первого интерфейса, группа выходов третьего узла переключателей подключена к группе входов блока канальных передатчиков, управляющим входом соединенного с выходом элемента И, первый и второй входы которого соединены соответственно с выходом ответа блока обратимого преобразования параллельного кода в последовательный и выходу элемента НЕ, входом подключенного к группе выходов синхронизации ввода-вывода блока усиления первого интерфейса, группа входов второго узла переключателей соединена с группой выходов блока элементов НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения внешних устройств с магистралью ЭВМ | 1987 |

|

SU1527639A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 1989 |

|

RU2022344C1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

Изобретение относится к вычислительной технике и может быть использовано для электрического и алгоритмического согласования микро- ЭВМ с периферийными устройствами ввода-вывода, в частности с дисплеем и накопителем на гибких магнитных дисках. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности увеличения числа устройств, одновременно подключаемых к интерфейсу микроЭВМ. Устройство содержит блоки усиления первого и второго интерфейсов, блок обратимого преобразования параллельного кода в последовательный, три узла переключателей, элемент И, элемент НЕ, блок канальных передатчиков, блок элементов НЕ. 1 ил. о « (Л

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Насос | 1917 |

|

SU13A1 |

| МикроОВМ | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Практическое пособие./Под ред.Л.Н.Преснухина, кн.2 | |||

| Персональные ЭВМ, М.: Высшая школа , J988 , рис .kk . | |||

Авторы

Даты

1991-10-30—Публикация

1988-08-15—Подача