Изобретение относится к электросвязи и предназначено для передачи первичного и вторичного потоков данных, в частности по оптическому волокну.

Известна оптическая система с биполярным сигналом, содержащая на передающей части преобразователь, два компаратора, три триггера, выделитель тактовой частоты, три элемента И-НЕ и оптический передатчик, на приемной части - фотодетектор, выделитель тактовой частоты, семь триггеров, шесть элементов И-НЕ, логическую схему, аналоговый усилитель.

Недостатком известной системы является невозможность передачи вторичного потока данных. В этой системе осуществлено двойное преобразование сигнала HDB-NPZ - СМ1, что снижает надежность системы.

Известна также система передачи по оптическому волокну первичного и вторичного потоков данных, содержащая на передающей части трансформатор, шесть триггеров, два устройства задержки, формирователь импульсов, четыре элемента И, два элемента ИЛИ, выделитель тактовой частоты. На приемной части система содержит решающее устройство (схема дискретизации), сдвиговый регистр, четыре элемента И, пять триггеров, два транзисторных ключа, трансформатор, формирователь импульсов (устройство ответвления) и выделитель тактовой частоты.

Недостатком известной системы является невозможность передачи вторичного потока данных в том случае, когда в первичном потоке данных присутствуют одни единичные посылки, а также низкая надежность передачи вторичного потока данных.

Цель изобретения - повышение достоверности передачи и приема вторичного потока данных путем замены кодовой комбинации 11 кода МСМ1 на кодовую комбинацию 10 и путем повышения стабильности формирования тактовой частоты.

Поставленная цель достигается тем, что в систему, содержащую на передающей стороне выделитель тактовой частоты, вход которого подключен к первому выводу первичной обмотки трансформатора, первый и второй выводы вторичной обмотки которого подключены к D-входам соответственно первого и второго триггеров, С-входы которых объединены, третий триггер, формирователь импульсов, элемент И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к инверсному выходу второго триггера, выход первого триггера соединен с первым входом элемента И, второй вывод первичной обмотки трансформатора и средний вывод вторичной обмотки трансформатора подключены к общей шине, причем первый вывод первичной обмотки трансформатора является входом первичного потока данных передающей стороны, входом вторичного потока данных которой является D-вход третьего триггера, а на приемной стороне - решающий блок, инверсный выход которого соединен с первым входом первого элемента И и входом четвертого элемента И, второй вход которого подключен к прямому выходу сдвигового регистра, второй вход которого соединен с выходом формирователя импульсов и с вторым входом решающего блока, первый вход которого соединен с входом выделителя тактовой частоты, прямой выход которого соединен с входом формирователя импульсов, с С-входом первого триггера, с С-входом второго триггера и с С-входом третьего триггера, выход которого соединен с S-входом четвертого триггера, выход которого соединен с D-входом пятого триггера, С-вход которого подключен к С-входу четвертого триггера, инверсный выход выделителя тактовой частоты соединен с вторыми входами третьего и второго элементов И, выходы которых соединены с входами соответственно первого и второго ключей, выходы которых подключены соответственно к первому и второму выводам первичной обмотки трансформатора, прямой выход решающего блока соединен с первым входом сдвигового регистра, инверсный выход которого подключен к второму входу первого элемента И, выход которого соединен с D-входом первого триггера, выход которого соединен с первым входом второго элемента И, выход второго триггера соединен с первым входом третьего элемента И, вход четвертого элемента И подключен к D-входу третьего триггера, средний вывод первичной обмотки трансформатора и второй вывод вторичной обмотки трансформатора подключены к общей шине, при этом первый вход решающего блока является входом приемной стороны, выходами первичного и вторичного потоков данных которой является соответственно первый вывод вторичной обмотки трансформатора и выход пятого триггера, введены на передающей стороне элемент ИЛИ-НЕ, четвертый, пятый, шестой и седьмой триггеры и счетчик-делитель, выход которого соединен с С-входом третьего триггера, выход которого соединен с С-входом пятого триггера, выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с D-входом шестого триггера, выход которого соединен с D-входом седьмого триггера, выход которого соединен с S-входом пятого триггера, с R-входом шестого триггера и с третьим входом элемента ИЛИ, выход которого соединен с D-входом четвертого триггера, С-вход которого подключен к С-входу шестого триггера, а С-входы седьмого, шестого и четвертого триггеров соединены с выходами формирователя импульсов, вход которого соединен с вторым входом элемента И, с выходом выделителя тактовой частоты, с входом счетчика-делителя и с С-входом первого триггера, D-вход которого подключен к второму входу элемента ИЛИ-НЕ, при этом выход четвертого триггера является выходом передающей стороны, а на приемной стороне введен счетчик-делитель, выход которого соединен с С-входом четвертого триггера, при этом прямой выход выделителя тактовой частоты соединен с входом счетчика-делителя, а D-вход второго триггера подключен к прямому выходу сдвигового регистра.

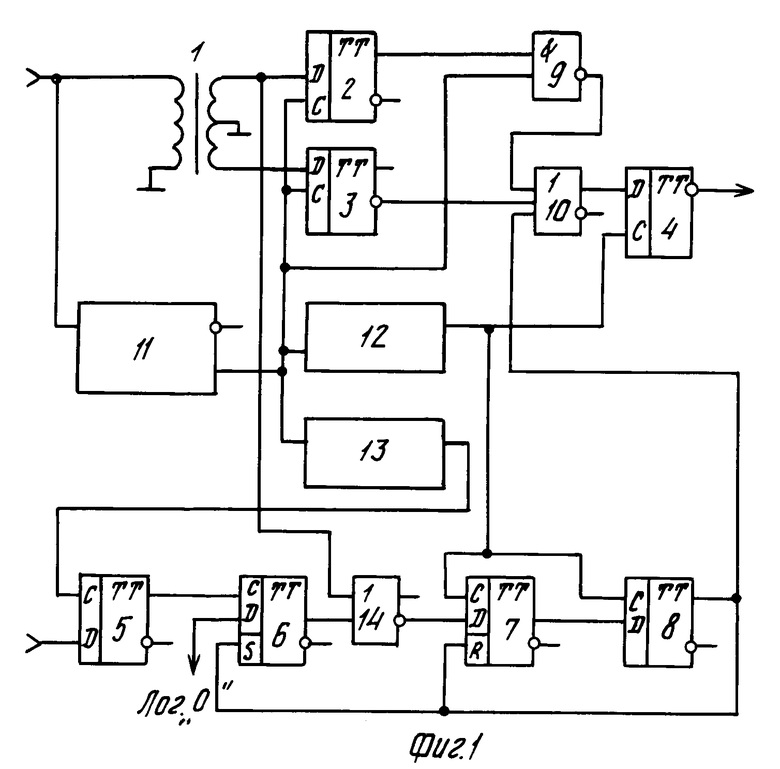

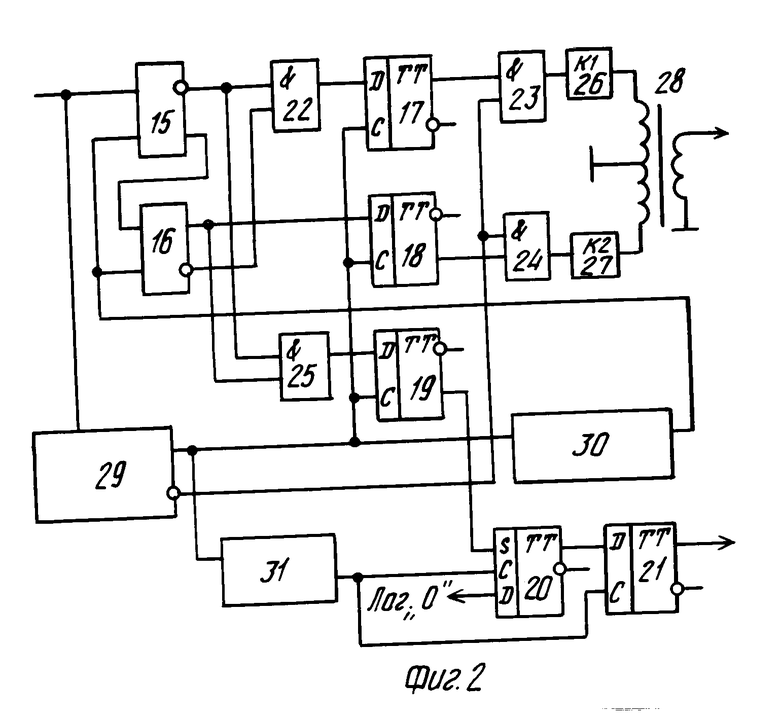

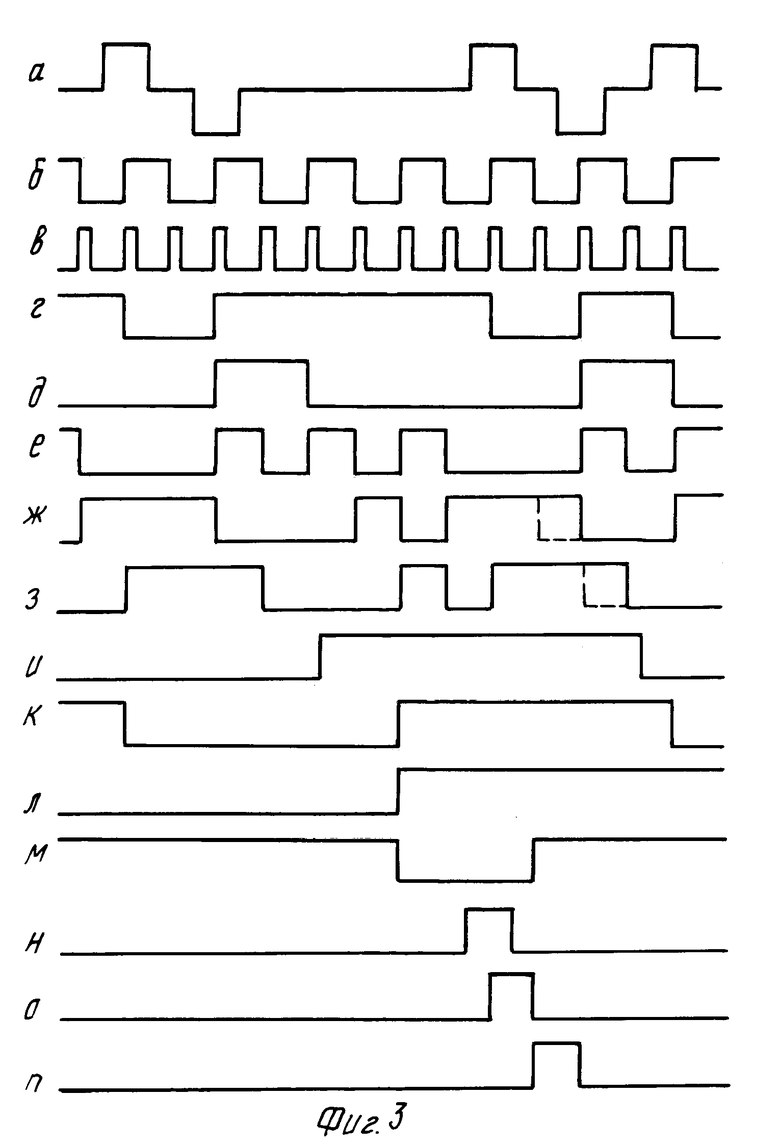

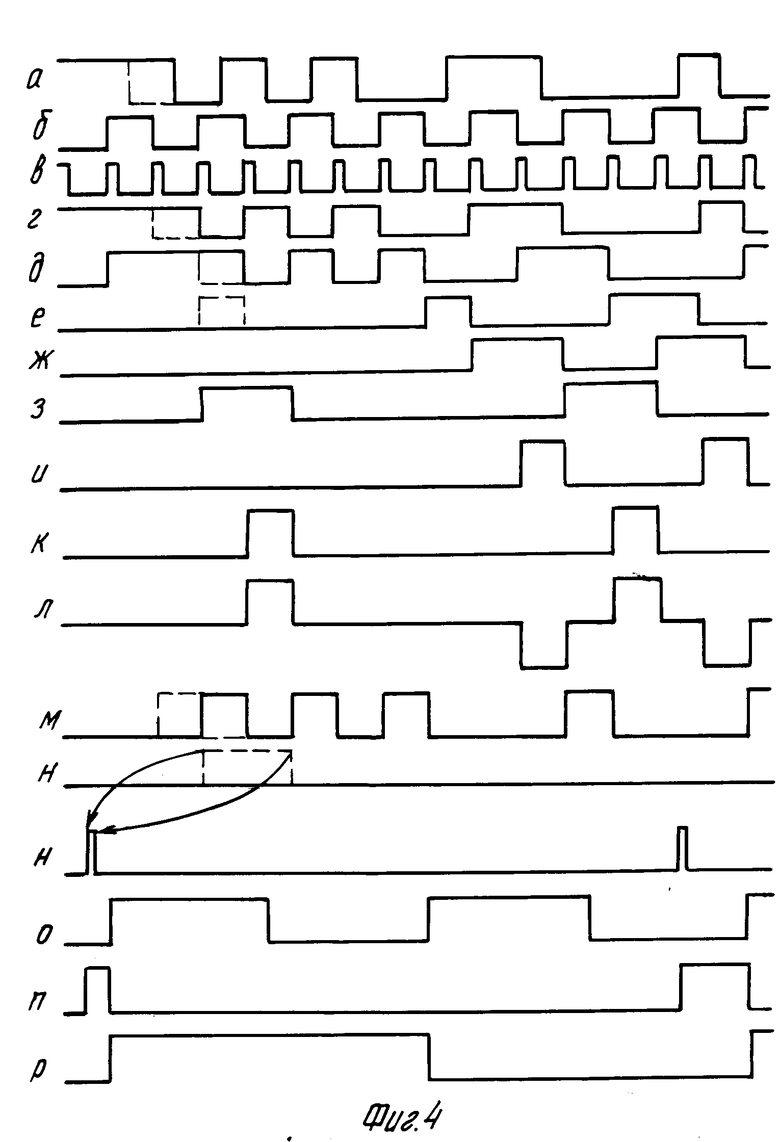

На фиг. 1 представлена структурная схема передающей стороны системы передачи и приема вторичного потока данных; на фиг. 2 - структурная схема приемной стороны системы; на фиг. 3 и 4 - временные диаграммы работы передающей и приемной сторон системы.

Система передачи и приема вторичного потока данных содержит на передающей стороне трансформатор 1, семь триггеров 2-8, элемент И 9, элемент ИЛИ 10, выделитель 11 тактовой частоты, формирователь 12 импульсов, счетчик-делитель 13, элемент ИЛИ-НЕ 14. На приемной стороне система содержит решающий блок 15, сдвиговый регистр 16, пять триггеров 17-21, четыре элемента И 22-25, два ключа 26, 27, трансформатор 28, выделитель 29 тактовой частоты, формирователь 30 импульсов и счетчик-делитель 31.

Система работает следующим образом. На передающей стороне системы информационный сигнал первичного потока данных в коде НDB-3 (см. фиг. 3,а) и скоростью передачи 34368 кбит/c поступает на первый вывод первичной обмотки трансформатора 1 и на выделитель 11 тактовой частоты, в котором из сигнала выделяется тактовая частота Fт = 34,368 МГц (см. фиг. 3,б). Сигнал, поступающий на D-входы триггеров 2 и 3 с первого и второго выводов вторичной обмотки трансформатора 1 стробируется тактовой частотой Fт. Сигнал с выхода триггера 2 (см. фиг. 3,г), поступает на элемент И 9, где складывается с тактовой частотой Fт. Сигнал с выхода триггера 3 (см. фиг. 3,д) поступает на элемент ИЛИ 10, где складывается с сигналами с выходов элемента И 9 (см. фиг. 3,е) и триггера 8 (см. фиг. 3,n), с выхода элемента ИЛИ 10 сигнал (см. фиг. 3, ж) поступает на D-вход триггера 4, где стробируется импульсам (см. фиг. 3,в) двойной тактовой частоты 2Fт = 68,736 МГц, полученными с помощью формирователя 12 импульсов из тактовой частоты Fт. Сигнал с выхода триггера 4 (см. фиг. 3,з) в коде МСМ1 поступает в канал связи. Информационный сигнал (см. фиг. 3,и) вторичного потока данных в формате RZ и скоростью передачи 64 кбит/с поступает на D-вход триггера 5 и стробируется импульсами (см. фиг. 3, к), следующими с частотой 64 кГц, которые получены путем деления тактовой частоты Fт на 537 с помощью счетчика-делителя 13. Сигнал с выхода триггера 5 (см. фиг. 3,л) своим передним фронтом устанавливает триггер 6 (см. фиг. 3,м) в состояние логического нуля и разрешает тем самым прохождение импульса с первого вывода вторичной обмотки трансформатора 1 через элемент ИЛИ-НЕ 14 (см. фиг. 3,н). Этот импульс записывается передним фронтом импульса сигнала двойной тактовой частоты 2Fт в триггер 7 (см. фиг. 3,о) и далее следующим импульсом двойной тактовой частоты 2 Fт - в триггер 8. Сигнал с триггера 8 поступает на элемент ИЛИ 10, а также устанавливает триггер 6 в состояние логической единицы, а триггер 7 - в состояние логического нуля.

На приемной стороне (см. фиг. 2) сигнал в коде МСМ1, поступивший из канала связи, решенный по амплитуде (см. фиг. 4,а) поступает на вход решающего блока 15 и выделителя 29 тактовой частоты, где происходит формирование тактовой последовательности с частотой Fт = 34,368 МГц (см. фиг. 7,б), из которой формируются импульсы двойной тактовой частоты 2Fт = 68,736 МГц (см. фиг. 7, в) с помощью формирователя 30 импульсов. В решающем блоке 15 входной сигнал решается по времени импульсами двойной тактовой частоты 2Fт (см. фиг. 4,г) и поступает на вход сдвигового регистра 16, на стробирующий вход которого поданы импульсы двойной тактовой частоты 2 Fт (см. фиг. 4,в), с выхода сдвигового регистра 16 сигнал (см. фиг. 4,д) поступает на вход триггера 18. Сигнал с инверсных выходов решающего блока 15 и сдвигового регистра 16 поступает на элемент И 22. С выхода элемента И 22 сигнал (см. фиг. 4,е) поступает на вход триггера 17. Сигналы, поступающие на входы триггеров 17 и 18, стробируются тактовой частотой Fт (см. фиг. 4, 3 и фиг. 4, ж) и поступают на элементы И 23 и 24, разрешая прохождение сигнала инверсной тактовой частоты Fт (см. фиг. 4,к и).

С выходов элементов И 23, 24 через транзисторные ключи 26, 27 сигнал поступает на первый и второй выводы первичной обмотки трансформатора 28, с вывода 1 вторичной обмотки которого снимается суммарный сигнал (см. фиг. 4, л) первичного потока данных в коде HDB-3. Сигналы с инверсного выхода решающего блока 15 и прямого выхода сдвигового регистра 16 поступают на элемент И 25, с выхода которого сигнал (см. фиг. 4,м) поступает на вход триггера 19 и стробируется тактовой частотой Fт. Триггер 20 сигналом (см. фиг. 4, н) с выхода триггера 19 устанавливается в состояние логической единицы (см. фиг. 4,о), а импульсами (см. фиг. 4,о) частотой 64 кГц с выхода счетчика-делителя 31 устанавливается в ноль, при этом этим же импульсом производится запись в триггер 21 сигнала, поданного на его вход. С выхода триггера 21 снимается сигнал (см. фиг. 4,р) вторичного потока данных в формате NRZ.

Положительный эффект от использования предлагаемой системы по сравнению с прототипом заключается в повышении достоверности передачи и приема вторичного потока данных, так как для передачи вторичного потока данных используется перекодировка единичных посылок типа 11 первичного потока данных в посылки типа 10.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля промежуточных станций системы связи | 1990 |

|

SU1714813A1 |

| СИСТЕМА ЦИФРОВОЙ ИЗБИРАТЕЛЬНОЙ СВЯЗИ | 1991 |

|

RU2022475C1 |

| Устройство для настройки регенератора | 1990 |

|

SU1800624A1 |

| УСТРОЙСТВО ДЛЯ ТЕЛЕКОНТРОЛЯ ПРОМЕЖУТОЧНЫХ СТАНЦИЙ СИСТЕМЫ СВЯЗИ | 1991 |

|

RU2024203C1 |

| Формирователь импульсов | 1990 |

|

SU1830618A1 |

| Устройство для измерения напряжения | 1990 |

|

SU1734027A1 |

| УСТРОЙСТВО ЭЛЕКТРОННОГО СМЕЩЕНИЯ ЧАСТОТЫ | 1989 |

|

SU1840230A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| ПРЕОБРАЗОВАТЕЛЬ СТЫКОВ ДЛЯ ПЕРЕДАЧИ ЦИФРОВЫХ СИГНАЛОВ (ВАРИАНТЫ) | 1994 |

|

RU2105413C1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

Использование: в электросвязи. Сущность изобретения: система содержит на передающей стороне трансформаторы, триггеры, элемент И, элемент ИЛИ, выделитель тактовой частоты, формирователь импульсов, счетчик-делитель, элемент ИЛИ-НЕ, на приемной стороне - решающий блок, сдвиговые регистры, триггеры, элемент И, ключи, трансформатор, выделитель тактовой частоты, формирователь импульсов и счетчик-делитель. Цель изобретения - повышение достоверности передачи и приема вторичного потока данных. 4 ил.

СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ПЕРВИЧНОГО И ВТОРИЧНОГО ПОТОКОВ ДАННЫХ, содержащая на передающей стороне выделитель тактовой частоты, вход которого подключен к первому выводу первичной обмотки трансформатора, первый и второй выводы вторичной обмотки которого подключены к D-входам соответственно первого и второго триггеров, C-входы которых объединены, третий триггер, формирователь импульсов, элемент И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к инверсному выходу второго триггера, выход первого триггера соединен с первым входом элемента И, второй вывод первичной обмотки трансформатора и средний вывод вторичной обмотки трансформатора подключены к общей шине, причем первый вывод первичной обмотки трансформатора является входом первичного потока данных передающей стороны, входом вторичного потока данных которой является D-вход третьего триггера, а на приемной стороне - решающий блок, инверсный выход которого соединен с первым входом первого элемента И и входом четвертого элемента И, второй вход которого подключен к прямому выходу сдвигового регистра, второй вход которого соединен с выходом формирователя импульсов и с вторым входом решающего блока, первый вход которого соединен с входом выделителя тактовой частоты, прямой выход которого соединен с входом формирователя импульсов, с C-входами первого, второго и третьего триггеров, выход последнего соединен с S-входом четвертого триггера, выход которого соединен с D-входом пятого триггера, C-вход которого подключен к C-входу четвертого триггера, инверсный выход выделителя тактовой частоты соединен с вторыми входами третьего и второго элементов И, выходы которых соединены с входами соответственно первого и второго ключей, выходы которых подключены соответственно к первому и второму выводам первичной обмотки трансформатора, прямой выход решающего блока соединен с первым входом сдвигового регистра, инверсный выход которого подключен к второму входу первого элемента И, выход которого соединен с D-входом первого триггера, выход которого соединен с первым входом второго элемента И, выход второго триггера соединен с первым входом третьего элемента И, вход четвертого элемента И подключен к D-входу третьего триггера, средний вывод первичной и второй вывод вторичной обмоток трансформатора подключены к общей шине, при этом первый вход решающего блока является входом приемной стороны, выходами первичного и вторичного потоков данных которой являются соответственно первый вывод вторичной обмотки трансформатора и выход пятого триггера, отличающаяся тем, что с целью повышения достоверности передачи и приема вторичного потока данных, на передающей стороне введены элемент ИЛИ-НЕ, четвертый - седьмой триггеры и счетчик-делитель, выход которого соединен с C-входом третьего триггера, выход которого соединен с C-входом пятого триггера, выход которого соединен с первым входом элемента ИЛИ - НЕ, выход которого соединен с D-входом шестого триггера, выход которого соединен с D-входом седьмого триггера, выход которого соединен с S-входом пятого триггера, с R-входом шестого триггера и с третьим входом элемента ИЛИ, выход которого соединен с D-входом четвертого триггера, C-вход которого подключен к C-входу шестого триггера, а C-входы седьмого, шестого и четвертого триггеров соединены с выходом формирователя импульсов, вход которого соединен с вторым входом элемента И, с выходом выделителя тактовой частоты, с входом счетчика-делителя и с C-входом первого триггера, D-вход которого подключен к второму входу элемента ИЛИ - НЕ, при этом выход четвертого триггера является выходом передающей стороны, а на приемной стороне введен счетчик-делитель, выход которого соединен с C-входом четвертого триггера, при этом прямой выход выделителя тактовой частоты соединен с входом счетчика-делителя, а D-вход второго триггера подключен к прямому выходу сдвигового регистра.

| СПОСОБ ВЫПОЛНЕНИЯ ЛАПАРОСКОПИЧЕСКОЙ ФУНДОПЛИКАЦИИ В ЗАВИСИМОСТИ ОТ КОНСТИТУЦИОНАЛЬНОГО ТИПА ПАЦИЕНТА | 2012 |

|

RU2529415C2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-10-30—Публикация

1990-06-12—Подача