Изобретение относится к автоматике, в частности к устройству для приема и передачи информации.

Известны устройства, содержащие первый регистр, информационный и синхронизирующий входы которого являются первым информационным и первым синхронизирующим входом устройства, дешифратор, вход которого соединен с первым выходом первого регистра, а выходы подключены к одним входам элементов И первой группы, другие входы которых соединены с выходом первого элемента задержки, а выходы подключены к входам считывания первого блока памяти, выход которого соединен с информационным входом второго регистра, синхронизирующий вход которого подключен к выходу второго элемента задержки, вход которого соединен с выходом первого элемента задержки, триггер, прямой и инверсный выходы которого подключены к одним входам первого и второго элементов И, первый элемент ИЛИ, выход которого соединен с выходом третьего элемента задержки, второй блок памяти, вторую, третью, четвертую и пятую группы элементов И, четвертый и пятый элементы задержки третий регистр, информационный и синхронизирующий входы которого являются вторым информационным и синхронизирующим входами устройства, а выходы подключены к одним входам элементов И второй, третьей и четвертой групп, второй элемент ИЛИ, входы которого соединены с выходами первого элемента И третьего элемента задержки, а выход подключен к входу считывания второго блока памяти, к входу четвертого элемента задержки и к одним входам элементов И пятой группы, другие входы которых соединены с выходом второго блока памяти, а выходы являются информационными выходами устройства, группу триггеров, единичные входы которых соединены с выходами соответствующих элементов И второй, третьей и четвертой групп, подключенных к входам первого элемента ИЛИ, первый счетчик, счетный вход которого соединен с выходом четвертого элемента задержки, подключенного к входу пятого элемента задержки, выход которого соединен с другими входами первого и второго элементов И, компаратор, информационные входы которого подключены к второму выходу первого регистра и к выходу первого счетчика, а выход соединен с единичным входом триггера, сумматор, информационные входы которого соединены с выходами второго регистра и счетчика, а выход подключен к адресному входу второго блока памяти, шестой элемент задержки, вход которого соединен с выходом второго элемента И, третий элемент ИЛИ, один вход которого подключен к выходу второго элемента задержки, а выход соединен с другими входами элементов И второй группы, седьмой элемент задержки, вход которого подключен к выходу второго элемента И третьей группы, а выход соединен с другим входом третьего элемента ИЛИ, и второй счетчик, установочный вход которого подключен к выходу шестого элемента задержки, счетный вход которого подключен к выходу второго элемента И третьей группы, а выход переноса является сигнальным выходом устройства, при этом установочные входы триггеров группы соединены с выходом второго элемента И, а прямые выходы подключены к соответствующим входам элементов И пятой группы, установочные входы первого и второго регистров, первого счетчика и триггера соединены с выходом шестого элемента задержки, другие входы элементов И третьей группы подключены к выходу второго элемента И второй группы, другие входы элементов И четвертой группы соединены с выходом второго элемента третьей группы, вход первого элемента задержки подключен к первому синхронизирующему входу устройства, а выход второго элемента И является управляющим выходом устройства.

Недостаток этого устройства состоит в его невысокой надежности, обусловленной тем, что конструктивное выполнение не позволяет сохранить задания на решение функциональных задач, если терминалы сети не готовы к их приему в течение заданного времени, определяемого счетчиком.

Цель изобретения состоит в повышении надежности устройства путем исключения потери заданий на решение функциональных задач.

Поставленная цель достигается тем, что в известное устройство введены третий блок памяти, информационные входы которого соединены с выходами первого регистра, первый элемент И, входы которого соединены с выходом первого элемента задержки и соответствующим выходом дешифратора, триггер, прямой вход которого подключен к выходу первого элемента И, а инверсный выход соединен с третьим входом элементов И второй группы, второй элемент И, один вход которого подключен к прямому выходу триггера, другой вход соединен с выходом второго элемента задержки, а выход подключен к входу считывания третьего блока памяти, четвертый элемент задержки, вход которого соединен с выходом второго счетчика, а выход подключен к входу записи третьего блока памяти, пятый элемент задержки, вход которого соединен с выходом второго элемента И, а выход подключен к инверсному входу триггера, третий счетчик, суммирующий вход которого соединен с выходом второго счетчика, вычитающий вход подключен к выходу пятого элемента задержки, а выход соединен с адресным входом третьего блока памяти, второй элемент ИЛИ, один вход которого является первым синхронизирующим входом устройства, другой соединен с выходом пятого элемента задержки, а выход подключен к синхронизирующему входу первого регистра, и группа элементов ИЛИ, одни входы которых соединены с выходами третьего блока памяти, другие - являются первым информационным входом устройства, а выходы подключены к информационному входу первого регистра.

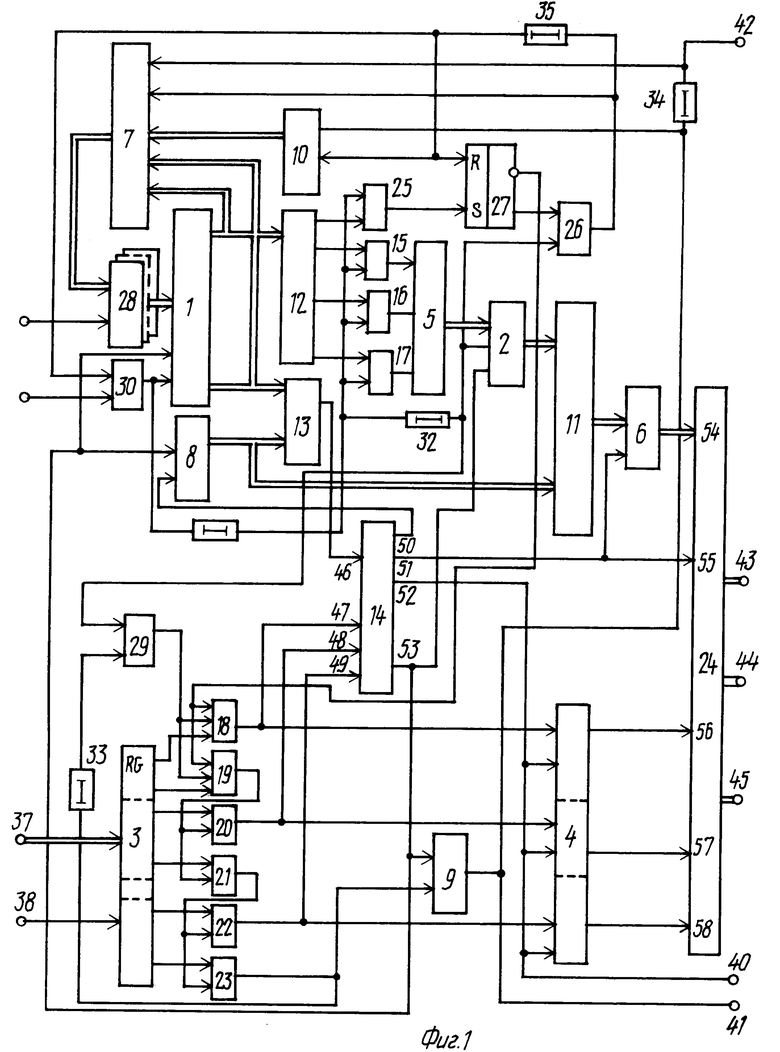

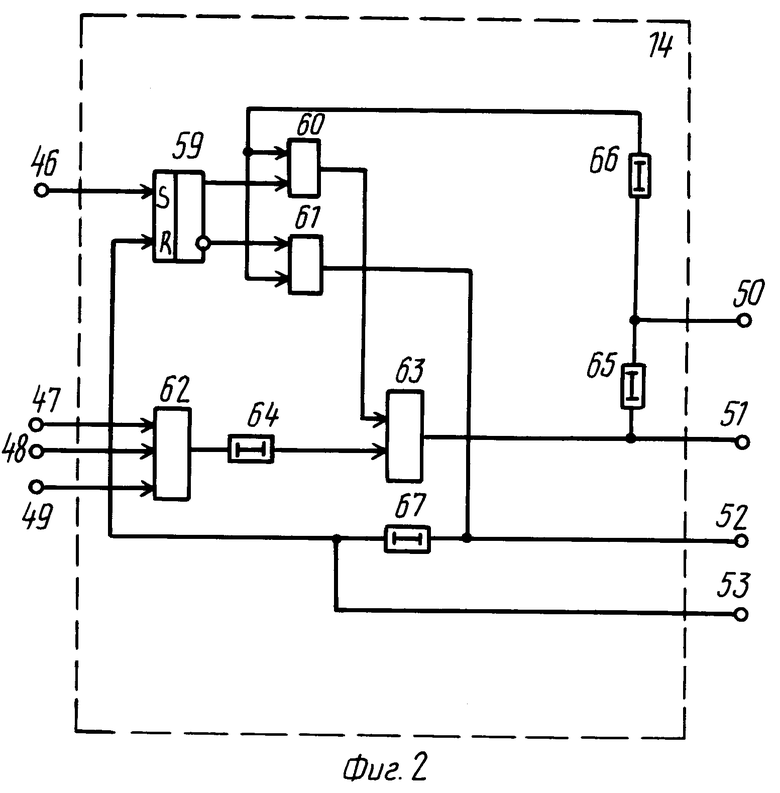

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - пример конструктивного выполнения блока управления; на фиг. 3 - пример выполнения мультиплексора.

Устройство (фиг. 1) содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, первый 5, второй 6 и третий 7 блоки памяти, первый 8, второй 9 и третий 10 счетчики, сумматор 11, дешифратор 12, компаратор 13, блок управления 14, первая 15-17, вторая 18-19, третья 20-21 и четвертая 22-23 группы элементов И, мультиплексор 24, первый 25 и второй 26 элементы И, триггер 27, группа 28 элементов ИЛИ, первый 29 и второй 30 элементы ИЛИ, первый 29 и второй 30 элементы ИЛИ, первый 31, второй 32, третий 33, четвертый 34, пятый 35 элементы задержки.

На фиг. 1 также показаны входы 36-39 и выходы 40-45 устройства, внутренние связи 46-58.

Блок управления (фиг. 2) содержит триггер 59, элементы 60, 61 И, элементы 62, 63 ИЛИ, элементы 64, 65, 66 и 67 элементы задержки.

Мультиплексор (фиг. 3) содержит группы элементов 68-70 И.

Блок управления 14 и мультиплексор 24 представлены на фиг. 1 для упрощения чертежа отдельными блоками, куда включены узлы и элементы прототипа, показанные на фиг. 2 и 3.

Устройство работает следующим образом.

Учитывая, что в сети работают несколько терминалов, входы которых подключены к выходам 43-45 соответственно, то их состояние, в котором они находятся (заняты, неисправны или готовы к приему запросов) поступает в соответствующие разряды реги- стра 3. При этом, если, например, первый терминал готов к приему задания на решение задачи, то элемент 18 И будет открыт, а элемент 19 И, подключенный к инверсному выходу того разряда будет закрыт.

Диспетчер сети формирует задание на решение задачи, который с входа 36 заносится через элементы 28 И в регистр 1 синхроимпульсом с входа 39. Запрос на решение задачи представляет собой кодограмму следующего вида: Код типа задачи расшифровывается дешифратором 12 и открывает один из элементов 15-17 И, на другие входы которых поступает синхроимпульс с входа 39, задержанный элементом задержки 31 на время переходных процессов в регистре 1 и дешифраторе 12.

Синхроимпульс проходит через открытый элемент группы элементов 15-17 и поступает на вход фиксированной ячейки памяти блока 5, где записан базовый адрес области памяти, в которой хранятся исходные данные для решения задачи.

Код базового адреса считывается из блока 5 на вход регистра 2, куда и заносится синхроимпульсом с выхода элемента задержки 32, задерживающего синхроимпульс на время считывания кода из блока 5 памяти.

С выхода регистра 2 код базового адреса поступает на вход комбинационного сумматора 11, на другой вход которого подается содержимое счетчика 8. Учитывая, что к началу работы устройства счетчик 8 сброшен в исходное состояние, то на выходе сумматора 11 и на адресном входе блока памяти 6 устанавливается код базового адреса первой ячейки блока 5 памяти, где хранятся первые исходные данные в следующем виде:

После установки базового адреса на входе блока памяти 6 импульс синхронизации с выхода элемента задержки 32, проходящий через элемент 29 ИЛИ, используется для организации выбора терминала, готового в данной ситуации принять на себя решение задачи с указанным номером.

С этой целью указанный синхроимпульс с выхода элемента 29 ИЛИ поступает на одни входы элементов 18, 19 И, другие входы которых подключены к прямому и инверсному выходам первого разряда регистра 3, фиксирующего готовность первого терминала к работе.

Если первый терминал готов к принятию задачи на решение, то элемент 18 И будет открыт, а элемент 19 И закрыт. Тогда импульс с выхода элемента 29 ИЛИ проходит через элемент 18 И на вход разряда регистра 4 и, во-первых, устанавливает триггер первого разряда регистра 4 с единичное состояние, который высоким потенциалом с выхода 56 открывает группу 68 элементов И мультиплексора 24, подключая тем самым выход блока памяти 6 к выходу 43 и далее к входу первого терминала.

Во-вторых, этот же синхроимпульс проходит на вход 47 блока 14 и далее через элемент 62 ИЛИ на вход элемента задержки 64, где задерживается на время подключения первого терминала к выходу блока памяти 6, и затем через элемент 63 ИЛИ поступает на вход считывания блока 6 памяти и на входы элементов 68 И мультиплексора 24, считывая и выдавая содержимое ячейки с базовым адресом на выход 43.

Кроме того, с выхода элемента 63 ИЛИ блока 14 тот же импульс поступает на вход элемента задержки 65, где задерживается на время считывания данных, и далее поступает как на счетный вход счетчика 8, устанавливая в нем единицу, так и на вход элемента задержки 66, где задерживается на время, равное сумме времени срабатывания счетчика 8, компаратора 13 и триггера 59, и далее поступает на входы элементов 60, 61 блока 14.

Процесс увеличения адреса считывания счетчиком 8 продолжается до тех пор, пока компаратор 13 не зафиксирует равенство кода числа исходных данных, хранящихся в регистре 1, с числом, зафиксированным в счетчике 8. Тогда импульсом с выхода компаратора 13 триггер 59 блока 14 устанавливается в единичное состояние, при котором элемент 60 И будет закрыт, а элемент 61 будет открыт.

Импульс с выхода элемента 66 задержки, задержанный на время срабатывания компаратора 13 и триггера 59, проходит через элемент 61 И на выход 52 блока 14 и далее на выход 40 в качестве сигнала окончания выдачи исходных данных и запуска задачи на решение.

Кроме того, этот же импульс возвращает триггер первого разряда регистра 4 в исходное состояние, отключая первый терминал от выхода блока 6, а также, после задержки элементом 67 на время сброса триггеров регистра 4 в исходное состояние, поступает на установочные входы триггера 59, регистров 1 и 2, счетчиков 8 и 9.

Если же в процессе проверки состояния терминалов сети первый из них будет не готов к работе, то элемент 18 И будет закрыт, а элемент 19 И - открыт. Тогда импульс с выхода элемента 19 И поступает на опрос состояния элементов 20, 21 И, фиксирующих готовность второго терминала.

При готовности второго терминала открыт будет элемент 20 И, и импульс с его выхода установит очередной триггер регистра 4 в единичное состояние, и поступит на вход элемента 62 ИЛИ блока 14, запуская устройство на процесс выдачи исходных данных описанным выше образом на вход второго терминала.

Если же и второй терминал не готов принять задание на решение задачи, то импульс с выхода элемента 19 И проходит через элемент 21 И на входы элементов 22, 23 И.

Может оказаться, что к данному моменту времени все терминалы сети оказались занятыми. Тогда импульс с выхода элемента 23 И поступает на счетный вход счетчика 9, фиксирующего тот факт, что задание на решение задачи не принято ни одним терминалом, и на вход элемента задержки 33, время задержки которого определяется принятым временем ожидания задания в очереди на обработку и с выхода которого этот импульс вновь поступает через элемент 29 ИЛИ на опрос состояния терминалов, фиксируемого элементами 18-23 И.

Счетчик 9 предназначен для проверки общего времени ожидания задания в очереди на обработку, превышающего установленное значение. Например, максимальное число циклов ожидания может быть равным 8. Тогда очередной девятый импульс, поступающий на счетный вход счетчика 9 будет появляться на выходе переполнения счетчика и на выходе 41 устройства, свидетельствуя о том, что в терминальной сети возникла неисправность, требующая вмешательства оператора.

Однако после того, как задание не удается разместить в течение заданного времени, оно будет потеряно, так как на вход 36 устройства поступит очередное задание от диспетчера.

Для исключения потери заданий в случаях, когда все терминалы заняты, импульс переноса с выхода счетчика 9 поступает на счетный вход счетчика 10, занося в него единицу, в результате чего на входе блока памяти 7 будет сформирован адрес 0001.

Кроме того, этот же импульс, задержанный элементом 34 на время срабатывания счетчика 10, поступает на вход записи блока 7 и заносит в ячейку с адресом, сформированным счетчиком 10, содержание задания, находящегося в регистре.

Этот же импульс с выхода 42 устройства сигнализирует о готовности устройства к приему нового задания с выхода 36.

Если же и очередное задание не будет передано какому-либо терминалу, то аналогичным образом в счетчике 10 будет сформирован очередной адрес ячейки, куда и будет записано следующее задание и т.д.

Такой процесс будет продолжаться до тех пор, пока очередное задание не будет передано на исполнение какому-либо из терминалов и после этого в поступлении новых заданий с выхода 36 не наступит пауза.

Это состояние устройства, при котором регистр 1 будет обнулен, зафиксирует дешифратор 12, который высоким потенциалом откроет элемент 25 И и синхроимпульс с выхода 39, задержанный элементом 31, проходит через него на вход триггера 27, устанавливая его в единичное состояние, при котором элемент 26 И будет открыт, а элемент 18 и 19 И - закрыт.

Тогда синхроимпульс, задержанный элементом 32 на время срабатывания триггера 27, проходит через элемент 26 И сразу на вход считывания блока 7, считывая содержание последнего задания из блока 7 по адресу, хранящемуся в счетчике 10.

Содержание ячейки памяти с соответствующим адресом с выхода блока 7 через элементы ИЛИ 28 поступает на информационные входы регистра 1 и заносится в него тем же синхроимпульсом, задержанным элементом 35 на время считывания данных из блока 7, который через элемент 30 ИЛИ поступает на синхровход регистра 1.

Одновременно этот же синхроимпульс поступает как на установочный вход триггера 27, сбрасывая его в исходное состояние, так и на вычитающий вход счетчика 10, устанавливая адрес очередной ячейки блока 7, подлежащей считыванию.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1991 |

|

RU2020554C1 |

| УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ ЛЕКСИЧЕСКИХ МНОЖЕСТВ | 1990 |

|

RU2022354C1 |

| Устройство для выделения контура изображения | 1990 |

|

SU1785017A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2020564C1 |

| СИСТЕМА ДИСТАНЦИОННОГО ОБУЧЕНИЯ СТУДЕНТОВ | 2006 |

|

RU2315364C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОПОЛНЕНИЯ МНОЖЕСТВА | 1990 |

|

RU2022353C1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| Устройство для селекции признаков изображений объектов | 1988 |

|

SU1547006A2 |

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

Изобретение относится к автоматике, в частности к устройству для приема и передачи информации. Цель изобретения состоит в повышении надежности устройства. Поставленная цель достигается путем исключения потери заданий на решение функциональных задач, что обеспечивается введением третьего блока памяти, первого и второго элементов И, триггера, четвертого и пятого элементов задержки, третьего счетчика, второго элемента ИЛИ и группы элементов ИЛИ. Кроме того, устройство содержит два регистра, дешифратор, пять групп элементов И, два блока памяти, три элемента задержки, два элемента ИЛИ. 3 ил.

УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ, содержащее первый регистр, информационный и синхронизирующий входы которого являются первыми информационным и синхронизирующим входами устройства, дешифратор, вход которого соединен с первым выходом первого регистра, а выходы подключены к первым входам элементов И первой группы, вторые входы которых соединены с выходом первого элемента задержки, а выходы подключены к входам считывания первого блока памяти, выход которого соединен с информационным входом второго регистра, синхронизирующий вход которого подключен к выходу второго элемента задержки, вход которого соединен с выходом первого элемента задержки, триггер, прямой и инверсный выходы которого подключены к первым входам первого и второго элементов И, первый элемент ИЛИ, выход которого соединен с входом третьего элемента задержки, второй блок памяти, вторую - пятую группы элементов И, четвертый и пятый элементы задержки, третий регистр, информационный и синхронизирующий входы которого являются вторым информационным и синхронизирующим входам устройства, а выходы подключены к первым входам элементов И второй - четвертой групп, второй элемент ИЛИ, входы которого соединены с выходами первого элемента И и третьего элемента задержки, а выход подключен к входу считывания второго блока памяти, к входу четвертого элемента задержки и к первым входам элементов И пятой группы, вторые входы которых соединены с выходом второго блока памяти, а выходы являются информационными выходами устройства, группу триггеров, единичные входы которых соединены с выходами соответствующих элементов И второй - четвертой групп, подключенных к входам первого элемента ИЛИ, первый счетчик, счетный вход которого соединен с выходом четвертого элемента задержки, выходом подключенного к входу пятого элемента задержки, выход которого соединен с вторыми входами первого и второго элементов И, компаратор, информационные входы которого подключены к второму выходу первого регистра и к выходу первого счетчика, а выход соединен с единичным входом триггера, сумматор, информационные входы которого соединены с выходами второго регистра и счетчика, а выход подключен к адресному входу второго блока памяти, шестой элемент задержки, вход которого соединен с выходом второго элемента И, третий элемент ИЛИ, первый вход которого подключен к выходу второго элемента задержки, а выход соединен с вторыми входами элементов И второй группы, седьмой элемент задержки, вход которого подключен к выходу второго элемента И четвертой группы, а выход соединен с вторым входом третьего элемента ИЛИ, и второй счетчик, установочный вход которого подключен к выходу шестого элемента задержки, счетный вход подключен к выходу второго элемента И четвертой группы, а выход переноса является сигнальным выходом устройства, при этом установочные входы триггеров группы соединены с выходом второго элемента И, а прямые выходы подключены к соответствующим входам элементов И пятой группы, установочные входы первого и второго регистров, первого счетчика и триггера соединены с выходом шестого элемента задержки, вторые входы элементов И третьей группы подключены к выходу второго элемента И второй группы, вторые входы элементов И четвертой группы соединены с выходом второго элемента И третьей группы, вход первого элемента задержки подключен к первому синхронизирующему входу устройства, а выход второго элемента И является управляющим выходом устройства, отличающееся тем, что, с целью повышения надежности, оно содержит третий блок памяти, информационные входы которого соединены с выходами первого регистра, первый элемент И, входы которого соединены с выходами первого элемента задержки и с соответствующим выходом дешифратора, триггер, прямой вход которого подключен к выходу первого элемента И, а инверсный выход соединен с третьими входами элементов И второй группы, второй элемент И, первый вход которого подключен к прямому выходу триггера, второй вход соединен с выходом второго элемента задержки, а выход подключен к входу считывания третьего блока памяти, четвертый элемент задержки, вход которого соединен с выходом второго счетчика, а выход подключен к входу записи третьего блока памяти, пятый элемент задержки, вход которого соединен с выходом второго элемента И, а выход подключен к инверсному входу триггера, третий счетчик, суммирующий вход которого соединен с выходом второго счетчика, вычитающий вход подключен к выходу пятого элемента задержки, а выход соединен с адресным входом третьего блока памяти, второй элемент ИЛИ, первый вход которого является первым синхронизирующим входом устройства, второй вход соединен с выходом пятого элемента задержки, а выход подключен к синхронизирующему входу первого регистра, и группу элементов ИЛИ, первые входы которых соединены с выходами третьего блока памяти, вторые входы являются первым информационным входом устройства, а выходы подключены к информационному входу первого регистра.

| Устройство для ввода информации | 1989 |

|

SU1612291A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-15—Публикация

1991-06-28—Подача