Устройство относится к вычислительной технике и может быть использовано для защиты ячеек памяти от несанкционированного обращения к ним.

Известно устройство для защиты памяти [1], содержащее первый блок регистров, первый блок триггеров, первый блок элементов И, первый элемент ИЛИ, триггер, регистр адреса и два дешифратора, причем входы первого дешифратора являются входами идентификатора устройства, а выходы соединены с первыми входами первого блока регистров, выходы данных первого блока регистров соединены с соответствующими входами установки триггеров первого блока триггеров, прямые выходы триггеров первого блока триггеров соединены с первыми входами первого блока элементов И, вторые входы которого соединены с прямым выходом триггера, третьи входы первого блока элементов И соединены с выходами второго дешифратора, выход элемента ИЛИ соединен с входом разрешения выдачи адреса регистра адреса и является управляющим выходом устройства.

Недостатками известного устройства являются узкие функциональные возможности и сложность конструкции.

Наиболее близким по технической сущности к заявляемому является устройство для защиты памяти [2], содержащее три дешифратора, первый и второй блоки регистров, пять элементов ИЛИ, регистр адреса, два блока триггеров, элемент задержки, триггер и два блока элементов И, причем входы первого дешифратора являются входами идентификатора устройства, входы второго дешифратора являются входами адреса устройства, входы третьего дешифратора являются входами операции устройства, входы идентификатора, адреса и операции устройства соединены соответственно с входами третьего элемента ИЛИ, информационными входами регистра адреса и входами второго элемента ИЛИ, выходы регистра адреса являются выходами адреса устройства, выход третьего элемента ИЛИ соединен с входами сброса первого и второго блоков триггеров, к информационным входам которых подключены соответственно выходы первого и второго блоков регистров, к входам которых подключены выходы первого дешифратора, выходы первого блока триггеров, второго дешифратора и триггера подключены к входам первого блока элементов И, выходы второго блока триггеров и третьего дешифратора подключены к входам второго блока элементов И, выходы первого и второго блоков элементов И подключены соответственно к входам первого и четвертого элементов ИЛИ, выход первого элемента ИЛИ соединен с первым входом регистра адреса и является управляющим выходом устройства, выходы четвертого и второго элементов ИЛИ соединены соответственно с единичным и нулевым входами триггера, выходы второго дешифратора соединены с входами пятого элемента ИЛИ, выход которого через элемент задержки подключен к второму входу регистра адреса.

Недостатками известного устройства, выбранного в качестве прототипа, являются узкие функциональные возможности и сложность конструкции. Узкие функциональные возможности прототипа обусловлены тем, что в нем защита памяти осуществляется отдельно по операциям с ней и отдельно для всех защищаемых ячеек памяти. Иначе говоря, в прототипе принимаются отдельно два решения: разрешена ли пользователю (с заданным идентификатором) запрашиваемая им операция с памятью в целом и разрешено ли данному пользователю обращение к запрашиваемой им ячейке памяти.

Таким образом, в прототипе, если пользователю запрещена некоторая операция, она запрещена (или соответственно разрешена) ему для всех ячеек памяти, подлежащих защите. Аналогично, если некоторая ячейка защищаемой памяти недоступна данному пользователю, она недоступна для всех его операций. Такая организация защиты памяти является недостаточно гибкой. Более унивеpсальной является защита памяти, когда для каждого пользователя (определяемого идентификатором) для каждой ячейки памяти задан набор разрешенных операций, причем индивидуально для каждой ячейки защищаемой памяти. Эту задачу и реализует заявляемое устройство.

Целью изобретения является расширение функциональных возможностей за счет возможности задания набора разрешенных операций и упрощение устройства.

Цель достигается тем, что в устройство для защиты памяти, содержащее четыре элемента ИЛИ, два регистра, группу элементов И, элемент задержки, регистр адреса и дешифратор, причем входы идентификатора устройства соединены с входами первого элемента ИЛИ, входы операции устройства соединены с входами второго элемента ИЛИ, входы адреса устройства соединены с входами четвертого элемента ИЛИ и с информационными входами регистра адреса, выходы которого являются адресными выходами устройства, входы третьего элемента ИЛИ соединены с выходами элементов И группы, первые входы которых подключены к выходам дешифратора, выход элемента задержки соединен с входом сброса регистра адреса, введены блок памяти, формирователь импульсов и элемент И, причем выход первого элемента ИЛИ соединен с синхровходом первого регистра, к информационным входам которого подключены входы идентификатора устройства, выход второго элемента ИЛИ соединен с синхровходом второго регистра, к информационным входам которого подключены входы операции устройства, выходы первого регистра и входы адреса устройства соединены с адресными входами блока памяти, выходы которого подключены к вторым входам элементов И группы, выходы второго регистра соединены с входами дешифратора, выходы третьего элемента ИЛИ и формирователи импульсов соединены с входами элемента И, выход которого подключен к синхровходу регистра адреса и является управляющим выходом устройства, выход четвертого элемента ИЛИ соединен с входом формирователя импульсов, выход которого подключен также к входу элемента задержки.

Таким образом, заявляемое устройство соответствует критерию изобретения "новизна".

Изучение аналогичных устройств в смежных областях техники не выявило устройств, обладающих общими отличительными признаками прототипа и заявляемого устройства, что позволяет сделать вывод о соответствии заявляемого устройства критерию изобретения "Существенные отличия".

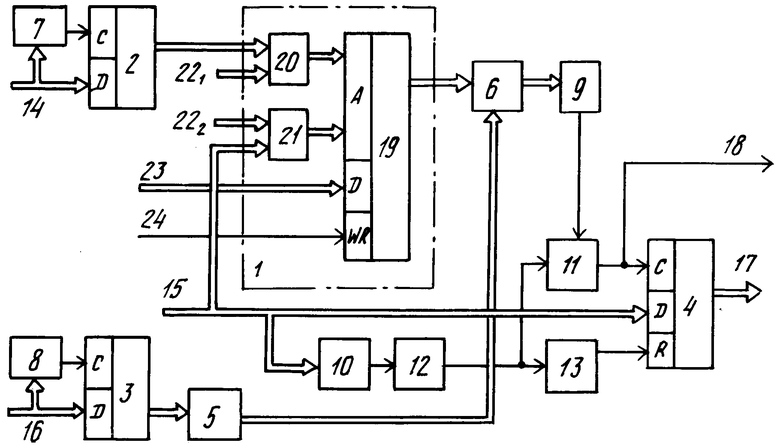

На чертеже приведена структурная схема заявляемого устройства для защиты памяти.

Устройство для защиты памяти содержит блок 1 памяти, первый 2 и второй 3 регистры, регистр 4 адреса, дешифратор 5, группу 6 элементов И, с первого по четвертый элементы ИЛИ 7-10, элемент И 11, формирователь 12 импульсов и элемент 13 задержки, входы 14-16 и выходы 17 и 18.

Блок 1 памяти содержит узел 10 памяти, первую 20 и вторую 21 группы элементов ИЛИ. Первые входы элементов ИЛИ группы 20 соединены с выходами регистра 2, вторые входы являются первой группой 22 адресных входов блока памяти.

Устройство работает следующим образом.

На вход 14 идентификатора устройства поступает идентификатор, имеющий два поля, где первое поле является идентификатором пользователя, а второе - идентификатором программы. На входы 16 устройства поступает код операции. На входы 15 устройства поступает код запрашиваемой ячейки памяти - ее адрес.

При подготовке устройства к работе в ячейки блока 1 памяти записываются коды разрешенных операций для каждого пользователя с каждой защищаемой ячейкой памяти. Процесс записи осуществляется таким образом: на входы 22 блока 20 подается код идентификатора пользователя (и программы), на входы 22 блока 21 - код адреса защищаемой ячейки памяти, на входы 23 записи кода - код, соответствующий разрешенным операциям данной программы данного пользователя с выбранной ячейкой памяти. Разрядность кода на входах 23 равна числу различных операций с памятью. Так, если некоторому пользователю при числе операций с памятью, равном "4", разрешены операции, закодированные как первая ("1") и вторая ("2"), то код, подаваемый для данной ячейки и данного пользователя на входы 23, имеет вид "1100". После установления сигналов на входах 22 и 23 подается импульс на вход 24 разрешения записи, и в соответствующую ячейку узла 19 записывается нужный код. Так производится для всех ячеек блока 1.

Таким образом, в исходном состоянии при готовности устройства к работе в ячейках блока 1 для каждого пользователя с конкретной программой и для каждой ячейки, защищаемой данным устройством, записаны коды разрешения. Состояние регистров 2 и 3 произвольно, содержимое регистра 4 адреса нулевое.

При поступлении кода идентификатора на входы 14 устройства (между обращениями в память на входах 14-16 нулевые сигналы) срабатывает элемент ИЛИ 7 и положительным фронтом сигнала на своем выходе записывает код идентификатора (пользователя и его программы) в регистр 2. Поступление кода операции на входы 16 аналогично реализует запись кода требуемой данному пользователю операции в регистр 3. (Запись в регистры 2 и 3 осуществляется корректно, так как сигнал на синхровходы регистров 2 и 3 поступает с естественной задержкой относительно кода на информационных входах, задерживаясь на элементах ИЛИ. Для обеспечения полной уверенности в срабатывании регистров между элементами ИЛИ 7 и 8 и соответственно синхровходами регистров 2 и 3 могут быть включены элементы задержки).

Двоичный код операции, зафиксированный в регистре 3, поступает на дешифратор 5, где преобразуется в позиционный код, причем единственная "единица" позиционного кода с выходов дешифратора 5 соответствует запрашиваемой операции.

Код адреса запрашиваемой ячейки защищаемой памяти поступает на входы 15 устройства. При поступлении этого кода на выходах блока 1 памяти формируется код разрешенных операций (для данного пользователя с его программой и запрашиваемой ячейки памяти). Этот код поступает на вторые входы элементов И группы 6. Если данная операция для данного пользователя с данной программой на запрашиваемой ячейке разрешена, то на выходе соответствующего элемента И группы 6 формируется положительный потенциал, вызывающий положительный сигнал на выходе элемента ИЛИ 9, элемент И 11 открывается.

Код ячейки памяти поступает также на входы элемента ИЛИ 10, сигнал с выхода которого поступает на формирователь 12 импульсов, формирующий с задержкой, достаточной для уверенного срабатывания последовательности блоков 1, 6 и 9, импульс требуемой длительности на своем выходе, который поступает через элемент И 11 на синхровход регистра 4 адреса, записывая в него код запрашиваемой ячейки памяти, защищаемой устройством, а также на выход 18 устройства, сообщая устройству управления ЭВМ о корректности обращения к памяти. Если запрашиваемая операция данного пользователя с его программой запрещена на запрашиваемой ячейке защищенной памяти, то на выходе элемента ИЛИ 9 нулевой потенциал, т.е. адрес запрашиваемой ячейки памяти не записывается в регистр 4 адреса, чем и осуществляется защита памяти.

После установки адреса в регистре 4 с задержкой, формируемой элементом 13 и необходимой для уверенного считывания кода адреса из регистра 4 адреса, появляется высокий потенциал на выходе элемента 13 задержки и устанавливает регистр адреса в нулевое состояние, завершая процесс обращения к защищенной памяти.

Выходы 17 регистра 4 адреса, как и в прототипе, могут быть соединены далее через дешифратор с накопительными элементами запоминающего устройства, ячейки которого защищаются, для выбора требуемых ячеек защищенной памяти (дешифратор и накопительные элементы не показаны).

Таким образом, заявляемое устройство позволяет реализовать процедуру защиты памяти не "по отдельности" для операций и запрашиваемых ячеек памяти для различных пользователей, а индивидуально для каждой ячейки защищенной памяти и для каждого пользователя с его конкретной программой определять разрешенные операции, что является более гибкой и широкой (в смысле использования) процедурой, чем аналогичная процедура прототипа, позволяющая для каждого пользователя реализовать защиту всех (а не индивидуальных) ячеек от некоторых операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1991 |

|

RU2020554C1 |

| УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ ЛЕКСИЧЕСКИХ МНОЖЕСТВ | 1990 |

|

RU2022354C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2023295C1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

| Устройство для кусочно-линейной аппроксимации | 1990 |

|

SU1837272A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| Устройство для формирования маршрута сообщения | 1990 |

|

SU1793447A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОПОЛНЕНИЯ МНОЖЕСТВА | 1990 |

|

RU2022353C1 |

Изобретение относится к вычислительной технике и может быть использовано для защиты ячеек памяти от несанкционированного обращения к ним. Целью изобретения является расширение функциональных возможностей и упрощение устройства. Устройство для защиты памяти содержит четыре элемента ИЛИ, два регистра, группу элементов И, элемент задержки, регистр адреса и дешифратор, блок памяти, формирователь импульсов и элемент И. 1 ил.

УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ, содержащее четыре элемента ИЛИ, два регистра, группу элементов И, элемент задержки, регистр адреса и дешифратор, причем первая группа входов идентификатора устройства соединена с входами первого элемента ИЛИ, входы операции устройства - с входами второго элемента ИЛИ, первая группа входов адреса устройства - с входами третьего элемента ИЛИ и с информационными входами регистра адреса, выходы которого являются адресными выходами устройства, входы четвертого элемента ИЛИ соединены с выходами элементов И группы, первые входы которых подключены к выходам дешифратора, выход элемента задержки соединен с входом сброса регистра адреса, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности задания набора разрешенных операций и упрощения, в него введены формирователь импульсов, элемент И и блок памяти разрешенных операций, содержащий узел памяти и две группы элементов ИЛИ, причем выход первого элемента ИЛИ соединен с синхровходом первого регистра, к информационным входам которого подключены входы первой группы идентификатора устройства, выход второго элемента ИЛИ соединен с синхровходом второго регистра, к информационным входам которого подключены входы операции устройства, выходы первого регистра и вторая группа входов идентификатора устройства соединены соответственно с первыми и вторыми входами элементов ИЛИ первой группы блока памяти разрешенных операций, входы адреса устройства первой и второй групп соединены соответственно с первыми и вторыми входами элементов ИЛИ второй группы блока памяти разрешенных операций, выходы элементов ИЛИ первой и второй групп соединены с адресными входами узла памяти, информационные входы и вход разрешения записи которого являются одноименными входами устройства, а выход - выходом блока памяти разрешенных операций и подключен к вторым входам элементов И группы, выходы второго регистра соединены с входами дешифратора, выходы четвертого элемента ИЛИ и формирователя импульсов - с входами элемента И, выход которого подключен к синхровходу регистра адреса и является выходом разрешения обращения устройства, выход третьего элемента ИЛИ соединен с входом формирователя импульсов, выход которого подключен к входу элемента задержки.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для защиты памяти | 1988 |

|

SU1508216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-09-30—Публикация

1990-11-15—Подача