Изобретение относится к электросвязи и может быть использовано в кодоимпульсных системах телеуправления.

Известное устройство для приема трехкратно повторяемых команд управления содержит три блока памяти, мажоритарный блок, два ключа, анализатор кодового признака, накопитель, дешифратор, пять элементов ИЛИ, три счетчика, распределитель и элемент И и позволяет существенно повысить помехоустойчивость приема команд телеуправления за счет мажоритарной обработки.

Известное устройство для приема команд телеуправления содержит два блока памяти, два счетчика, четыре триггера, три инвертора, элемент И, элемент ИЛИ, регистр сдвига, два ключа, два дешифратора, два блока сравнения и позволяет расширить область применения устройства за счет приема команд управления в прямом и инверсном коде.

Известное устройство для приема команд телеуправления содержит блок преобразования последовательных кодовых комбинаций в сигналы управления, три блока памяти, интегратор, элемент ИЛИ, генератор опорных частот, делитель частоты, элемент И, счетчик пачек импульсов считывания, адресный счетчик, три дифференцирующих элемента, элементы ИЛИ, RS-триггер и позволяет вести прием без синхронизации по тактам способом приема кодовых сигналов.

Недостатком устройства является ограничение на скорость приема команд телеуправления, вызванное необходимостью последовательного анализа на каждом такте приема большого объема двоичной информации, равного числу двоичных символов в команде телеуправления, записанного в каждом из трех блоков памяти.

Поставленная цель достигается тем, что в устройство для приема команд телеуправления, содержащее интегратор, вход которого является входом устройства, выход подключен к входу первого блока памяти, генератор опорной частоты, выход которого соединен с входом делителя частоты, два элемента ИЛИ, элемент И, RS-триггер, формирователь сигналов управления, адресный счетчик, счетчик пачек импульсов, блоки памяти, выход первого элемента ИЛИ подключен к формирователю сигналов управления, введены регистры сдвига, элементы сравнения, RS-триггеры, D-триггеры, элемент ИЛИ и группа элементов И, блок памяти ключевой кодовой комбинации, дешифратор, элемент НЕ, первый, второй, третий выходы делителя частоты через второй элемент ИЛИ соединены с управляющим входом интегратора, первый выход подключен непосредственно к управляющим входам первого, второго и третьего блоков памяти, к первому входу третьего элемента ИЛИ и к установочному входу счетчика пачек импульсов, второй и третий выходы подключены к С-входам, соответственно, первого и второго регистров сдвига, выходы которых подключены к входам второго и третьего блоков памяти, D-входы регистров сдвига соединены с выходом интегратора, выход каждого блока памяти соединен с первыми входами одноименного элемента сравнения и одноименного элемента И группы, выходы элементов И группы соединены с входами первого элемента ИЛИ, выход третьего элемента ИЛИ подключен через адресный счетчик к адресным входам блоков памяти, выходы счетчика пачек импульсов через блок памяти ключевой кодовой комбинации подключены к вторым входам элементов сравнения и непосредственно к входам дешифратора, первый выход которого соединен с S-входами RS-триггеров и R-входами D-триггеров и через элемент НЕ соединен с первым входом элемента И, второй вход которого подключен к генератору опорной частоты, а выход соединен с вторым входом третьего элемента ИЛИ и со счетным входом счетчика пачек импульсов, второй выход дешифратора соединен с С-входами D-триггеров, выходы которых подключены к вторым входам одноименных элементов и группы выходы элементов сравнения соединены с установочными входами R одноименных RS-триггеров, выходы RS-триггеров соединены с D-входами одноименных D-триггеров.

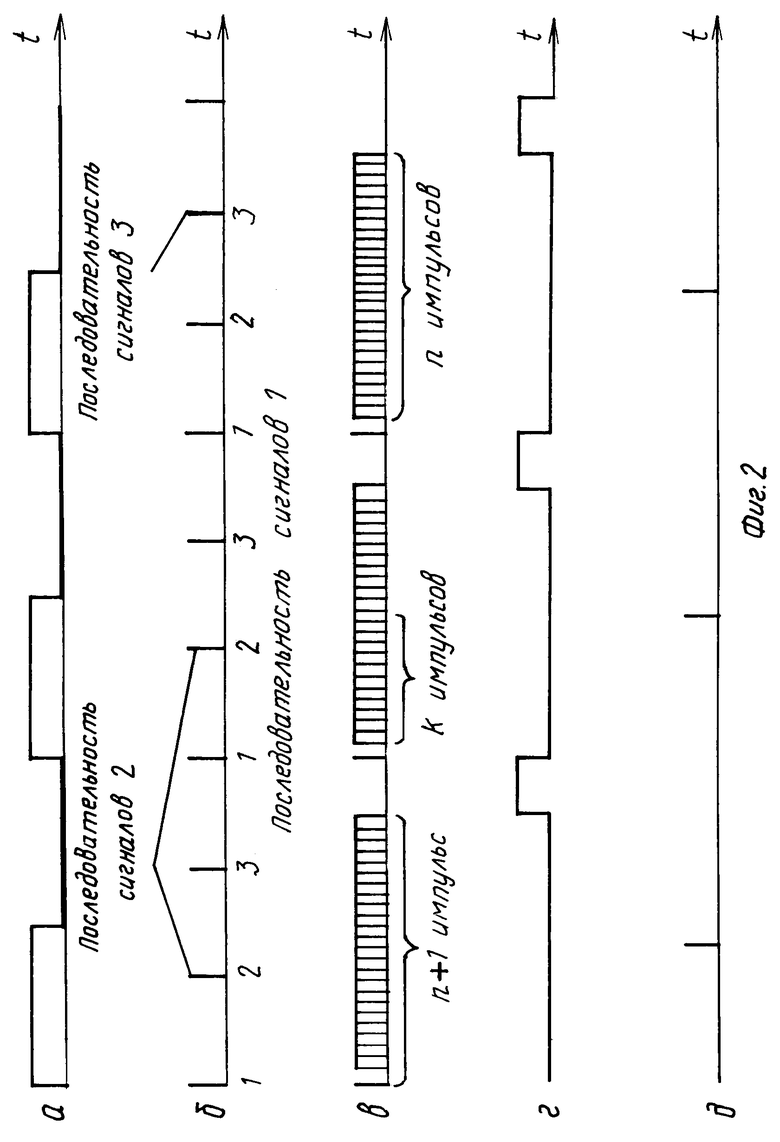

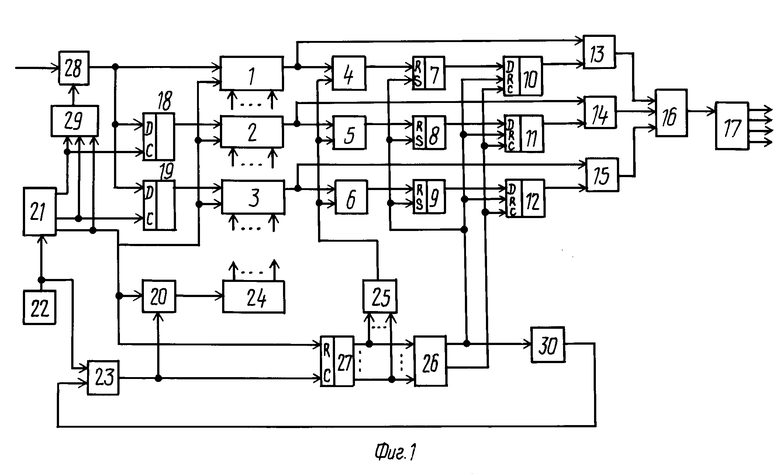

На фиг.1 приведена структурная электрическая схема предложенного устройства; на фиг.2 - временные диаграммы основных сигналов устройства; на фиг. 2А - эпюра частоты F приема; на фиг.2Б - последовательности сигналов 1, 2 и 3 соответственно на первом, втором и третьем выходах делителя частоты 21; на фиг.2В - пачки импульсов, поступающих на вход адресного счетчика 24; на фиг.2Г - сигнал на первом выходе дешифратора 26, запирающего работу устройства; на фиг.2Д - сигнал на втором выходе дешифратора 26, разрешающий прохождение информационной части команды управления в формирователь 17.

Устройство для приема команд телеуправления содержит первый 1, второй 2, третий 3 блоки памяти, емкость каждого из которых равна n числу двоичных символов в команде телеуправления, первый 4, второй 5 и третий 6 элементы сравнения, RS-триггеры 7, 8, 9, D-триггеры 10, 11, 12, группу элементов И 13, 14, 15, первый 16 элемент ИЛИ, формирователь 17 сигналов управления, регистры сдвига 18, 19, третий 20 элемент ИЛИ, делитель 21 частоты, генератор 22 опорной частоты, первый 23 элемент И, адресный счетчик 24 емкостью n+1, блок 25 памяти ключевой кодовой комбинации емкостью К, где К - число символов в ключевой кодовой комбинации, дешифратор 26, счетчик пачек 27, интегратор 28, второй элемент 29 ИЛИ, элемент НЕ 30.

Устройство осуществляет прием информации без предварительной тактовой синхронизации, прием команд данным способом осуществляется следующим образом. Входная информация обрабатывается без привязки к фронтам принимаемых элементарных посылок. При этом время, равное длительности одного символа Т, делится на 3 равных интервала. В течение каждого интервала информация с выхода демодулятора интегрируется и в конце интервала регистрируется значение принимаемой информации: "0" или "1". Информация, регистрируемая во время одноименных интервалов, записывается в соответствующие блоки памяти, где хранится в течение времени, необходимого для приема команд телеуправления. За время Т содержимое каждого блока памяти, состоящее из информационных символов, записанных последовательно в одноименные интервалы поочередно считывается и проверяется на соответствие эталонной ключевой комбинации и закону кодирования. В (4) доказано, что в течение времени, необходимого для приема команды, хотя бы один из временных интервалов будет находиться в зоне оптимального приема.

Устройство работает следующим образом.

За период частоты приема F (фиг.2А) делитель частоты 21 формирует на своих выходах три последовательности коротких импульсов 1, 2 и 3, смещенных друг относительно друга на 1/3 длительности передачи одного символа Т (фиг. 2Б). Импульсом 2 (фиг.2Б) информация с выхода интегратора записывается в первый регистр сдвига 18, осуществляющий задержку принимаемой информации на один период частоты F.

Импульсом 3 (фиг. 2Б) информация с выхода интегратора записывается во второй регистр сдвига 19, осуществляющий задержку принимаемой информации на два периода частоты F.

Импульсом 1 (фиг.2Б) информация с выхода интегратора переписывается в первый 1 блок памяти и с выхода первого 18 и второго 19 регистров сдвига задержанная информация переписывается во второй 2 и в третий 3 блоки памяти.

Последовательности импульсов 1, 2, 3 через второй элемент ИЛИ 29 воздействуют на установочный вход интегратора 28 и переводят его в исходное состояние.

Импульсы 1 устанавливают в исходное состояние счетчик пачек 27.

При этом на первом выходе дешифратора 26 устанавливается сигнал логического "0". Тем самым снимается установочный сигнал (фиг.2Г) с триггеров 7-12 и через элемент НЕ 30 поступает разрешающий сигнал логической "1" на первый элемент И 23.

Через элемент И 23 на счетчик пачек 27 поступают импульсы частоты f>n+1. Выходной код счетчика пачек 27 осуществляет перебор адресов с нулевого до n блока памяти ключевой кодовой комбинации.

При этом происходит считывание эталонной ключевой кодовой комбинации на вторые входы элементов сравнения 4-6. Сигналы на выходе третьей схемы ИЛИ 20, а также на первом и втором выходах дешифратора 26 приведены на фиг.2В, Г, Д.

Последовательности импульсов 1, 2 и 3 (фиг. 2Б) осуществляют считывание информации с выхода интегратора либо непосредственно в блок памяти 1, либо через буферные регистры сдвига 18, 19 в блоки памяти 2 и 3.

Формирование пачки из n+1 импульсов, поступающих на вход адресного счетчика 24, приводит к обновлению на каждом такте на один бит информации, записанной в каждом из блоков памяти. Введение регистров сдвига 18 и 19 обеспечивает временной разнос в приеме информации по различным подканалам, т. е. делает невозможным выделение ключевой кодовой комбинации одновременно по двум или трем подканалам. Это позволяет осуществлять одновременное параллельное считывание информации из трех блоков памяти и обеспечивает выполнение поставленной в изобретении цели - повышение быстродействия устройства. Цикл обработки накопленной в блоках памяти информации начинается импульсом 1, разблокирующим работу устройства.

Когда импульсом 1 в один из блоков памяти 1, 2 или 3 будет записан последний символ команды управления, то первый же из n импульсов частоты обработки f, поступивший через схему ИЛИ 20 на вход адресного счетчика 24 приведет к считыванию из этого блока памяти на вход соответствующего элемента сравнения 4-6 первого символа ключевой кодовой комбинации. Одновременно этот же импульс с выхода элемента И 23 переключает счетчик пачек 27, который является адресным счетчиком для блока памяти ключевой кодовой комбинации. При этом с выхода блока памяти ключевой кодовой комбинации на второй вход схемы сравнения считывается также первый символ эталонной ключевой комбинации.

Сравнение принятого и эталонного символов происходит на элементах сравнения 4-6. При несовпадении символов на выходе элемента сравнения появляется сигнал логической "1", который устанавливает RS-триггер данного подканала в состояние логического "0" по выходу. После сравнения всех К символов ключевой (счетчик пачек 27 насчитывает К импульсов частоты f) дешифратор 26 по второму выходу формирует импульс (фиг.2Д), который переписывает на выход D-триггеров 10-12 состояние, установившееся к этому времени на их D-входах. Если по одному из подканалов принятая ключевая кодовая комбинация совпадает с эталонной, на выходе D-триггера данного подканала установится состояние логической "1", что обеспечит прохождение информационной части команды управления через элемент И данного подканала (13-15) и элемент ИЛИ 16 на вход формирователя сигналов управления 17. За счет введения регистров сдвига 18 и 19 невозможно одновременное выделение ключевой по двум и более подканалам.

При соответствии считанной в блок 17 информации закону кодирования она регистрируется в качестве принятой команды телеуправления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема трехкратно повторяемых команд управления | 1986 |

|

SU1385309A1 |

| Устройство для приема команд телеуправления | 1988 |

|

SU1575220A1 |

| Устройство для приема многократно повторяемых команд | 1984 |

|

SU1226510A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ С МНОГОСТАНЦИОННЫМ ДОСТУПОМ | 1985 |

|

RU2072634C1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Телеизмерительная система с управляющей обратной связью | 1988 |

|

SU1571636A1 |

Изобретение относится к электросвязи и может быть использовано в кодоимпульсных системах телеуправления. Целью изобретения является повышение допустимой скорости приема. Устройство содержит блоки памяти 1,2,3, элементы сравнения 4,5,6 RS-триггеры 7,8,9, D-триггеры 10,11,12, элементы И 13,14,15, элементы ИЛИ 16, формирователь сигналов управления 17, регистры сдвига 18, 19, элемент ИЛИ 20, делитель 21 частоты, генератор 22 опорной частоты, элемент И 23, адресный счетчик 24, блок 25 памяти ключевой кодовой комбинации, дешифратор 26, счетчик 27 пачек, интегратор 28, элементы ИЛИ 29 и НЕ 30. Устройство позволяет принимать команды управления без предварительной тактовой синхронизации высокой скорости передачи. 2 ил.

УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ, содержащее интегратор, выход которого является входом устройства, выход подключен к входу первого блока памяти, генератор опорной частоты соединен с входом делителя частоты, два элемента ИЛИ, элемент И, RS-триггер, формирователь сигналов управления, адресный счетчик, счетчик пачек импульсов, блоки памяти, выход первого элемента ИЛИ подключен к формирователю сигналов управления, отличающееся тем, что с целью повышения допустимой скорости приема, в устройство введены регистры сдвига, элементы сравнения, RS-триггеры, D-триггеры, элементы ИЛИ и группа элементов И, блок памяти ключевой кодовой комбинации, дешифратор, элемент НЕ, первый, второй и третий выходы делителя частоты через второй элемент ИЛИ соединены с управляющим входом интегратора, первый выход подключен непосредственно к управляющим входам первого, второго и третьего блоков памяти, к первому входу третьего элемента ИЛИ и к установочному входу счетчика пачек импульсов, второй и третий выходы подключены к C-входам соответственно первого и второго регистров сдвига, выходы которых подключены к входам второго и третьего блоков памяти, D-входы регистров сдвига соединены с выходом интегратора, выход каждого блока памяти соединен с первыми входами одноименного элемента сравнения и одноименного элемента И группы, выходы элементов И группы соединены с входами первого элемента ИЛИ, выход третьего элемента ИЛИ подключен через адресный счетчик к адресным входам блоков памяти, выходы счетчика пачек импульсов через блок памяти ключевой кодовой комбинации подключены к вторым входам элементов сравнения и непосредственно к входам дешифратора, первый выход которого соединен с S-входами RS-триггеров и R-входами D-триггеров и через элемент НЕ с первым входом элемента И, второй вход которого подключен к генератору опорной частоты, выход соединен с вторым входом третьего элемента ИЛИ и со счетным входом счетчика пачек импульсов, второй выход дешифратора соединен с C-входами D-триггеров, выходы которых подключены к вторым входам одноименных элементов И группы, выходы элементов сравнения соединены с установочными входами одноименных RS-триггеров, выходы RS-триггеров соединены с D-входами одноименных D-триггеров.

| Авторское свидетельство СССР N 841501, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-11-15—Публикация

1991-06-26—Подача