со

00

ел

оо о со

Изобретение опгоснтся к телеуправлению и может использоваться для приема трёхкратно нередапаемых команд управления, содержащих комбинацию фазового пуска и И11(}юрмапионпую часть.

Целью изобретения является повы 1ение помехоустойчивости приема команд управления.

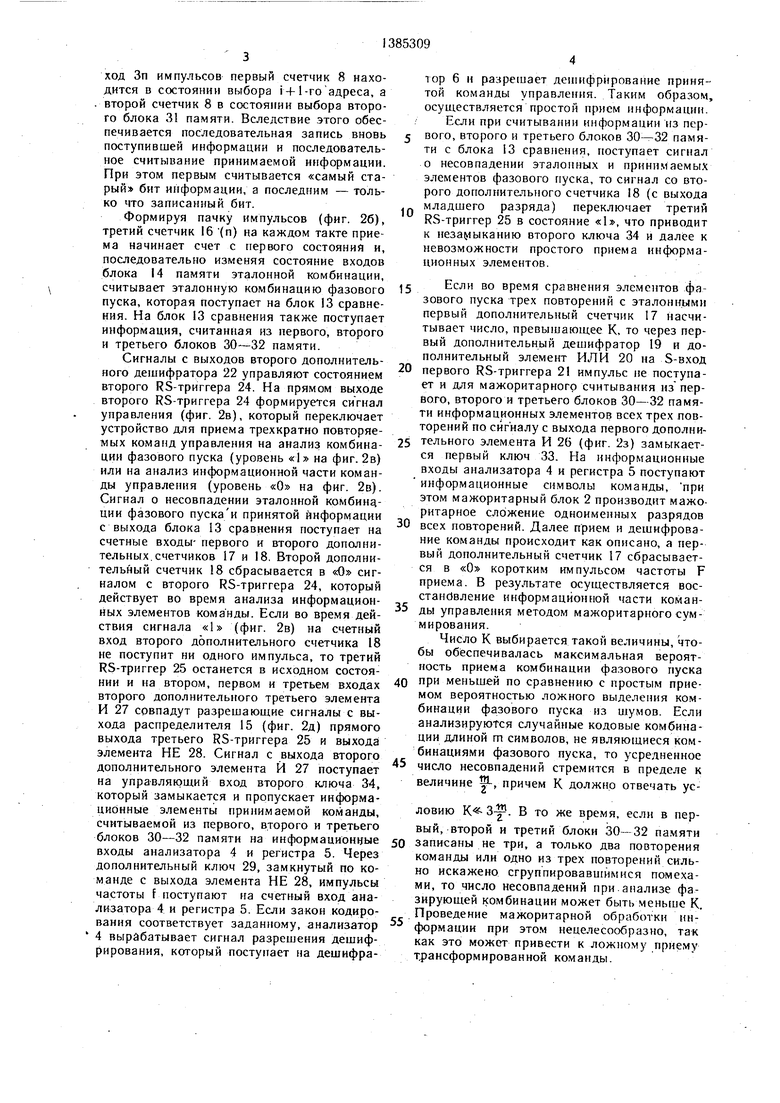

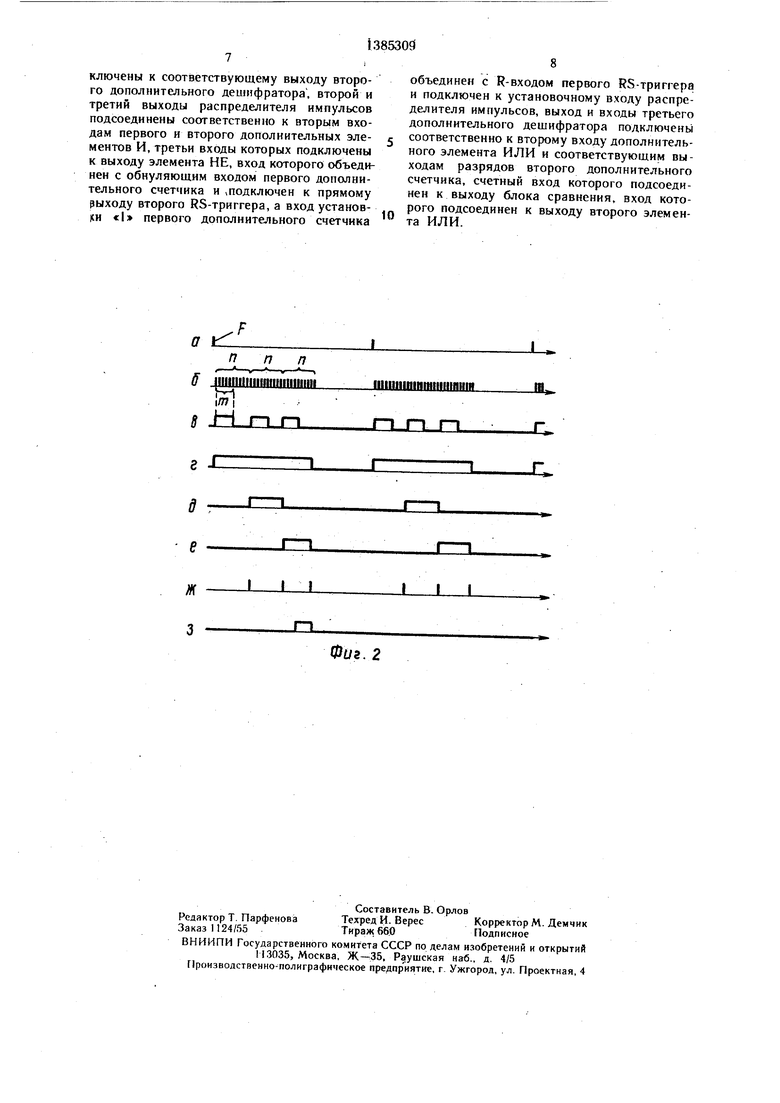

На фиг. представлена структурная электрическая схема предлагаемого устройства для приема трехкратно повторяемых команд управ ления; па фиг. 2 - временные диаграммы сигналов, поясняющие работу устройства для приема трехкратно повторяемых команд управления.

Устройство для приема трехкратно повторяемых команд управления содержит блок I элементов памяти входной информации, мажоритарный блок 2, блок 3 ключей, анализатор 4 кодового признака, регистр 5 сдвига, дешифратор 6, блок 7 элементов ИЛИ, первый и второй счетчики 8 п 9 импульсов, первый элемент ИЛИ 10, элемент И I 1, второй элемент ИЛИ 12, блок 13 сравнения, блок 14 памяти эталонной комбинации, распределитель 15 импульсов, третий счетчик 16 импульсов, первый и второй дополнительные счетчики 17 и 18 импульсов, первый дополнительный дешифратор 19, дополнительный элемент ИЛИ 20, первый RS-триггер 21, второй и третий дополнительные дешифраторы 22 и 23, второй и третий RS-триггеры 24 и 25, первый и второй дополнительные элементы И 26 и 27, элемент НЕ 28, дополнительный ключ 29. .

Блок 1 элементов памяти входной информации содержит первый, второй и третий блоки 30-32 памяти. Блок 3 ключей содержит первый и второй ключи 33 и 34 и раз вязываюший элемент 35. Блок 7 элементов ИЛИ содержит первый, второй и третий элементы ИЛИ 36-38.

Устройство для приема трехкратно повторяемых команд управления работает следующим образом..

Короткий тактовый импульс, поступаю- и1ий с частотой F приема (фиг. 2 а) на тактовый вход устройства для приема трехкратно повторяемых команд управления (фиг. I), устанавливает первое состояние распределителя 15, переключает на короткое время первый, второй и третий блоки 30-32 памяти из режима считывания в режим записи. Это обеспечивает запись входного (принимаемого) символа в соответствуюш.ий первый, второй или третий блок (30-32) па мяти, выбор которого определяется состоянием второго счетчика 9. На счетный вход второго счетчика 9 поступает сигнал с выхода старшего разряда первого счетчика 8. Сигнал с выхода второго счетчика 9 через первый, второй или третий элементы ИЛИ 36-38 поступает на вход выбора ячейки памяти соответствующего первого, второго

или третьего блока (30-32) памяти, а сигналы, поступаюшие на адресные входы первого, второго и третьего блоков 30-32 памяти, определяются состоянием первого счетчика 8. После окончания записи тактовый импульс частоты F через первый элемент ИЛИ 10 измеЕ(яет на «Г состояние первого счетчика 8.

В дальнейшем на счетный вход третьего счетчика 16 через элемент И 11 и на счетный вход первого, счетчика 8 через первый элемент ИЛИ 10 и элемент ИИ поступают импульсы с частотой обработки f, которая выбирается из соотношения , где Р - частота приема; п - число элементов кодоC вой комбинации команды управления.

После подсчета п импульсов с выхода третьего счетчика 16 через второй дополнительный дешифратор 22 на тактовый вход распределителя 15 поступает сигнал (фиг. 2 ж), который переключает распределитель 15 последовательно во второе, третье и четвертое состояния. Сигналы первого, второго и третьего выходов распределителя 15 показаны на фиг. 2г, д, е соответственно.

5При установке распределителя 15 в четвертое состояние сигнал (фиг. 2г) с первого выхода распределителя 15 поступает на первый вход элемента И 11 и запрещает прохождение через него импульсов частоты обработки. Разрешение прохождения импульсов

0 обработки происходит после установки исходного состояния распределителя 15 импульсом частоты F приема. Таким образом, осуществляется формирование пачки Зп импульсов (фиг. 26), используемых для считывания Зп бит информации из первого, вто5 рого и третьего блоков 30-32 памяти.

Пусть во время записи очередного бита информации первым счетчиком 8 выбирается i-й адрес, а вторым счетчиком 9 через вто0 рой элемент ИЛИ 37 выбирается второй блок 31 памяти. После записи только что .«рииятого символа информации .в i-ю ячейку памяти второго блока 31 памяти первый счетчик 8 устанавливается в состояние i-f-J. Если в i-ю ячейку памяти записан последний

5 символ третьего повторения команды, то в i-f 1-й ячейке находится первый символ первого повторения команды, записанной Зп тактов тому назад; Этот символ и поступает первым на выход второго блока 31 памяти. Дальнейшее поступление импульсов обра- ботки на вход первого счетчика 8 последовательно выбирает i+2,..., п-й адреса второго блока 31 памяти.

Каждый раз после выбора п-го адреса переключается состояние второго счетчика 9

/ и через соответствующие первый, второй и третий элементы ИЛИ 36-38 выбирается следующий из первого, второго и третьего блоков 30-32. После поступления на выход Зп импульсов первый счетчик 8 находится в состоянии выбора 1 +1-го адреса, а

второй счетчик 8 в состоя гин выбора второго блока 31 памяти. Вследствие этого обеспечивается последовательная запись вновь поступившей информации и последовательное считывание принимаемой информации. При этом первым считывается «самый старый бит информации, а последним - только что записанный бит.

Формируя пачку импульсов (фиг. 26), третий счетчик 16 (п) на каждом такте приема начинает счет с первого состояния и, последовательно изменяя состояние входов блока 14 памяти эталонной комбинации, считывает эталонную комбинацию фазового пуска, которая поступает на блок 13 сравнения. На блок 13 сравнения также поступает информация, считанная из первого, второго и третьего блоков 30-32 памяти.

Сигналы с выходов второго дополнительного дешифратора 22 управляют состоянием второго RS-триггера 24. На прямом выходе второго RS-триггера 24 формируется сигнал управления (фиг. 2в), который переключает устройство для приема трехкратно повторяемых команд управления на анализ комбинации фазового пуска (уровень «1 на фиг. 2в) или на анализ информационной части команды управления (уровень «О на фиг. 2в). Сигнал о несовпадении эталонной комбинд- ции фазового пуска и принятой информации с выхода блока 13 сравнения поступает на счетные входы- первого и второго дополнительных, счетчиков 17 и 18. Второй дополнительный счетчик 18 сбрасывается в «О сигналом с второго RS-триггера 24, который действует во время анализа информационных элементов кома нды. Если во время действия сигнала «1 (фиг. 2в) на счетный вход второго дополнительного счетчика 18 не поступит ни одного импульса, то третий RS-триггер 25 останется в исходном состоянии и на втором, первом и третьем входах второго дополнительного третьего элемента И 27 совпадут разрешающие сигналы с выхода распределителя 15 (фиг. 2д) прямого выхода третьего RS-триггера 25 и выхода элемента НЕ 28. Сигнал с выхода второго дополнительного элемента И 27 поступает на управляющий вход второго ключа 34, который замыкается и пропускает информационные элементы принимаемой команды, считываемой из первого, второго и третьего блоков 30-32 памяти на информационные входы анализатора 4 и регистра 5. Через дополнительный ключ 29, замкнутый по команде с выхода элемента НЕ 28, импульсы частоты f поступают на счетный вход анализатора 4 и регистра 5. Если закон кодирования соответствует заданному, анализатор

4 вырабатывает сигнал разрешения дешифрирования, который поступает на дешифратор 6 и разрешает дешифрирование принятой команды управления. Таким образом, осуществляется простой прием информации. Если при считывании информации из первого, второго и третьего блоков 30-32 памяти с блока 13 сравнения, поступает сигнал о несовпадении эталонных и принимаемых элементов фазового пуска, то сигнал со второго дополнительного счетчика 18 (с выхода

- младшего разряда) переключает третий RS-триггер 25 в состояние «1, что приводит к пеза 1ыканию второго ключа 34 и далее к невозможности простого приема информационных элементов.

5 Если во время сравнения элементов фазового пуска трех повторений с эталонными первый дополнительный счетчик 17 насчитывает число, превышающее К, то через первый дополнительный дешифратор 19 и дополнительный элемент ИЛИ 20 на S-вход

0 первого RS-триггера 21 импульс не поступает и для мажоритарного считывания из первого, второго и третьего блоков 30-32 памяти информационных элементов всех трех повторений по сигналу с выхода первого дополни5 тельного элемента И 26 (фиг. 2з) замыкается первый ключ 33. На информационные входы анализатора 4 и регистра 5 поступают информационные символы команды, при этом мажоритарный блок 2 производит мажоритарное сложение одноименных разрядов

0 всех повторений. Далее прием и дешифрование команды происходит как описано, а первый дополнительный счетчик 17 сбрасывается в «О коротким импульсом частоты F приема. В результате осуществляется вос- станбвление информационной части коман5 ды управления методом мажоритарного суммирования.

Число К выбирается такой величины, чтобы обеспечивалась максимальная вероятность приема комбинации фазового пуска

0 при меньшей по сравнению с простым приемом вероятностью ложного выделения комбинации фазового пуска из шумов. Если анализируются случайные кодовые комбинации длиной m символов, не являющиеся комбинациями фазового пуска, то усредненное

5

число несовпадении стремится в пределе к величине , причем К должно отвечать условию K f-3- . В то же время, если в первый, второй и третий блоки 30-32 памяти 0 записаны не три, а только два повторения команды или одно из трех повторений сильно искажено сгруппировавшимися помехами, то число несовпадений при анализе фазирующей комбинации может быть меньше К. .Проведение мажоритарной обработки информации при этом нецелесообразно, так как это может привести к ложному приему т| ансформнрованной команды.

Поэтому предусмотрен второй более низкий порог, при котором запрещается мажо- ритарпый анализ информационной части команды управления до тех нор, пока в первом, втором и третьем блоках 30-32 памяти не будут 3anHcatibi все три повторения ко- манд1э1. Этот порог реализован с использованием второго донолнительного счетчика 18, третьего дополнительного деигифратора 23 и дoнoлнитeль югo элемента ИЛИ 20. Если второй дополнительный счетчик 18 за время анализа одного из повторений команды (любого) насчитает число несовпадений I, удовлетворяющее неравенству i/i I, то сигнал

с выхода третьего дополнительного ратора 23 через дополнительный элемент ИЛИ 20 устанавливает первый RS-триггер 21 в состояние, при котором первый дополнительный элемент И 26 занрен1ает мажоритарную обработку информационной части команды управления. Этим предотвращается возможность ложного приема трансформированной команды управления.

Формула изобретения

Устройство для приема трехкратно повторяемых команд управления, содержащее последовательно соединенные блок элементов памяти входной информации, мажоритарный-блок, блок ключей, регистр сдвига и дешифратор, последова -гльно соединенные элементы И, первый элемент ИЛИ, первый и второй счетчики импульсов, а также анализатор кодового признака, распределитель импульсов, третий счетчик импульсов, .бЛок элементов ИЛИ и второй элемент ИЛИ, первый вход которого подключен к первому входу мажоритарного блока, объединенные вторые входы и объединенные третьи входы мажоритарного блока и второго элемента ИЛИ подключены соответственно к второму и третьему выходам блока элементов памяти входной информации, адресные входы которого подключены к соответствующим выходам разрядов первого счетчика импульсов, входы Выбора ячейки памяти блока элементов памяти входной информации подключены к соответствующим выходам блока элементов ИЛИ, первые входы которого подключены к соответствующим выходам разрядов второго счетчика-импульсов, первый вход и выход .элемента И подключены соответственно к первому выходу распределителя импульсов и счетному входу третьего счетчика импульсов, второй вход первого эле. мента ИЛИ подключен к установочному входу распределителя импульсов и тактовому входу блока элементов памяти входной информации, информационный и тактовый входы и выход анализатора кодового признака

0

5

0

5

0

5

0

5

0

5

подключены соответственно к выходу блока ключей, тактовому входу регистра сдвига и разрешающему входу дешифратора, а выход второго элемента ИЛИ подсоединен к второму информационному входу блока ключей, причем информационный и тактовый входы блока элементов памяти входной информации, второй вход элемента И и выходы дешифратора являются соответственно информационным и тактовым входами, входом им- Пульсов обработки и выходами устройства, а блок элементов памяти входной информации содержит первый; второй и третий блоки памяти, адресные входы, входы выбора ячеек памяти, объединенные информационные входы, объединенные тактовые входы и выходы которых являются соответственно адресными входами, входами выбора ячеек памяти, информационным и тактовым входами и первым, вторым и третьим выходами блока элементов памяти входной информации,.блок ключей содержит первый и второй ключи, информационный и управляющие входы которых являются соответственно первым и вторым информационными входами и первым и вторым управляющими входами блока ключей, выходы первого и второго ключей, объединенные через развязывающий элемент, являются выходом блока ключей, блбк элементов ИЛИ содержит первый, второй и третий элементы ИЛИ, первые входы и объединенные вторые входы и выходы которых являют(;я соответственно первыми входами, вторым входом и выходами блока эле-- ментов ИЛИ, отличающееся тем, что, с целью повышения помехоустойчивости приема команд управления, введены последовательно соединенные блок памяти эталонной ком-, бинации, блок сравнения, первый дополнительный счетчик импульсов, первый дополнительный дешифратор, дополнительный элемент ИЛИ; первый RS-триггер и первый дополнительный элемент И, выход которого подсоединегг к первому управляющему входу блока ключей и второму входу блока элементов ИЛИ, последовательно соединенные второй дополнительный дешифратор, второй RS-триггер, второй дополнительный счетчик импульсов, третий RS-триггер и второй дополнительный элемент И, выход которого подсоединен к второму управляющему входу блока ключей, последовательно соединенные элемент НЕ и дополнительный ключ, информационный вход и выход которого подключены соответственно к выходу элемента И и тактовому входу регистра сдвига, а также третий дополнительный дешифратор, при этом выходы разрядов третьего счетчика импульсов подсоединены к соответствующим входам второго дополнительного дешифратора и блока памяти эталонной комбинации. R- вход третьего RS-триггера и тактовый вход распределителя импульсов подключены к соответствующему выходу второго дополнительного дешифратора, второй и третий выходы распределителя импульсов подсоединены соответственно к вторым входам первого и второго дополнительных эле- ментов И, третьи входы которых подключены к выходу элемента НЕ, вход которого объединен с обнуляющим входом первого дополнительного счетчика и ,подключен к прямому рыходу второго RS-триггера, а вход установ- (СИ с| первого дополнительного счетчика

объединен с R-входом первого RS-триггера и подключен к установочному входу распределителя импульсов, выход и входы третьего дополнительного дещифратора подключены соответственно к второму входу дополнительного элемента ИЛИ и соответствующим выходам разрядов второго дополнительного счетчика, счетный вход которого подсоединен к выходу блока сравнения, вход которого подсоединен к выходу второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема трехкратно повторяемых команд управления | 1979 |

|

SU873436A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для адаптивного мажоритарного декодирования фазирующих сигналов | 1984 |

|

SU1213492A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для измерения временных интервалов | 1979 |

|

SU775714A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для тактовой синхронизации с регенерацией дискретных сигналов | 1976 |

|

SU594595A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

Изобретение относится к телеуправлению. Цель изобретения - повышение помехоустойчивости приема команд управления. Устр-во содержит .блок 1 элементов памяти входной информации, мажоритарный блок 2. блок 3 ключей, анализатор 4 кодового признака, регистр 5 сдвига, дешифратор 6, блок 7 элементов ИЛИ, счетчики 8, 9 и 16 импульсов, элементы ИЛИ 10 и 12, элемент И II, распределитель 15 импульсов. В устр-во введены блок 13 сравнения, блок 14 памяти эталонной комбинации, счетчики 17 и 18 им: пульсов, дешифраторы 19, 22 и 23, элемент ИЛИ 20, RS-триггеры 21, 24 и 25, элементы И 26 и 27, элемент НЕ 28 и ключ 29. В устр-ве осуществляется прием трех повторений команды управления, при котором выделение комбинации фазового пуска осуществляется путем подсчета числа песовпадаю- HU1X элементов принятых комбинаций фазового нуска трех повторений команды с эталонной комбинацией фазового пуска. Прием информационной части команды управления осун1ествляется путем мажоритарного суммирования элементов информационных частей трех повторений команды. Этим предот- В1Га1иается возможность ложного приема трансформированной команды управления. 2 ил. S О)

1/77 I

8 J Lr-Lr-T

ж

I 11

Фиг. 2

JL

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1979 |

|

SU873436A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-03-30—Публикация

1986-02-25—Подача