Изобретение относится к технологии изготовления кремниевых высоковольтных мощных микросхем с диэлектрической изоляцией.

Известен способ изготовления высоковольтных кремниевых микросхем с диэлектрической изоляцией, включающий травление разделительных канавок на плоскопараллельной монокристаллической слаболегированной кремниевой пластине, формирование сильнолегированного скрытого слоя того же типа проводимости, что и пластина, на поверхности вытравленного рельефа, покрытие поверхности рельефа изолирующим окислом и поликремнием-подложкой, удаление монокристаллического кремния для формирования изолированных областей-карманов, формирование в карманах транзисторных структур методом планарной технологии, вскрытие окон, не выходящих за пределы карманов, для сильнолегированных областей, смыкающихся со скрытым слоем, формирование сильнолегированных областей, формирование диэлектрика на поверхности сильнолегированных областей, вскрытие окон в диэлектрике под контакты к монокристаллическому кремнию, формирование шин металлизации к элементам микросхем и скрытому слою [1]. Сильнолегированную область, смыкающуюся со скрытым слоем, создают для снижения сопротивления между скрытым слоем и металлическим контактом. Это особенно важно для высоковольтных мощных микросхем, так как для их изготовления используется монокристаллический кремний с высоким удельным сопротивлением.

Между сильнолегированным скрытым слоем и металлом контакта остается область нелегированного монокристаллического кремния с высоким удельным сопротивлением, приводящая к увеличению остаточных напряжений на транзисторах, что зачастую бывает крайне нежелательно. Наличие области нелегированного монокристаллического кремния обусловлено тем, что между внешней границей сильнолегированной области, которая фиксирована, и внутренней границей скрытого слоя, которая изменяется из-за изменения толщины монокристаллического кремния кармана, так как при формировании поликремниевой подложки возникают механические напряжения и вся структура испытывает изгиб, возможен зазор от нуля (при минимальной толщине монокристаллического кремния) до 8 мкм (при максимальной толщине монокристаллического кремния). Именно эта нелегированная область и увеличивает сопротивление между металлическим контактом и скрытым слоем.

Наиболее близким к предлагаемому способу изготовления микросхем с диэлектрической изоляцией является способ, включающий травление разделительных канавок на плоскопараллельной монокристаллической слаболегированной кремниевой пластине, формирование сильнолегированного скрытого слоя того же типа проводимости, что и пластина, на поверхности вытравливаемого рельефа, покрытие поверхности рельефа изолирующим окислом и поликремнием-подложкой, удаление монокристаллического кремния для формирования изолированных областей-карманов, формирование в изолированных областях-карманах транзисторных структур методом планарной технологии, вскрытие окон, выходящих за пределы карманов, для сильнолегированных областей, смыкающихся со скрытым слоем, формирование сильнолегированных областей, формирование диэлектрика на поверхности сильнолегированных областей, вскрытие окон в диэлектрике под контакты к монокристаллическому кремнию, формирование шин металлизации к элементам микросхем и скрытому слою [2].

Однако данный способ не применим для высоковольтных схем. Диэлектрик над сильнолегированной областью, лежащей на поликремнии, пробивается при напряжениях порядка 60-105 В.

Целью изобретения является повышение надежности высоковольтных мощных микросхем за счет устранения пробоя тонкого диэлектрика между металлизированной шиной и подложкой и повышение выхода годных за счет исключения обрывов на ступеньке, образованной вытравливанием изолирующего окисла.

Цель достигается тем, что по предлагаемому способу в отличие от известных способов изготовления микросхем с диэлектрической изоляцией, включающему травление разделительных канавок на плоскопараллельной монокристаллической слаболегированной кремниевой пластине, формирование сильнолегированного скрытого слоя того же типа проводимости, что и пластина, на поверхности вытравленного рельефа, покрытие поверхности рельефа изолирующим окислом и поликремнием-подложкой, удаление монокристаллического кремния для формирования изолированных областей-карманов, формирование в изолированных областях- карманах транзисторных структур методом планарной технологии, вскрытие окон, выходящих за пределы карманов, для сильнолегированных областей, смыкающихся со скрытым слоем, формирование сильнолегированных областей, формирование диэлектрика на поверхности сильнолегированных областей, вскрытие окон в диэлектрике под контакты к монокристаллическому кремнию, формирование шин металлизации к элементам микросхем и скрытому слою, вскрытие окон в диэлектрике для сильнолегированных областей, смыкающихся со скрытым слоем, и контактных окон к этим областям проводят так, чтобы их границы не выходили за пределы изолированных областей-карманов в месте пересечения границы кармана металлизированной шиной. Если сильнолегированная область, смыкающаяся со скрытым слоем, выходит за пределы кармана в месте пересечения его металлизированной шиной с высоким потенциалом, то происходит пробой окисла над сильнолегированной областью. Возможен также обрыв металлизированной шины в месте пересечения изолирующего окисла кармана, выходящего на поверхность, так как при формировании окон под сильнолегированные области возможен растрав изолирующего окисла, что приводит к образованию ступеньки окисла.

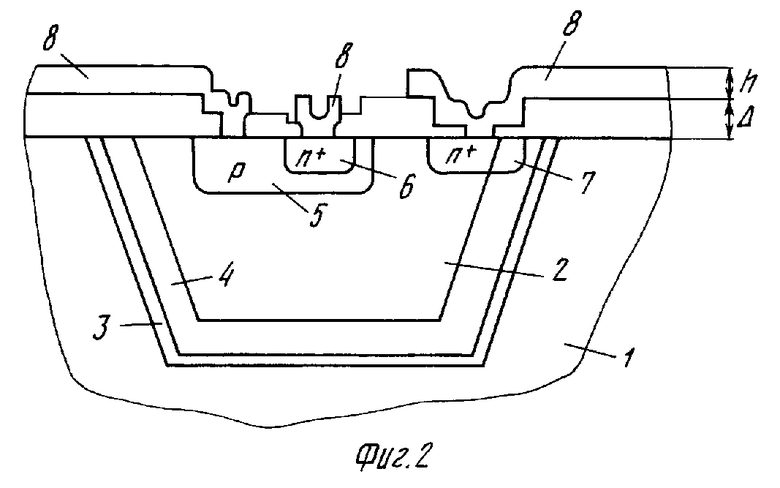

На фиг. 1 представлена топология транзистора в ИС с диэлектрической изоляцией, в котором реализован предлагаемый способ; на фиг.2 представлен разрез этого транзистора.

П р и м е р. Предлагаемый способ был опробован при изготовлении ИС в ходе ОКР Полюс-4. В подложке-поликремний 1, которая впоследствии подключается к потенциалу земли, сформированы карманы монокристаллического кремния n-типа проводимости с удельным сопротивлением 200 м см с изолирующим окислом 3 и скрытым слоем 4, выходящим на поверхность. В кармане 2 методом планарной технологии сформирована база 5. Затем методом фотолитографии вскрываются окна в окисле под область эмиттера 6 и сильнолегированную область 7, при этом должно выполняться условие

(D-d)-(3h-2,2 Δ-a) ≥ 0, где h - толщина металлизации;

Δ- - толщина окисла;

а - величина рассовмещения фотошаблонов между собой при изготовлении слоев областей 7 и 8.

Далее проводится формирование эмиттера 6 и сильнолегированной области 7 методом диффузии фосфора при Т=1060± 1оС. При этом параметры Rs=2,5-3,5 Ом/ , h21E=50-100. Во время диффузии фосфора проводится одновременно окисление. Затем проводится вскрытие окон под контакты также методом фотолитографии. Формируется металл толщиной 2 мкм с последующим созданием рисунка металлизации методом фотолитографии.

Таким образом, на фиг.1, 2 представлены структура и топология транзистора, у которого высоковольтная шина металлизации проходит над наиболее толстым окислом, обеспечивающим пробивные напряжения более 200 В, и в то же время за счет конфигурации сильнолегированной области 7 обеспечиваются низкие остаточные напряжения.

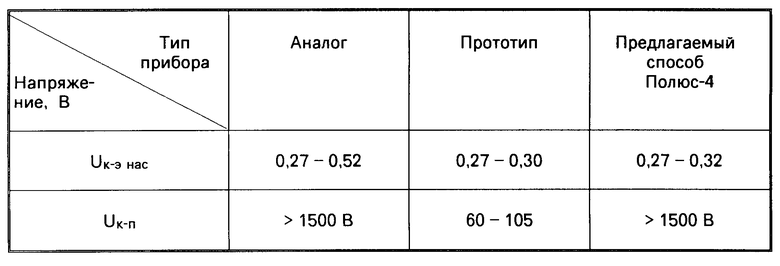

В таблице представлены значения пробивного напряжения Uк-п(коллектор-подложка, во многих случаях подложка имеет потенциал земли) аналога, прототипа и прибора, изготовленного по предлагаемой технологии, а также Uк-энас.

Как видно из таблицы, значение Uк-энас на приборе, изготовленном по предлагаемому способу, лежит в более узком диапазоне, чем на аналоге и равно Uк-энас прототипа. В то же время Uк-п на приборе, изготовленном по предлагаемому способу, равно Uк-п аналога и гораздо выше Uк-ппрототипа.

Применение предлагаемого способа изготовления высоковольтных мощных микросхем с диэлектрической изоляцией на ИС Полюс-4 позволяет повысить выход годных приборов на 5% по сравнению с базовым объектом-прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ | 1990 |

|

SU1686982A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ АВТОМАСШТАБИРУЕМОЙ БИКМОП СТРУКТУРЫ | 2003 |

|

RU2234165C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 2022 |

|

RU2783769C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1989 |

|

SU1702825A1 |

| ВЫСОКОВОЛЬТНАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1991 |

|

RU2006104C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 1995 |

|

RU2110868C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ОГРАНИЧИТЕЛЬНЫХ ДИОДОВ СВЕРХВЫСОКОЧАСТОТНОГО ДИАПАЗОНА ГРУППОВЫМ МЕТОДОМ | 2011 |

|

RU2452057C1 |

| Способ изготовления МДП-транзисторов интегральных микросхем | 1985 |

|

SU1322929A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА ВЫСОКОВОЛЬТНОГО ВЫПРЯМИТЕЛЯ | 1991 |

|

RU2006103C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ТРАНЗИСТОРОВ С ПРИПОДНЯТЫМИ ЭЛЕКТРОДАМИ | 2006 |

|

RU2329566C1 |

Использование: в микроэлектронике, технологии изготовления высоковольтных мощных микросхем с диэлектрической изоляцией. Сущность изобретения: при изготовлении микросхем с диэлектрической изоляцией на плоскопараллельной монокристаллической слаболегированной кремниевой пластине вытравливают разделительные канавки, формируют сильнолегированный скрытый слой того же типа проводимости, что и пластина, формируют изоляционный окисел, поликремниевую подложку и удаляют монокристаллический кремний для формирования изолированных карманов, формируют в изолированных карманах транзисторные структуры, вскрывают окна для сильнолегированных областей, смыкающихся со скрытым слоем, при этом выполняют условие, что их границы не выходят за пределы изолированных карманов в месте пересечения границы кармана металлизированной шиной, формируют сильнолегированные области, формируют диэлектрик на поверхности сильнолегированных областей, вскрывают окна под контакты и монокристаллическому кремнию, формируют шины металлизации. 1 табл., 2 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ, включающий травление разделительных канавок на плоскопараллельной монокристаллической слаболегированной кремниевой пластине, формирование сильнолегированного скрытого слоя того же типа проводимости, что и пластина, на поверхности вытравленного рельефа, покрытие поверхности рельефа изолирующим окислом и поликремнием-подложкой, удаление монокристаллического кремния для формирования изолированных областей-карманов, формирование в изолированных областях-карманах транзисторных структур методом планарной технологии, вскрытие окон, выходящих за пределы карманов, для сильнолегированных областей, смыкающихся со скрытым слоем, формирование сильнолегированных областей, формирование диэлектрика на поверхности сильнолегированных областей, вскрытие окон в диэлектрике под контакты к монокристаллическому кремнию, формирование шин металлизации к элементам микросхем и скрытому слою, отличающийся тем, что, с целью повышения надежности высоковольтных мощных микросхем путем устранения пробоя тонкого диэлектрика между металлизированной шиной и подложкой и повышения выхода годных за счет исключения обрывов на ступеньке, образованной вытравливанием изолирующего окисла, окна для сильнолегированных областей, смыкающихся со скрытым слоем, формируют, выполняя условие, что их границы не выходят за пределы изолированных областей-карманов в месте пересечения границы кармана металлизированной шиной.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США N 3722079, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-11-30—Публикация

1991-06-13—Подача