Изобретение относится к вычислительной технике и связи и может быть использована в многоканальных системах передачи цифровой информации.

Известен приемник мажоритарно уплотненных сигналов (МУС), осуществляющий их декодирование и разделение.

Однако этот приемник обладает, при прочих равных условиях, низкой достоверностью, поскольку даже однократная ошибка, возникающая в канале передачи МУС, приводит к появлению в процессе разделения ошибки в информационных символах.

Наиболее близким техническим решением является приемник мажоритарно уплотненных сигналов, позволяющий обнаружить любые возникающие нечетные ошибки, и содержащий N корреляторов, N решающих блоков и генератор канальных сигналов, причем первые входы корреляторов соединены с выходами генератора канальных сигналов, вторые входы корреляторов соединены между собой, а выходы корреляторов подключены к входам соответствующих решающих сигналов, кроме того, введены блок выявления ошибок и последовательно соединенные перемножитель, дополнительный коррелятор и дополнительный решающий блок, выход которого соединен с первым входом блока выявления ошибок, остальные N входов которого соединены с выходом соответствующих N решающих блоков, причем второй вход дополнительного коррелятора соединен с объединенными входами N корреляторов, а входы перемножителя соединены с выходами генератора канальных сигналов.

К недостаткам данного устройства относится невозможность корректирования обнаруженных ошибок.

Целью данного изобретения является повышение достоверности приема информации за счет исправления обнаруженных однократных ошибок.

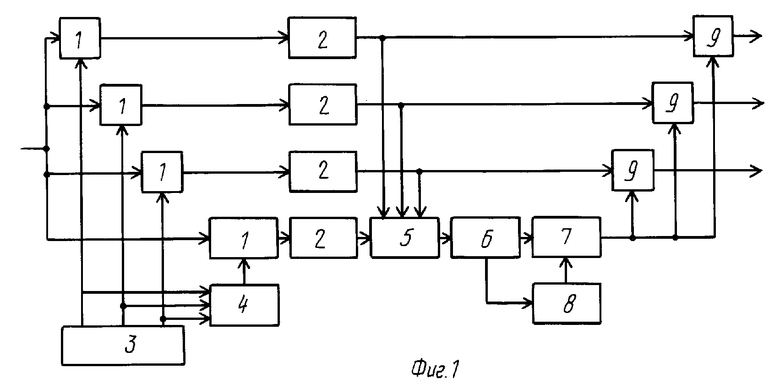

На фиг.1 показана структурная электрическая схема приемника мажоритарно уплотненных сигналов с проверкой на четность; на фиг.2 - структурная электрическая схема блока обработки.

Приемник содержит N+1 корреляторов 1, N+1 решающих блоков 2, генератор канальных сигналов 3, перемножитель 4, блок проверки на четность 5, регистр сдвига 6, ключевой элемент 7, счетчик импульсов 8, N блоков обработки 9.

Блок обработки 9 содержит накапливающий сумматор по модулю два 10, первый счетчик импульсов 11, первый ключевой элемент 12, второй счетчик импульсов 13, второй ключевой элемент 14, регистр сдвига 15 и управляемый инвертор 16.

Устройство работает следующим образом.

На передающей стороне перед операцией мажоритарного уплотнения последовательность из М информационных двоичных символов в каждом из N каналов дополняется (M+1)-ым символом проверки на четность так, чтобы сумма по модулю два всех М+1 символов была равна "0". Приемник после операции разделения каналов на каждом такте определяет наличие ошибок нечетной разности в совокупности символов, содержащихся в N каналах.

В случае наличия ошибки в каком-либо из N каналов, на выходе блока проверки на четность 5 формируется символ "1", в противном случае - символ "0".

Канал, в котором произошла ошибка, определяется в блоке обработки 9 путем проверки в каждом из N каналов совокупности из М+1 поступающих символов на четность. Там же происходит коррекция однократных ошибок.

Мажоритарно уплотненный сигнал поступает на первые входы N+1 корреляторов 1, из которых N корреляторов обрабатывают информационные символы, а (N+1)-й коррелятор является дополнительным. На вторые входы N корреляторов 1 подаются канальные сигналы с генератора канальных сигналов 3. На второй вход (N+1)-го коррелятора 1 подается сигнал, являющийся результатом перемножения канальных сигналов. Операция перемножения осуществляется в перемножителе 4. На выходе решающих блоков 2 в каждом из N+1 параллельных каналов обработки формируется символ "1", если сигнал на выходе соответствующего коррелятора 1 положительной полярности, или символ "0" в противоположном случае. В блоке 5 осуществляется суммирование по модулю два сигналов с выхода всех (N+1)-ого решающих блоков.

При наличии ошибки в нечетном числе из N информационных каналов результат суммирования будет равен "1", в случае отсутствия ошибки - "0". С выхода блока проверки на четность 5 сигнал поступает на регистр сдвига 6, осуществляющий задержку на (М+1) такт, необходимую для синхронной работы блока обработки 9. Счетчик 8 осуществляет счет поступающих символов до величины M и на (М+1)-ом также подает управляющий сигнал на второй вход ключевого элемента 7, на первый вход которого поступают сигналы с выхода регистра сдвига 6, и тем самым на (М+1)-м такте исключает сигнал из дальнейшей обработки.

В блоке обработки 9 осуществляется корреляция однократных ошибок, возникающих в мажоритарно уплотненном сигнале в процессе его передачи по каналу связи и разделении. Информационный сигнал с выхода каждого из N решающих блоков 2 поступает соответственно на первый вход обработки 9, откуда в параллельном виде он подается на вход первого 11 и второго 13 счетчиков, а также на первые входы накапливающего сумматора по модулю два 10 и ключевого элемента 12. Сумматор 10 осуществляет суммирование по модулю два блоков из М+1, поступающих на его первый вход символов, (М+1)-й из которых является проверочным символом. Результат суммирования ("1" или "0") по сигналу с выхода счетчика 11, осуществляющего счет до М+1 и по окончании выдающего управляющий сигнал на второй вход накапливающего сумматора 10, поступает первый вход 14, на торой вход которого поступает сигнал ("1" или "0") с выхода 7. Счетчик 13 осуществляет счет поступающих символов до величины М и на (М+1)-м такте подает управляющий сигнал на второй вход ключевого элемента 12, отключая на (М+1)-м такте сигнал из дальнейшей обработки. Регистр сдвига 15 осуществляет задержку на М+1 такт, необходимую для синхронной работы управляемого инвертора 16, на первый вход которого поступает задержанный сигнал с выхода регистра сдвига 15. На второй вход управляемого инвертора 16 поступает сигнал с выхода ключевого элемента 14. Если этот сигнал соответствует символу "1", то управляемый инвертор изменяет информационный символ ("1" или "0") на противоположный, тем самым осуществляя коррекцию ошибки в данном канале в данном такте. Если сигнал с выхода ключевого элемента 14 соответствует символу "0", то управляемый инвертор не меняет состояние входного сигнала в данном такте.

Таким образом, предложенный приемник мажоритарно уплотненных сигналов с проверкой на четность осуществляет определение такта, в котором произошла ошибка, определяет канал, в котором произошла ошибка, и осуществляет коррекцию однократных ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник мажоритарно-уплотненных сигналов | 1982 |

|

SU1062874A1 |

| Приемник мажоритарно-уплотненных сигналов | 1982 |

|

SU1125758A2 |

| СПОСОБ ОБРАБОТКИ И ПРИЕМНИК СООБЩЕНИЙ ЦИРКУЛЯРНЫХ ОДНОСТОРОННИХ СЕТЕЙ ПЕРЕДАЧИ ДАННЫХ С ПОВТОРЕНИЯМИ | 2016 |

|

RU2643441C2 |

| Декодер с обнаружением и исправлением ошибок | 1972 |

|

SU478446A1 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Устройство поиска псевдошумового сигнала по задержке | 1988 |

|

SU1626426A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОШУМОВОГО СИГНАЛА ПО ЗАДЕРЖКЕ | 1991 |

|

RU2017337C1 |

| Устройство для определения псевдослучайного сигнала по задержке | 1973 |

|

SU447718A1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

Изобретение относится к вычислительной технике и связи. Его использование в многоканальных системах передачи цифровой информации позволяет повысить достоверность приема информации за счет исправления обнаруженных однократных ошибок. Приемник содержит N + 1 корреляторов 1 (N - число уплотненных сигналов), N + 1 решающих блоков 2, генератор канальных сигналов 3, перемножитель 4 и блок проверки на четность 5. Благодаря введению регистра сдвига 6, ключевого элемента 7, счетчика импульсов 8 и N блоков обработки 9 в приемнике определяется такт, на котором произошла ошибка, и канал, где она произошла, после чего производится коррекция этой ошибки. 1 з.п.ф-лы, 2 ил.

| Приемник мажоритарно-уплотненных сигналов | 1982 |

|

SU1125758A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-12-15—Публикация

1990-05-24—Подача