Изобретение относится к электротехнике и может быть использовано для моделирования вольт-амперных характеристик (ВАХ) первичных источников электроэнергии, в частности солнечных батарей.

Известен вторичный источник питания, со специальной формой ВАХ [1], используемый как имитатор солнечных батарей, состоящий из ряда преобразовательных ячеек - стабилизаторов тока, соединенных по входу с выводами для подключения питания Un, а по выходу через развязывающие диоды с нагрузкой. Выходы всех преобразовательных ячеек зашунтированы транзисторами, причем базовый вывод одного транзистора соединен с выходом узла сравнения, к входным выводам которого подключены источник опорного напряжения, выход источника питания и выход включенного в цепь нагрузки датчика тока. Базовые выводы остальных транзисторов через компараторы соединены с выходом датчика тока нагрузки.

Недостатками такого источника являются низкие надежность и точность воспроизведения требуемых ВАХ из-за несовпадения значений выходных токов преобразовательных ячеек и порогов срабатывания компараторов.

Известен также вторичный источник питания [2], содержащий N ячеек - стабилизаторов тока, соединенных входами с выводами для подключения источника питающего напряжения, датчик тока нагрузки, узел сравнения опорного напряжения с суммарным значением напряжения на датчике тока и выходного напряжения, N транзисторов, N развязывающих диодов, N-1 и компараторов и N-2 сумматоров.

Недостатком этого вторичного источника питания является низкая точность воспроизведения требуемых ВАХ из-за смещения координаты крутопадающего участка ВАХ при выходе из строя ячейки - стабилизатора тока какого-либо из питающих каналов или из-за того, что в случае выхода из строя ячейки первого питающего канала развязывающий диод закрыт и линейный регулятор отключен от выходных выводов источника.

Цель изобретения - повышение точности воспроизведения ВАХ.

Цель достигается тем, что во вторичный источник питания, содержащий N ячеек - стабилизаторов тока, соединенных входами с выводами для подключения источника питающего напряжения, датчик тока нагрузки, узел сравнения опорного напряжения с суммарным значением напряжения на датчике тока и выходного напряжения, N транзисторов, N развязывающих диодов, N-1 компараторов, причем коллектор-эмиттерные цепи всех транзисторов, кроме первого, подключены параллельно выходу соответствующих ячеек - стабилизаторов тока, база первого транзистора подключена к выходу узла сравнения и базы остальных транзисторов соединены с выходами соответствующих основных компараторов, выходы ячеек - стабилизаторов тока через соответствующие развязывающие диоды соединены с выводом для подключения нагрузки, ячейки - стабилизаторы тока у всех питающих каналов, кроме N-го, снабжены информационными выходами, в качестве источника опорного напряжения второго питающего канала использован информационный выход ячейки - стабилизатора тока первого питающего канала, а источники опорного напряжения последующих питающих каналов выполнены в виде сумматоров, причем входы сумматора каждого i-го питающего канала подключены к опорному входу основного компаратора и информационному выходу ячейки - стабилизатора тока (i-1)-го питающего канала, введены N-1 компаратоpов, N-1 переключателей и источник опорного напряжения, при этом опорные входы дополнительных компараторов присоединены к дополнительному источнику опорного напряжения, во всех питающих каналах выходы основного и дополнительного компаратоpов соединены друг с другом, сигнальный вход дополнительного компаратора во всех питающих каналах соединен с переключающим контактом переключателя своего питающего канала, размыкающий контакт которого соединен с общей шиной, а замыкающий - с опорным входом основного компаратора своего питающего канала, кроме того, в первом питающем канале выход ячейки - стабилизатора тока соединен с цепью коллектор-эмиттер транзистора через развязывающий диод.

Сопоставительный анализ заявляемого решения и прототипа показывает, что в первое введены дополнительные N-1 компараторов, N-1 переключателей, а также источник опорного напряжения, при этом опорные входы дополнительных компараторов присоединены к дополнительному источнику опорного напряжения, во всех питающих каналах выходы основного и дополнительного компараторов соединены друг с другом, сигнальный вход дополнительного компаратора во всех питающих каналах соединен с переключающим контактом переключателя своего питающего канала, размыкающий контакт которого соединен с общей шиной, а замыкающий - с опорным входом основного компаратора своего питающего канала, кроме того, в первом питающем канале выход ячейки - стабилизатора тока соединен с цепью коллектор-эмиттер транзистора через развязывающий диод. Таким образом, заявляемое техническое решение соответствует критерию "новизна".

Совокупность известных и введенных элементов и их связей обусловили новое свойство: если для формирования крутопадающего участка ВАХ источника требуется количество питающих каналов М, меньшее общего количества питающих каналов N, то остальные S = N-M питающих каналов могут быть использованы в качестве резервных, подключаемых к выходу источника вместо вышедших из строя основных питающих каналов. В случае выхода из строя ячейки - стабилизатора тока в первом питающем канале закрывается развязывающий диод, который отключает неисправную ячейку - стабилизатор тока от выхода источника. Линейный регулятор при этом не отключается и обеспечивает требуемое изменение ВАХ источника. В результате исключаются режим, когда происходит смещение координаты крутопадающего участка ВАХ источника из точки Iн = М ˙ Iя, так как число М рабочих питающих каналов поддерживается неизменным, и режим, когда линейный регулятор отключен от выходных выводов источника, выходное напряжение источника не регулируется и определяется выходным напряжением исправных питающих каналов.

Таким образом, в заявляемом источнике обеспечивается достижение положительного эффекта, заключающегося в повышении точности воспроизведения требуемых ВАХ путем устранения смещения координаты тока Iн крутопадающего участка из точки М ˙ Iя и устранении режима, когда происходит нерегулируемое изменение выходного напряжения источника. Это позволяет сделать вывод о соответствии предлагаемого технического решения критерию "существенные отличия".

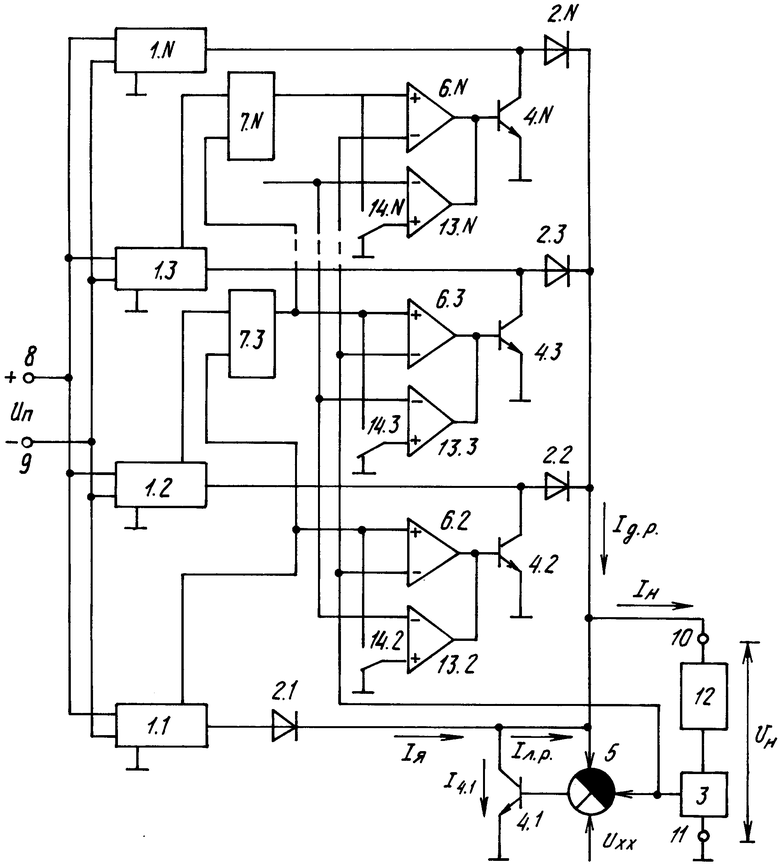

На чертеже представлена структурная схема заявляемого источника питания.

Вторичный источник питания содержит ячейки 1.1-1.N - импульсные стабилизаторы тока, снабженные информационными выходами (с индивидуальных датчиков тока), развязывающие диоды 2.1-2.N, датчик 3 тока нагрузки, транзисторы 4.1-4. N и узел 5 сравнения. В первом питающем канале компараторы 6.1, 13.1 и переключатель 14.1 не использованы, а в остальных питающих каналах применены компараторы 6.2-6.N, 13.2-13.N и переключатели 14.2-14.N. В первом и втором питающих каналах установка сумматоров 7.1 и 7.2 не является необходимой, а в остальные питающие каналы введены сумматора 7.3-7.N. На схеме отмечены также выводы 8 и 9 для подключения первичного источника питания, выводы 10 и 11 для подключения нагрузки 12 и источники опорного напряжения Uхх и Uоn.

Опорный вход в компараторах 6.2-6.N и сигнальный вход в компараторах 13.2-13. N являются инвентиpующими, сигнальный вход в компараторах. 6.2-6.N и опорный вход в компараторах 13.2-13. N - инвентирующими. Компараторы 6.2-6. N и 13.2-13.N попарно объединены, а их выходные сигналы совмещаются на общем выходе по логике ИЛИ. В качестве объединенных компараторов могут быть использованы микросхемы 521СА1 (Шило В.Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. М.: Советское радио, 1979, с. 220-221).

Ячейки 1.1-1.N включены параллельно через развязывающие диоды 2.1-2.N и датчик 3 тока нагрузки между выводами 8 и 9 для подключения первичного источника питания и выводами 10 и 11 для подключения нагрузки. Выходы ячеек 1.1-1.N зашунтированы транзисторами 4.1-4.N. Входы узла 5 сравнения подключены к выходам источника опорного напряжения Uхх, датчика 3 тока нагрузки и общему потенциальному выходу источника (после развязывающих диодов 2.1-2. N), а выход - к базовой цепи транзистора 4.1.

Сигнальные входы компараторов 6.2-6. N соединены с выходом датчика 3 тока нагрузки. Объединенные опорный вход компаратора 6.2 и замыкающий контакт переключателя 14.2 соединены с информационным входом ячейки 1.1, а объединенные опорный вход каждого компаратора 6.i и замыкающий контакт каждого переключателя 14.i из совокупности остальных компараторов и переключателей через сумматор 7.i подключены к опорному входу компаратора 6.(i-1) и информационному выходу ячейки 1.(i-1).

Опорные входы компараторов 13.2-13.N объединены и подключены к источнику опорного напряжения Uоп. Сигнальные входы компараторов 13.2-13.N соединены с переключающими контактами переключателей 14.2-14.N, размыкающие контакты которых подключены к общей шине. Выходы компараторов 6.2-6.N и 13.2-13.N соединены между собой и присоединены к базовым цепям соответствующих транзисторов 4.2-4.N.

Источник питания работает следующим образом.

При подаче входного питающего напряжения Uп каждая из ячеек 1.1-1.N обеспечивает стабилизацию своего выходного тока на уровне Iя. Подключение ячеек 1.2-1.N к нагрузке осуществляется диодно-транзисторными коммутаторами, состоящими из диодов 2.2-2.N и транзисторов 4.2-4.N. Сигнал управления транзистором 4.1 подается с выхода узла 5 сравнения, транзисторами 4.2-4.N - с выходов компараторов 6.2-6.N и 13.2-13.N. В зависимости от состояния компараторов 6.2-6. N и 13.2-13. N транзисторы 4.2-4.N находятся либо в открытом, либо в закрытом состоянии. Соответственно ячейки 1.2-1.N работает либо в режиме короткого замыкания, когда токи в нагрузку 12 не поступают, либо в режиме передачи энергии в нагрузку.

Напряжения, пропорциональные выходным токам ячеек 1.1-1.N снимаются с информационных выходов указанных ячеек и подаются на входы сумматоров 7.3-7. N. Порог срабатывания Uв.i компаратора 6.i определяется выходным напряжением сумматора 7.i и пропорционален сумме выходных токов всех предыдущих ячеек:

U6.i = (i-1)КIя, (1) где К - коэффициент пропорциональности.

Пороги срабатывания компараторов 6.2-6.N находятся в соотношении

U6.2 < U6.3 < ...< U6.N. (2)

Пороги срабатывания компараторов 13.2-13.N определяются напряжением Uоп и выбираются в пределах

(M-1)IяK < Uоп < (М)IяК, (3) а напряжения U13.i, подаваемые на сигнальные входы компараторов 13.2-13.N, определяются выражением

U13.i = (i-1)IяК > Uoп, (4) если сигнальные входы этих компараторов через переключатели 14.2-14. N объединены с опорными входами компараторов 6.2-6.N, или равно нулю, если эти входы через переключатели 14.2-14.N закорочены на общую шину.

На выходе компараторов 6.2-6.N устанавливается логическая "1", если напряжение на их сигнальном входе меньше напряжения на опорном входе, логический "0", если напряжение на их сигнальном входе равно или больше напряжения на опорном входе. На выходе компараторов 13.2-13.N устанавливается логический "0", если их сигнальные входы через переключатели 14.2-14.N подключены к общей шине, если их сигнальные входы через переключатели 14.2-14. N подключены к опорным входам компараторов 6.2-6.N и напряжения U13.i на этих входах меньше Uоп. На выходе компараторов 13.2-13.N устанавливается логическая "1", если их сигнальные входы через переключатели 14.2-14.N подключены к опорным входам компараторов 6.2-6.N и напряжения U13.i на этих входах больше Uоп.

Исходное состояние схемы. На выходе компараторов 6.2-6.N напряжение соответствует логической "1". Переключающие контакты переключателей 14.2-14.М замкнуты с размыкающими контактами и на выходах компараторов 13.2-13.М напряжение соответствует логическому "0". Переключающие контакты остальных переключателей 14. (М+1)-14. (М+S) замкнуты с замыкающими контактами и на выходах компараторов 13.(М+1)-13.(М+S) напряжение соответствует логической "1". На базах транзисторов 4.2-4.N напряжения соответствуют логической "1" и транзисторы 4.2-4.N открыты.

Пока ток нагрузки Iн< Iя напряжение U3 на выходе датчика 3 тока нагрузки меньше порога срабатывания компаратора 6.2, все компараторы 6.2-6.N, 13.2-13. N, транзисторы 4.2-4.N находятся в исходном состоянии. Требуемое выходное напряжение источника питания

Uн = Uхх - IнК3 (5) обеспечивается линейным регулятором напряжения, состоящим из транзистора 4.1 ячейки 1.1, узла 5 сравнения и источника опорного напряжения Uхх К3 - коэффициент передачи датчика 3 тока нагрузки.

В режиме холостого хода (при Iн = 0) выходное напряжение источника питания Uн = Uхх. По мере роста тока Iн транзистор 4.1 закрывается и согласно выражению (5) напряжение Uн линейно уменьшается. При токе Iн = Iя транзистор 4.1 закрывается, в нагрузку 12 поступает весь выходной ток ячейки 1.1, напряжение Uн равно Uхх - IяК3, а напряжение на выходе датчика 3 тока нагрузки достигает порога срабатывания компаратора 6.2.

При срабатывании компаратора 6.2 напряжение на базе транзистора 4.2 становится равным напряжению логического "0" и транзистор 4.2 закрывается. Закрывание транзистора 4.2 вызывает скачкообразное увеличение тока Iн нагрузки, что приводит к открыванию транзистора 4.1 и уменьшению до нуля выходного тока Iл.р. линейного регулятора. Выходное напряжение Uн и выходной ток Iн источника остаются при этом равными соответственно Uхх-IяК3 и Iя.

Дальнейшее уменьшение сопротивления Rн нагрузки и соответственное увеличение тока Iн сопровождается линейным уменьшением напряжения Uн согласно выражению (5). При токе Iн=2Iя выходное напряжение датчика 3 тока нагрузки становится равным порогу срабатывания компаратора 6.3. В этот момент напряжение на базе транзистора 4.3. становится равным напряжению логического "0". Транзистор 4.3 закрывается, к выходу источника подключаются ячейки 1.1-1.3 и ток Iн скачком увеличивается до величины 3Iя. Открывается транзистор 4.1, ток Iн уменьшается до требуемого значения 2Iя, а напряжение Uн равно Uхх-2IяК3.

Дальнейшее увеличение тока Iн вызывает поочередное срабатывание компараторов 6.4-6. М, закрывание транзисторов 4.4-4.М и подключение к выходу источника питания ячеек 1.4-1.М. При токе Iн, равном (М-1)Iя, срабатывает компаратор 6. М, ячейка 1.М переводится в режим отдачи энергии в нагрузку 12, а увеличение тока Iн до величины М ˙ Iя происходит за счет уменьшения тока I4.1.

При токе Iн=МIя достигается порог срабатывания компаратора 6.(М+1). Но состояние транзистора 4.(М+1) при этом не изменяется, так как напряжение на выходе компаратора 13.(М+1) соответствует логической "1".

Таким образом, при токе Iн=МIя к выходу источника питания подключены ячейки 1.1-1. М, ток I4.1 равен нулю и уменьшение напряжения Uн при дальнейшем уменьшении сопротивления Rн нагрузки происходит при постоянном токе Iн согласно выражению

Uн = Rн ˙ МIя

На выходе источника питания формируется приближенная ВАХ солнечной батареи с координатами: напряжение холостого хода Uхх, ток короткого замыкания М ˙ Iя.

По мере увеличения сопротивления Rн и уменьшения тока Iн происходит постепенное отключение ячеек 1.1-1.М от выхода источника вторичного электропитания.

Из сказанного следует, что ток Iл.р. регулируется так, чтобы всегда выполнялось условие (5), а изменение тока Iд.р. производится таким образом, чтобы ток I4.1 не превышал величины Iя.

В случае выхода из строя одной из ячеек 1.1-1.М их суммарный выходной ток Iн уменьшается на величину выходного тока Iя этой ячейки. Работает источник питания в этом случае следующим образом.

При выходе из строя, например, ячейки 1.i ее выходной ток становится равным нулю. Напряжение на сигнальных входах компараторов 13.(М+1)-13.(М+S) и пороги срабатывания компараторов 6. (i+1)-6.N уменьшаются при этом на величину, пропорциональную Iя. Напряжение U13.(М+1) на сигнальном входе компаратора 13.(М+1), равное согласно выражению (4) М ˙ IяК, уменьшается в этом случае до величины (М-1) ˙ IяК и становится меньше порога срабатывания Uоп компаратора 13. (М+1), задаваемого согласно выражению (3). Компаратор 13. (М+1) переходит в состояние, когда на его выходе устанавливается напряжение, соответствующее логическому "0".

По достижении током Iн величины (i-1)Iя срабатывают сразу два компаратора: 6. i и 6.(i+1). Срабатывание компаратора 6.i и закрывание транзистора 4.i не может привести к изменению выходного тока Iд.р. дискретного регулятора (выходной ток ячейки 1.i равен нулю, а при срабатывании компаратора 6. (i+1) и закрывании транзистора 4.(i+1) ток Iд.р. увеличивается от (i-1)Iя до значения iIя.

Поочередное срабатывание остальных компараторов 6.(i+2)-6.М и закрывание транзисторов 4.(i+2)-4.М приводит к увеличению тока Iд.р. до значения (М-2)Iя, когда к выходу источника подключены все рабочие из основных ячеек 1.1-1. М. При этом достигнут порог срабатывания компаратора 6.(М+1), а напряжение на совмещенных выходах компараторов 6.(М+1) и 13.(М+1) соответствует логическому "0". Транзистор 4.(М+1) закрывается, к выходу источника подключается резервная ячейка 1.(М+1) и выходной ток дискретного регулятора увеличивается до (М-1)Iя.

Выход из строя двух из ячеек 1.1-1.М вызывает изменение состояния компараторов 13.(М+1) и 13.(М+2), а по мере достижения током Iн значений (М-3) и (М-2)Iя, соответствующих в этом случае порогам срабатывания компараторов 13. (М+1) и 13.(М+2), к выходу источника подключаются резервная ячейка 1. (М+1), а затем резервная ячейка 1.(М+2).

Дальнейший выход из строя основных ячеек 1.1-1.М вызывает подключение соответствующего числа резервных ячеек 1.(М+1) - 1.(М+S). При этом максимальный суммарный выходной ток Iн источника остается неизменным и равен МIя.

В случае выхода из строя ячейки - стабилизатора тока 1.1 уменьшаются до нуля ее выходной ток и опорные сигналы компараторов 6.2-6.N. С помощью развязывающего диода 2.1 неисправная ячейка 1.1 отключается от линейного регулятора, вместо нее подключается ячейка 1.2, а линейный регулятор обеспечивает требуемое изменение ВАХ источника.

Введение источника опорного напряжения, N-1 компаратоpов и N-1 переключателей позволяет часть питающих каналов, не задействованных в формировании ВАХ источников, использовать в качестве резервных питающих каналов, подключать их к выходу источника в случае нарушения нормального режима работы основных питающих каналов и исключить подключение резервных питающих каналов к выходу источника в случае нормального режима работы основных. Это позволяет исключить ошибку воспроизведения требуемой ВАХ, связанную с изменение координаты ее крутопадающего участка.

Включение в первом питающем канале развязывающего диода анода к выходу ячейки - стабилизатора тока, а катодом к коллектору транзистора позволяет в случае выхода из строя первой ячейки отключить ее от выхода источника, не отключая линейный регулятор и сохраняя тем самым возможность регулировать ВАХ источника по требуемому закону.

Преимущество заявляемого технического решения по сравнению с прототипом состоит в повышении точности воспроизведения вторичным источником питания требуемых ВАХ, а именно исключается ошибка воспроизведения ВАХ, вызванная выходом из строя ячеек 1.1-1.М.

Исключение ошибки воспроизведения ВАХ источника, вызванной нарушением нормального режима работы питающих каналов при выходе их строя ячеек 1.1-1. М, достигается тем, что часть не задействованных в формировании ВАХ источника ячеек 1.(М+1)-1.(М+S) с помощью введенных переключателей и компараторов может быть подключена к выходу источника взамен вышедших из строя, а изменение места включения развязывающего диода 2.1 позволяет отключать неисправную ячейку 1.1, оставляя включенным линейный регулятор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный источник напряжения | 1987 |

|

SU1476449A1 |

| Стабилизированный преобразователь переменного напряжения в постоянное | 1980 |

|

SU1005240A2 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО РЕГУЛИРУЕМОГО ТОКА | 1991 |

|

RU2010305C1 |

| Импульсный резервированный стабилизатор напряжения | 1983 |

|

SU1086501A1 |

| Многоканальный стабилизированный источник вторичного электропитания | 1984 |

|

SU1166085A1 |

| Вторичный источник питания | 1979 |

|

SU828184A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО РЕГУЛИРУЕМОГО ТОКА | 1991 |

|

RU2010304C1 |

| УСТРОЙСТВО СОЗДАНИЯ ПРЕДНАМЕРЕННЫХ ПОМЕХ ГЛОБАЛЬНЫМ НАВИГАЦИОННЫМ СПУТНИКОВЫМ СИСТЕМАМ | 2024 |

|

RU2828474C1 |

| Имитатор солнечной батареи | 1980 |

|

SU868924A1 |

| СПОСОБ СНИЖЕНИЯ ЭНЕРГОПОТРЕБЛЕНИЯ В N-МЕРНОЙ КОНТЕКСТНО-АДРЕСУЕМОЙ ПАМЯТИ | 2010 |

|

RU2453935C1 |

Использование: для моделирования вольт-амперных характеристик (ВАХ) первичных источников электроэнергии, в частности солнечных батарей. Сущность изобретения: позволяет повысить точность воспроизведения источником требуемых ВАХ, а именно исключается ошибка воспроизведения ВАХ, вызванная выходом из строя преобразовательных ячеек (ПЯ). Источник состоит из N питающих каналов (ПК), включенных параллельно между входными и выходными выводами. Первый ПК включает в себя ПЯ, шунтирующий транзистор (ШТ) и развязывающий диод (РД). Второй ПК включает в себя ПЯ, ШТ, РД, два компаратора и переключатель (П), а в состав остальных ПК добавлен сумматор. Для воспроизведения требуемых ВАХ используется M ПК, причем первый ПК обеспечивает линейное регулирование своего выходного тока (ВТ), а ПК от второго до M-го обеспечивают дискретное регулирование своего суммарного ВТ. Остальные (N-M) ПК используются в качестве резервных. Выбор основного или резервного режима работы ПК осуществляются с помощью П. В случае выхода из строя одной или нескольких ПЯ взамен неисправных ПК подключается соответствующее число ПК из числа резервных. Для исключения подключения резервных ПК в случае нормального режима работы основных ПК компараторы совмещены по выходу по логике ИЛИ. 1 ил.

ВТОРИЧНЫЙ ИСТОЧНИК ПИТАНИЯ, содержащий N ячеек-стабилизаторов тока, соединенных входами с выводами для подключения источника питающего напряжения, датчик тока нагрузки, узел сравнения опорного напряжения с суммарным значением напряжения на датчике тока и выходного напряжения, N транзисторов, N развязывающих диодов, N - 1 компараторов, причем цепи коллектор - эмиттер всех транзисторов, кроме первого, подключены параллельно выходу соответствующих ячеек-стабилизаторов тока, база первого транзистора подключена к выходу узла сравнения, а базы остальных транзисторов соединены с выходами соответствующего основного компараторов, выходы ячеек-стабилизаторов тока через соответствующие развязывающие диоды соединены с выводом для подключения нагрузки, ячейки-стабилизаторы тока всех питающих каналов, кроме I-го, снабжены информационными выходами, в качестве источника опорного напряжения второго питающего канала использован информационный выход ячейки-стабилизатора тока первого питающего канала, а источники опорного напряжения последующих питающих каналов выполнены в виде сумматоров, причем входы сумматоры каждого i-го питающего канала подключены к опорному входу основного компаратора и информационному выходу ячейки-стабилизатора тока (i - 1)-го питающего канала, отличающийся тем, что, с целью повышения точности воспроизведения вольтамперных характеристик, в него введены дополнительные N - 1 компараторов, а также источник опорного напряжения и N - 1 переключателей, при этом опорные входы дополнительных компараторов присоединены к источнику опорного напряжения, во всех питающих каналах выходы основного и дополнительного компараторов соединены друг с другом, сигнальный вход дополнительного компаратора во всех питающих каналах соединен с переключающим контактом переключателя своего питающего канала, размыкающий контакт которого соединен с общей шиной, а замыкающий - с опорным входом основного компаратора своего питающего канала, кроме того, в первом питающем канале выход первой ячейки-стабилизатора тока соединен с цепью коллектор - эмиттер первого транзистора через первый развязывающий диод.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 1579277, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1995-01-20—Публикация

1991-01-03—Подача