Изобретение относится к средствам обработки и передачи сигналов там, где требуется линейное интерполирование сигналов при повышенном быстродействии или при работе в реальном масштабе времени, например телеметрии, в автоматике, связи и т.д.

Известно устройство, выполняющее линейную интерполяцию, содержащее тактовый генератор, двоичный счетчик, регистр хранения, сумматор. В известном устройстве процесс интерполирования состоит из многократно повторяющейся операции суммирования постоянного приращения к накапливаемой сумме (частичные суммы - интерполированные значения процесса). Цепная операция суммирования вызывает накопление ошибки интерполирования.

Наиболее близким по технической сущности к предлагаемому устройству является линейный интерполятор, содержащий регистр, сумматоры, коммутатор, дешифраторы, тактовый генератор, двоичный счетчик и блок управления. Известный линейный интерполятор лишен недостатков устройства интерполирования, но требует повышенных затрат оборудования в случае, если требуется интерполировать больше семи значений между опорными отсчетами. В этом случае приходится включать последовательно несколько интерполяторов, что не всегда допустимо.

Цель изобретения - расширение функциональных возможностей.

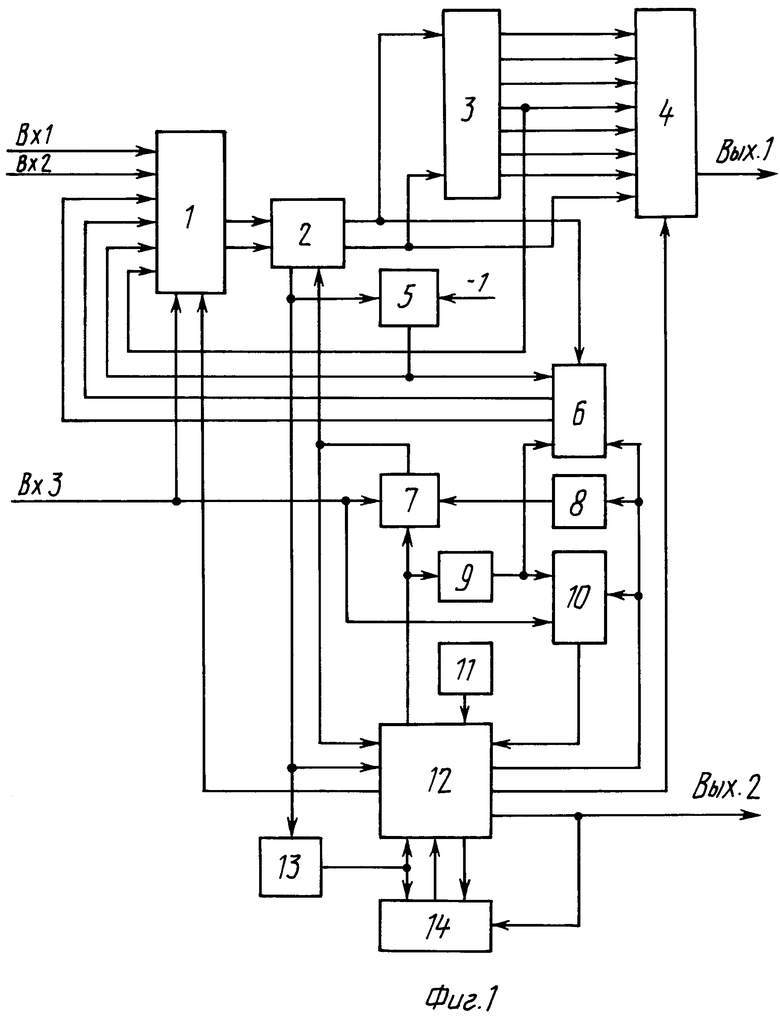

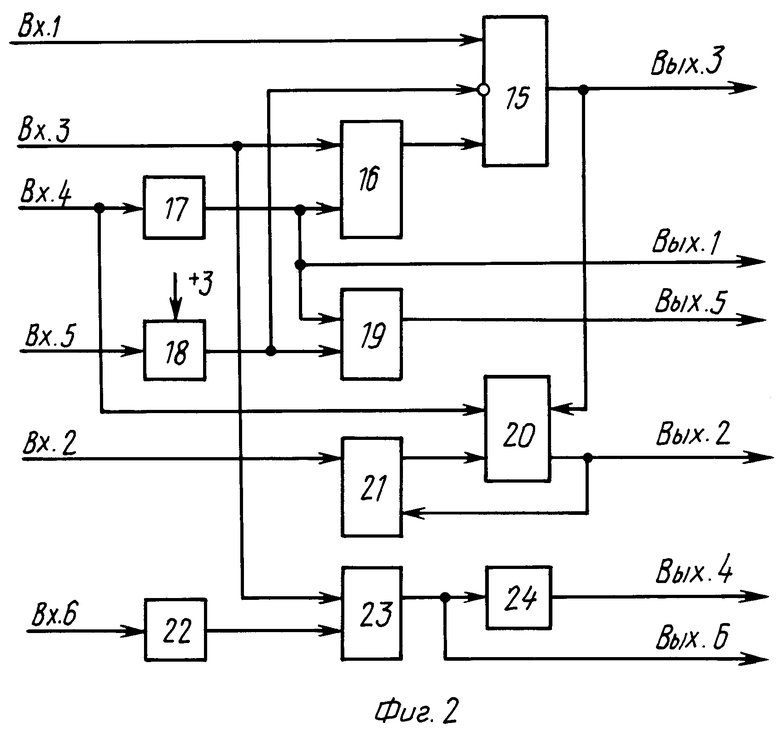

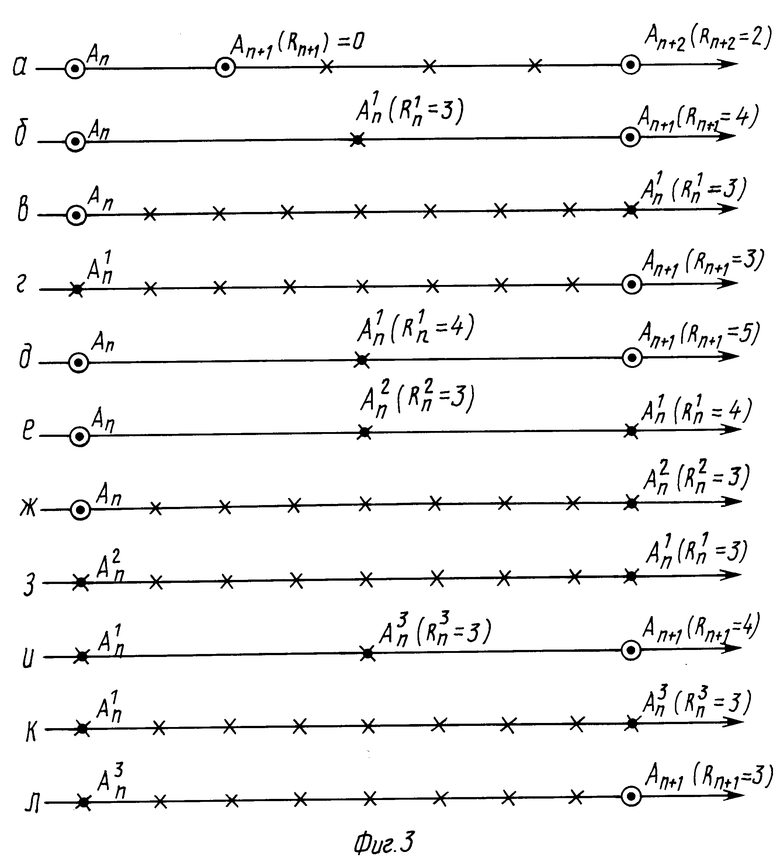

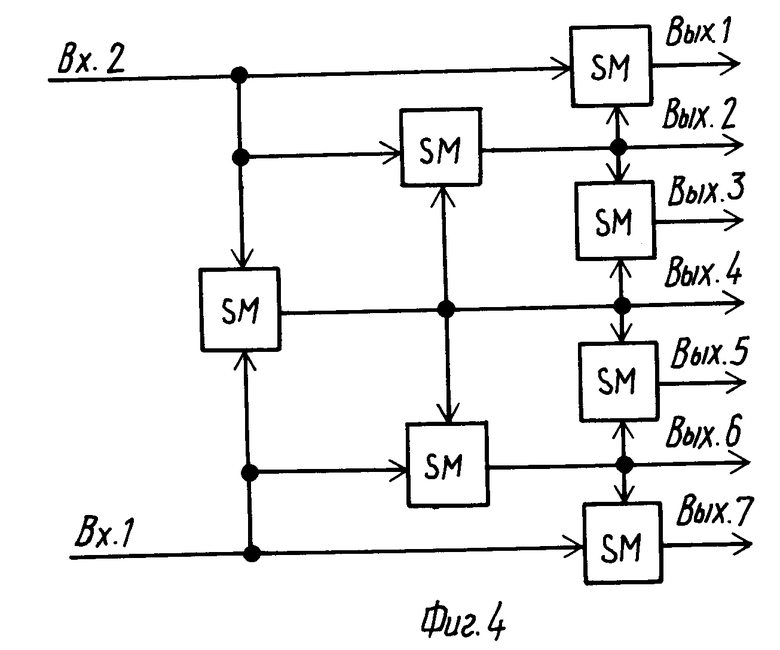

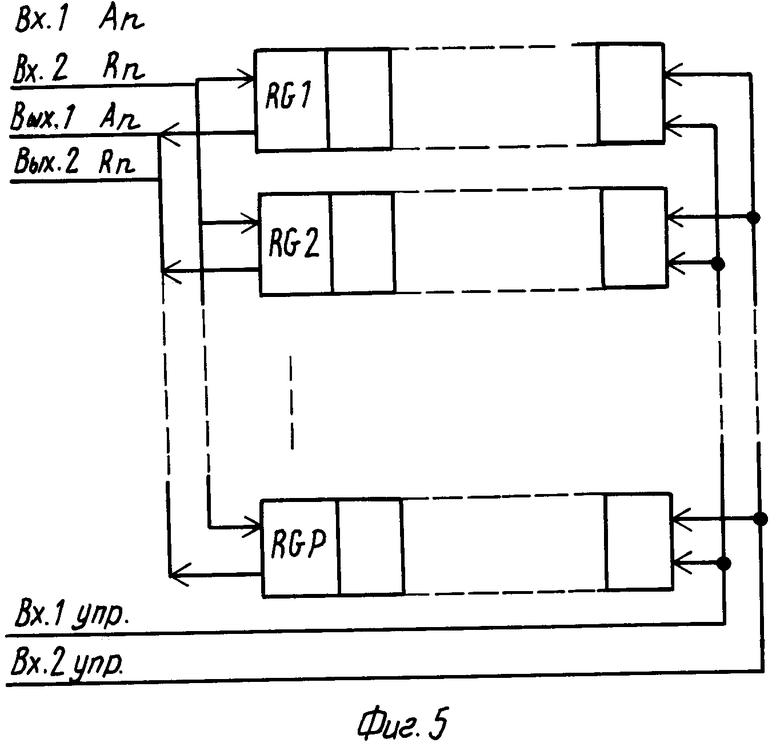

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока управления; на фиг. 3 - временная диаграмма работы интерполятора; на фиг. 4,5 - примеры структурных схем соответственно блока регистров, блока сумматоров и блока стековой памяти.

На фиг. 3 используются обозначения:

⊙ - отсчеты данных входного процесса (An, Rn)

х - интерполированные вспомогательные опорные значения процесса (Anj, Rnj)

Х - интерполированные значения процесса на выходе устройства ( );

);

Rn - ранг входных отсчетов An и вспомогательных Anj, определяющий число интерполированных значений An,k.

Устройство (фиг.1) содержит коммутатор 1, блок 2 регистров, блок 3 сумматоров, коммутатор 4, дешифратор 5, блок 6 стековой памяти, элемент ИЛИ 7, два элемента задержки 8 и 9, счетчик 10, тактовый генератор 11, блок управления 12, дешифратор 13, счетчик 14. Первым и вторым информационными входами устройства являются соответственно пятый и шестой информационные входы коммутатора 1. Входом управления устройства являются объединенные вместе второй адресный вход коммутатора 1, третий вход элемента ИЛИ 7 и третий вход двоичного счетчика 10. Информационным выходом устройства является выход коммутатора 4, а выходом управления устройства является третий выход блока управления 12.

Блок управления 12 (фиг.2) содержит элемент И 15, триггер 16, элемент 17 задержки, элемент 18 сравнения, элемент И 19, регистр 20, сумматор 21, дешифратор 22, элемент И 23 и элемент 24 задержки. Первым и вторым входами блока управления являются соответственно первый вход элемента И 15 и второй вход сумматора 21. Вход "Установка" триггера 16 соединен с первым входом элемента И 23 и является третьим входом блока управления. Четвертый вход блока управления заведен на вход элемента 17 задержки и вход "сброс" регистра 20. Пятым и шестым входами блока управления являются соответственно вход элемента 18 сравнения и вход дешифратора 22. Первым, вторым и третьим выходами блока управления являются соответственно выход элемента 17 задержки, выход регистра 20 и выход элемента И 15. Четвертым и пятым выходами блока управления являются соответственно выходы элемента И 24 задержки элемента И 19. Шестым выходом блока управления является выход элемента И 23.

Блок управления работает следующим образом. По сигналу, поступившему на четвертый вход блока управления, через время τ(элемент задержки 17) включается триггер 16. Сигнал с выхода элемента задержки 17 поступает также на первый выход блока управления и служит целям начальной установки отдельных элементов интерполятора. Сигнал с четвертого входа блока управления, кроме того, устанавливает в нулевое положение регистр 20. Потенциал с выхода триггера 16 (сигнал "Пуск") поступает на вход элемента И 15, на другой вход данного элемента поступают сигналы от тактового генератора (через первый вход блока управления). Элемент сравнения 18 анализирует значение кода ранга Rn, поступающее через пятый вход блока управления. Если значение ранга R≅3, то потенциал с выхода элемента сравнения 18 разрешает (при наличии потенциала с выхода триггера 16) прохождение импульсов с первого входа блока управления на третий выход блока управления. Эти импульсы стробируют данные с выхода интерполятора (отсчеты An и  ). В этом случае выполняется процесс интерполяции.

). В этом случае выполняется процесс интерполяции.

Если же R>3, то в данном случае блок управления запрещает процесс передачи данных на выход (отсчетов Аn и  ), так как отсутствует необходимый потенциал на выходе элемента сравнения 18. Но обеспечивается потенциал разрешения на элемент И 19, что разрешает прохождение сигнала с выхода элемента 17 задержки на пятый выход блока управления. По этому сигналу в интерполяторе выполняются следующие операции:

), так как отсутствует необходимый потенциал на выходе элемента сравнения 18. Но обеспечивается потенциал разрешения на элемент И 19, что разрешает прохождение сигнала с выхода элемента 17 задержки на пятый выход блока управления. По этому сигналу в интерполяторе выполняются следующие операции:

- запись в блок стековой памяти последнего опорного отсчета An или Anj;

- увеличение на единицу значение признака заполнения стека;

- запись вспомогательного опорного отсчета Anj+1 в блок 2 регистров интерполятора.

Сумматор 21 и регистр 20 блока управления формируют последовательный список адресов, который поступает через второй выход блока управления 12 на адресный вход коммутатора 4 интерполятора. В начальный момент значение кода на выходе регистра 20 равно нулю (сброс по сигналу с четвертого входа блока управления), а на входе сумматора (второго входа блока управления) установлен код приращения. По сигналу с выхода элемента И 15 код с выхода сумматора 21 заносится в регистр 20. Код с выхода регистра 20 поступает на второй вход сумматора 21, поэтому на выходе регистра 20 на каждом такте появляется предыдущий код, увеличенный на приращение, установленное на втором входе блока управления.

Триггер 16 блока 12 приводится в начальное состояние по сигналу с третьего входа блока управления. По этому же сигналу элемент И 23 формирует на своем выходе сигнал в зависимости от потенциала на выходе дешифратора 22. Потенциал на выходе дешифратора 22 зависит от кода, установленного на шестом входе блока управления. Если на шестом входе блока управления нулевое значение, то нет активных сигналов на выходе элементов 23 и 24. Если же на шестом входе блока управления установлен код не равный нулю, то активный сигнал с выхода элемента И 23 поступает на шестой выход блока управления, а через время (элемент 24 задержки) появляется и на четвертом выходе блока управления.

Таким образом, блок управления (фиг.2) формирует набор сигналов для обеспечения следующих режимов:

- интерполяцию и передачу на выход интерполятора отсчетов данных Anи  ;

;

- интерполяцию вспомогательного опорного отсчета Anj+1 (конечное значение текущего интервала интерполяции) и запоминание в блоке стековой памяти предыдущего конечного значения интервала интерполяции An или Anj;

- чтение из блока стековой памяти очередного конечного значения интервала интерполяции An или Anj.

На фиг. 3 приведена временная диаграмма работы интерполятора под управлением блока управления. Временная диаграмма иллюстрирует все упомянутые выше режимы работы блока управления 12.

Блок 2 регистров выполняет функцию временного хранения отсчетов (начального и конечного) значений концов интервала интерполяции и значения ранга, соответствующего конечному значению отсчета интервала интерполяции. Блок 2 регистров состоит из 3 регистров. Причем два регистра включены последовательно по информационным входам, а входы управления записью всех регистров объединены. Такое включение обеспечивает выполнение блоком регистров функций, указанных выше. При этом запись очередной пары отсчетов приводит к следующему. Значение кода из одного регистра перемещается в другой регистр. В третьем регистре хранится значение ранга. Процесс интерполяции выполняется между отсчетами данных, хранящимися в двух регистрах, а число интерполированных значений указывает параметр, находящийся в третьем регистре. Необходимое число N интерполированных значений  определяется выражением N=2Rn-1.

определяется выражением N=2Rn-1.

Блок 3 сумматоров (фиг.1) выполняет операцию интерполяции между двумя значениями отсчетов входного процесса, находящимися в блоке 2 регистров. Блок 3 сумматоров вычисляет (интерполирует) всегда семь значений независимо от каких-либо условий. Схема блока сумматоров 3 комбинационная, поэтому достаточно установить значения кодов на входах блока сумматоров и через время прохождения сигналов через сумматоры на всех семи выходах блока сумматоров находятся интерполированные значения, принадлежащих прямой, заданной своими конечными значениями (первый и второй выходы блока 2 регистров интерполятора). Схема блока сумматоpов очевидна, каждый сумматор вычисляет среднее арифметическое кодов, установленных на его входах.

Блок 6 стековой памяти предназначен для временного хранения конечных значений текущих интервалов интерполяции и их выдачи в случае необходимости. Блок 4 стековой памяти состоит из набора однотипных регистров сдвига, которые управляются параллельно (соответствующие цепи управления всех регистров объединены между собой). Одноименные разряды регистров образуют числовую линейку, предназначенную для хранения конечного значения отсчета данных интервала интерполяции и соответствующего ему значения ранга. Информационные коды заносятся в блок стековой памяти через последовательные информационные входы регистров сдвига. При сдвиге вправо блока регистров информация заносится в него, а при сдвиге влево выталкивается из него.

Интерполятор (фиг.1) начинает работать немедленно при записи очередного отсчета данных в блок 2 (конечное значение текущего интервала интерполяции). Отсчеты данных состоят собственно из значения An и кода ранга Rn (ранг указывает количество интерполированных значений, которое требуется вычислить на текущем интервале интерполяции). Отсчеты данных могут поступать либо от внешнего источника, либо от элементов схемы устройства (выбор источника определяется коммутатором 1). После записи отсчета данных интерполятор переходит из двух режимов работы:

- если на интервале интерполяции требуется интерполировать не более семи значений, то начальное значение интервала и интерполированные значения через коммутатор 4 передаются на первый выход устройства в сопровождении сигналов стробирования со второго выхода устройства;

- если на интервале интерполяции требуется интерполировать более семи значений, то в этом случае конечное значение интервала интерполяции из блока 2 регистров и значение Rn-1) с выхода дешифратора 5 заносятся в блок 6 стековой памяти, увеличивая при этом значение указателя стека (счетчик 10) на единицу, а в блок 2 заносится вспомогательное конечное значение интервала интерполяции (интервал интерполяции уменьшается в два раза) и значение (Rn-1) с выхода дешифратора 5.

После окончания работы в первом режиме блок 12 управления опрашивает значение указателя стека (код с выхода счетчика 10). Если указатель равен нулю, то в этом случае устройство переходит в режим ожидания данных от внешнего источника. Если указатель не равен нулю, то в этом случае блок 12 управления обеспечивает чтение из блока 6 стековой памяти очередного конечного значения интервала интерполяции и записи его в блок 2 устройства, уменьшая при этом значение указателя стека на единицу. После записи в блок 2 выполняется один из режимов работы устройства, как было описано выше.

Рассмотрим работу устройства для случая, когда Rn>3 (фиг.3,б). После записи отсчета An+1 (Rn+1-4) в блок 2 интерполятор переходит во второй режим работы, так как требуется интерполировать на интервале более семи значений. В этом случае отсчет An+1 (Rn+1-1) записывается в блок 6 стековой памяти, а в блок 2 заносится отсчет An1(Rn1=3), с четвертого выхода блока сумматоров. Отсчет An1 соответствует середине интервала между отсчетами Аn и An+1 (фиг.3б). После записи отсчета An1 в блок 2, устройство переходит в первый режим работы. Интерполятор выполняет передачу данных через свой первый выход (фиг.3в) отсчета Аn и семь интерполированных значений из интервала между отсчетами An и An1. После этого в блоке управления проверяется наличие данных в блоке 6, то этот отсчет записывается в блок 2 (фиг.3,г) и интерполятор переходит в первый режим работы. В результате на его первый выход передаются отсчет Аn и семь интерполированных значений из интервала между отсчетами An и An1 (фиг.3,г).

Подробнее опишем работу устройства в первом режиме, т.е. интерполяции и передачи на выход начального значения интервала интерполяции и интерполированных значений (число интерполированных и передаваемых значений указывает ранг Rn). После записи в блок 2 конечного значения интервала интерполяции An или Anj , включая соответствующее значение ранга Rn или Rnj, и при условии, что Rn или Rnjменьше или равно трем, интерполятор начинает работу в первом режиме. Условие Rn≅3 существует из-за того, что блок 3 сумматоров интерполирует не более семи значений при установке кодов на его входах, а из выражения N=2Rn-1 следует, что в этом случае должно выполняться условие Rn≅3.

Сигнал с выхода элемента ИЛИ 7 поступает на четвертый вход блока управления. Через время интерполяции в блоке 3 сумматоров устройство готово к передаче данных на выход. К этому времени код с выхода дешифратора 13 занесен в счетчик 14 (число передаваемых данных на выход устройства), на адресном входе коммутатора 4 установлено нулевое значение, соответствующее передаче на выход начального значения интервала интерполяции. Адресный код на коммутаторе 4 будет изменяться с шагом, определяемым выходным кодом дешифратора 13. К этому времени на семи выходах блока 3 сумматоров установлены интерполированные значения, принадлежащие прямой заданной своими конечными значениями (первый и второй выходы блока 2 регистров). Требуется только выбрать необходимые значения и передать их на выход, что выполняется с помощью коммутатора 4. Блок управления 12 формирует необходимую последовательность кодов на адресном входе коммутатора 12 и сигналы сопровождения данных на втором выходе интерполятора.

На каждом интервале интерполяции, при работе в первом режиме, интерполятор передает на выход Р значений процесса, включая начальную точку интервала. Конечная точка интервала передается на выход в следующем цикле интерполяции, в качестве начальной точки следующего интервала и т.д. Причем значение определяется выражением

P=2Rn.

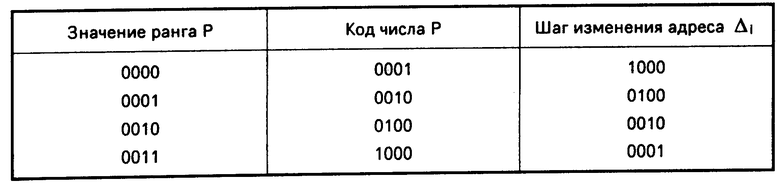

Величину Р формирует дешифратор 13 по значению ранга, поступающему ему на вход. Код числа Р формируется так, как указано в таблице, кроме того в таблице приведены коды Δi, соответствующие рангу Rn. В таблице используются обозначения:

Rn - код ранга, соответствующий конечному значению интервала интерполяции; Р - число значений процесса передаваемых на выход устройства; Δi- шаг приращения кода адреса на адресном входе коммутатора 4.

Из таблицы видно, что коды чисел Р и Δiявляются зеркальным отображением друг друга, поэтому для формирования данных кодов достаточно одного дешифратора 13, а соответствующие коды получаются перекоммутацией разрядов выходного кода дешифратора 13.

Значение кода Δi поступает на блок 12 управления, где используется для формирования последовательности адресов, которая используется коммутатором 4. Код Δiсохраняет постоянное значение во время всего текущего цикла интерполяции.

Значение кода с выхода дешифратора 13 (при соответствующей коммутации разрядов выходного кода) заносится в двоичный счетчик 14. Каждая передача данных на выход устройства сопровождается вычитанием единицы из кода, установленного в двоичном счетчике 14. При достижении двоичным счетчиком 14 нулевого значения, на его выходе формируется сигнал "Конец счета). Этот сигнал поступает на блок управления 12, на триггер 16 (фиг. 2) и выключает его. На этом заканчивается передача данных на выход. По этому сигналу ("Конец счета") в блоке управления 12 проверяется наличие данных в блоке 6 стековой памяти и далее так, как было описано выше.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Устройство для сжатия информации | 1981 |

|

SU970421A1 |

| ОПТИКО-ЭЛЕКТРОННЫЙ ШИРОКОДИАПАЗОННЫЙ ИЗМЕРИТЕЛЬ ЛИНЕЙНЫХ СМЕЩЕНИЙ | 1993 |

|

RU2069309C1 |

| ОПТИКО-ЭЛЕКТРОННОЕ УСТРОЙСТВО ИЗМЕРЕНИЯ ПОЛОЖЕНИЯ ОТСЧЕТНОГО КРУГА УГЛОМЕРНОГО ИНСТРУМЕНТА | 1992 |

|

RU2082087C1 |

| Устройство для сжатия информации | 1983 |

|

SU1129638A1 |

| ОПТИКО-ЭЛЕКТРОННЫЙ ИЗМЕРИТЕЛЬ УГЛА ПОВОРОТА АЛИДАДЫ | 1994 |

|

RU2092790C1 |

| Устройство для сжатия информации | 1988 |

|

SU1547011A1 |

| АКУСТООПТИЧЕСКИЙ ДАТЧИК УГЛА | 1990 |

|

RU2029237C1 |

| Устройство для сжатия информации | 1985 |

|

SU1392584A1 |

| Устройство для программного управления | 1982 |

|

SU1108392A1 |

Изобретение относится к средствам обработки и передачи сигналов там, где требуется линейное интерполирование сигналов при повышенном быстродействии, при работе в реальном масштабе времени, например телеметрии, в автоматике, связи, вычислительной технике и т.д. Интерполятор состоит из двух коммутаторов блока регистров, блока сумматоров, блока стековой памяти и блока управления. Регистр и блок сумматоров реализуют параллельный процесс интерполяции линейного отрезка, заданного конечными значениями. Блок управления, блок стековой памяти и коммутаторы обеспечивают интерполяцию данных на отрезке произвольной длины /кратной степени два/, вычисляя при необходимости вспомогательные опорные значения процесса. Интерполятор не требует дополнительных данных об исходном сигнале, кроме последовательных конечных значений интервала интерполяции и параметра, указывающего количество требуемых интерполированных значений на интервале. 1 з.п. ф-лы, 5 ил.

| Линейный интерполятор | 1989 |

|

SU1686408A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-02-09—Публикация

1991-06-13—Подача