низатора подключен к стробирукяцему входу второго линейного интерполятора , второй вход элемента ИЛИ - к

1108392

выходу первого линейного интерполятора, а выход коммутатора - к входу блока согласования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1987 |

|

SU1427333A1 |

| Устройство для программного управления скоростью подачи | 1982 |

|

SU1067473A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для программного управления группой станков | 1970 |

|

SU871745A3 |

| Светолучевой осциллограф | 1984 |

|

SU1318918A1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее синхронизатор, информационныевыходы которого соединены с первыми входами схемы сравнения, последовательно соединенные блок ввода программы, первый регистр и второй регистр, а также первый сумматор, выходы которого подключены к первым информационным входам первого линейного интерполятора, первые входы - к первым выходам второго регистра, вторые входы - к первым входам четвертого регистра и выходам третьего регистра, входы которого соединены с выходом датчика обратной связи, механически связанного с приводом, вход которого подключен к выходу блока согласования, вторые входы схемы сравнения подключены к вторым выходам второго регистра, а выход - к стробирующим входам второго, третьего и четвертого регистров, блока ввода программы и синхронизатора, первый синхронизирующий выход которого соединен со стробирующим входом первого линейного интерполятора, отличающееся тем, что, с целью повышения точности устройства, в него введены последовательно соединенные второй линейный интерполятор, делитель частоты Ia четыре, элемент ИЛИ, делитель частоты на два и коммутатор, а также элемент п-2И-(-г-ИЛИ, триггер и второй сумматор, первые входы которого сое(/) динены с первыми выходами второго регистра, вторые входы - с выходами четвертого регистра, а выходы с первыми информационными входами второго линейного интерполятора, подключенного вторыми информационными входами к третьим выходам второго регистра, к вторым информационным входам первого линейного интерполятора и к первым входам элемента Л-2И- -ИЛИ, вторые входы которого соединены с вторыми синхрони зирующими выходами синхронизатора, а выход - с входом установки в единицу триггера и с другим стробирующим входом четвертого регистра, вторые входы которого соединены с выходами датчика обратной связи, вход установки в ноль триггера соединен с выходом схе1Ф1 сравнения, с вторым входом коммутатора, третий вход которого подключен к выходу второго линейного интерполятора, третий синхронизирующий выход синхро

Изобретение относится к автоматке и вычислительной технике и може быть применено при построении систем программного управления.

Известна система программного уравления с шаговым приводом, содержащая интерполятор, импульснофазовый преобразователь, электронный коммутатор, шаговый двигатель, гидравлический усилитель мощности и датчик обратной связи, в которой достигается высокая точность обработки, так как в результате установки датчика перемещений исключаются ошибки, вызываемые неточностями в изготовлении механических звеньев привода 111.

Известно устройство для комбинированного числового программного управления, содержащее датчик обратной связи, сумматор, блок ввода блок буферной памяти, интерполятор блок регулирования контурной скороти, следящий привод, генератор импульсов, блок разгона и торможения Благодаря введению коммутатора повьшается быстродействие устройства 21.

В указанном устройстве так же, как и в системе LI, достигается высокая точность обработки, благодаря наличию обратной связи, однако они характеризуются большой погрешностью линейного интерполятора, приводящей к неточности устройств в целом.

Для достижения необходимой точности в таких устройствах требуется увеличение числа опорных точек, по которым производится интерполяция , что приводит к увеличению объема программы и усложнению вводных устройств. Кроме того, в известных устройствах отсутствует блок памяти для запоминания значений координат в предшествующие моменты времени, что приводит к неточности устройства.

Наиболее близким к изобретению является устройство цифрового программного управления, содержащее блок ввода программь, блок памяти, 5 выполненный на регистрах и группах злементов И, блок формирования сигнала Смена цикла, интерполятор, сумматор, блок согласования, привод и датчик обратной связи, причем

блок ввода программы через первый регистр и первую группу элементов И подключен к второму регистру, выходы которого через вторую группу элементов И подключены к третьему

5 регистру, а выходы третьего регистра через третью группу элементов И соединены с входами четвертого регистра, при этом выходы второго, третьего и четвертого регистров

0 через сумматор соединены с входами пятого регистра, выходы которого подключены к интерполятору, а выход блока формирования сигнала Смена цикла соединен с стробирующими вхо дами первой, второй и третьей групп элементов И, выход интерполятора через блок согласования поступает на привод, а выход датчика обратной связи соединен с входом сумматора.

0 Б данном устройстве повьпиается надежность и благодаря блоку памяти для запоминания значений координат в предществующие моменты времени повьш1ается точность С31.

5 Однако в известном устройстве велика погрешность линейного интерполятора, что приводит к неточности устройства в целом, либо к увеличению объема программы.

Кроме того, в этом устройстве появляются большие скачки скорости в точках сопряжения линейных участков, что приводит к увеличению динамических ошибок.

Цель изобретения - повьпиение точности и уменьшение динамических ошибок .

Поставленная цель достигается тем, что в устройство, содержащее синхронизатор, информационные выходы которого соединены с первыми входами схемы сравнения, последовательно соединенные блок ввода программы, первый регистр и второй регистр а также первый сумматор, выходы котрого подключены к первым информационым входам первого линейного интерполятора, первые входы - к первым выходам второго регистра, вторые входы - к первым входам четвертого регистра и выходам третьего регистр входы которого соединены с выходом датчика обратной связи, механически связанного с приводом, вход которого подключен к выходу блока согласования, вторые входы схемы сравнения подключены к вторым выходам второго регистра, а -выход - к стробирующим входам второго, третьего и четвертого регистров, блока ввода программы и синхронизатора, первый синхронизирующий вьпсод которого соединен с стробирующим входом первого линейного интерполятора, введены последовательно соединенные второй линейный интерполятор, делитель частоты на четыре, элемент ИЛИ, делитель частоты на два и коммутатор, а также элемент л-2И-п-ИЛИ, триггер и второй сумматор, первые входы которого соединены с первыми выходами второго регистра, вторые входы - с выходами четвертого регистра, а выходы - с первыми информационными входами второго линейного интерполятора, подключенного вторыми информационными входами к третьим выходам второго регистра, к вторым информационным входам первого линейного интерполятора и к первым входам элемента 1-2И-п-ИЖ, вторые входы которого соединены с вторыми синхронизирующими выходами синхронизатора, а выход - с входом установки в единицу триггера и .с другим стробируклцим входом четвертого регистра, вторые входы которого соединены с выходами датчика обратной связи, вход установки в ноль триггера соединен с выходом схемы сравнения, выход - с вторым входом коммутатора, третий вход которого подключен к выходу второго линейного интерполятора, третий синхронизирующий выход синхронизатора подключен к стробирующему входу второго линейного интерполятора, второй вход элемента ИЛИ к выходу первого линейного интерполятора, а выход коммутатора - к входу блока согласования.

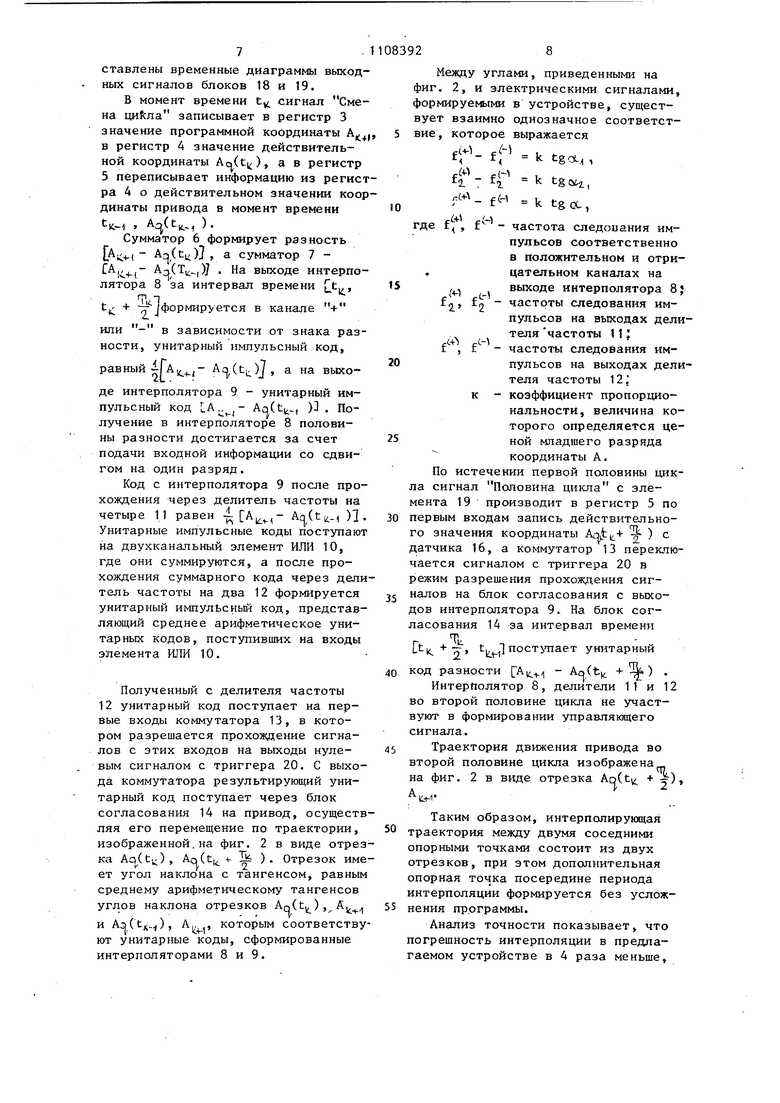

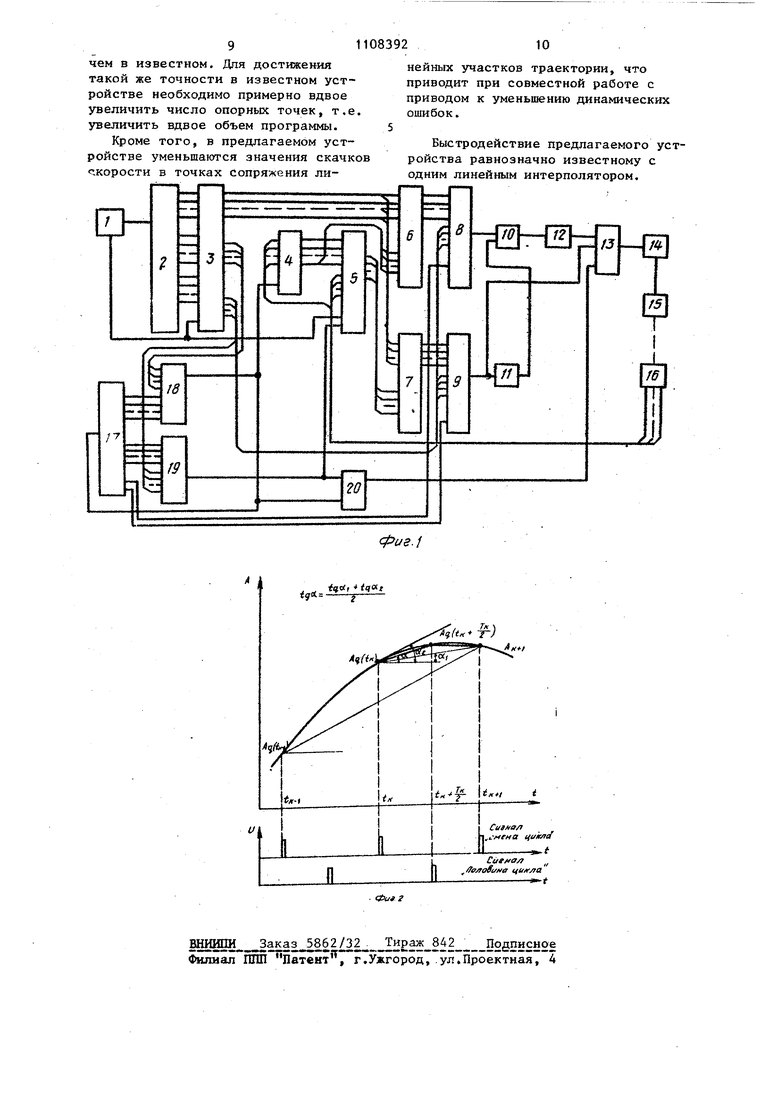

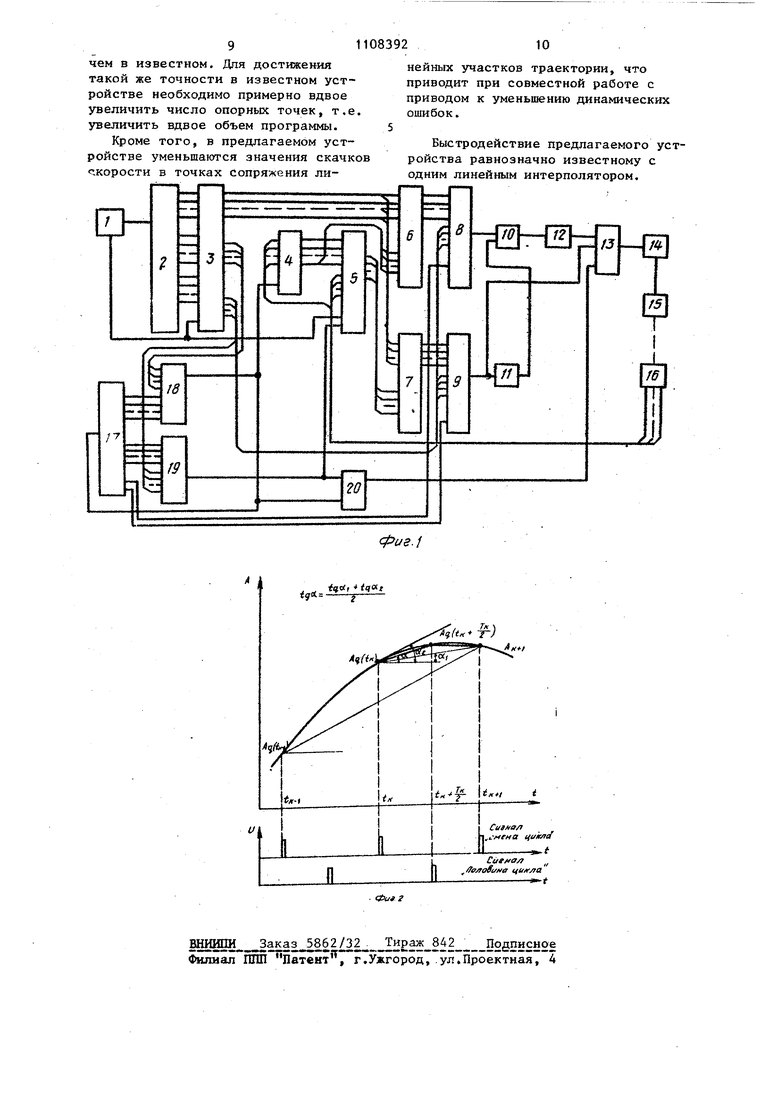

На фиг. 1 представлена структурная схема устройства; на фиг. 2 траектория движения привода.

Устройство содержит блок ввода программы 1, регистры 2-5, сумматоры 6 и 7, линейные интерполяторы 8, 9, элемент ИЛИ 10, делители частоты на четыре и на два 11 и 12, коммутатор 13, блок согласования 14, привод 15, датчик обратной связи 16 (ДОС), синхронизатор 17, схему сравнения 18, элемент П-2И-П-ИЛ 19 и триггер 20.

Блок ввода программы 1 через регистр 2 соединен с регистром 3, который соединен первой группой выходов с входагл сумматоров 6 и 7, второй группой выходов - с входами схемы сравнения 18, третьей группой выходов - с входами элемента П-2И-ПШМ 19 и с входами интерполяторов 8, 9. Выходы регистра 4 соединены с входами регистра 5 и с второй группой входов сумматора 6, а выходы.регистра 5 соединены с второй группой входов сумматора 7. Выходы сумматоров 6 и 7 с единены соответственно с входами интерполяторов В и 9. Выходы интерполятора 9 соединены с вxoдa D коммутатора 13 и через делитель 11 с входами элемента ИЛИ 10, вторые входы которо-, го подключены к выходам интерполятора 8. Выходы элемента ИЛИ 10 через делитель 12 соединены с вторыми входами коммутатора 13, выходы которого через блок согласования 14 подключены к приводу 15.

Первая группа выходов синхронизатора 17 соединена с группой входов схемы сравнения 18, вторая группа выходов - с группой входов элемента п -2И-П-ИЛИ 19, а два синхронизирующих выхода соединены соответственно со стробирующими входами интерполяторов 8, 9. Выход схемы сравнения 18 соединен с входами опроса блока ввода 1, с входом установки в ноль триггера 20, со стробирутоир1ми входами регистров 3, 4, 5, с управляющим входом синхронизатора 17 и триггера 20. Выход элемента Г --2И А-ИЛИ 19 соединен со стробирукнцим входом регистра 4 и единичным входом триггера 20, а выход триггера 20 соединен с управ ляющим входом коммутатора 13. Устройство работает следующим образом. В блоке ввода 1 запис.,на программа, содержащая координаты опорны точек, программное время и период иктерпсшяиди. По сигналу опроса блок 1 выдает одно значение программной координаты и соответствующие ей программное время и период интерполяции 5 которые записываются в буфер и регистр 2, Регистры 3, 4 и 5 вь полнены на синх,ронных триггерйх D -типа. Информация на выходе регистра появляется по окончании стробирующего сигнала. Регистр 5, кроме того, вьтолнен с входной логикой, обеспечивающей запись по первым или вторым информационным входам в зависимости от поступления стробирующего сигнала по первому шга второму стробирующе гу входу Сумматоры 6 и 7 выполнены на логических потенциальных элементах, обеспечивающих сохранение информации на выходе до тех пор, пока присутствует информация на входах, благодаря этому исключается, необходимость в регистрах памяти на выходах сумматоров. Линейные интерполяторы 8 и 9 вьшолнены на делителях частоты .с переменным коэффициентом деления (микросхема К 155 ИЕ8).и элементах И. В качестве делителей частоты 11 и 12 используются реверсивные счетчики, Синхронизатор 17 обеспечивает работу устройства в реальном време ни. Он формирует на информационных входах двоичный 17-ти разрядньн код времени, на вторых синхронизир щих выходах - короткие импульсные сигналы при изменении состояния со ответствукщего выходного разряда к да времени с нуля на единицу. На п вом и третьем синхронизирующих выходах формируются две несовпадающие во времени импульсные последовательности с частотами следования импульсов 2 гаГц, используемые для тактирования интерполяторов 8 и 9. Импульсные сигналы на первом и третьем синхронизирующих выходах появляются после того, как на вход синхронизатора поступит первьй импульс со схемы сравнения 18. После осуществления подготовительных операций производится запуск программного режима. При этом считывается информация о первой опорной точке с буферного регистра 2 в регистр 3, записывается код с ДОС 16 в регистр 4 и запускается блок ввода 1 для считывания информации в буферный регистр 2 о второй опорной точке. Далее устройство переходит в состояние ожидания сравнения реального времени с программным временем первого кадра, которое осуществляется в схеме сравнения 18. В момент сравнения кодов реального и программного времени схема сравнения 18 вьщает импульс, который осуществляет перезапись в регистрах 3, 4 и 5, запуск блока ввода 1 и разрешает формирование синхронизатором т.актовых импульсов на первом и третьем синхронизирующих выходах. При этом начинают работать интерполяторы 8, 9 и начинается программный режим управления приводом. Синхронизатор на вторых синхронизирующих выходах формирует короткие импульсы при изменении состоя- . НИН соответствующего разряда с нуля на единицу. Код периода интерполяции Т, который выбирается равным с при N О, 1, .. . , содержит единицу в одной из позиций. Кроме того Т и время , сосоответствующее опорным точкам, выбираются так, чтобы выполнялось условие целое число. При поступлении кода Т и импульсных сигналов с выходов счетчика на элемент П-2И-ИИЛИ 19 формируется импульс, расположенный на временной оси посередине периода интерполяции. Триггер 20 формирует потенциальный сигнал, который в первой половине периода Т. равен нулю, а во второй половине - единице, так как в нулевое состояние он устанавливается импульсом со схемы сравнения 18, а в единичное - импульсом с элемента 19. Формирование траектории, по которой перемещается привод, поясняется фиг. 2, на которой также представлены временные диаграммы выходных сигналов блоков 18 и 19.

В момент времени t сигнал Смена записывает в регистр 3 значение программной координаты А, в регистр 4 значение действительной координаты Аа(С|), а в регистр 5 переписывает информацию из регистра 4 о действительном значении координаты привода в момент времени , A::j(t,, ).

Сумматор 6 формирует разность t kL-i-i Aq(ti/)J, а сумматор 7 AqCT,)J . На выходе интерполятора 8 за интервал времени ,

IJ1 -1 tj/; + формируется в канапе +

или - в зависимости от знака разности, унитарный импульсный код,

равный-ГA; - Ao(ti)J, а на выходе интерполятора 9 - унитарный импульсный код 1.Ац, AaCtj.,, )3 . Получение в интерполяторе 8 половины разности достигается за счет подачи входной информации со сдвигом на один разряд.

Код с интерполятора 9 после прохождения через делитель частоты на четыре 11 равен ,- An(tt/-, )1. Унитарные импульсные коды поступают на двухканальный элемент ИЛИ 10, где они суммируются, а после прохождения суммарного кода через делитель частоты на два 12 формируется унитарный импульсный код, представляющий среднее арифметическое унитарных кодов, поступивших на входы элемента ИЛИ 10.

Полученный с делителя частоты 12 унитарный код поступает на первые входы коммутатора 13, в котором разрешается прохождение сигналов с этих входов на выходы нулевым сигналом с триггера 20. С выхода коммутатора результирующий унитарный код поступает через блок согласования 14 на привод, осуществляя его перемещение по траектории, изображенной.на фиг. 2 в виде отрезка Aq(t), AnCt,-ь S: ). Отрезок имеет угол наклона с тангенсом, равным среднему арифметическому тангенсов углов наклона отрезков An(t(,) , Aj,,, и Аэ(с.), А,, которым соответствуют унитарные коды, сформированные интерполяторами 8 и 9.

Между углами, приведенными на фиг. 2, и электрическими сигналами, формируег« ми в устройстве, существует взаимно однозначное соответствие, которое выражается

k tgoL,,

:М -Н, ..

1 1 k tg 062.1

fH k te rt

l -S (A- ,

cM ,--t

где t , t - частота следования импульсов соответственно в положительном и отрицательном каналах на

, выходе интерполятора 8; f, fn частоты следования импульсов на выходах делителя частоты 1J

f , f - частоты следования импульсов на выходах делителя частоты 12I к - коэффициент пропорциональности, величина которого определяется ценой младшего разряда координаты А.

По истечении первой половины цикла сигнал Половина цикла с элемента 19 производит в регистр 5 по 0 первым входам запись действительного значения координаты ) с датчика 16, а коммутатор 13 переключается сигналом с триггера 20 в режим разрешения прохождения си1- налов на блок согласования с выходов интерполятора 9. На блок согласования 14 за интервал времени

Ф t t, j nocT TiaeT унитарный

код разности A,.., - AoCtj +)

Интерполятор 8, делители 11 и 12 во второй половине цикла не участвуют в формировании управлякяцего сигнала.

5 Траектория движения привода во второй половине цикла изображена

на фиг. 2 в виде отрезка AoCtij т) А1

t-t-i

Таким образом, интерполирующая траектория между двумя соседними опорными точками состоит из двух отрезков, при этом дополнительная опорная точка посередине периода интерполяции формируется без услож5 нения программы.

Анализ точности показывает, что погрешность интерполяции в предлагаемом устройстве в 4 раза меньше.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ С ШАГОВЫМПРИВОДОМ | 0 |

|

SU336646A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-08-15—Публикация

1982-07-23—Подача