Изобретение относится к вычислительной технике и может быть использовано как вычислитель моды распределения и формирователь полигона (гистограммы) случайного процесса.

В качестве наиболее близкого аналога предлагается статистический анализатор, содержащий два регистратора, два блока памяти, сумматор, два элемента задержки и генератор тактовых импульсов (RU, C1, 2015555, MПK G 06 F 17/18, 1994 г.).

Технический результат, на достижение которого направлено изобретение, заключается в снижении требуемого объема оперативной памяти, поскольку отпадает необходимость хранить отсчеты исследуемой случайной величины. Кроме того, расширены функциональные возможности за счет вычисления моды.

Указанный технический результат достигается тем, что статистический анализатор содержит оперативное запоминающее устройство, сумматор, три регистра, счетчик, аналого-цифровой преобразователь, триггер, три элемента 2И, два элемента 2ИЛИ, два элемента задержки и блок управления, при этом вход счетчика соединен с адресным входом оперативного запоминающего устройства, информационный вход которого соединен с выходом первого регистра, информационный вход которого соединен с выходом сумматора, первый вход которого соединен с информационным выходом блока памяти, а второй вход сумматора служит входом задания единицы, выход переноса сумматора соединен с D-входом триггера, выход которого соединен с тактовым входом второго регистра, информационный вход которого объединен с адресным входом блока памяти и подключен к информационному выходу аналого-цифрового преобразователя, выход готовности которого соединен с первым входом первого элемента 2ИЛИ, выход которого через первый и второй последовательно соединенные элементы задержки соединен с первым входом второго элемента 2ИЛИ, выход которого соединен с входом управления блока памяти, тактовый вход первого регистра объединен с тактовым входом триггера и подключен к выходу первого элемента задержки, второй вход первого элемента 2ИЛИ соединен с выходом первого элемента 2И, первый вход которого объединен со счетным входом счетчика и подключен к выходу второго элемента 2И, первый вход которого объединен с первым входом третьего элемента 2И и служит тактовым входом анализатора, выход третьего элемента 2И соединен с тактовым входом аналого-цифрового преобразователя, информационный вход которого является информационным входом анализатора, входами запуска и обнуления которого служат соответствующие входы блока управления, первый выход которого соединен со вторым входом второго элемента 2И, второй выход блока управления соединен со вторым входом второго элемента 2ИЛИ, третий выход блока управления соединен со вторым входом третьего элемента 2И, четвертый выход блока управления соединен с управляющим входом счетчика, выход переполнения которого подключен к первому входу блока управления, пятый выход которого соединен со вторым входом первого элемента 2И, второй вход блока управления соединен с выходом триггера, обнуляющий вход которого объединен с обнуляющими входами счетчика и первого регистра и подключен к обнуляющему входу анализатора, информационным выходом которого является выход второго регистра.

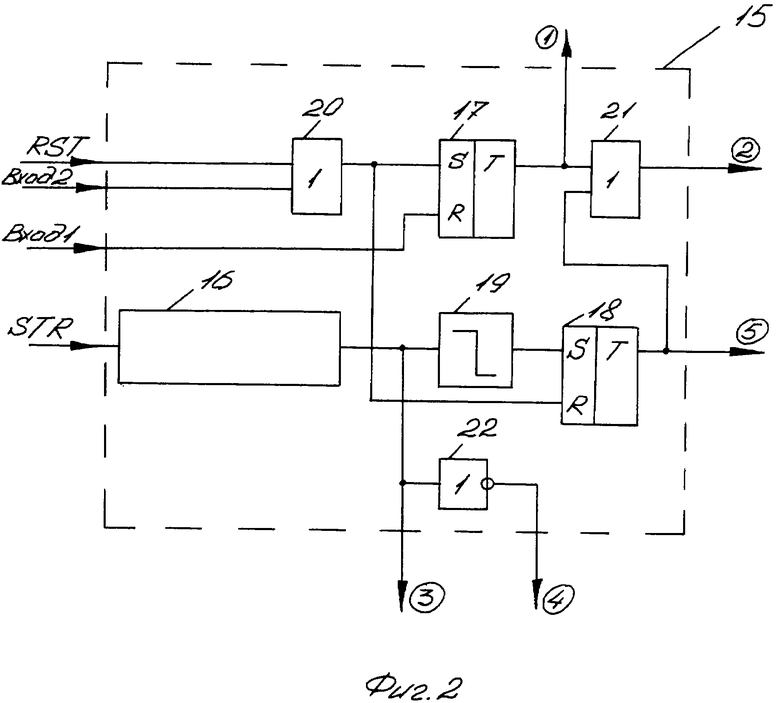

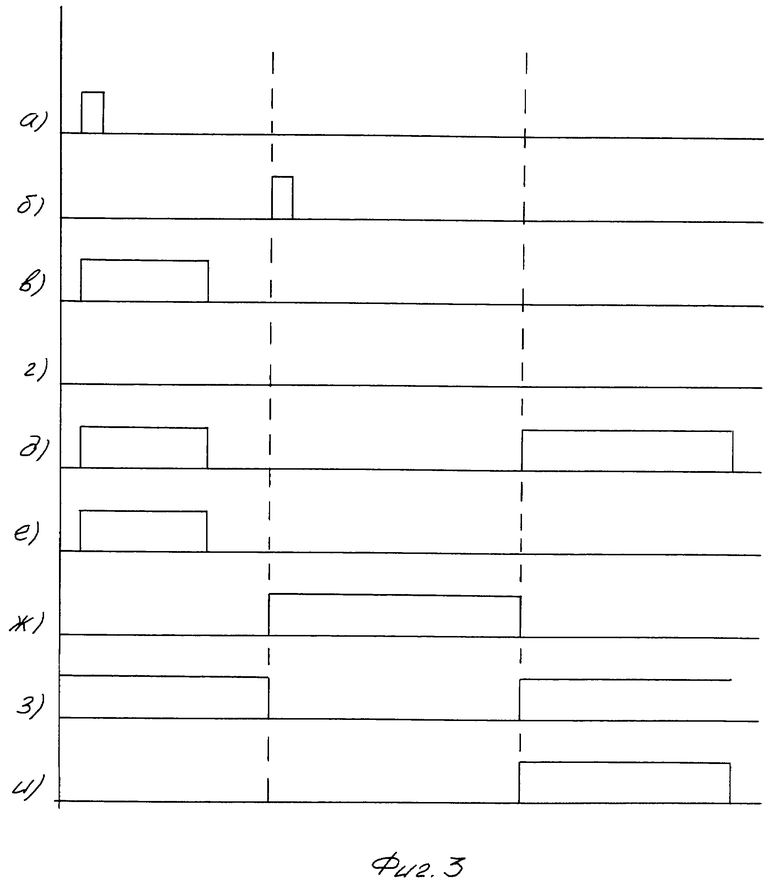

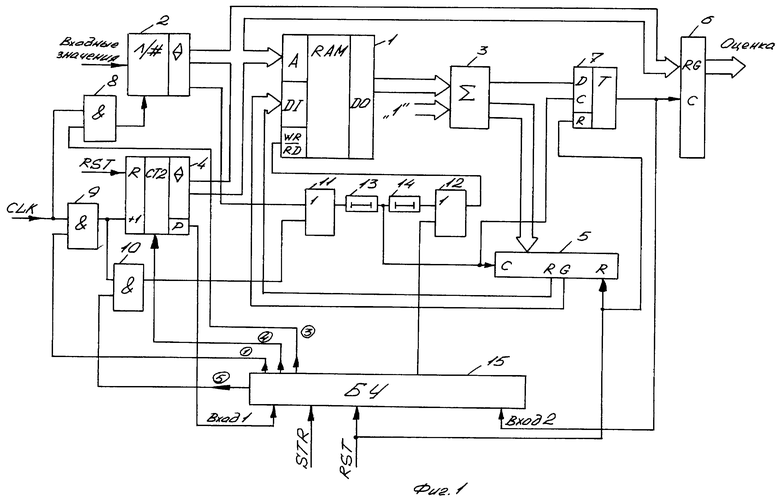

Изобретение поясняется чертежами, где на фиг.1 изображена структурная схема статистического анализатора; на фиг.2 - структурная схема блока управления; на фиг.3 - временные диаграммы, иллюстрирующие работу статистического анализатора.

Статистический анализатор содержит оперативное запоминающее устройство (ОЗУ) 1, аналогово-цифровой преобразователь (АЦП) 2, сумматор 3, счетчик 4, регистры 5 и 6, триггер 7, элементы 2И 8, 9 и 10, элементы 2ИЛИ 11 и 12, элементы задержки 13 и 14, блок управления (БУ) 15. Информационный вход DI ОЗУ 1 соединен с выходом регистра 5, информационный вход которого соединен с выходом сумматора 3, первый вход которого соединен с информационным выходом DO ОЗУ 1, а второй вход сумматора 3 служит входом задания единицы. Выход переноса сумматора 3 соединен с D-входом триггера 7, выход которого соединен с тактовым входом регистра 6, информационный вход которого объединен с адресным входом ОЗУ 1 и подключен к информационному выходу АЦП и разрядному выходу счетчика 4. Выход готовности АЦП 2 соединен с первым входом элемента 2ИЛИ 11, выход которого через элементы задержки 13 и 14 соединен с первым входом элемента 2ИЛИ 12, выход которого соединен с входом WR/RD ОЗУ 1. Тактовый вход регистра 5 объединен с тактовым входом триггера 7 и подключен к выходу элемента задержки 13. Второй вход элемента 2ИЛИ 11 соединен с выходом элемента 2И 10, первый вход которого объединен со счетным входом счетчика 4 и подключен к выходу элемента 2И 9, первый вход которого объединен с первым входом элемента 2И 8 и служит тактовым входом CLK статистического анализатора. Выход элемента 2И 8 соединен с тактовым входом АЦП 2, информационный вход которого является информационным входом X(t) анализатора, входами запуска STR и обнуления RST которого служат соответствующие входы БУ 15, первый выход которого соединен со вторым входом элемента 2И 9, второй выход БУ 15 соединен со вторым входом элемента 2ИЛИ 12, третий выход соединен со вторым входом элемента 2И 8, четвертый выход соединен с управляющим входом счетчика 4, выход переполнения которого подключен к первому входу БУ 15, пятый выход которого соединен со вторым входом элемента 2И 10. Второй вход БУ 15 соединен с выходом триггера 7, обнуляющий вход которого объединен с обнуляющими входами счетчика 4 и регистра 5 и подключен к обнуляющему входу RST анализатора, информационным выходом которого является выход регистра 6.

Блок управления содержит одновибратор 16, триггеры 17 и 18, дискриминатор 19 задних фронтов, элементы 2ИЛИ 20 и 21, инвертор 22. Выход одновибратора 16 соединен с входами инвертора 22 и дискриминатора 19, выход которого соединен с установочным входом триггера 18, обнуляющий вход которого объединен с установочным входом триггера 17 и подключен к выходу элемента 2ИЛИ 20, выход триггера 17 соединен с первым входом элемента 2ИЛИ 21, второй вход которого соединен с выходом триггера 18. RST входом блока 15 служит первый вход элемента 2ИЛИ 20, второй вход которого является вторым входом блока 15, STR входом которого служит вход одновибратора 16, выход которого является третьим выходом блока 15, первым и вторым выходами которого служат выходы 2ИЛИ 21 и триггера 17 соответственно, четвертым выходом блока 15 служит выход инвертора 22, а пятым выходом - выход триггера 18.

На временных диаграммах показаны импульсы на входе RST (фиг.3-а); импульс на входе STR (фиг.3-б); логические уровни на входе WR/RD ОЗУ 1 (фиг.3-в); импульс на первом входе БУ 15 (фиг.3-г); логические уровни на первом, втором, третьем, четвертом и пятом выходах БУ 15 (фиг.3-д, е, ж, з, и соответственно).

Статистический анализатор путем формирования полигона значений исследуемого параметра вычисляет моды распределения - наивероятнейшее значение. При этом ширина дифференциального коридора Δх определяется шагом квантования исследуемого сигнала X(t), если исследуются амплитудные характеристики или частотой дискретизации Δt при изучении, например, распределения временных интервалов.

В случае, когда исследуемый процесс подчинен унимодальному и симметричному закону распределения, устройство вычисляет математическое ожидание, т. к. мода и математическое ожидание в этой ситуации равны.

Работу анализатора можно условно разбить на три этапа.

1 этап. Начальная установка устройства, во время которой производится очистка ОЗУ и обнуляется вся последовательная логика.

2 этап. Накопление числа попаданий в заданные дифференциальные коридоры.

3 этап. Анализ, поиск наибольшего значения.

Начальная установка устройства осуществляется по импульсу обнуления RST (фиг.3-а). При этом на первом и втором выходах БУ 15 устанавливаются высокие логические уровни (фиг. 3-д, е), разрешающие счет адресному счетчику 4 и переводящие ОЗУ 1 в режим записи. В то же время на информационный вход DT ОЗУ 1 подается код нуля с выхода обнуленного регистратора 5. Таким образом, по всем адресам ОЗУ 1 записываются коды нулей, что является подготовкой к загрузке очередного массива данных. По импульсу переноса (переполнения) (фиг. 3-г) с выхода счетчика 4 подача тактовых импульсов на его вход прекращается, а ОЗУ переводится в режим чтения (фиг.3-в) устройство готово к построению полигона.

Начало следующего этапа определяется моментом поступления импульса STR (фиг. 3-б). БУ 15 на третьем и четвертом выходах выставляет соответственно высокий и низкий логические уровни (фиг.3-ж, з), что приводит к запуску АЦП 2 и отключению выходов счетчика 4 от адресной шины (перевод в состояние высокого импеданса). Поступающие на адресный вход ОЗУ 1 квантованные отсчеты Хm (m - номер дифференциального коридора, i=1, M, М - число адресов ОЗУ 1) вызывают из ОЗУ 1 содержимое ячеек по m-ному адресу. Содержимое N(Xm) поступает на первый вход сумматора 3, на входе которого имеем сумму-инкремент N(Xm)+1.

По импульсу сопровождения вырабатываемым АЦП 2 N(Xm)+1 переписывается в регистр 5, после чего с задержкой τ2, вносимой элементом задержки 14, ОЗУ 1 переходит в режим записи, и значение N(Xm)+1 переписывается в ОЗУ 1 по тому же адресу.

Описанная процедура повторяется в каждый тактовый интервал в течение всего времени накопления. В итоге к моменту его окончания, в ОЗУ 1 по m-ному адресу будет накоплено число попаданий значений величины X(t) в m-ный дифференциальный коридор. По истечении времени, отведенного на накопление, высокий логический уровень БУ 15 сменяется на низкий (фиг.3-ж) - аналогово-цифровое преобразование прекращается и АЦП 2 отключается от адресной шины, к которой подключается выход адресного счетчика 4. Кроме того, установившийся на выходе БУ 15 высокий логический уровень (фиг.3-и) разрешает прохождение тактовых импульсов с выхода элемента 2И 9 через элемент 2И 10 на вход элемента 2ИЛИ 11. Несложно видеть, что тактовые импульсы, поступающие на один из входов элемента 2ИЛИ 11 будут выполнять те же функции, что и импульсы сопровождения с выхода АЦП 2, которые поступали на этапе накопления на другой вход указанного элемента 2ИЛИ.

В результате содержимое ячеек каждого m-ного адреса, в связи с подбором адресов счетчиком 4, будет циклически увеличиваться на единицу младшего разряда до тех пор, пока на выходе переноса сумматора 3 не появится соответствующий импульс. Появление импульса переноса свидетельствует о том, что в ячейке по данному адресу зафиксировано наибольшее число попаданий. Т.е. пик полигона приходится на m-ный дифференциальный коридор, причем значение m и есть мода.

Далее импульс переполнения через D-триггер 7, который выполняет функции синхронизатора, поступает уже как перепад напряжений на тактовый вход регистра 6 результата. На этом этап анализа, а следовательно, и весь цикл вычислений завершается.

Элементы задержки 13 и 14 в структуре анализатора необходимы для обеспечения надежного инкрементирования и перезаписи. При этом задержка в элементе 13 должна быть τ1≥1,5(tA+tΣ), где tA - время выборки ОЗУ 1, tΣ- быстродействие сумматора 3; задержка в элементе 14 t2 должна быть достаточной для окончания переходных процессов записи в регистр 5 и в случае выполнения регистра по технологии ТТЛ t2 100 нc.

Принцип действия БУ 15 состоит в следующем.

По импульсу RST триггер 17 устанавливается в единичное состояние и формирует на первом и втором выходах блока 15 высокие логические уровни (фиг. 3-д, е). Возвращение триггера 17 в исходное состояние происходит под действием импульса переполнения счетчика 4 (фиг.1), который поступает на первый вход блока 15. По импульсу STR одновибратор 16 вырабатывает импульс, длительность которого равна длительности интервала накопления (третий выход блока 15), запуская таким образом АЦП 2.

По окончании формирования вершины указанного импульса дискриминатор 19 задних фронтов вырабатывает короткий импульс, переводящий триггер 18 в единичное состояние. В связи с этим на первом и пятом выходах блока 15 устанавливаются высокие логические уровни, свидетельствующие о начале этапа анализа, по окончании которого на второй вход блока 15 поступает скачок напряжения с выхода D-триггера 7, который переводит триггеры 17 и 18 в исходные состояния.

Предлагаемый статистический анализатор может быть использован и просто как формирователь полигона. Для этого из устройства исключают элементы 2И 10 и 2ИЛИ 11, а выход импульса сопровождения АЦП 2 подключают непосредственно ко входу элемента задержки 13. Значения столбцов полигона снимают с информационного выхода DO ОЗУ 1. В случае необходимости работы анализатора в двух режимах, как формирователя полигона и вычислителя моды, переключение режимов производят по пятому выходу БУ 15. При построении полигона на пятом выходе блока 15 на всех этапах работы устанавливают уровень логического нуля.

В рассмотренной структуре анализатора выходы АЦП 2 и счетчика 4 должны иметь три состояния. При этом под управляющим входом счетчика 4 (вход, соединенный с четвертым выходом БУ 15) подразумевается вход, переводящий выходные каскады счетчика в состояние высокого импеданса.

При анализе амплитудных характеристик в качестве АЦП 2 может быть использован функционально законченный преобразователь типа 1113ПВ1, в котором тактовый вход соединен с выводом N11, а выход сигнала сопровождения (готовности) с выводом N17. При анализе временных характеристик под АЦП 2 следует подразумевать преобразователь время-код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор временных интервалов (варианты) | 2020 |

|

RU2753822C1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ | 2002 |

|

RU2229158C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| ДИСКРИМИНАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2002 |

|

RU2234729C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

Изобретение относится к области вычислительной техники и может быть использовано для анализа случайных процессов. Техническим результатом является расширение функциональных возможностей. Анализатор содержит оперативное запоминающее устройство, сумматор, три регистра, счетчик, аналого-цифровой преобразователь, триггер, три элемента 2И, два элемента 2ИЛИ, два элемента задержки и блок управления. 3 ил.

Статистический анализатор, содержащий оперативное запоминающее устройство, сумматор, три регистра, счетчик, аналого-цифровой преобразователь, триггер, три элемента 2И, два элемента 2ИЛИ, два элемента задержки и блок управления, при этом вход счетчика соединен с адресным входом оперативного запоминающего устройства, информационный вход которого соединен с выходом первого регистра, информационный вход которого соединен с выходом сумматора, первый вход которого соединен с информационным выходом оперативного запоминающего устройства, а второй вход сумматора служит входом задания единицы, выход переноса сумматора соединен с D-входом триггера, выход которого соединен с тактовым входом второго регистра, информационный вход которого объединен с адресным входом оперативного запоминающего устройства и подключен к информационному выходу аналого-цифрового преобразователя, выход готовности которого соединен с первым входом первого элемента 2ИЛИ, выход которого через первый и второй последовательно соединенные элементы задержки соединен с первым входом второго элемента 2ИЛИ, выход которого соединен с входом управления оперативного запоминающего устройства, тактовый вход первого регистра объединен с тактовым входом триггера и подключен к выходу первого элемента задержки, второй вход первого элемента 2ИЛИ соединен с выходом первого элемента 2И, первый вход которого объединен со счетным входом счетчика и подключен к выходу второго элемента 2И, первый вход которого объединен с первым входом третьего элемента 2И и служит тактовым входом анализатора, выход третьего элемента 2И соединен с тактовым входом аналого-цифрового преобразователя, информационный вход которого является информационным входом анализатора, входами запуска и обнуления которого служат соответствующие входы блока управления, первый выход которого соединен со вторым входом второго элемента 2И, второй выход блока управления соединен со вторым входом второго элемента 2ИЛИ, третий выход блока управления соединен со вторым входом третьего элемента 2И, четвертый выход блока управления соединен с управляющим входом счетчика, выход переполнения которого подключен к первому входу блока управления, пятый выход которого соединен со вторым входом первого элемента 2И, второй вход блока управления соединен с выходом триггера, обнуляющий вход которого объединен с обнуляющими входами счетчика и первого регистра и подключен к обнуляющему входу анализатора, информационным выходом которого является выход второго регистра.

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 1991 |

|

RU2015555C1 |

| Устройство для определения закона распределения | 1987 |

|

SU1520545A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| US 4534041 A, 06.08.1985. | |||

Авторы

Даты

2003-07-20—Публикация

2000-09-01—Подача