Изобретение относится к технике электроизмерений и может быть использовано для упреждающего контроля напряжения, например в автоматических системах контроля качества электрической энергии.

Известно устройство контроля уровня напряжения (Информационный листок N 74/0818), содержащее два пороговых элемента, настроенных на верхний и нижний пределы допуска контролируемого напряжения, схему совпадения, исполнительный орган.

Известное устройство имеет ограниченные функциональные возможности, обусловленные невозможностью осуществле- ния контроля уровней знакопеременного напряжения.

Наиболее близким по технической сущности к заявляемому изобретению следует считать устройство, описанное в а.с. СССР N 625167, кл. G 01 R 19/00, 1975, содержащее два пороговых элемента, настроенных на верхний и нижний пределы допуска контролируемого напряжения, два триггера, логическую схему совпадения, элемент запрета, исполнительный орган, генератор тактовых импульсов, дифференцирующую цепь и резистивный делитель опорного напряжения.

Прототип также имеет ограниченные функциональные возможности, так как не позволяет контролировать уровни знакопеременного напряжения. Этот недостаток объясняется тем, что пороговые элементы настроены только на положительные верхний и нижний пределы допуска контролируемого напряжения.

Цель изобретения - расширение функциональных возможностей за счет автоматического контроля знакопеременных, например синусоидальных, напряжений стабильной частоты.

Цель достигается тем, что в устройство для контроля напряжений, содержащее первый и второй компараторы, первый и второй триггеры и элемент совпадения, введены фильтр, нуль-орган, умножитель частоты, элемент ИЛИ, инвертор, третий триггер, двоичный счетчик, блок логики и две схемы сравнения кодов, первые информационные входы которых объединены между собой и подключены к выходу двоичного счетчика, входом присоединенного к выходу элемента совпадения, первый, второй и третий входы которого связаны соответственно с выходом третьего триггера, выходом инвертора и выходом умножителя частоты, входом объединенного с первыми входами нуль-органа, первого и второго компараторов и подключенного к выходу фильтра, вход которого является входом устройства, выходом объединенного с выходом блока логики, первый и второй входы которого связаны соответственно с инверсным выходом первого и прямым выходом второго триггеров, вход установки в ноль первого и второго триггеров соединен соответственно с выходом первой и выходом второй схем сравнения кодов, а входы установки в единичное состояние всех триггеров объединены между собой и подключены к выходу нуль-органа, причем вход установки в ноль третьего триггера объединен с входом инвертора и присоединен к выходу элемента ИЛИ, первый и второй входы которого связаны соответственно с выходом первого и выходом второго компараторов. Блок логики выполнен в виде четырех элементов И-НЕ, причем первые входы первого и второго элементов И-НЕ объединены между собой и являются первым входом блока логики, второй вход которого присоединен одновременно к первому входу третьего и второму входу второго элементов, выход последнего из которых подключен одновременно к вторым входам первого и третьего элементов, выход каждого из которых связан с соответствующим входом четвертого элемента, выходом объединенного с выходом устройства.

Сущность изобретения состоит в расширении функциональных возможностей устройства путем измерения значений углов от момента перехода положительной и отрицательной полуволн контролируемого напряжения до момента равенства контролируемого напряжения заданным соответственно положительному и отрицательному значениям напряжений.

Заявляемое техническое решение отличается от прототипа наличием новых блоков и элементов, а именно: фильтра, нуль-органа, умножителя частоты, элемента ИЛИ, инвертора, третьего триггера, двоичного счетчика, блока логики и двух схем сравнения кодов.

Эти отличия позволяют сделать вывод о соответствии заявляемого технического решения критерию "новизна".

Сравнение заявляемого технического решения с другими решениями показывает, что в научно-технической литературе не обнаружено устройств с такой совокупностью новых элементов и соответствующих связей. Таким образом, заявляемое техническое решение соответствует критерию "существенные отличия".

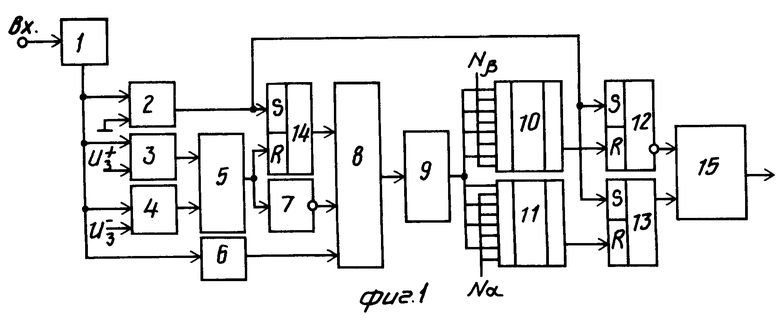

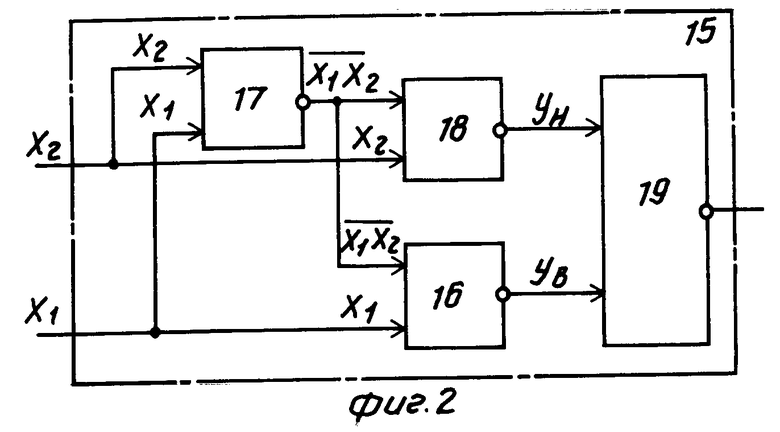

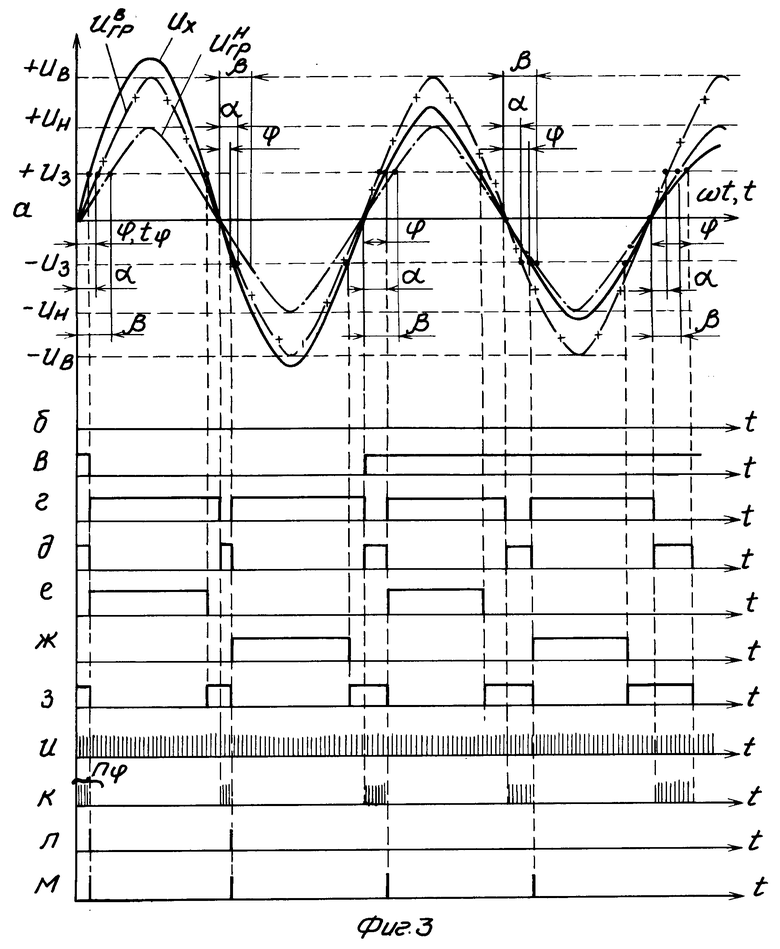

На фиг. 1 представлена функциональная схема устройства для упреждающего контроля напряжения; на фиг. 2 - функциональная схема блока логики; на фиг. 3 - временные диаграммы работы устройства.

Устройство (фиг. 1) содержит фильтр 1, нуль-орган 2, первый и второй компараторы 3 и 4, элемент ИЛИ 5, умножитель 6 частоты, инвертор 7, элемент 8 совпадения, двоичный счетчик 9, первую и вторую схемы 10 и 11 сравнения кодов, первый, второй и третий триггеры 12-14 и блок 15 логики, выполненный в виде четырех элементов И-НЕ 16-19.

Фильтр 1 предназначен для выделения из входного сигнала его первой гармонической составляющей синусоидальной формы. Вход фильтра 1 является входом устройства, а выход фильтра подключен одновременно к первым входам нуль-органа 2, компараторов 3, 4 и входу умножителя 6 частоты.

Нуль-орган 2 предназначен для формирования импульсов единичного уровня при каждом переходе синусоиды первой гармонической составляющей входного сигнала через ноль. Выход нуль-органа 2 связан одновременно с входами установки в единичное состояние триггеров 12-14.

Компараторы 3 и 4 предназначены для сравнения амплитуды первой гармонической составляющей напряжения входного сигнала с заданными значениями. Выходы компараторов 3 и 4 подключены к соответствующим входам элемента ИЛИ 5. Уставка срабатывания компаратора 3 соответствует заданному положительному значению напряжения, а уставка срабатывания компаратора 4 - заданному отрицательному значению напряжения.

Умножитель 6 частоты предназначен для умножения частоты входного сигнала. Коэффициент умножения умножителя 6 частоты выбран равным 36 ˙10S (где S - целое положительное число). Выход умножителя 6 частоты соединен с третьим входом элемента 8 совпадения.

Инвертор 7, предназначенный для инвертирования выходного сигнала элемента ИЛИ 5, входом объединен с входом установки в ноль третьего триггера 14 и подключен к выходу элемента ИЛИ 5, а выходом связан с вторым входом элемента 8 совпадения.

Элемент 8 совпадения, выполненный в виде логического элемента И, предназначен для пропуска на его выход счетных импульсов, поступающих по третьему входу, при одновременном наличии на втором и первом его входах разрешающих сигналов единичного уровня. Первый вход и выход элемента 8 связаны соответственно с выходом третьего триггера 14 и счетным входом двоичного счетчика 9.

Двоичный счетчик 9 предназначен для счета числа импульсов, поступивших на его счетный вход. Выход счетчика 9 соединен одновременно с первыми информационными входами схем 10, 11 сравнения кодов.

Схемы 10 и 11 сравнения кодов предназначены для сравнения цифрового кода контролируемого угла, присутствующего на кодовом выходе двоичного счетчика 9, с заданными кодами, пропорциональными соответственно верхнему и нижнему граничным значениям угла. Схемы 10 и 11 могут быть выполнены на основе известных (см. Б. И.Горшков. Элементы радиоэлектронных устройств. Справочник. М. : Радио и связь, 1988, с. 140, рис. 11.16) принципов построения аналогичных функциональных устройств. Выход первой схемы 10 и выход второй схемы 11 подключены соответственно к входу установки в ноль первого и второго триггеров 12 и 13.

Триггеры 12-14 выполнены в виде RS-триггеров.

Инверсный выход первого триггера 12 подключен к второму входу блока 15 логики, первый вход которого связан с прямым выходом второго триггера 13. Входы установки в единичное состояние триггеров 12-14 объединены между собой и подключены к выходу нуль-органа 2.

Блок 15 логики (фиг. 2) предназначен для формирования выходного сигнала устройства в зависимости от результата контроля. Блок 15 логики выполнен в виде четырех логических элементов И-НЕ 16-19. Первые входы первого и второго элементов 16 и 17 объединены между собой и являются первым входом блока 15 логики, второй вход которого присоединен одновременно к первому входу третьего и второму входу второго элементов И-НЕ 18 и 17. Выход второго элемента И-НЕ 17 подключен одновременно к вторым входам первого и третьего элементов 16 и 18, выход каждого из которых связан с соответствующим входом четвертого элемента И-НЕ 19, входом объединенного с выходом заявляемого устройства.

На фиг. 3 обозначено:

± Uв и ±Uн - верхний и нижний пределы допуска первой гармонической составляющей знакопеременного напряжения Ux;

Uгрв и Uгрн - верхняя и нижняя граничные синусоиды первой гармонической составляющей знакопеременного напряже- ния Ux;

+Uз и -Uз - положительное и отрицательное заданные значения напряжения срабатывания первого и второго компараторов 3 и 4 (см. на фиг. 1);

ϕ - измеряемый угол от момента перехода первой гармонической составляющей контролируемого напряжения через нуль до момента равенства ее значения заданным ±Uз напряжениям;

αиβ - заданные верхнее и нижнее значения измеряемого угла ϕ.

Заданные значения напряжения +Uз и -Uз выбирают ниже значений напряжений +Uн и -Uн соответственно вблизи уровня постоянной составляющей контролируемого напряжения.

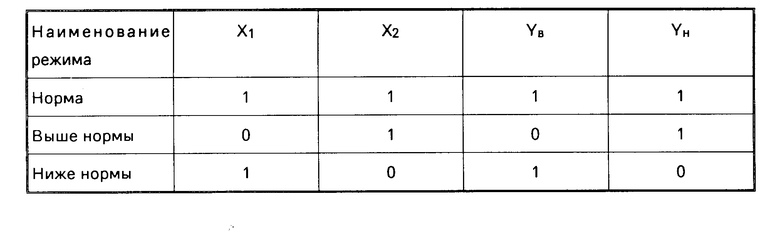

При нахождении первой гармонической составляющей напряжения Ux в пределах поля допуска (+Uн < Ux < + Uв либо -Uн < Ux< < -Uв), то есть при нахождении измеряемого ϕ угла в пределах от β до α , на выходе устройства сигнал отсутствует, а в случае выхода за границы поля допуска - имеет место наличие сигнала. Тогда решающее правило, реализуемое устройством, имеет вид

F(ϕ) =

(1) где F( ϕ) - выходной сигнал устройства, зависящий от текущего значения угла ϕ.

(1) где F( ϕ) - выходной сигнал устройства, зависящий от текущего значения угла ϕ.

С учетом значений логических переменных в режимах "Норма", "Выше" или "Ниже" нормы напряжения Ux, на основе известных методов логического синтеза (см. Поляков В. Е. и др. Теоретические основы построения логической части релейной защиты и автоматики энергосистем. М.: Энергия, 1979) и набора элементов И-НЕ функциональная схема блока 15 логики может быть представлена в виде, показанном на фиг. 2.

Выходные сигналы устройства в режимах "Норма", "Выше" или "Ниже" нормы могут быть представлены в виде

Fo(ϕ) = { ,

, };

};

Fв(ϕ) = { ,

, }; (2)

}; (2)

Fн(ϕ) = { ,

, }, где

}, где  - переменная, принимающая значения Х или

- переменная, принимающая значения Х или  .

.

Тогда значения логических переменных в отдельных режимах можно представить в виде, представленном в таблице. Кроме того, измеряемый угол ϕ связан с частотой измеряемого напряжения f выражением

ϕ=2πftϕ= или

или

tϕ=  (3) где f и Т - частота и период измеряемого сигнала;

(3) где f и Т - частота и период измеряемого сигнала;

tϕ- временной интервал, соответствующий углу ϕ (фиг. 3).

При квантовании временного интервала счетными импульсами будем иметь, что количество nϕ импульсов, попавших в интервал tϕ , будет

nϕ=  = tϕfсч (4) где fсч и Тсч - частота и период следования счетных импульсов.

= tϕfсч (4) где fсч и Тсч - частота и период следования счетных импульсов.

С целью уменьшения частотной погрешности будем выполнять заполнение временного интервала tϕ импульсами, пропорциональными частоте f входного сигнала.

Частота f измеряемого сигнала, которая может быть произвольной, связана с частотой fсч следования счетных импульсов зависимостью

fсч = Кf, (5) где К - численный коэффициент, представляющий коэффициент умножения частоты.

Тогда, согласно (4), имеет

nϕ = tϕ Kf (6) или, после подстановки tϕ из (3) в (6), имеем

nϕ=  k (7)

k (7)

Таким образом, количество импульсов nϕ , заполняющих интервал tϕ, является функцией измеряемого угла ϕ , коэффициента К и не зависит от частоты f измеряемого сигнала.

Устройство для упреждающего контроля напряжения работает следующим образом.

В исходном состоянии контролируемое напряжение на входе устройства отсутствует, двоичный счетчик 9 и триггеры 12-14 установлены в ноль.

В режиме измерения контролируемое напряжение подается на вход устройства. При этом на выходе фильтра 1 появляется первая гармоническая составляющая Ux напряжения (фиг. 3а), амплитуда которой пропорциональна контролируемому напряже - нию, а ее форма синусоидальна.

При возрастании амплитуды напряжения Ux (первый полупериод на фиг. 3а) и каждом переходе синусоиды напряжения через ноль на выходе нуль-органа 2 будет появляться импульс (фиг. 3б) уровня логической единицы, переводящий триггеры 12-14 по S-входу в единичное состояние (фиг. 3в,г,е), подготавливая их к приему информации по R-входу. Поскольку на выходах компараторов 3 и 4 сигнал нулевого уровня (фиг. 3е,ж), то на выходе инвертора 7 будет присутствовать сигнал логической единицы (фиг. 3з), который поступит на второй вход элемента 8 совпадения. На первом входе элемента 8 будет присутствовать сигнал логической единицы, поступивший с выхода триггера 14. Одновременно с этим первая гармоническая составляющая напряжения, изменяющаяся с частотой f, поступает на вход умножителя 6 частоты, на выходе которого будут появляться счетные импульсы с частотой следования fсч = Кf, поступающие на третий вход элемента 8 (фиг. 3и). Эти импульсы будут повторяться на выходе элемента 8 и поступать на счетный вход двоичного счетчика 9. В момент, когда напряжение Uх станет равным заданному положительному значению +Uз (либо -Uз, см. второй полупериод на фиг. 3а), сработает компаратор 3 (либо компаратор 4 для отрицательной полуволны) и на его выходе появится сигнал логической единицы. Этот сигнал, пройдя через элемент ИЛИ 5, переведет по R-входу триггер 14 в нулевое состояние и запретит прохождение счетных импульсов с выхода умножителя 6 частоты через элемент 8 совпадения. Одновременно с этим сигнал логической единицы, присутствующий на выходе элемента ИЛИ 5, после инвертирования инвертором 7 поступит на второй вход элемента 8 совпадения, имея уровень логического нуля. Таким образом, в счетчике 9 будет накоплено число nϕимпульсов (фиг. 3 к ) и на его кодовом выходе будет зафиксирован на код Nϕ , пропорциональный измеряемому углу ϕ .

Цикл измерения угла завершен.

В цикле сравнения угла код Nϕ поступает одновременно на первые информационные входы схем 10 и 11 сравнения кодов. При этом на втором информационном входе схемы 10 и втором информационном входе схемы 11 присутствуют соответственно заданные цифровые коды NαиNβ . Причем код Nα пропорционален верхнему граничному значению α измеряемого угла ϕ, а код Nβ - нижнему граничному значению β измеряемого угла.

Импульс на выходе схемы 10 либо схемы 11 появится только в случае, если код Nϕ окажется меньше заданного кода NαлибоNβ соответственно.

В случае возрастания амплитуды напряжения Ux по результатам сравнения (см. первый период на фиг. 3а) цифровой код Nϕ будет меньше заданных кодов NαиNβ , поэтому на выходе схем 10 и 11 появится импульс (фиг. 3л,м), который переведет триггеры 12 и 13 соответственно в нулевое состояние. При этом с инверсного выхода триггера 12 сигнал единичного уровня (фиг. 3г) поступит на второй вход блока 15 логики, а на первый вход блока 15 - сигнал нулевого уровня, присутствующий на прямом выходе триггера 13 (фиг. 3в). Цикл сравнения завершен.

После логических преобразований сигналов, поступивших по входам блока 15, в соответствии с выражением (2) и таблицей на выходе устройства появится сигнал логической единицы, фиксирующий событие предстоящего превышения амплитуды напряжением Ux верхнего предела допуска ±Uн (то есть до выполнения равенства Ux = ±Uв).

При предстоящем нахождении напряжения Ux в пределах допуска (режим "Норма", второй период на фиг. 3а), когда ±Uн < Ux <± Uв, цикл измерения угла ϕ аналогичен рассмотренному.

В цикле сравнения кода Nϕ с заданными кодами NαиNβ сигнал логической единицы на выходе схемы 11 сравнения кодов будет отсутствовать, поскольку Nϕ > Nα . Следовательно, триггер 13 сохранит единичное состояние, а триггер 12 изменит состояние на нулевое. При этом с прямого выхода триггера 13 и инверсного выхода триггера 12 на входы блока 15 логики поступит сигнал логической единицы.

После логических преобразований сигналов в блоке 15 на выходе устройства будет присутствовать сигнал нулевого уровня, фиксирующий событие предстоящего нахождения амплитуды напряжения Ux в пределах поля допуска (± Uн < Ux <± Uв).

При предстоящем снижении амплитуды напряжения (см. положительную полуволну третьего периода на фиг. 3а) ниже границы ±Uн поля допуска (режим "Ниже" нормы), когда Ux < ±Uн, цикл измерения угла ϕ аналогичен рассмотренному.

В цикле сравнения кода Nϕ с заданными кодами NαиNβ на выходе схем 10 и 11 будет присутствовать логический ноль и триггеры 12 и 13 сохраняют единичное состояние. При этом с инверсного выхода триггера 12 на второй вход блока 15 логики поступит сигнал нулевого уровня, а на первый вход блока 15 - единичный сигнал, присутствующий на прямом выходе триггера 13. Цикл сравнения завершен.

После логических преобразований сигналов в блоке 15 на выходе устройства будет присутствовать сигнал логической единицы, фиксирующий событие предстоящего снижения амплитуды напряжения Ux ниже предела поля допуска ±Uн (то есть, до выполнения равенства Ux = ±Uн).

Технико-экономический эффект заявляемого устройства заключается в том, что данное устройство позволяет контролировать предстоящее изменение амплитуды напряжения не только в области положительных значений напряжения Ux, но и в области отрицательных значений, что подтверждает достоверность достижения цели, заключающейся в расширении функциональных возможностей устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР КАЧЕСТВА ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1993 |

|

RU2096788C1 |

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2000 |

|

RU2171995C1 |

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОКАЗАТЕЛЕЙ КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1991 |

|

RU2022348C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОСИТЕЛЬНЫХ УРОВНЕЙ ПОБОЧНЫХ КОЛЕБАНИЙ РАДИОПЕРЕДАТЧИКОВ | 1990 |

|

RU2033618C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2001 |

|

RU2189047C1 |

| Следящий электропривод | 1985 |

|

SU1259207A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2005 |

|

RU2279094C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1995 |

|

RU2121753C1 |

Использование: контроль напряжения, например в автоматических системах контроля качества электрической энергии. Сущность изобретения: устройство для контроля отклонения переменного напряжения содержит фильтр, нуль-орган, два компаратора, элемент ИЛИ, умножитель частоты, инвертор, элемент совпадения, двоичный счетчик, два элемента сравнения кодов, три триггера и логический блок, выполненный на четырех элементах И-НЕ. 1 з.п. ф-лы, 3 ил., 1 табл.

| Авторское свидетельство СССР N 1486944, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-02-20—Публикация

1990-10-03—Подача