Изобретение относится к микроэлектронике, в частности к большим интегральным схемам (БИС), и может быть использовано при конструкции базовых матричных кристаллов (БМК).

Известна ячейка базового матричного кристалла, включающая множество компонентов, относительное расположение которых обеспечивает возможность создания на их основе с помощью межсоединений любого элемента из базового набора логических схем и последующего формирования большой схемы путем создания межсоединений между подобными ячейками [1]

Однако известная ячейка не обладает достаточной степенью интеграции и помехозащищенностью.

Наиболее близкой по технической сущности является ячейка базового матричного кристалла, содержащая набор компонентов, выполненных в полупроводниковой подложке, n слоев металлизации с размещенными шинами питания, входными и выходными контактами и межсоединениями одного из набора логических элементов, выполненного в виде двухуровневых каскадных токовых ключей с дифференциальным управлением от соответствующих входных контактов верхнего и нижнего уровней, верхний уровень которых подключен через нагрузочные резисторы к первой шине питания, вторая шина питания соединена с вторым уровнем через источник тока, первые входы питания входных эмиттерных повторителей нижнего уровня соединены с первой шиной питания [2]

Однако одним из трудных аспектов схем с парафазной передачей сигнала, с которым приходится сталкиваться в области матричных схем, является то, что эти схемы являются дифференциальными, что означает, что вместо одной сигнальной линии, передающей сигнал по кристаллу, необходимо использовать две. Это касается проблемы плотности. В известном техническом решении шины располагаются в разных слоях металлизации и в верхних слоях занимают площадь, которая могла бы использоваться для трассировки связей между ячейками. В известной ячейке предусмотрена специальная свободная от компонентов зона, предназначенная для проведения линий трассировки, что также оказывает отрицательное влияние на плотность интеграции. Существуют также большие сложности с многоуровневыми парафазными сигналами, относящиеся к программам автоматизированного проектирования матричных кристаллов.

Другими трудными аспектами являются мощность потребления базовых элементов и их помехозащищенность, так как мощность потребления является одним из определяющих факторов, ограничивающих степень интеграции, а величина помехозащищенности элементов оказывает непосредственное влияние на функционирование всей схемы.

Технической задачей изобретения является повышение степени интеграции, помехозащищенности и снижение потребляемой мощности.

Достигается это тем, что в ячейке базового матричного кристалла, содержащей набор компонентов, выполненных в полупроводниковой подложке, n слоев металлизации с размещенными шинами питания, входными и выходными контактами и межсоединениями одного из набора логических элементов, выполненного в виде двухуровневых каскадных токовых ключей с дифференциальным управлением от соответствующих входных контактов верхнего и нижнего уровней, верхний уровень которых подключен через нагрузочные резисторы к первой шине питания, вторая шина питания соединена с вторым уровнем через источник тока, первые входы питания входных эмиттерных повторителей нижнего уровня соединены с первой шиной питания, шины питания расположены в нижнем слое металлизации, входные и выходные контакты соответствующих дифференциальных сигналов логического элемента выведены по крайней мере в один из вышележащих слоев металлизации и расположены в соседних по диагонали дискретах координатной сетки автоматической трассировки, причем выходы верхнего уровня токовых ключей соединены с соответствующими выходными контактами дифференциальных сигналов логического элемента, а вторые входы питания входных эмиттерных повторителей нижнего уровня подключены к второй шине питания.

Сущность изобретения заключается в том, что предлагается нескоммутированная топологическая ячейка, в которой в качестве базовой схемотехники элементов применены схемы каскадных дифференциальных токовых ключей, отличительными особенностями которых являются парафазный прием и передача сигнала, а также использование коллекторного выхода, причем входные и выходные контакты соответствующих сигналов логического элемента выведены в один из вышележащих слоев металлизации и расположены в соседних по диагонали дискретах координатной сетки, что в конечном итоге ведет к уменьшению паразитных наводок сигналов в связях и повышению помехозащищенности схем. Такие схемы могут функционировать при перепаде логического сигнала в несколько раз меньше, чем в схемах традиционной ЭСЛ логики. В данном изобретении компоненты топологической ячейки обеспечивают величину логического перепада порядка 200 мВ. Обычно элементы, которые могут быть реализованы на топологической ячейке, образуют некоторый относительно стандартный набор-библиотеку логических элементов, и используются в системах автоматизированного проектирования БИС. Расположение компонентов в предлагаемой ячейке и рисунки металлизации элементов таковы, что они позволяют спроектировать на ее основе базовый матричный кристалл типа "море вентилей". При этом топологические ячейки располагаются на одной из координат вплотную друг к другу, что дает максимальное использование площади подложки. Кроме того, специальные части металлизации элементов при таком расположении ячеек на подложке стыкуются между собой и образуют сквозные шины питания на кристалле. Шины питания располагаются в нижнем слое металлизации, что позволило получить дополнительную площадь под трассировку в верхних слоях металла, т.е. повысить плотность интеграции.

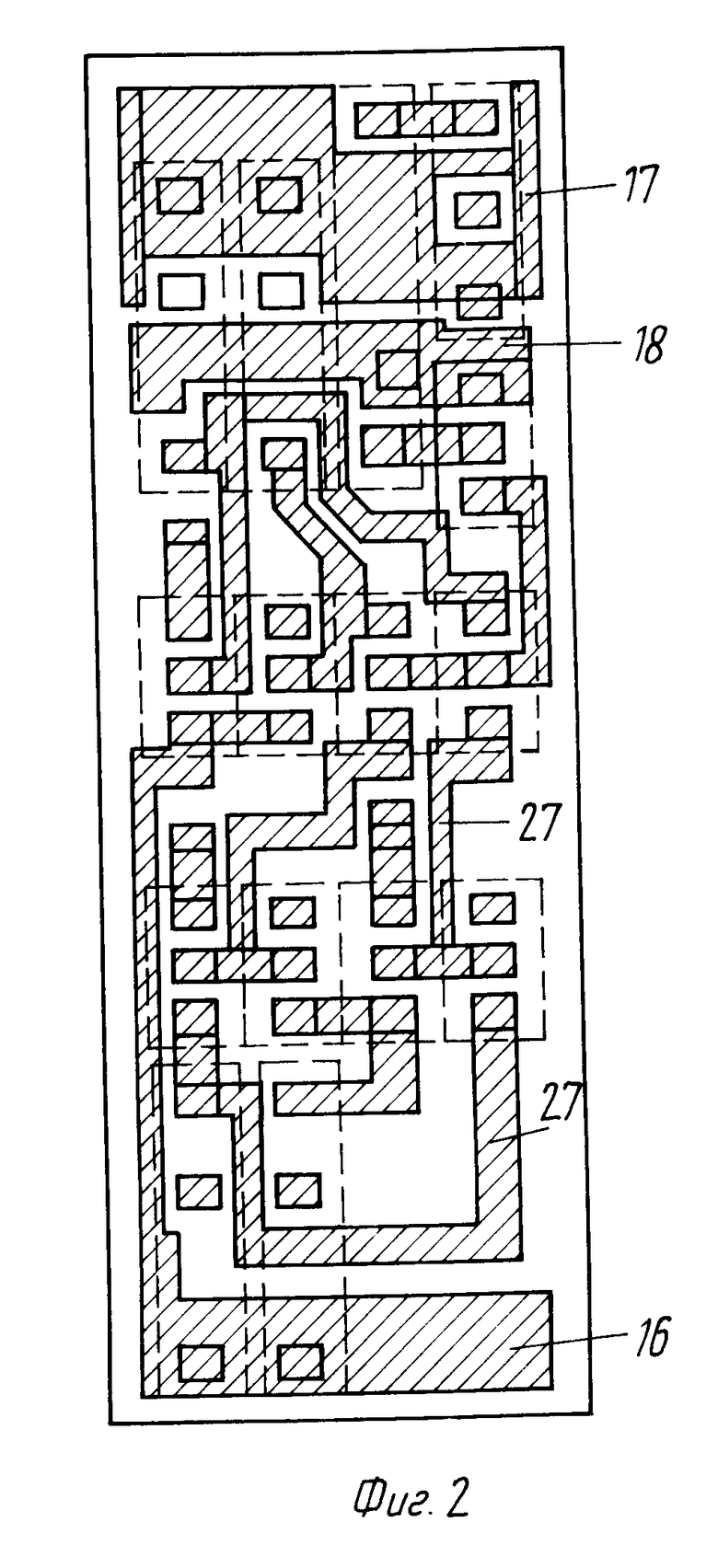

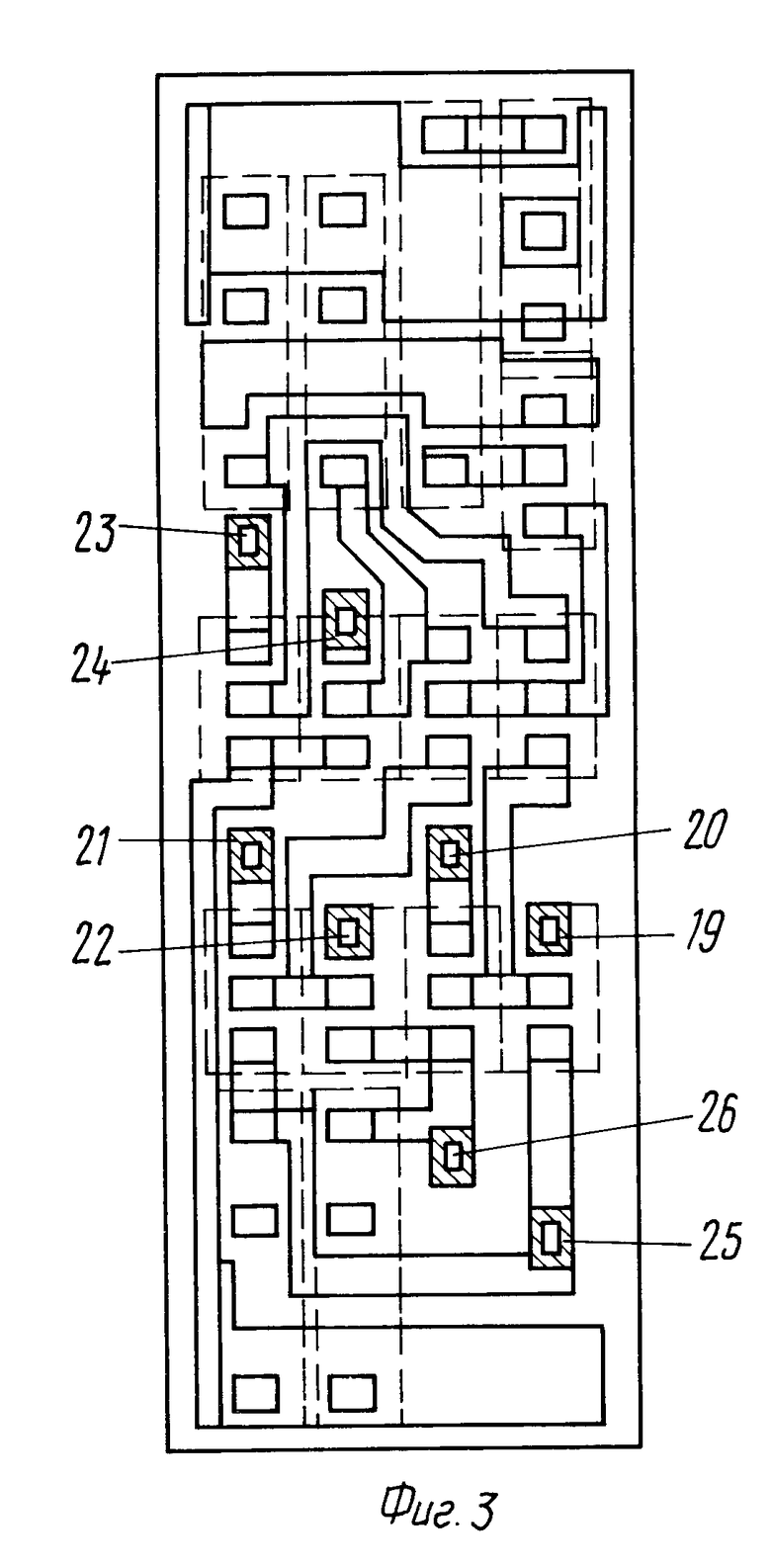

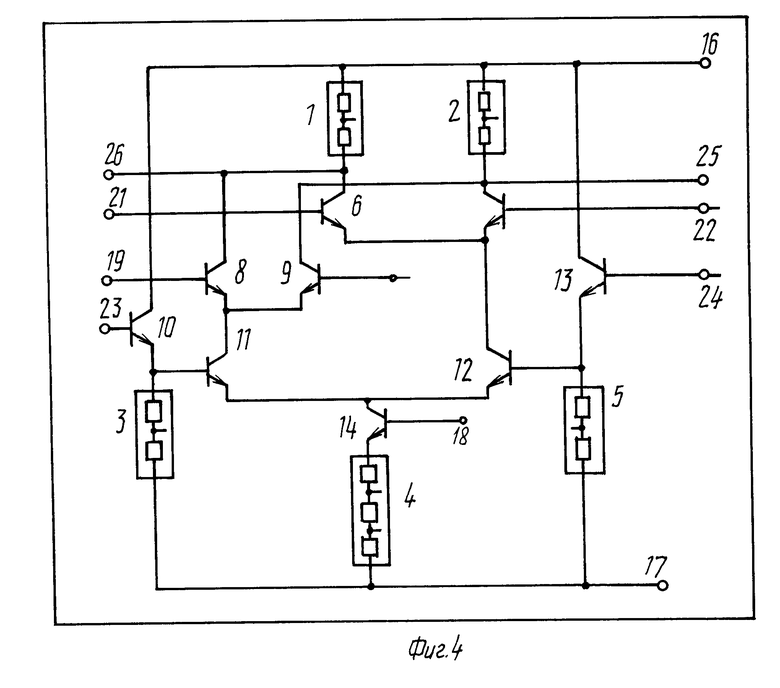

На фиг. 1 представлена полупроводниковая подложка с набором компонентов; на фиг. 2 и 3 вид ячейки с набором компонентов с первым и вторым слоями металлизации соответственно (заштрихованные поверхности); на фиг. 4 принципиальная электрическая схема логического элемента.

Ячейка базового матричного кристалла содержит набор компонентов нагрузочные резисторы 1 и 2, резисторы 3-5, транзисторы 6-14, выполненные в полупроводниковой подложке 15, первую и вторую шины 16 и 17 питания и шину 18 опорного напряжения источника тока, расположенные в первом слое металлизации, входные контакты 19 и 20, 21 и 22, 23 и 24, выходные контакты 25 и 26 дифференциальных сигналов A/-A/, B/-B/, выведенные во второй слой металлизации. Входные контакты 19 и 20, 21 и 22, 23 и 24 и выходные контакты 25 и 26 расположены в соседних по диагонали дискретах координатной сетки автоматической трассировки. Транзисторы 6 и 7, 8 и 9 образуют верхний уровень дифференциального каскадного токового ключа, а транзисторы 11 и 12 нижний уровень. Транзистор 10 с резистором 3 и транзистор 13 с резистором 5 представляют эмиттерные повторители нижнего уровня, входы питания которых соединены с шинами 16 и 17 питания. Транзистор 14 с резистором 4 и шиной 18 опорного напряжения образует источник тока. Коллекторы транзисторов 6 и 7 через нагрузочные резисторы 1 и 2 соединены с первой шиной 16 питания и непосредственно с соответствующими выходными контактами 26 и 25. В первом слое металлизации реализованы связи 27 между компонентами.

Шины 16 и 17 питания выполнены в первом слое металлизации таким образом, что при расположении топологических ячеек по одной из координат вплотную друг другу, части шин 16 и 17 стыкуются между собой, образуя сквозные шины питания на кристалле. Это позволило максимально использовать площадь подложки и получить дополнительную площадь под трассировку в верхних слоях металлизации, что в конечном итоге повысило степень интеграции.

Расположение входных контактов 19 и 20, 21 и 22, 23 и 24, выходных контактов 25 и 26 парафазных сигналов в соседних по диагонали дискретах координатной сетки, в которой ведется автоматическая трассировка связей БИС, позволяет существенно упростить программы, трассировки, так как дает возможность использовать имеющиеся программы однофазной трассировки с последующим "разваливанием" проведенной связи на две части. В силу того, что такие полученные двойные связи идут всегда в соседних дискретах, и трассировка двух смежных слоев металлизации ведется, как правило, ортогонально, такое расположение входных контактов 19-24 и выходных контактов 25 и 26 позволяет уменьшить паразитные наводки сигналов в связях и приводит к улучшению помехозащищенности схем.

Принципиальная электрическая схема логического элемента, представленная на фиг. 4 в качестве примера, реализует функцию мультиплексоров 2х1 Z=Ax(-S)+BS без использования выходных эмиттерных повторителей верхнего уровня, которые практически не дают усиления по току на высокой частоте. Непосредственное подсоединение коллекторов транзисторов 6-9 верхнего уровня дифференциального токового ключа к выходным контактам 25 и 26 позволяет получить следующие преимущества: уменьшено минимальное количество компонентов, необходимых для реализации базовой схемы (9 транзисторов вместо 11 и 5 резисторов вместо 9), что дает экономию площади, отводимой под ячейку, и соответственно повышает плотность кристалла; уменьшено количество необходимых напряжений питания (необходимы только напряжение "земли", одно напряжение питания и опорное напряжение для схем источников тока, вместо напряжений "земли", двух питающих напряжений и одного напряжения Uв в традиционной схеме), как следствие этого, уменьшается количество шин на кристалле, предназначенных для разводки питания; кроме того, уменьшено падение напряжения на токовом дереве до 3 В вместо 3,6 В, благодаря этим мерам показатель качества улучшается примерно в 1,5-2 раза по сравнению с прототипом, который, в свою очередь, имеет показатель качества в 2-3 раза лучше, чем у ЭСЛ схем, другими словами, при одинаковом быстродействии мощность потребления по сравнению с прототипом уменьшена в 1,5-2.

Использование в качестве базовой схемотехники каскадных дифференциальных токовых ключей с парафазным приемом и передачей сигнала и использование коллекторного выхода позволяет функционировать этим схемам при перепаде логического сигнала в несколько раз меньшим, чем в схемах с традиционной ЭСЛ логикой, в данном случае компоненты ячейки обеспечивают логический перепад 200 В.

Резисторы с 1-5 выполнены составными с несколькими выводами. Это дает возможность получать несколько градаций мощности одного и того же элемента, что позволяет снижать задержки в критической цепи и экономить мощность за счет тех частей схемы (большой), где не требуется максимальное быстродействие. В целом возможность выбора мощности логических элементов позволяет более гибко варьировать мощность всего кристалла и в конечном итоге добиться более высокой степени интеграции за счет использования большего количества маломощных элементов.

При описании схемы принято, что уровню логической "1" соответствует более отрицательный уровень логического сигнала (т.е. принята "негативная" логика). Подача одинаковых уровней на два контакта одного парафазного входа запрещена.

При подаче напряжения питания на шины 16-18 при условии, что на входной контакт 23 подан сигнал лог."0", а на входной контакт 24 подан сигнал лог. "1", сигнал лог."0" через схему сдвига уровня, представляющую собой эмиттерный повторитель, выполненный на транзисторе 10 и резисторе 3, поступает на базу транзистора 11. Соответственно, сигнал лог."1" через эмиттерный повторитель, выполненный на транзисторе 13 и резисторе 5, поступает на базу транзистора 12, который вместе с транзистором 11 образует схему дифференциального токового ключа. Таким образом, база транзистора 11 оказывается смещенной в положительном направлении на величину Uлог относительно базы транзистора 12, где Uлог. величина логического перепада, равная Uлог."1" Uлог."0". При таком соотношении потенциалов транзистор 11 открыт, а транзистор 12 закрыт и ток Iо источника тока, выполненного на транзисторе 14, течет через транзистор 11 в дифференциальный токовый ключ, выполненный на транзисторах 8 и 9, т.е. ключ, выполненный на транзисторах 6 и 7, оказывается обесточен. При подаче на контакт 19 уровня лог."1", а на входной контакт 20 уровня лог. "0", транзистор 8 открыт, транзистор 9 закрыт, и ток источника Iо через транзистор 9 поступает в резистор 2, на котором выделяется напряжение, которое подается непосредственно на выходной контакт 25 элемента и равное лог."1", так как величины резисторов 1 и 2 равны. Резистор 1 в это время обесточен и потенциал на выходном контакте 26 элемента равен лог. "0". Таким образом, при подаче на входной контакт 23 лог. "0" данная схема реализует логическую функцию "Z"="A".

При подаче на входной контакт 23 лог. "1" и на входной контакт 24 лог. "0" ток источника тока течет в ключ, выполненный на транзисторах 6 и 7. Ключ на транзисторах 8 и 9 обесточен, работа ключа на транзисторах 6 и 7 протекает аналогично работе ключа на транзисторах 8 и 9, схема выполняет логическую функцию "Z"="B".

Таким образом относительно входных контактов 23, 19 и 21 данный элемент реализует логическую функцию Z=Ax(-S)+BxS, т.е. функцию мультиплексора.

Таким образом, изобретение позволяет получить ячейку БМК с повышенной степенью интеграции, помехозащищенности и сниженной потребляемой мощностью.

Элементы, которые могут быть реализованы на ячейке, образующие некоторый стандартный набор библиотеку логических элементов используются в системах автоматического проектирования БИС и позволяют спроектировать базовый матричный кристалл типа "море вентилей". При этом расположение ячеек вплотную друг к другу дает максимальное использование площади подложки, что вместе с особым расположением и выполнением глобальной системы шин питания позволяет значительно повысить плотность компоновки, а особенности выполнения электрической схемы логического элемента дают возможность улучшить электрические параметры ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходной формирователь импульсов | 1991 |

|

SU1798898A1 |

| Выходной формирователь | 1989 |

|

SU1725379A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| Амплитудный формирователь | 1989 |

|

SU1698964A1 |

| ОПТИЧЕСКОЕ ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ МАТРИЦ | 1994 |

|

RU2079873C1 |

| М-S-триггер | 1990 |

|

SU1799495A3 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037187C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| ОПТИЧЕСКИЙ МНОГОКАНАЛЬНЫЙ АССОЦИАТИВНЫЙ КОРРЕЛЯТОР | 1992 |

|

RU2037188C1 |

Использование: в микроэлектронике. Сущность изобретения: ячейка содержит набор компонентов, выполненных в полупроводниковой подложке, n-слоев металлизации с размещенными шинами питания, причем шины питания расположены в нижнем слое металлизации. Входные и выходные контакты соответствующих дифференциальных сигналов логического элемента выведены по крайней мере в один из вышележащих слоев металлизации и расположены в соседних по диагонали дискретах координатной сетки автоматической трассировки. Вторые входы питания входных эмиттерных повторителей нижнего уровня подключены к второй шине питания. 4 ил.

ЯЧЕЙКА БАЗОВОГО МАТРИЧНОГО КРИСТАЛЛА, содержащая набор компонентов, выполненных в полупроводниковой подложке, n слоев металлизации с размещенными шинами питания, входными и выходными контактами и межсоединениями одного из набора логических элементов, выполненного в виде двухуровнего каскодного токового ключа с дифференциальным управлением от соответствующих входных контактов верхнего и нижнего уровней, верхний уровень токового ключа подключен через нагрузочные резисторы к первой шине питания, вторая шина питания соединена с вторым уровнем через источник тока, первые входы питания входных эмиттерных повторителей нижнего уровня соединены с первой шиной питания, отличающаяся тем, что шины питания расположены в нижнем слое металлизации, входные и выходные контакты соответствующих дифференциальных сигналов логического элемента выведены по крайней мере в один из вышележащих слоев металлизации и расположены в соседних по диагонали дискретах координатной сетки автоматической трассировки, причем выходы верхнего уровня токового ключа соединены с соответствующими выходными контактами дифференциальных сигналов логического элемента, а вторые входы питания входных эмиттерных повторителей нижнего уровня подключены к второй шине питания.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ПРИБОР ДЛЯ КОНТРОЛЯ толщины НЕМАГНИТНЫХ | 0 |

|

SU255589A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-05-10—Публикация

1992-11-27—Подача