Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности.

Известно устройство для нормализации и округления вещественных чисел, содержащее входные регистры сумматора, регистр выдвинутых разрядов, нормализатор результатов, узел формирования сигналов округления, выходной регистр [1].

Недостатком устройства является недостаточная точность при обработке, так как при операндах формата 64-го разряда мантисса имеет всего 52 разряда. Кроме того, невозможна обработка операндов формата 32.

Наиболее близким по технической сущности к изобретению является устройство для нормализации и округления вещественных чисел, содержащее три входных регистра, сумматор мантисс, узел управления, регистр, нормализатор результата, выходной регистр [2].

Недостатками этого устройства являются недостаточная точность вычислений и наличие ошибки, накапливаемой из-за округления вещественных чисел.

Целью изобретения является повышение точности и уменьшение ошибки вычислений.

Сущность изобретения заключается в изменении коммутации сигналов на входе сумматора мантисс за счет подключения второго входного регистра к первому входу сумматора, при этом в сумматор попадает старшая выдвинутая за разрядную сетку при выравнивании порядков тетрада, и в симметрии положительной и отрицательной погрешности при округлении за счет выполнения узла формирования сигнала округления со сложной логической функцией.

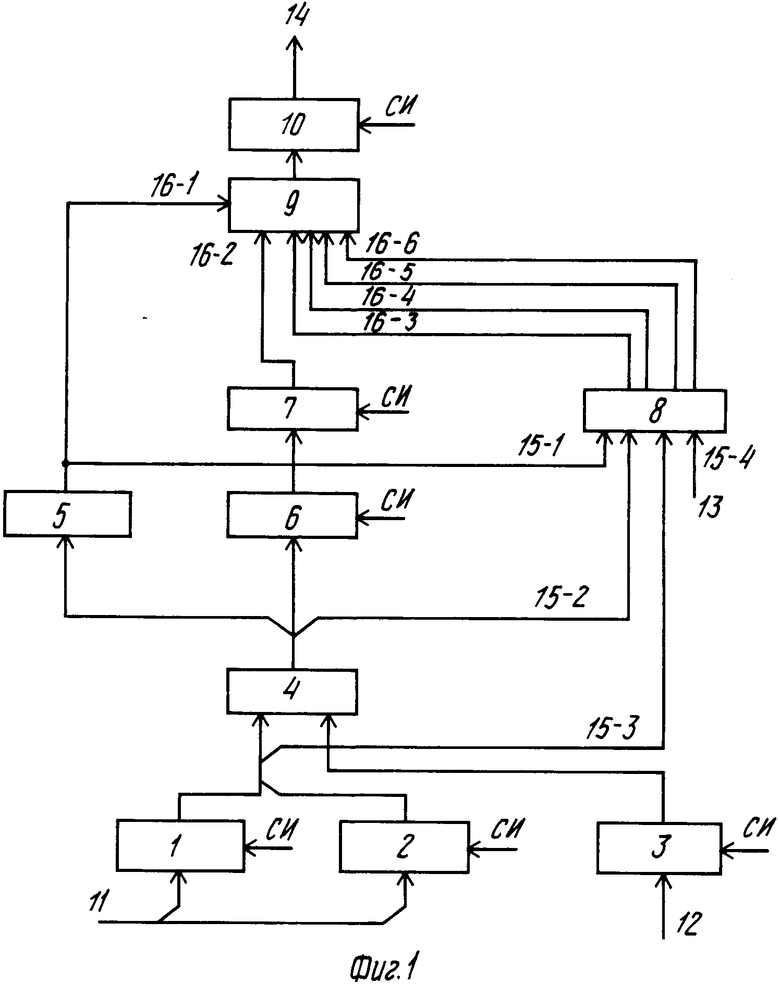

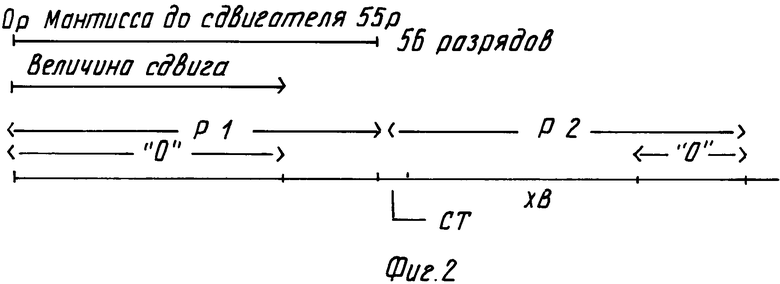

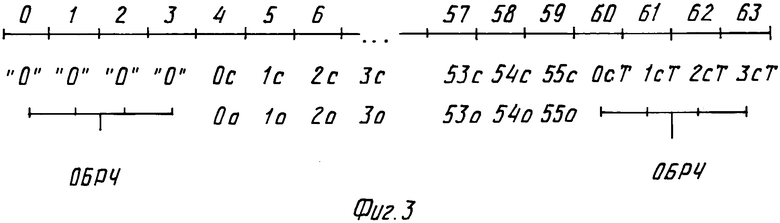

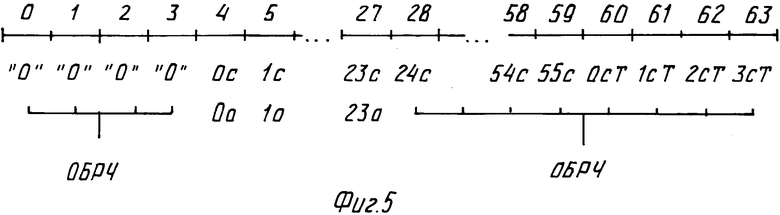

На фиг.1 представлена блок-схема устройства для нормализации и округления вещественных чисел; на фиг. 2 показано формирование полей на входе устройства при формате операнда 64; на фиг.3 представлена подача слагаемых на сумматор мантисс при формате операнда 64; на фиг.4 - формирование полей на входе устройства при формате операнда 32; на фиг.5 - подача слагаемых на сумматор мантисс при формате операнда 32.

Устройство содержит первый, второй и третий входные регистры 1, 2 и 3, сумматор 4 мантисс, узел 5 управления, дополнительный регистр 6, регистр 7, узел 8 формирования сигнала округления, нормализатор 9 результата, выходной регистр 10. В устройстве имеются входная шина 11 мантиссы первого числа (из сдвигателя), входная шина 12 мантисс второго числа (с меньшим порядком с возможностью обращения), входная шина 13 сигнала обращения мантиссы, выходная шина 14 результата устройства. Узел 8 формирования сигнала округления имеет управляющий вход 15-1, первый информационный вход 15-2, второй информационный вход 15-3, третий информационный вход 15-4. Нормализатор 9 результата имеет управляющий вход 16-1, первый, второй, третий, четвертый и пятый информационные входы 16-2, 16-3, 16-4, 16-5 и 16-6.

Входная шина 11 соединена через регистры 1, 2 с первым информационным входом сумматора 4 мантисс и с входом 15-3 узла 8 формирования сигнала округления. Входная шина 12 через регистр 3 соединена с вторым информационным входом сумматора 4 мантисс. Выход сумматора мантисс подключен к входу узла 5 управления, к входу дополнительного регистра 6 и к входу 15-2 узла 8 формирования сигнала округления. Выход дополнительного регистра 6 подключен через регистр 7 к входу 16-2 нормализатора 9 результата. Входная шина 13 сигнала обращения мантиссы соединена с входом 15-4 узла 8 формирования сигнала округления. Выход узла 5 управления подключен к управляющему входу 15-1 узла 8 формирования сигнала округления и к управляющему входу 16-1 нормализатора 9 результата. Первый, второй, третий и четвертый выходы узла 8 формирования сигнала округления соединены соответственно с входами 16-3, 16-4, 16-5 и 16-6 нормализатора 9 результата. Выход нормализатора результата подключен к входу выходного регистра 10. Выход выходного регистра является выходной шиной 14 результата устройства.

Сумматор 4 мантисс может быть выполнен как аналогичное устройство в прототипе.

Узел 5 управления нормализатором по сборкам нулей, поступающим из сумматора 4 мантисс, формирует код сдвига для нормализатора 9 результата. Если при суммировании мантисс было переполнение, то старшая сборка нулей равна единице (ОСБН = 1), вырабатывается код сдвига СДН = 0000 и в нормализаторе 9 происходит сдвиг мантиссы на одну тетраду вправо, если нормализация результата не требуется (ОСБН = 0, 1СБН = 1), то вырабатывается код сдвига СНД = 0001 и мантисса проходит через нормализатор 9 без изменений, вообще, код сдвига равен числу старших нулевых тетрад суммы мантисс. Формирование разрядов кода сдвига описывается формулами

8СДН = -0СБН* - 1СБН* - 2СБН* - 3СБН* - 4СБН* - 5СБН* - 6СБН* - 7СБН;

4СДН = -0СБН* - 1СБН* - 2СБН* - 3СБН* + (4СБН + 5СБН + 6СБН + 7СБН 3 - 8СБН* - 9СБН* - 10СБН* - 11СБН);

2СДН = (0СБН + 1СБН + 2СБН + 3СБН)* - 0СБН* - 1СБН +

-0СБН* - 1СБН* - 2СБН* - 3СБН* (4СБН + 5СБН + 6СБН + 7СБН)* - 4СБН* - 5СБН +

-0СБН* - 1СБН* - 2СБН* - 3СБН* - 4СБН* - 5СБН* - 6СБН* - 7СБН* (8СБН + 9СБН + 10СБН + 11СБН)*- 8СБН* - 9СБН +

-0СБН* - 1СБН* - 2СБН* - 3СБН* - 4СБН* - 5СБН* - 6СБН* - 7СБН*

-8СБН* - 9СБН* - 10СБН* - 11СБН* - - 12СБН* - 13СБН;

1СДН = (0СБН + 1СБН + 2СБН + 3СБН)* (-0СБН* 1СБН + -0СБН* - 2СБН) +

-0СБН* - 1СБН* - 2СБН* - 3СБН* (4СБН + 5СБН + 6СБН - 7СБН)* (-4СБН* 5СБН + -4СБН* - 6СБН) +

-0СБН* - 1СБН* - 2СБН* - 3СБН* - 4СБН* - 5СБН* - 6СБН* - 7СБН* (8СБН + 9СБН + 10СБН + 11СБН)*

(-8СБН* 9СБН + -8СБН* - 10СБН) +

-0СБН* - 1СБН* - 2СБН* - 3СБН* - 4СБН* - 5СБН* - 6СБН* - 7СБН* - 8СБН* - 9СБН* - 10СБН* - 11СБН* (-12СБН* 13СБН + - 12СБН* - 14СБН).

Нормализатор 9 результата представляет собой двухуровневый сдвигатель влево и вправо, здесь одновременно со сдвигом производится округление в 63-м разряде при формате 64 или в 31-м разряде при формате 32.

Работа 31-го и 63-го разрядов описывается формулами

31НР = 31НР2* - ОКР32 + ОКР32* ЕОКР32;

62НР = 63НР2* - ОКР64 + ОКР64* ЕОКР64, где 31НР2 и 63НР2 - разряды после второго уровня нормализатора 9 результата.

Узел 8 формиpования сигнала округления вырабатывает сигналы необходимости округления ОКР и сигналы способа округления БОКР.

Если операнды имеют формат 64,

ОКР64 = ХВ + СТ* -НОР + 14 СБН* ПРП;

-ЕОКР64 = ОБРЧ (-15СБН + НОР* ХВ).

Если операнды имеют формат 32,

ОКР32 = ХВ + 6СБН*ПРП + 7СБН* - НОР + МЛ 32;

ЕОКР32 = МЛ32 + 7СБН* -НОР, где СТ - информация о наличии хотя бы одной единицы в старшей выдвинутой тетраде;

ХВ - информация о наличии хотя бы одной единицы в остальных выдвинутых разрядах;

НОР - информация о том, что была нормализация;

СБН - сборка нулей;

ПРП - переполнение;

ОБРЧ - сигнал обращения мантиссы;

МЛ32 - информация о наличии хотя бы одной единицы в младших "32" разрядах сумматора.

Устройство в случае формата 64 работает следующим образом.

Мантиссы чисел по шинам 11 и 12 соответственно попадают в регистры 1 и 3 (см. фиг.3). Старшая выдвинутая за разрядную сетку при выравнивании порядков тетрада мантиссы числа с меньшим порядком СТ по шине 11 поступает в регистр 2, туда же поступает информация о наличии хотя бы одной единицы в остальных выдвинутых разрядах ХВ. В сумматор 4 мантисс поступают в порядке старшинства в качестве первого слагаемого нулевая тетрада, четырнадцать тетрад мантиссы из сдвигателя, старшая выдвинутая тетрада из регистра 2, в качестве второго слагаемого тетрада, содержащая четыре единицы или нуля в зависимости от того, было ли обращение правой мантиссы, четырнадцать тетрад обращенной мантиссы, еще одна единичная или нулевая тетрада в зависимости от обращения правой мантиссы (см. фиг.4).

В сумматоре 4 формируется 64-разрядная сумма и шестнадцать сборок нулей, по сборкам нулей в узле 5 управления формируется код сдвига СДН для нормализатора 9 результата. Сумма через регистры 6 и 7 поступает в нормализатор 9 результата, где происходит в случае необходимости сдвиг мантиссы результата влево в случае наличия старших нулевых тетрад или вправо в случае переполнения. Если производилась нормализация, то в разрядную сетку возвращается старшая выдвинутая при выравнивании порядков тетрада, прошедшая суммирование в сумматоре 4 мантисс.

В узле 8 формирования сигнала округления вырабатываются два сигнала: ОКР64, говорящий о том, что надо производить округление, если за разрядную сетку при выравнивании порядков или при переполнении вытолкнулась хотя бы одна единица, и КОКР 64, говорящий о том, как надо округлять - наложением единицы или нуля на младший разряд нормализованной мантиссы. Округление нулем производится, если правая мантисса перед суммированием обращалась и младшая сборка нулей 15СБН равняется нулю либо при наличии обращения была нормализация НОР и в разрядах, теряемых при выравнивании порядков без учета старшей выдвинутой тетрады, была хотя бы одна единица:

ОКР64 = ХВ + СТ* - НОР + 14СБН* ПРП;

-ЕОКР64 = ОБРЧ (-15СБН + НОР* ХВ), где СТ - наличие хотя бы одной единицы в старшей выдвинутой тетраде; ПРП - переполнение.

Если операнды имеют формат 32, то мантисса занимает 24 левых разряда разрядной сетки, остальные 32 разряда заполнены нулями (см. фиг.5). В остальном процесс сложения и нормализации при формате 32 не отличается от случая формата 64.

Сигналы необходимости округления ОКР32 и способа округления ЕОКР32 задаются формулами

ОКР32 = ХВ + 6СБН*ПРП + 7СБН* -НОР + МЛ32;

ЕОКР32 = МЛ32 + 7СБН* -НОР, где МЛ32 - наличие хотя бы одной единицы в младших 32 разрядах сумматора.

Использование устройства обеспечивает более высокую точность вычислений (так, в распространенном случае, когда старшая выдвинутая за разрядную сетку при выравнивании порядков тетрада отлична от нуля, а в остальных выдвинутых разрядах находятся нули и требуется нормализация, получается точный результат) и уменьшение ошибки, накапливаемой из-за округления за счет симметризации положительной и отрицательной погрешности при округлении.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| ОПТИЧЕСКИЙ СУММАТОР | 1993 |

|

RU2079872C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| ОПТИЧЕСКОЕ ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ МАТРИЦ | 1994 |

|

RU2079873C1 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности. Устройство содержит три входных регистра, сумматор мантисс, узел управления, регистр, нормализатор результата, выходной регистр. Новым является введение узла формирования сигнала округления и дополнительного регистра. Введение узла округления со сложной логической функцией обеспечивает симметрию положительной и отрицательной погрешности, а изменение коммутации сигналов на входе сумматора мантисс обеспечивается за счет подключения второго входного регистра к первому входу сумматора. 5 ил.

УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ, содержащее три входных регистра, сумматор мантисс, узел управления, регистр, нормализатор результата, выходной регистр, входы первого и второго входных регистров подключены к входной шине мантиссы первого числа, выходы первого и второго входных регистров соединены с первым информационным входом сумматора мантисс, второй информационный вход которого подключен к выходу третьего входного регистра, вход которого подключен к входной шине мантиссы второго числа, выход сумматора мантисс соединен с входом узла управления, выход которого подключен к управляющему входу нормализатора результата, первый информационный вход которого соединен с выходом регистра, выход нормализатора результата подключен к входу выходного регистра, выход которого является выходной шиной результата устройства, отличающееся тем, что в него введены узел формирования сигнала округления и дополнительный регистр, причем выход сумматора мантисс соединен с входом дополнительного регистра и с первым информационным входом узла формирования сигнала округления, второй информационный вход которого подключен к первому информационному входу сумматора мантисс, третий информационный вход узла формирования сигнала округления является входной шиной сигнала обращения мантиссы, первый, второй, третий, четвертый информационные выходы узла формирования сигнала округления соединены соответственно с вторым, третьим, четвертым, пятым информационными входами нормализатора результата, выход дополнительного регистра соединен с входом регистра,управляющий вход узла формирования сигнала округления подключен к выходу узла управления.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Процессор центральный | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметическое исполнительное устройство | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

Авторы

Даты

1994-08-30—Публикация

1992-06-19—Подача