Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности.

Известно-арифметико-логическое устройство, содержащее управляющий коммутатор, исключающее элемент ИЛИ, элемент И-НЕ, элемент НЕ, управляющий триггер, элемент И, регистр перезаписи и n вычислительных блоков, где n разрядность операндов [1]

Недостатками устройства являются ограниченные функциональные возможности и низкая производительность.

Наиболее близким по технической сущности к изобретению является арифметико-логическое устройство, содержащее два узла обращения, сумматор, дешифратор, сдвигатель, формирователь маски, логический блок, блок управления, узел управления, формирователь признаков результата, формирователь прерываний, выходной коммутатор, выходной регистр, первый и второй информационные входы сумматора соединены с выходами первого и втрого узлов обращения соответственно, выход сумматора подключен к первым информационным входам выходного коммутатора, формирователя признаков результата, формирователя прерываний, второй и третий информационные входы которого соединены с входными шинами первого и второго операндов, вторые информационные входы выходного коммутатора и формирователя признаков результата подключены к выходу логического блока, первый выход узла управления соединен с входом формирователя маски, выход которого подключен к первому информационному входу блока управления, второй выход узла управления соединен с управляющим входом сдвигателя, вход дешифратора подключен к входной шине кода операций устройства, первый информационный вход узла управления соединен с входной шиной величины сдвига устройства, выход дешифратора соединен с вторыми информационными входами узла управления и блока управления, выход которого подключен к управляющим входам первогои второго узлов обращения, выходного коммутатора и выходного регистра, информационный вход которого соединен с выходом выходного коммутатора, выход выходного регистра подключен к выходной шине результата операций устройства, выход формирователя признаков результата соединен с выходной шиной кодов условий устройства, первый выход формирователя прерываний подключен к входной шине прерывания переполнения при тегированных операциях устройства [2]

Однако устройство имеет недостаточную производительность, точность, ограниченные функциональные возможности. Это обусловлено тем, что устройство работает с 32-разрядными операндами, операции умножения и деления реализуются программным путем, не выполняется операция подсчета числа единиц.

Целью изобретения является повышение производительности, точности устройства и расширение его функциональных возможностей за счет выполнения дополнительных логических операций.

Поставленная цель достигается тем, что в арифметико-логическом устройстве, содержащем два узла обращения, сумматор, дешифратор, сдвигатель, формирователь маски, логический блок, блок управления, узел управления, формирователь признаков результата, формирователь прерываний, выходной коммутатор, выходной регистр, первый и второй информационные входы сумматора соединены с выходами первого и второго узлов обращения соответственно, выход сумматора подключен к первым информационным входам выходного коммутатора, формирователя признаков результата, формирователя прерываний, второй и третий информационные входы которого соединены с входными шинами первого и второго операндов, вторые информационные входы выходного коммутатора и формирователя признаков результата подключены к выходу логического блока, первый выход узла управления соединен с входом формирователя маски, выход которого подключен к первому информационному входу блока управления, второй выход узла управления соединен с управляющим входом сдвигателя, вход дешифратора подключен к входной шине кода операций устройства, первый информационный вход узла управления соединен с входной шинойвеличины сдвига устройства, выход дешифратора ссоединен с вторыми информационными входами узла управления и блока управления, выход которого подключен к управляющим входам первого и второго узлов обращения, выходного коммутатора и выходного регистра, информационный вход которого соединен с выходом выходного коммутатора, выход выходного регистра подключен к выходной шине результата операций устройства, выход формирователя признаков результата соединен с выходной шиной кодов условий устройства, первый выход формирователя прерываний подключен к выходной шине прерывания переполнения при тегированных операциях устройства, введены три входных коммутатора, формирователь временных стробов, блок сравнения, два формирователя переноса, формирователь знака и цифр частного, семь коммутаторов, два регистра, дополнительный выходной коммутатор, формирователь знака результата, формирователь конца операций, дополнительный узел обращения, дополнительный сумматор, формирователь значений грубого сдвига, формирователь значений точного сдвига, причем первые информационные входы первого входного коммутатора, первого формирователя переноса, формирователя знака и цифр частного, пятого коммутатора,третий информационный вход формирователя признаков результата подключены к входной шине первого операнда, информационный вход третьего входного коммутатора, первые информационные входы второго входного коммутатора, седьмого коммутатора, вторые информационные входы первого формирователя переносов, формирователя знака и цифр частного, пятого коммутатора, четвертый информационный вход формирователя признаков результатов соединены с входной шиной второго операнда, третий информационный вход первого формирователя переноса подключен к входной шине входного переноса, первый информационный вход формирователя временных стробов, третий информационный вход блока управления соединены с входной шиной системного сброса, второй информационный вход формирователя временных стробов, четвертый информационный вход блока управления соединены с шиной начала операции, первые информационные входы формирователя знака результата, четвертого и шестого коммутаторов, вторые информационные входы первого и второго входных коммутаторов подключены к шине логического "0", второй информационный вход формирователя знака результата соединен с шиной логической "1", выход первого входного коммутатора подключен к входу первого узла обращения, выход второго входного коммутатора соединен с входом второго узлаобращения, выход сумматора подключен к первому информационному входу дополнительного выходного коммутатора, к третьим информационным входам формирователя знака и цифр частного, пятого коммутатора, к информационному входу первого коммутатора, к входу формирователя значений грубого сдвига, к третьему информационному входу пятого коммутатора, выход которого соединен с входом первого регистра, выход которого подключен к третьим информационным входам первого и второго входных коммутаторов, к четвертому информационному входу первого формирователя переноса, выход выходного регистра соединен с вторым информационным входом дополнительного вы- ходного коммутатора, с четвертыми информационными входами первого входного коммутатора, пятого коммутатора, с пятыми информационными входами первого формирователя переноса, формирователя признаков результата, выход третьего входного коммутатора подключен к шестому информационному входу первого формирователя переноса, к пятому информационному входу блока управления, к шестому информационному входу которого, к первому информационному входу блока сравнения, к седьмому информационному входу первого формирователя переноса, к управляющему входу третьего входного коммутатора подключен первый выход формирователя временных стробов, второй выход которого соединен с шестым информационным входом формирователя признаков результата, с седьмым информационным входом блока управления, с восьмым информационным входом первого формирователя переноса, спервым информационным входом формирователя конца операций, второй информационный вход которого, третий информационный вход формирователя знака результата, четвертые информационные входы формирователя знака и цифр частного, формирователя прерываний, седьмой информационный вход формирователя признаков результата, девятый информационный вход первого формирователя переноса подключены к третьему информационному выходу формирователя временных стробов, выход дешифратора соединен с информационным входом второго формирователя переноса, с четвертым информационным входом формирователя знака результата, с пятыми информационными входами формирователя знака и цифр частного, формирователя прерывания, с восьмым информационным входом формирователя признаков результата, с десятым информационным входом первого формирователя переноса, с третьими информационными входами формирователя временных стробов, формирователя конца операций, четвертый информационный вход которого и четвертый информационный вход формирователя временных стробов подключены к выходу блока сравнения, выход формирователя знака и цифр частного соединен с третьим информационным входом дополнительного выходного коммутатора, с пятым информационным входом формирователя знака результата, с одиннадцатым входом первого формирователя переноса, выход которого подключен к третьему информационному входу сумматора, выход формирователя знака результата соединен с четвертым информационным входом дополнительного выходного коммутатора, выход которого подключен к третьему информационному входу выходного коммутатора, второй выход формирователя прерываний соединен с пятыми информационными входами формирователя временных стробов, формирователя конца операций,с выходной шиной прерывания деления на "0" устройства, выход формирователя конца операций подключен к шестому информационному входу формирователя временных стробов, к выходной шине конца многотактных операций устройства, первый выход сдвигателя соединен с входом формирователя значения точного сдвига, выход которого подключен к первым информационным входам второго и третьего косммутаторов, к второму информационному входу шестого коммутатора, выход формирователя значениягрубого сдвига соединен с вторыми информационными входами второго, третьего и четвертого коммутаторов, третий информационный вход которого и третий информационный вход шестого коммутатора подключены к входной шине величины сдвига устройства, второй информационный вход блока сравнения, третьи информационные входы второго и третьего коммутаторов, четвертые информационные входы четвертого и шестого коммутаторов соединены с выходом дополнительного сумматора, первый информационный вход которого подключен к выходу дополнительного узла обращения, информационный вход которого соединен с выходом второго регистра, информационный вход которого подключен к выходу второго коммутатора, выход третьего коммутатора соединен с вторым информационным входом дополнительного сумматора, третий информационный вход которого соединен с выходом второго формирователя переноса, выход шестого коммутатора подключен к третьему информационному входу узла управления, четвертый информационный вход которого соединен с выходом четвертого коммутатора, пятый, шестой, седьмой информационные входы узла управления подключены соответственно, к входной шине номера байта, к первой управляющей шине, к второй управляющей шине устройства, выход пятого коммутатора соединен с информационным входом сдвигателя, второй выход которого подключен к первому управляющему входу логического блока, второй управляющий вход которого соединен с выходом седьмого коммутатора, второй информационный вход которого подключен к выходу формирователя маски, выход логического блока соединен с четвертым информационным входом второго коммутатора, управляющие входы второго регистра первого и второго входных коммутаторов, первого, второго, третьего, четвертого, пятого, шестого коммутаторов, формирователя временных стробов, дополнительного выходного коммутатора, дополнительного узла обращения, второго формирователя переноса соединены с выходом блока управления, управляющий вход логического блока, управляющий вход седьмого коммутатора подключены к выходу узла управления.

Сущность изобретения заключается в аппаратной реализации операций умножения, деления, подсчета числа единиц за счет введения трех входных коммутаторов, формирователя временных стробов, блока сравнения, двух формирователей переносов, формирователя знака и цифр частного, семи коммутаторов, формирователя знака результата, формирователя конца операций, дополнительного узла обращения, дополнительного сумматора, формирователя значения грубого сдвига, формирователя значения точного сдвига и связей между ними.

Выполнение узлов обращения, сумматоров, сдвигателя, логического блока 64-разрядными позволяет обрабатывать 64-разрядные числа, что повышает точность устройства.

Сравнение предлагаемого технического решения с прототипом позволяет установить его соответствие критерию "новизна". При изучении других технических решений в данной области техники признаки, отличающие изобретение от прототипа, не были выявлены и поэтому они обеспечивают предлагаемому техническому решению критерий "изобретательский уровень".

Математическое моделирование, а также предварительные испытания устройства показали возможность промышленной применимости изобретения.

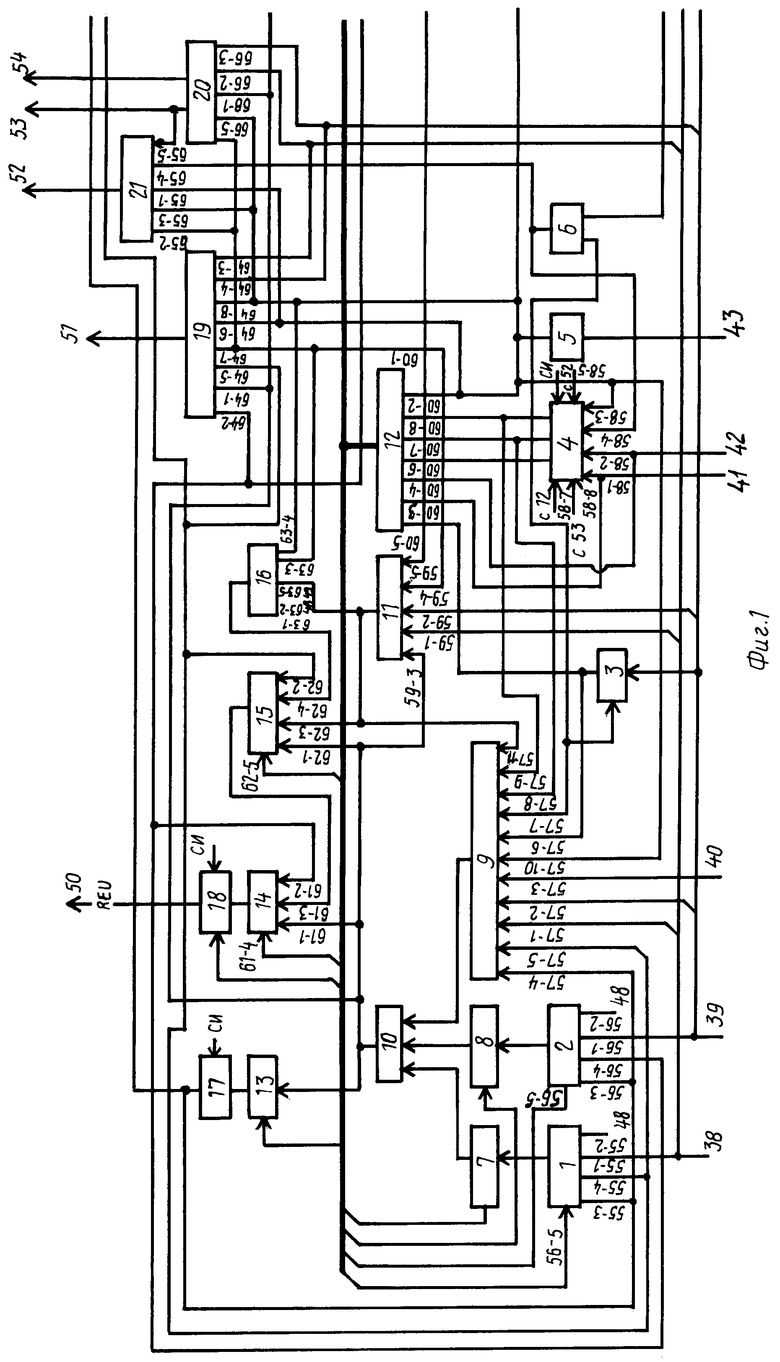

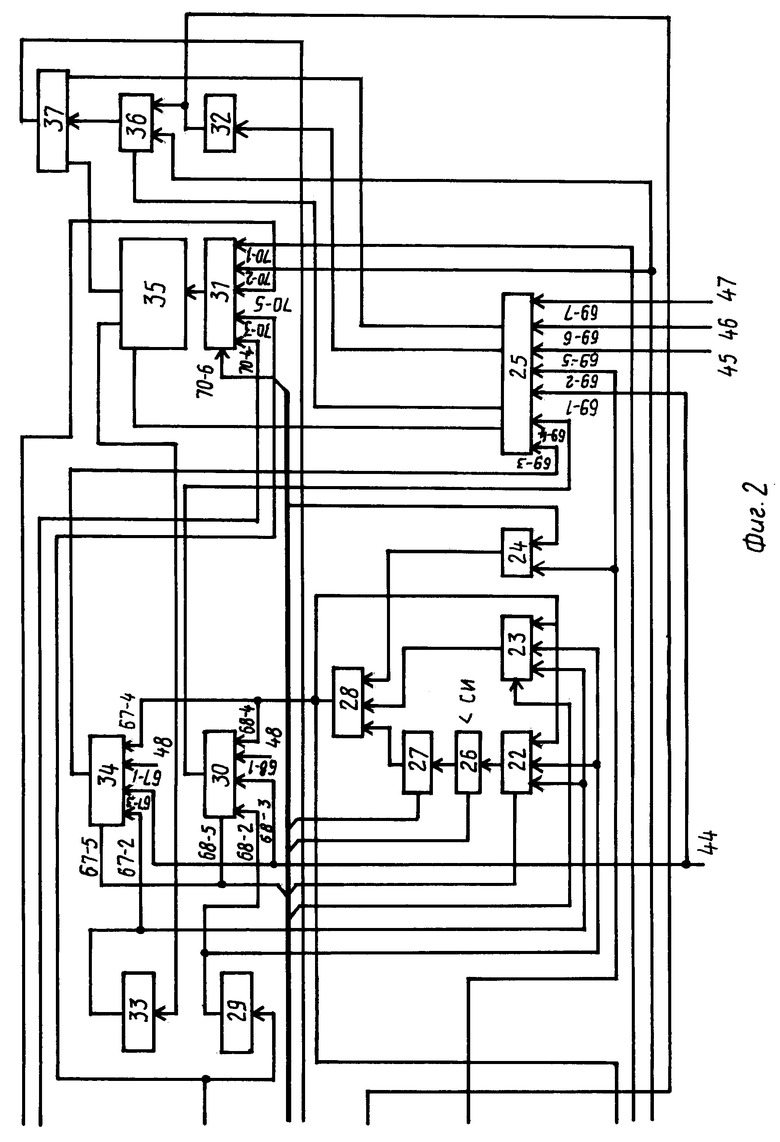

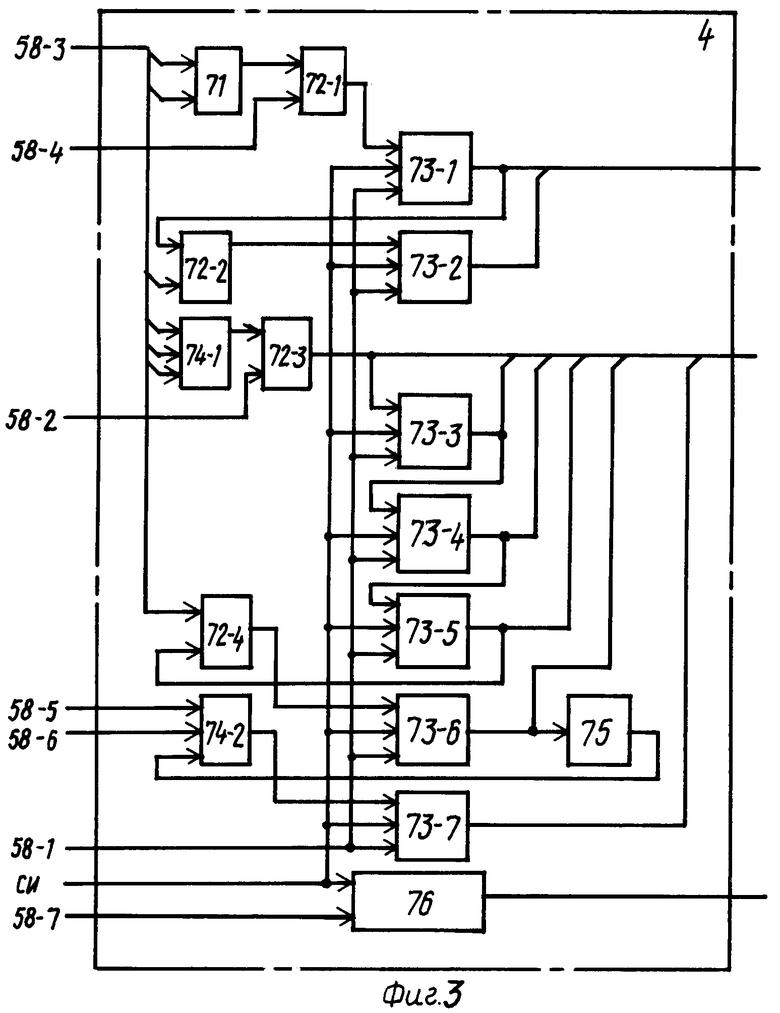

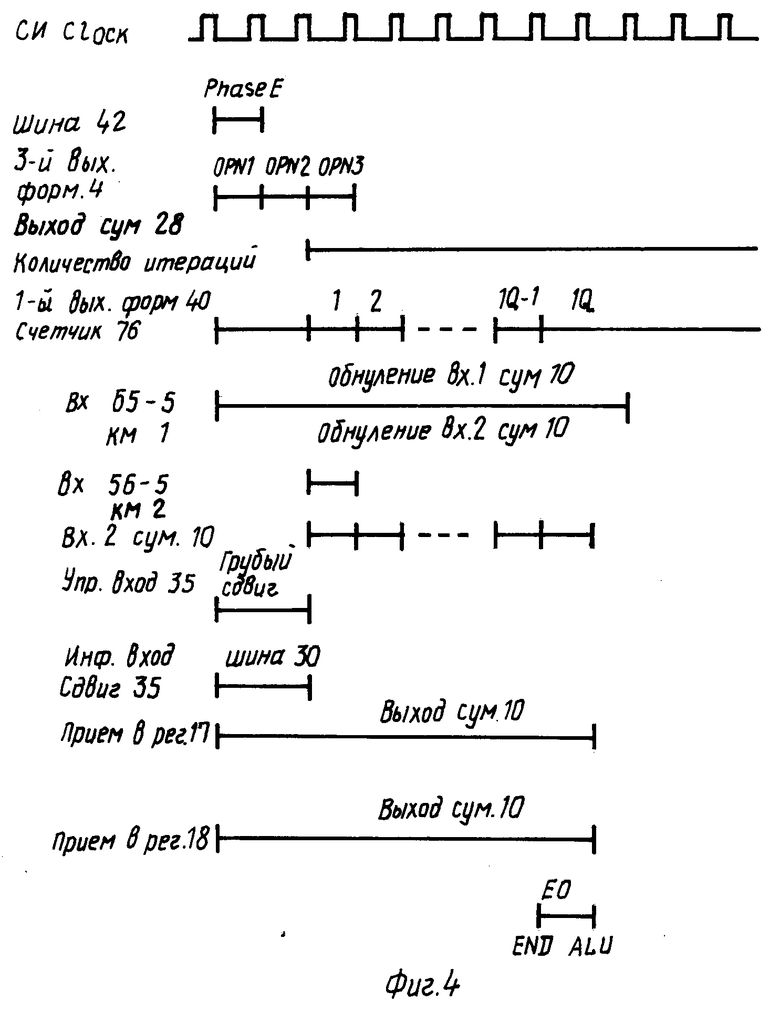

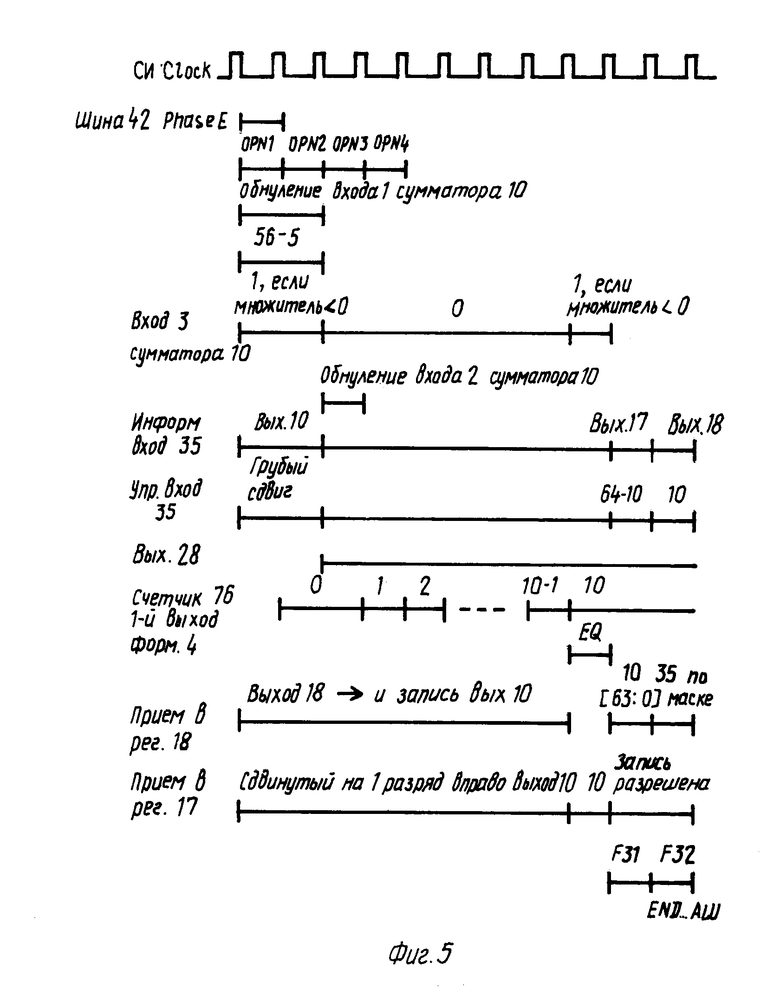

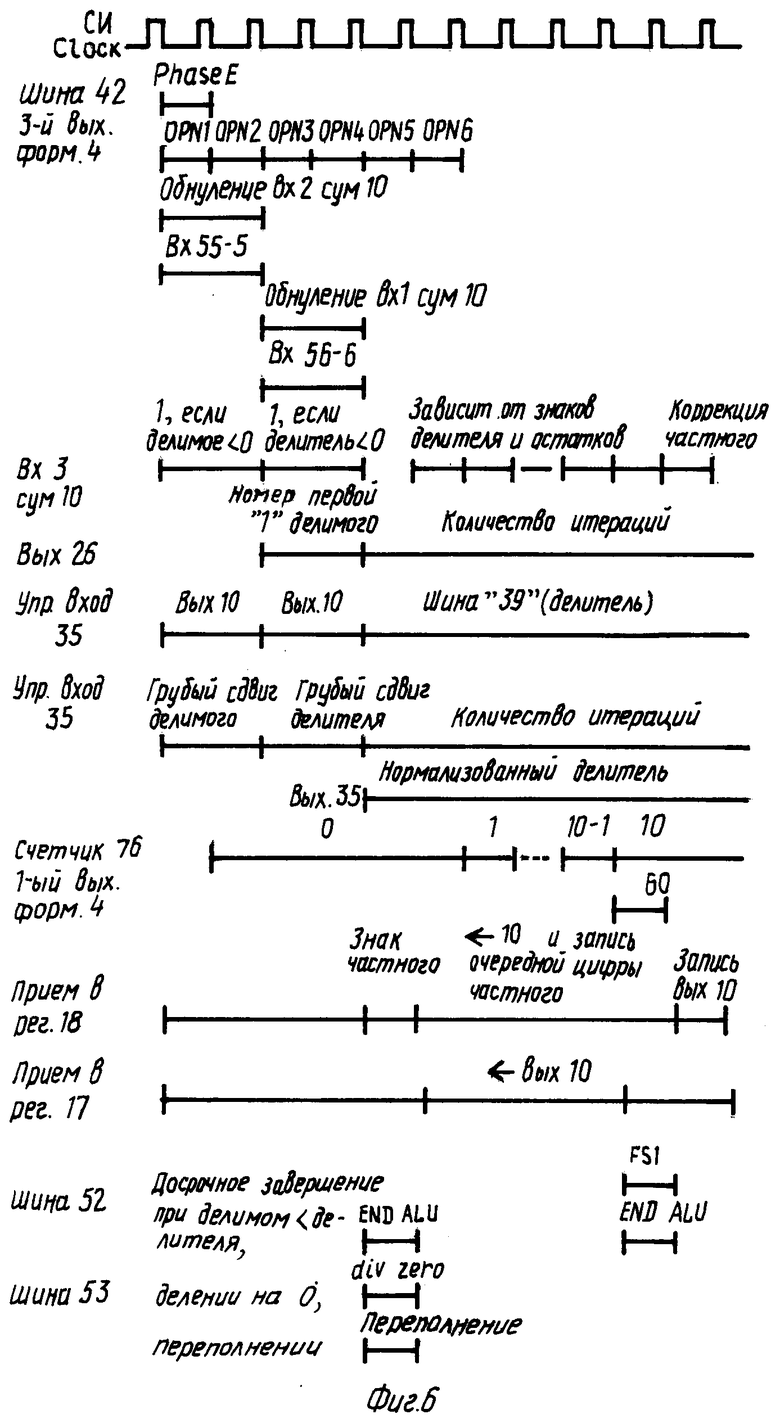

На фиг. 1 и 2 представлена структурная схема арифметико-логического устройства; на фиг. 3 формирователь временных стробов; на фиг. 4 временная диаграмма выполнения операции РОРС; на фиг. 5 временная диаграмма выполнения операции умножения; на фиг. 6 временная диаграмма выполнения операции деления.

Арифметико-логическое устройство содержит первый входной коммутатор 1, второй входной коммутатор 2, третий входной коммутатор 3, формирователь 4 временных стробов, дешифратор 5, блок 6 сравнения, первый узел 7 обращения, второй узел 8 обращения, первый формирователь 9 переноса, сумматор 10, формирователь 11 знака и цифр частного, блок 12 управления, первый коммутатор 13, выходной коммутатор 14, дополнительный выходной коммутатор 15, формирователь 16 знака результата, первый регистр 17, выходной регистр 18, формирователь 19 признаков результата, формирователь 20 прерываний, формирователь 21 конца операций, второй коммутатор 22, третий коммутатор 23, второй формирователь 24 переноса, узел 25 управления, второй регистр 26, дополнительный узел 27 обращения, дополнительный сумматор 28, формирователь 29 значения грубого сдвига, четвертый коммутатор 30, пятый коммутатор 31, формирователь 32 маски, формирователь 33 значения точного сдвига, шестой коммутатор 34, сдвигатель 35, седьмой коммутатор 36, логический блок 37.

В устройстве имеются входная шина 38 первого операнда, входная шина 39 второго операнда, входная шина 40 входного переноса, входная шина 41 системного сброса, входная шина 42 начала операции, входная шина 43 кода операции, входная шина 44 величины сдвига, входная шина 45 номера байта, первая управляющая шина 46, вторая управляющая шина 47, шина 48 логического "0", шина 49 логический "1", выходная шина 50 результата операций, выходная шина 51 кодов условий, выходная шина 52 конца многотактных операций, выходная шина 53 прерывания деления на "0", выходная шина 54 прерывания переполнения при тегированных операциях.

Первый входной коммутатор имеет четыре информационных входа 55-1 55-4 и управляющий вход 55-5, а второй коммутатор четыре информационных входа 56-1 56-4 и управляющий вход 56-5. Первый формирователь переноса имеет одиннадцать информационных входов 57-1 57-11. Формирователь временных стробов имеет шесть информационных входов 58-1 59-6, управляющий вход 58-7. Формирователь знака и цифр частного содержит пять информационных входов 59-1 58-5. Блок управления имеет восемь информационных входов 60-1 60-8. Выходной коммутатор содержит три информационных входа 61-1 61-3, управляющий вход 61-4. Дополнительный входной коммутатор имеет четыре информационных входа 62-1 62-4 и управляющий вход 62-5. Формирователь знака результата имеет пять информационных входов 63-1 63-5. Формирователь признаков результата имеет восемь информационных входов 64-1 64-8. Формирователь конца операций содержит пять информационных входов 65-1 65-5. Формирователь прерываний имеет пять информационных входов 66-1 66-5. Шестой коммутатор имеет четыре информационных входа 67-1 67-4, управляющий вход 67-5. Четвертый коммутатор имеет четыре информационных входа 68-1 68-4, управляющий вход 68-5. Узел управления содержит семь информационных входов 69-1 69-7. Седьмой коммутатор имеет пять информационных входов 70-1 70-5, управляющий вход 70-6.

Формирователь временных стробов содержит элемент ИЛИ 71, четыре элемента И 72-1 72-4, семь триггеров 73-1 73-7, два элемента ИЛИ 74-1 74-2, элемент НЕ 75 и счетчик 76.

В арифметико-логическом устройстве входная шина 38 первого операнда соединена с входом 55-1 коммутатора 1, входом 57-1 формирователя 9, входом 57-1 формирователя 11, входом 64-3 формирователя 19, входом 66-2 формирователя 20, входом 70-1 коммутатора 31. Входная шина 39 второго операнда подключена к входу 56-1 коммутатора 2, входу коммутатора 3, входу 64-4 формирователя 19, входу 66-3 формирователя 20, входу 70-2 коммутатора 31, первому информационному входу коммутатора 36. Входная шина 40 входного переноса соединена с входом 57-3 формирователя 9. Входная шина 41 системного сброса подключена к входу 58-1 формирователя 4 и входу 60-3 блока 12. Входная шина 42 начала операции соединения с входом 58-2 формирователя 4, со входом 60-4 блока 12. Входная шина 43 кода операции подключена к входу дешифратора 5.

Входная шина 44 величины сдвига соединена с входом 67-3 коммутатора 34, входом 68-3 коммутатора 30, входом 69-1 узла 25 управления. Входная шина 45 номера байта, первая управляющая шина 46, вторая управляющая шина 47 соединены соответственно с сходами 69-5, 69-6, 69-7 узла 25 управления.

Шина 48 логического "0" подключена к входу 55-2 коммутатора 1, входу 56-2 коммутатора 2, входу 63-1 формирователя 16, входу 67-1 коммутатора 34, входу 68-1 коммутатора 30. Шина 49 логической "1" соединена с входом 63-2 формирователя 16. Выход коммутатора 1 подключен к входу узла 7 обращения. Выход коммутатора 2 соединен с входом узла 8 обращения. Первый, второй, третий информационные входы сумматора 10 подключены соответственно к выходам узлов 7 и 8 и формирователя 9. Выход сумматора 10 соединен с информационным входом коммутатора 13, входом 61-1 коммутатора 14, входом 62-1 коммутатора 15, входом 59-3 формирователя 11, входом 64-1 формирователя 19, входом 66-1 формирователя 20, входом формирователя 29, входом 70-3 коммутатора 31. Выход коммутатора 13 подключен к информационному входу регистра 17. Выход регистра 17 соединен с входом 55-3 коммутатора 1, входом 56-3 коммутатора 2, входом 57-4 формирователя 9, входом 70-5 коммутатора 31. Выход коммутатора 3 подключен к шестому выходу 57-6 формирователя 9 и входу 60-5 блока 12 управления.

Первый выход формирователя 4 соединен с управляющим входом коммутатора 3, входом 57-7 формирователя 9, входом 60-6 блока 12 управления, с первым информационным входом блока 6. Второй выход формирователя 4 подключен к входу 57-8 формирователя 9, входу 60-7 блока 12 управления, входу 64-6 формирователя 19, входу 65-1 формирователя 21. Третий выход формирователя 4 соединен с входом 57-9 формирователя 9, входом 60-8 блока 12 управления, входом 59-4 формирователя 11, входом 63-3 формирователя 16, входом 64-7 формирователя 19, входом 65-2 формирователя 21, входом 66-4 формирователя 20.

Выход дешифратора 5 подключен к входу 57-10 формирователя 9, входу 58-3 формирователя 4, входу 59-5 формирователя 11, входу 60-2 блока 12 управления, входу 63-4 формирователя 16, входу 64-8 формирователя 19, входу 65-3 формирователя 21, входу 66-5 формирователя 20, информационному входу формирователя 24, входу 69-2 узла 25 управления. Выход блока 6 сравнения соединен с входом 58-4 формирователя 4, входом 65-4 формирователя 21. Выход формирователя 11 подключен к входу 57-11 формирователя 9, входу 62-3 коммутатора 15, входу 63-5 формирователя 16. Выход формирователя 16 соединен с входом 62-4 коммутатора 15, выход которого подключен к входу 61-3 коммутатора 14. Выход коммутатора 14 соединен с информационным входом регистра 18.

Выход формирователя 29 подключен к входу 68-2 коммутатора 30, вторым информационным входам коммутаторов 22 и 23. Выход формирователя 33 соединен с входом 67-2 коммутатора 34 и первыми информационными входами коммутаторов 22 и 23. Выход коммутатора 22 подключен к информационному входу регистра 26, выход которого соединен с информационным входом узла 27 обращения. Первый, второй, третий информационные входы сумматора 28 соединены соответственно с выходами узла 27 обращения, коммутатора 23, формирователя 24.

Выход сумматора 28 соединен с вторым информационным входом блока 6 сравнения, третьими информационными входами коммутаторов 22 и 23, входом 67-4 коммутатора 34, входом 68-4 коммутатора 30. Выход коммутатора 34 подключен к входу 69-3 узла 25 управления. Выход коммутатора 30 соединен с входом 69-4 узла 25 управления. Первый выход узла 25 управления соединен с входом формирователя 32. Третий выход узла 25 управления подключен к информационному входу блока 37. Выход коммутатора 31 подключен к информационному входу сдвигателя 35, первый выход которого соединен с входом формирователя 33. Второй выход сдвигателя 35 подключен к первому управляющему выходу блока 37. Выход формирователя 32 маски соединен с вторым информационным входом коммутатора 36 и входом 60-1 блока 12 управления. Выход коммутатора 36 подключен к второму управляющему входу блока 37, выход которого соединен с входом 56-4 коммутатора 2, входом 61-3 коммутатора 14, входом 64-2 формирователя 19.

Управляющие входы узлов 7, 8, 27 сдвига, коммутаторов 3, 13, 22, 23, регистров 18, 26, вход 55-5 коммутатора 1, вход 56-5 коммутатора 2, вход 61-4 коммутатора 14, вход 62-5 коммутатора 15, вход 67-5 коммутатора 34, вход 68-5 коммутатора 30, вход 70-6 коммутатора 31 соединены с выходом блока 12 управления. Второй и четвертый выходы узла 25 управления подключены соответственно к управляющим входам сдвигателя 35 и коммутатора 36. Выход регистра 18 соединен с входом 55-4 коммутатора 1, входом 57-5 формирователя 9, входом 62-2 коммутатора 15, входом 64-5 формирователя 19, входом 70-4 коммутатора 31, с выходной шиной 50 результата операций. Выход формирователя 19 подключен к выходной шине 51 кодов условий.

Первый выход формирователя 20 соединен с выходной шиной 54 прерывания переполнения при тегированных операциях.

Второй выход формирователя 20 соединен с входом 58-6 формирователя 4, входом 65-5 формирователя 21 и выходной шиной 53 прерывания деления на "0".

Выход формирователя 21 подключен к входу 58-5 формирователя 4 и выходной шине 52 конца многотактных операций.

64-разрядные коммутаторы 1 и 2 выполнены по схеме обычного коммутатора с 4 направлений. Коммутатор 1 в зависимости от выполняемой операции и такта передает узел 7 обращения и далее на вход 1 сумматора 10 либо первый операнд, либо из регистра 17 остаток от деления, полученный в предыдущей итерации, либо частное при коррекции результата. Коммутатор 2 в зависимости от выполняемой операции и такта передает на вход узла 8 обращения и далее на вход 2 сумматора 10 либо второй операнд, либо из регистра 17 частичное произведение, полученное в предыдущей итерации, либо нормализованный делитель с выхода 35.

Узлы 7, 8, 27 обращения выполнены по схеме обычного узла обращения. Узлы 7, 8 передают выходы коммутаторов 1 и 2 соответственно с обращением или без него на вход 1 и вход 2 сумматора 10 соответственно.

Первый формирователь 9 входного переноса реализует следующую логику:

C_SM- POPCNT * bit_RS2 * -OPN1 * -OPN2 + inv_A +

SIGNMUL * (OPN2 + OPN1) * RS2[63] + +OPN6 *

(UNSIGNDIV + SIGNDIV * -(RS1[63] + +RS2[63])) +

DIV * (-CNT_EQ_O) * REU[O] * -FS1 +

(opcode= SUB + opcode-=SUBcc +

opcode=TSUBcc + opcode=TSUBccTV) +

(opcode= SUBC + opcode= SUBCcc) * -icc_c +

(opcode= ADDC + opcode ADDCcc) * icc_c +

SIGNDIV * (-RT_EQ_O * QUOT_SIGN * FS1 * -TRO_REM +

(OPN3 + OPN4) * RS2[63] где POPCNT сигнал, говорящий о том, что выполняется операция подсчета количества единиц;

SIGNMUL выполняется одна из операций умножения с учетом арифметических знаков операндов;

SIGNDIV выполняется одна из операций деления с учетом арифметических знаков операндов;

UNSIGNDIV выполняется одна из операций деления без учета арифметических знаков операндов;

DIV выполняется одна из операций деления;

opcode код операции, приходящий по шине 43;

icc_c сигнал переноса, поступающий из управления по шине 40;

OPN1, OPN2, OPN3, OPN4, OPN6, FS1 временные стробы, вырабатывающиеся в формирователе 4,

TRO_REM сигнал, говорящий о том, что в процессе деления был хотя бы один нулевой остаток;

QUOT_SIGN знак частного;

RT_EQ_O сигнал, говорящий о том, что содержимое регистра 17 равно 0;

bit_RS2 i-й разряд второго операнда с выхода коммутатора 3;

RS1[i] i-й разряд первого операнда;

RS2[i] i-й разряд второго операнда;

REU[i] i-й разряд регистра 18;

inv_A сигнал обращения для узла 7;

CNT_EQ_O сигнал, говорящий, что счетчик итераций равен 0.

Коммутатор 3 выполнен по обычной схеме коммутатора с 64 направлений. Он выбирает очередной разряд множителя, приходящего по шине 39, на его управляющий вход с формирователя 4 подается значение счетчика итераций.

Дешифратор 5 вырабатывает управляющие сигналы ОРD из кода операции, приходящего по шине 43.

Блок 6 сравнивает значение счетчика итераций из формирователя 4 с количеством итераций, необходимым для выполнения многотактных операций, поступающим с выхода сумматора 28. При их совпадении вырабатывается сигнал EQ. Сигнал совпадения EQ реализован по следующей логике:

EQ= EQPR * NEQPRT * EQENABLE; где EQPR (-CNT_EQ_O + OPN3 * -DIV + +OPN6) *

AU * (IQ[5:0]-CNT[5:0]);

NEQPRT сигнал, делающий сигнал EQ однотактным;

EQENABLE сигнал, не позволяющий сигналу совпадения EQ вырабатываться во время предварительного анализа операндов;

AU выполняется одна из операций сложения, вычитания, умножения, деления или подсчета количества единиц;

CNT количество выполненных итераций, выход 1 формирователя 4;

1Q выход сумматора 28.

В формирователе 4 вырабатываются тактовые сигналы ОPN1, OPN2, OPN3, OPN4, OPN5, OPN6, задающие временную диаграмму преобразования операндов в прямой код, их нормализацию и вычисление количества итераций, требуемое для выполнения операции. По сигналу совпадения количества итераций и выхода счетчика, вырабатываемого в блоке 6, также формируются сигналы FS1, FS2, которые управляют коррекцией результата при умножении и делении.

OPN1 реализован по следующей логике:

OPN1 (MUL + DIV + POPCNT) * Phase_E;

Условия установки триггеров OPN2, OPN3, OPN4, OPN5, OPN6, FS1, FS2 в единицу в следующем такте представлены ниже:

для OPN2:OPN1;

для OPN3:OPN2;

для OPN4:OPN3;

для OPN5:OPN4 * DIV;

для OPN6:OPN5 * -div_zero * -END_ALU;

для FS1:EQ * (MUL + DIV);

для FS2: FS1 * MUL; где MUL сигнал, говорящий, что выполняется одна из операций умножения;

RESET сигнал системного сброса;

EQ сигнал, поступающий из блока сравнения 6 и означающий равенство необходимого количества и счетчика итераций;

Phase_E сигнал начала операции;

END_ALU сигнал окончания многотактных операций;

div_zero сигнал, означающий, что делитель равен 0.

Счетчик итераций в формирователе 4 каждый такт увеличивает свое значение на 1 (начиная с О) после предварительной обработки операндов и выполнен по схеме обычного 7-разрядного счетчика.

Формирователь 11 определяет знак частного следующим образом.

QUOT_SIGN (SIGNDIV * (RS1[63] ⊕ RS2[63])) *

-(OPN5 * (-TR_SGN + TRO_REM)), а очередную цифру частного так:

QUOT -(SM[64] ⊕ RS2[63] * -UNSIGNDIV) + (SM_EQ_O),

RS2[63] 63-ий разряд второго операнда;

RS1[63] 63-ий разряд первого операнда;

SM[64] 64-ый разряд сумматора 10;

SM_ EQ_ O сигнал, означающий равенство нулю остатка на выходе сумматора 10;

OPN5 временной строб, вырабатывающийся в формирователе 4;

TR_ SGN сигнал, означающий, что делитель больше делимого по абсолютной величине.

Формирователь 21 формирует сигнал окончания многотактных операций END_ ALU:

END_ALU MUL * FS2 + POPCNT * EQ +

DIV * (FS1 + OPN5 *

(div_ zero + (-TR_SGN) + TRO_REM) + +DIV_OVERF, где FS2 временной строб, вырабатывающийся в формирователе 4,

DIV_ OVERF сигнал, означающий, что произошло переполнение при выполнении операции деления.

65-разрядный сумматор 10 используется при выполнении всех арифметических операций. Он производит сложение величин, приходящих на его 1, 2 и 3 входы (вход 3 входной перенос) в дополнительном коде. Представляет собой обычный сумматор, в котором параллельно вычисляются функции распространения и формирования переноса для 8-и разрядных групп (группа старших разрядов состоит из 9-и разрядов), и вырабатываются условные 8-и разрядные суммы. После этого происходит выбор условной суммы в зависимости от того, пришел или нет перенос в 8 разрядов.

Блок 12 управления коммутаторами и схемами обращения вырабатывает следующие сигналы:

сигнал обращения содержимого регистра 26 в узле 27:

invert_ IQT MUL + POPCNT + OPN1 + OPN2 + OPN3 + OPN4; сигналы, поступающие на управляющие входы коммутатора 1:

ctrl_A_1 ((-CNT_EQ_O) * OPN1 * OPN2 + FS1) * DIV;

ctrl_ A_2 DIV * (OPN3 + OPN4 + FS1) + MUL * (OPN1 + OPN2 + (OPN3 + -CNT_ EQ_O) * RS2[i] + FS1 + FS2) + POPCNT;

сигналы, поступающие на управляющие входы коммутатора 2:

сtrl_B_1 (MUL + POPCNT) *

(-(CNT_EQ_O + OPN1 + OPN2) + OPN3) + DIV * (OPN1 + OPN2 + FS1);

ctrl_B_2 DIV * (OPN1 + OPN2 + OPN5 + OPN6 + FS1 +

-(CNT_EQ_O + OPN1 + OPN2)) + (POPCNT + MUL) * OPN3;

сигнал обращения в узле 7:

inv_A MUL * (EQ + FS1 + FS2) * -OPN1 * -OPN2 *

RS2[i] + SIGNDIV * (OPN1 + OPN2) * RS1 [63]

сигнал обращения в узле 8:

inv_B SUBSTR + SIGNMUL * (OPN2 + OPN1) *

RS2[63] + SIGNDIN * (OPN3 + OPN4) *

RS2[63] + OPN6 * (UNSIGNDIV + SIGNDIV *

-(RS1[63] ⊕ RS2[63])) +

DIV * CNT_EQ_O * REU[O] * -(DIV * FS1);

сигналы, поступающие на управляющие входы коммутатора 13:

ctrl_RT_1 MUL * (OPN3 + CNT_EQ_O * -EQ) *

-FS1 * -FS2;

сtrl_RT_2 DIV * -EQ * -OPN1 * -OPN2;

сигналы, поступающие на управляющие входы коммутатора 15:

сtrl_REUT_1 MUL * (OPN3 + (-CNT_EQ_O) * (-EQ));

ctrl_REUT_2 OPN5 + DIV * DIV_OVERF * (OPN6 + FS1);

сигналы, поступающие на управляющие входы коммутатора 14:

сtrl_REUL_1 MUL * (FS1 + FS2) + (-AU);

ctrl_REUL_2 MUL * -FS1 * -FS2 * (OPN3+

-CNT_EQ_O * -EQ) + OPN5 + DIV *

(DIV_OVERF * (OPN6 + FS1) +

-DIV_OVERF * (OPN6 + -CNT_EQ_O *

-FS1));

сигналы, поступающие на управляющие входы коммутатора 31:

сtrl_shift_op_1 (OPN5 + OPN6 + (-CNT_EQ_O) *

-OPN1 * -OPN2 * (MUL + DIV +

POPCNT) +

DIV * FS1) + MUL * FS1;

сtrl_shift_op_2 OPN1 + OPN2 + OPN3

+OPN4 * DIV +

MUL * FS1;

ctrl_shift_op_3 MUL * FS2;

сигналы, поступающие на управляющие входы коммутаторов 30 и 34:

сtrl_shifr_am_1=((-AU) + MUL * (FS1 + FS2) +

OPN5 + OPN6 + DIV * ((-CNT_EQ_O) + FS1)) * shcode;

ctrl_shift_am_2=(OPN1 + OPN2 + DIV * OPN4 +

MUL * (FS1 + FS2) +

OPN5 + OPN6 + DIV * ((-CNT_EQ_O) + FS1)) * shcode;

сигнал, поступающий на управляющий вход коммутатора 22:

сtrl_IQ MUL * (EQ + FS1) + DIV * OPN4;

сигнал, разрешающий прием в i-ый разряд регистра 26:

REU_WR_LOCK[i] -mask[i] * MUL * FS2;

сигнал, разрешающий прием в регистр 26:

ctrl_IQT OPN1 + OPN2 + MUL * (FS1 + EQ) +

DIV * OPN4;

сигнал разрешения увеличения выхода счетчика в формирователе 4 на единицу:

CNT_EN (MUL + POPCNT) * OPN3 * -EQ +

OPN6 +

-CNT_EQ_O * -EQ*-DIV_OVERF;

сигнал, поступающий на управляющий вход коммутатора 24:

a= DIV * (OPN3+OPN4), где SUBSBR сигнал, говорящий, что выполняется одна из операций вычитания,

REU[0] нулевой разряд регистра 18;

shcode выполняется одна из операций сдвига,

mask[i] i-й разряд маски из формирователя маски 32 для записи в регистр 18;

64-разрядные коммутаторы 14 и 15 выполнены по схеме обычного коммутатора с 3 и 4 направлений соответственно.

Коммутатор 13 на 65 разрядов пропускает в регистр 17 результат суммирования с выхода сумматора 10 прямо или со сдвигом влево или вправо на один разряд. Коммутатор выполнен по схеме обычного коммутатора с 3 направлений.

Коммутатор 15 выдает либо сдвинутое вправо содержимое регистра 18 с помещенным в самый старший разряд очередной цифрой частичного произведения, либо содержимое регистра 18, сдвинутое влево на l-разряд, с помещенной в самый младший разряд очередной цифрой частного, либо специальные величины, которые должны быть записаны в регистр результата в случае переполнения при делении. Коммутатор 14 выдает на вход регистра 18 результата либо выход коммутатора 15, либо выход сдвигателя 35, либо выход сумматора 10.

Формирователь 16 вырабатывает специальные величины, которые записываются в регистр 18 в случае переполнения при выполнении операции деления. В формирователе 16 реализована следующая логика:

для 0<=i<=30:

SGN_CST[i] OPN5 * QUOT_SIGN +

DIV_OVERF * -(SIGNDIV * QUOT_SIGN);

для i=31:

SGN_CST[i] OPN5 * QUOT_SIGN +

DIV_OVERF * -(SIGNDIV * -QUOT_SIGN);

для 31<i<=63:

SGN_CST[i] OPN5 * QUOT_SIGN +

DIV_OVERF * SIGNDIV * QUOT_SIGN;

В формирователе 19 вырабатываются коды условий результата

icc_N AU * ((MUL * (IQ>31)) * REU[31] +

(MUL * (IQ>31)) * EU[31]) + -AU * resshift[31]

icc_Z= AU * (-MUL * DIV * SM31_EQ_O +

DIV * (FS1 * +SM[31:O] + OPN5 +

-OPN6 * -END_ALU) +

MUL * -TRO * resshift31_EQ_O) +

-AU * resshift 31_EQ_O;

icc_V AU * DIV * DIV_OVERF +

ADDIT *

(RS1[31] * RS2[31] * -SM[31] +

-RS1[31] * -RS2[31] * SM[31]) +

SUBSTR * (RS1[31] * -RS2[31] * -SM[31] +

-RS1[31] * RS2[31] * SM[31]);

icc_C AU * ADDIT * (RS1[31] *

+RS2[31]

-SM[31] * (RS1[31] + RS2[31])) +

SUBSTR * (-RS1[31] * RS2[31] +

SM[31] * (-RS1[31] + RS2[31]));

xcc_N AU * EU[63] + -AU * resshift[63]

xcc_Z AU * (-DIV * -MUL *

+(SM_EQ_O)

DIV * (FS1 * SM_EQ_O + OPN5 +

-OPN6 * -END_ALU) +

MUL * -TRO * SM_EQ_O) + -AU * resshift_EQ_O;

xcc_V AU * ADDIT * (RS1[63] * RS2[63] * -SM[63] +

-RS1[63] * -RS2[63] * SM[63]) + SUBSTR *

(RS1[63] * -RS2[63] * -SM[63] +

-RS1[63] * RS2[63] * SM[63]);

xcc_C AU * ADDIT * (RS1[63] * RS2[63] + -SM[63] *

(RS1[63] + RS2[63])) +

SUBSTR * (-RS1[63] * RS2[63] +

SM[63] * (-RS1[63] + RS2[63])), где resshift выход сдвигателя 35,

TRO cигнал, говорящий о том, что нулевой разряд сумматора 10 хотя бы один раз при выполнении итераций был ненулевым;

ADDIT выполняется одна из операций сложения;

SM31_EQ_O SM[31:O] 0;

resshift31_EQ_O resshift[31:O] O;

resshift_EQ_O resshift O.

В формирователе 20 вырабатываются сигналы прерывания устройства переполнение при тегированных операциях overflow и деление на O div_zero:

overflow (opcode= TADDcc+opcode= TADDccTV) *

(RS1[1:0]0+RS2[1:0]0+RS1[31] * RS2[31] * (-SM[31]) +

(-RS1[31]) * (-RS2[31]) * SM[31]) + (opcode= TSUBcc +

opcode= TSUBccTV) * (RS1[1:0]-0+RS2[1:0]-0+RS1[31] *

(-RS2[31]) * (-SM[31]) + (-RS1[31]) * RS2[31] * SM[31]);

div_ zero DIV * OPN4 * (SM_EQ_O), где SM_EQ_O cигнал, говорящий о том, что выход сумматора 10 равен 0.

Формирователь 29 определяет по результату суммирования (выходу сумматора 10) (по количеству старших нулевых восьмерок) 3-х разрядную величину "грубого" сдвига msshift, которая через коммутатор 30 попадает в узел 25 управления сдвигателем и далее в сдвигатель 35. Здесь реализована следующая логика:

msshift[2] (-EQ8_O[7]) * (-EQ8_[61] * (-EQ8_O[5]) *

(EQ8_O[4]) * (EQ8_O[3] + EQ8_O[2] + EQ8_O[1] + EQ8_O[0]);

msshift[1] (-EQ8_O[7] * (-EQ8_O[6]) *

(EQ8_O[5] + EQ8_O[4]) + (-EQ8_O[7]) * (-EQ8_O[6]) *

(-EQ8_O[5] * (-EQ8_O[4]) + (-EQ8_O[3]) * (-EQ8_O[2]) *

(EQ8_O[1] + EQ8_O[0]);

msshift[0] (-EQ8_O[7]) * EQ8_O[6] + (-EQ8_O[7]) *

(-EQ8_O[6]) * (-EQ8_O[5]) * EQ8_O[4] + (-EQ8_O[7]) *

(-EQ8_O[6]) * (-EQ8_O[5]) * (-EQ8_O[4]) * (-EQ8_O[31] *

EQ8_O[2] + (-EQ8_O[7]) * (-EQ8_O[6]) * (-EQ8_O[5]) *

(-EQ8_O[4]) * (-EQ8_O[3]) * (-EQ8_O[2]) * (-EQ8_O[1]) *

EQ8_ O[0] где EQ8_[i] сборка нулей для i-й восьмерки разрядов с выхода сумматора 10.

Формирователь 33 анализирует старший байт с выхода сдвигателя 35, получаемый на выходе его третьей ступени, и вырабатывает 3-х разрядный код точного сдвига lsshift, который через коммутатор 34 "точного" сдвига попадает в узел 25 управления сдвигателем и далее сдвигатель 35. Формирователь 33 реализует следующую логику:

lsshift[2] (-EQ2_O[3] * (-EQ2_O[2]) *

(EQ2_O[1] + EQ2_O[0]);

lsshift[1] (-EQ2_O[3]) * EQ2_O[2] +

(-EQ2_O[3]) *

(-EQ2_O[2]) * (-EQ2_O[1]) * EQ2_O[0]

lsshift[0] (-au_byte[7]) * au_byte[6] +

(-EQ2_O[3]) *

(-au_byte[5]) * au_byte[4] + (-EQ2_O[3]) *

(-EQ2_O[2]) * (-au_byte[3]) * au_byte[2] +

(-EQ2_O[3]) * (-EQ2_O[2]) * (-EQ2_O[1]) *

(-au_byte[1]) * au_byte[0] где EQ2_O[i] сборка нулей для i-ой двойки разрядов с выхода au_byte сдвигателя 35;

au_byte выход после третьей ступени сдвигателя 35.

3-х разрядные коммутаторы 30 и 34 выполнены по обычной схеме коммутатора с 4-х направлений. Они передают на вход узла 25 управления сдвигателем либо количество сдвига, приходящее из управления, либо определенное в формирователях 33 и 29 значение точного и грубого сдвигов соответственно, либо выход сумматора 28, либо 0.

6-разрядный сумматор 28 вычисляет в дополнительном коде количество итераций, необходимое для выполнения многотактной операции, а также вырабатывает код сдвига для коррекции результата умножения.

6-и разрядные коммутаторы 22 и 23 выполнены по обычной схеме коммутаторов с 3-х направлений и управляют работой сумматора 28.

6-и разрядный регистр 26 хранит количество итераций.

Узел 27 обращения используется для инвертирования содержимого регистра 26.

Формирователь 24 вырабатывает входной перенос для сумматора 28

C_IQ_in -(POPCNT * IQT_EQ_O *

-TRO_REM) *

invert_IQT, где IQT_EQ_O сигнал, говорящий, что в регистре 26 записан 0;

invert_IQT сигнал обращения содержимого регистра 22 на узле 27.

В формирователе 32 вычисляется маска для каждого из 64 разрядов:

для i>=(64-SCM)

mask[i] 1;

для i< (64-SCM)

mask[i] 0, где SCM количество сдвигов, сформированное в узле 25. Разряды маски для сдвига влево перенумеровываются: самый младший разряд становится самым старшим.

64-разрядный коммутатор 36 выполнен по обычной схеме коммутатора с 2-х направлений. При командах сдвига на его выход проходит сформированная в формирователе 32 маска, во всех остальных случаях второй операнд, приходящий по шине 39.

Логический блок 37 реализован на 4-х входовых коммутаторах. Если выполнялась операция сдвига, то происходит маскирование результата сдвига и заполнение освободившихся разрядов знаком операнда при арифметическом сдвиге вправо. Здесь же выполняются и команды логики. Подключение операндов на управляющие входы коммутаторов в блоке 37 отражено в табл. 1.

Узел 25 управления вырабатывает сигналы управления блоком 37, коммутатором 36, формирователем 32 и сдвигателем 35. Для управления сдвигателем 35 формируется код сдвига scsh. Для команд SRL, SRA величина сдвига равна значению поля shcnt из устройства управления, а для команды SLL происходит пересчет количества сдвигов -(shcnt).

scsh shcnt * RIGHT + (-shcnt + 1) * LEFT, где shcnt приходящий из управления код сдвига;

scsh код сдвига для сдвигателя;

RIGHT признак выполнения сдвига вправо;

LEFT признак выполнения сдвига влево.

При формировании кода сдвига для формирователя 32 при сдвиге вправо учитывается номер позиции знака (маска расширяется):

SCM LEFT * shcnt + RIGHT * (codsign + shcnt), где SCM код сдвига для формирователя маски;

codsign номер позиции знака, приходящий из управления.

Логический блок 37 управляется сигналами y1, y2, у3, y4, которые формируются согласно табл. 2.

При выполнении команд пересылки меняется знак операнда. Для этого формируются сигналы

res_sign -sign * Fmov_neg + sign * -Fmov_neg + -Fmow_abs,

ins_63 (shcnt[5] + codsign[2]),

ins_sign FMOV_abs + FMOV_neg, где res_sign знак результата;

Fmow_neg признак операции инверсии знака, приходящий из управления;

Fmov_abs признак операции получения абсолютного значения операнда;

ins_ 63 признак того, что знак записывается в 63 разряд, иначе в 32 разряд.

ins_sign признак изменения знака.

С целью уменьшения количества оборудования используется циклический сдвигатель 35 вправо. Результирующая величина сдвига shcnt из узла 25 управляет шестью ступенями сдвигателя, на которых происходит сдвиг вправо на 0,32; 0,16; 0,8; 0,4; 0,2; 0,1 разрядов соответственно.

64-разрядный коммутатор 31 выполнен по обычной схеме коммутатора с 5-и направлений и пропускает на сдвигатель 35 одну из пяти величин, подлежащих сдвигу.

Все входящие в устройство элементы, узлы, блоки могут быть выполнены на элементах серии LCA 100К. В устройстве используется однофазная система синхронизации.

Арифметико-логическое исполнительное устройство выполняет следующие операции:

сложение (ADD, ADDcc, ADDX, ADDXcc);

тегированное сложение (TADDcc, TADDccTV);

вычитание (SUB, SUBcc, SUBX, SUBXcc);

тегированное вычитание (TSUBcc, TSUBccTV);

шаг умножения (MULScc);

деление (UDIV, SDIV, UDIVcc, SDIVcc, UDIVX, SDIVX);

умножение (UMUL, SMUL, UMULcc, SMULcc, MULX);

логические (AND, ANDcc, ANDN, ANDNcc, OR,

ORcc, ORN, ORNcc, XOR, XORcc, XNOR, XNORcc);

сдвига (SLL, SRL, SRA, SLLX, SRLX, SRAX);

подсчет количества единиц (РОPС);

пересылки вещественных чисел (FMOVs, FMOVd, FMOVq, FNEGs, FNEGd, FNEGq, FABSs, FABSd, FABSq).

Все операции, кроме операций умножения, деления и подсчета числа единиц, время выполнения которых зависит от конкретных операндов, являются однотактными.

Однотактные операции арифметики выполняются следующим образом: первый операнд, приходящий по шине 38 на вх 55-1, проходит через коммутатор 1 и узел 7 обращения и поступает на вход 1 сумматора 10. Другой операнд, приходящий по шине 39 на вх 56-1, с выхода коммутатора 2 поступает на узел 8 обращения, инвертируется в случае операции вычитания и подается на вход 2 сумматора 10. В сумматор 10 на вход 3 также поступает сигнал входного переноса, который формируется в формирователе 9. Входы 1 и 2 сумматора 10 расширяются до 65 разрядов (65 разряд заполняется либо знаком операнда (с учетом инверсии), либо нулем. Выход сумматора 10 (разряды 63-0) через коммутаторы 15 (вх 61-1) и 14 (вх 62-1) записывается в регистр 18, а также участвует в формировании признаков результата (icc и хсс) в формирователе 19 и сигнала 32-х разрядного переполнения при командах тегированного сложения и вычитания, формируемого в формирователе 20.

Операция сдвига вправо выполняется на комбинационном циклическом сдвигателе 35 вправо, при этом освободившиеся слева разряды с помощью маски, формируемой в формирователе 32 и проходящей через коммутатор 36, в блоке 37 заполняются нулями при логическом сдвиге и знаком операнда при арифметическом. Операции сдвига влево заменяются сдвигом вправо на величину 64-shcnt, при этом с помощью маски, формируемой в формирователе 32 и проходящей через коммутатор 36, в блоке 37 обнуляются освободившиеся справа разряды.

Логические операции выполняются в блоке 37 на коммутаторе, благодаря чему исключена инверсия второго операнда для команд ANDN, ANDNcc, ORN, ORNcc. На управляющие входы блока 37 подаются операнды, приходящие по шине 38 через коммутатор 31, сдвигатель 35 и по шине 39 через коммутатор 36, а на разрядные сигналы, сформированные в узле управления 25 из кода операций.

Операции пересылки могут сдвигать исходный операнд, поступающий по шине 38, с точностью до байта. В поле codsign, приходящем из внешнего устройства управления по шине 45, указывается номер старшего байта, содержащего знак операнда. Так как операции пересылки выполняются как сдвиг, то узел 25 управления сдвигателем формирует соответствующие команды сдвига. При выполнении пересылки вправо происходит обнуление левой части результата. При пересылке может задаваться обращение или обнуление знака, что определяется двумя разрядами, приходящими из внешнего устройства управления по шинам 46 и 47 соответственно.

Умножение выполняется в дополнительном коде с одним корректирующим шагом. Количество итераций равно числу значащих цифр множителя.

1. По сигналу запуска операции Phase_E, поступающему по шине 42, в следующем такте обнуляются счетчик итераций в формирователе 4, регистр 26 количества итераций. Множитель, приходящий по шине 39, проходит через коммутатор 2 и узел 8 обращения и преобразуется на сумматоре 10 в прямой код (при этом, если знак множителя равен 1, выход коммутатора 2 обращается, вход 3 сумматора 10 устанавливается в 1, вход 1 сумматора 10 при этом обнуляется).

2. Выход сумматора 10 анализируется на формирователе 29 "грубого" определения номера первой слева единицы. Выход сумматора 10 и значение "грубого" сдвига с выхода формирователя 29 подаются на вход 70-3 коммутатора 31 и вход 68-2 коммутатора 30 соответственно.

3. Старший байт, полученный в результате сдвига выхода сумматора 10 влево на величину, определенную в формирователе 29, берется с третьей ступени сдвигателя 35 и анализируется в формирователе 33 значения "точного" сдвига. Полученный номер первой слева единицы множителя (его прямого кода), представляющий собой конкатенацию выходов формирователей 29 и 33, проходит через коммутатор 22 и запоминается в регистре 26. Количество итераций получается вычитанием из "64" в сумматоре 28 содержимого регистра 26, которое обращается в узле 27.

4. С помощью коммутатора 3 с 64 направлений, управляемого счетчиком итераций формирователя 4, выбирается нулевой разряд множителя, приходящего по шине 39. В зависимости от его значения на вход 1 сумматора 10 с выхода коммутатора 1 подается либо 0 (если "0" разряд шины 39 0, либо множимое (приходящее по шине 38), (если "0" разряд шины 39 1). Входы 2 и 3 сумматора 10 при этом обнуляются. Первое частичное произведение с выхода сумматора 10 поступает на коммутатор 13 и записывается со сдвигом на один разряд вправо в регистр 17. Младший разряд частичного произведения (нулевой разряд суммы с выхода сумматора 10) через коммутаторы 15 и 14 записывается в самый старший разряд регистра 18 (ОРN3).

5. Счетчик итераций в формирователе 4 увеличивается на 1. Коммутатор 3 выбирает из шины 39 разряд, номер которого равен значению счетчика. Если этот разряд равен "1", то на вход 1 сумматора 10 через коммутатор 1 и узел 7 обращения подается операнд по шине 38 (множимое), если же этот разряд равен "0", то 0. На вход 3 сумматора 10 с выхода формирователя 9 подается 0, а частичное произведение, полученное в предыдущей итерации, с выхода регистра 17 поступает на вход 56-3 коммутатора 2 и с его выхода через узел 8 подается на вход 2 сумматора 10. Результат сложения с выхода 10 поступает на коммутатор 13 и записывается со сдвигом на 1 разряд вправо в регистр 17, содержимое регистра 18 с помощью коммутаторов 15 и 14 сдвигается на 1 разряд вправо, и в освободившийся старший разряд записывается нулевой разряд частичного произведения с выхода сумматора 10.

6. Пункт 5 повторяется, пока значение счетчика итераций в формирователе 4 не станет равным количеству итераций, которое запомнено в регистре 26. При совпадении этих двух величин в блоке 6 вырабатывается сигнал равенства и выполняется шаг коррекции: к последнему частичному произведению прибавляется инверсия множимого (на входе 3 сумматора 10 при этом устанавливается 1), если множитель отрицателен (при выполнении команд SMUL, SMULcc), или, если выполняется команда MULX, и 63-ий разряд множителя равен "1". На шаге коррекции последнее частичное произведении с выхода сумматора 10 записывается без сдвига в регистр 17, в это время регистр 18 блокируется.

7. Младшие разряды произведения, хранящиеся в регистре 18, сдвигаются в сдвигателе 35 вправо на (64-RgIQ) разрядов и записываются в регистр 18 (FS1).

8. Старшие разряды произведения, хранящиеся в регистре 17, сдвигаются в сдвигателе 35 влево на число разрядов, равное содержимому формирователя 26, и записываются в те разряды регистра 18, для которых значение выхода формирователя 32 равно 1. В разрядах, для которых выход формирователя 32 равен 0, сохраняются младшие разряды произведения. В формирователе 21 вырабатывается сигнал конца операции шина 52 (FS2).

Деление производится без восстановления остатка в дополнительном коде с нормализацией делителя до делимого.

1. По сигналу запуска операции Phase_E, поступающему по шине 42, в следующем такте обнуляются счетчик итераций в формирователе 4, регистр 26 количества итераций. Делимое, приходящее по шине 38, проходит через коммутатор 1 и узел 7 обращения и преобразуется на сумматоре 10 в прямой код (при этом, если знак делимого равен 1, выход коммутатора 1 обращается в узле 7, вход 3 сумматора 10 устанавливается в 1, вход 2 сумматора 10 при этом обнуляется).

2. Выход сумматора 10 анализируется на формирователе 29 "грубого" определения номера первой слева единицы. Выход сумматора 10 и значение "грубого" сдвига с выхода формирователя 29 подаются на вход 70-3 коммутатора 31 и вход 68-2 коммутатора 30 соответственно. Старший байт, полученный в результате сдвига выхода сумматора 10 влево на величину, определенную в формирователе 29, берется с третьей ступени сдвигателя 35 и анализируется в формирователе 33 значения "точного" сдвига. Полученный номер первой слева единицы делимого (его прямого кода), представляющий собой конкатенацию выходов формирователей 29 и 33, проходит через коммутатор 22 и запоминается в регистре 26 (OPN1, OPN2).

3. Делитель, приходящий по шине 39, проходит через коммутатор 2 и узел 8 обращения и преобразуется на сумматоре 10 в прямой код (при этом, если знак делителя равен 1, выход коммутатора 2 обращается в узле 8, вход 3 сумматора 10 устанавливается в 1, вход 1 сумматора 10 при этом обнуляется).

4. Выход сумматора 10 анализируется в формирователе 29 "грубого" определения номера первой слева единицы. Выход сумматора 10 и значение "грубого" сдвига с выхода формирователя 29 подаются на вход 70-3 коммутатора 31 и вход 68-2 коммутатора 30 соответственно. Старший байт, полученный в результате сдвига выхода сумматора 10 влево на величину, определенную в 29, берется с третьей ступени сдвигателя 35 и анализируется в формирователе 33 определения "точного" сдвига. Полученный номер первой слева единицы делителя (его прямого кода), представляющий собой конкатенацию выходов формирователей 29 и 33, проходит через коммутатор 23 и поступает на вход 2 сумматора 28. На вход 1 сумматора 8 при этом поступает обращенное на узле 27 содержимое регистра 26, а на вход 3 сумматора 28 перенос с выхода формирователя 24. Полученная таким образом разница номеров первых слева единиц в прямом коде делителя и делимого с выхода сумматора 28 через коммутатор 22 запоминается в регистре 26. Количество цифр частного может быть равно содержимому 26 или (содержимое регистра 26+1). Поэтому количество итераций равно (содержимое регистра 26+1).

5. Делитель (шина 39) через коммутатор 31 поступает на сдвигатель 35, сдвигается на сдвигателе 35 влево на величину, которая подается с выхода сумматора 28 на узел 25. На выходе сдвигателя 35 до конца операции держится нормализованный делитель. В регистр 18 с выхода формирователя 11 записывается знак частного или 0, если делитель больше делимого. В этом же такте определяется, равен ли нулю делитель, и если равен, то в формирователе 20 вырабатывается прерывание деление на ноль (шина 54). В последних двух случаях в формирователе 21 вырабатывается сигнал конца операции шина 52 (OPN5).

6. По сигналу OPN6 с выхода формирователя 4 начинается первая итерация: величина нормализованного делителя с выхода сдвигателя 35 вычитается из делимого на сумматоре 10. (При этом, если знаки делимого и делителя совпадают, то делитель, поступающий по шине 39, обращается на узле 8, на вход 3 сумматора 10 подается "1" с выхода формирователя 9, если же знаки отличаются, то делитель прибавляется, сигналы обращения для узла 8 и выход формирователя 9, поступающий на вход 3 сумматора 10, устанавливаются в "0". На вход 2 сумматора 10 подается с выхода сдвигателя 35 нормализованный делитель). Остаток с выхода сумматора 10 запоминается в регистре 17 со сдвигом на один разряд влево, который выполняется на коммутаторе 13. Цифра частного получается в формирователе 11 при анализе знаков остатка и делителя: если они одинаковы или остаток равен "0", то цифра частного равна "1". Содержимое регистра 18 сдвигается влево на один разряд, в освободившийся при этом младший разряд записывается полученная цифра частного с выхода формирователя 11. Это выполняется с помощью коммутаторов 15 и 14. В этом же такте в блоке 12 определяется ситуация переполнения (при операциях SDIV, SDIVcc, UDIV, UDIVcc): значащие цифры частного не помещаются в отведенное для него количество разрядов (при беззнаковом делении содержимое регистра 26 больше или равно 32 и первая цифра частного равна "1"; при знаковом делении содержимое регистра 26 больше или равно 31, и первая цифра положительного частного равна "1" или первая цифра отрицательного частного равна "0". При возникновении переполнения в регистр 18 записывается максимально возможное при данном коде операции и знаке результата значение частного, поступающее с выхода формирователя 16 через коммутаторы 14 и 15, и в формирователе 21 вырабатывается сигнал конца операции 52. При делении без знака в регистр 18 записывается OFU-h'00000000FFFFFFFF, в случае деления со знаком при положительном результате OFSP-h'000000007FFFFFFFF, а при отрицательном OFSN-h'FFFFFFFF80000000.

7. В формирователе 4 счетчик увеличивается на 1. Сдвинутый влево остаток предыдущей итерации из регистра 17 поступает через коммутатор 1 и узел 7 на вход 1 сумматора 10, на вход 2 сумматора 10 через коммутатор 2 и узел 8 подается с выхода сдвигателя 35 делитель. Если знаки остатка и делителя различны (выход формирователя 9, подаваемый на вход 3 сумматора 10 при этом равен "0", и делитель проходит через узел 7 без обращения). Если знаки остатка и делителя отличаются, или, если остаток, содержащийся в регистре 17, равен "0", то на вход 3 сумматора 10 с выхода формирователя 9 подается "1", и делитель обращается на узле 7. Анализируется знак полученного на выходе сумматора 10 остатка, записываемого через коммутатор 13 со сдвигом влево в регистр 17, а очередная цифра частного с выхода формирователя 11 через коммутаторы 15 и 14 в младший разряд регистра 18 (при этом предыдущее содержимое регистра 18 сдвигается на один разряд влево).

8. Пункт 7 повторяется до тех пор, пока значение счетчика в формирователе 4 не станет равным выходу сумматора 28. При совпадении этих двух величин выполняется последняя итерация.

9. Если полученное частное отрицательно и ни разу при итерациях не было нулевого остатка, то выполняется коррекция результата к вычисленному частному из регистра 18, поступающему через коммутатор 2 и узел 8 на вход 1 сумматора 10, прибавляется "1". Если же частное больше "0", или делимое делится на делитель без остатка, то к частному прибавляется "0". В первом случае на вход 3 сумматора 10 с выхода формирователя 9 подается "1", во втором "0", и в обоих случаях вход 1 сумматора 10 обнуляется. Полученный окончательный результат записывается с выхода сумматора 10 в регистр 18, в формирователе 21 вырабатывается сигнал конца операции END_ALU шина 52.

Операцию подсчета количества единиц РОРС проводят следующим образом.

1. По сигналу запуска операции Phase_E, поступающему по шине 42, в следующем такте обнуляются счетчик итераций формирователя 4, регистр 26 количества итераций. Операнд, приходящий по шине 39, подается на вход 2 сумматора 10 через узел 8 обращения и коммутатор 2, при этом входы 1 и 3 сумматора обнуляются. Выход сумматора 10 анализируется в формирователе 29 "грубого" определения номера первой слева единицы. Выход сумматора 10 и значение "грубого" сдвига с выхода формирователя 29 подаются на вход 70-3 коммутатора 31 и вход 68-2 коммутатора 30 соответственно. Старший байт, полученный в результате сдвига выхода сумматора 10 влево на величину, определенную в формирователе 29, берется с третьей ступени сдвигателя 35 и анализируется на формирователе 33 определения "точного" сдвига. Полученный номер первой слева единицы операнда (его прямого кода), представляющий собой конкатенацию выходов формирователей 29 и 33, проходит через коммутатор 22 и запоминается в регистре 26 (OPN1, OPN2).

2. С помощью коммутатора 3 с 64 направлений нулевой разряд шины 39 подается на вход 3 сумматора 10, на два другие входа сумматора 10 подается "0". Результат сложения запоминается в регистрах 17 и 18 (OPN3).

3. Счетчик в формирователе 4 увеличивается на единицу. Анализируется очередной разряд шины 39. Номер очередного разряда задается счетчиком итераций в формирователе 4. Если выбранный таким образом разряд шины 39 равен "1", то вход 3 сумматора 10 устанавливается в "1", на вход 2 подается содержимое регистра 17, вход 1 сумматора 10 до окончания операции устанавливается в "0". Очередная сумма записывается в регистры 17 и 18.

4. Пункт 3 повторяется до момента совпадения значения счетчика в формирователе 4 и количества итераций сумматора 28, при этом вырабатывается сигнал конца операции END_ALU (шина 52).

При этом если операнд в шине 39 содержит "1" в самом старшем разряде, то в регистр 26 записывается не 63 (111111), а "0". Далее операцию выполняют обычным способом.

Использование изобретения позволяет обеспечить по сравнению с известными аппаратное выполнение команд целого умножения и деления. При этом для выполнения операций требуется 1 команда, при программном выполнении несколько команд.

В табл. 3 дана зависимость времени выполнения подпрограммы умножения от длины множителя (при реализации операций умножения программным путем).

Среднее время умножения составляет 24 такта.

При аппаратном выполнении 16 тактов, т.е. в 1,5 раза быстрее.

Операция деления выполняется быстрее в 2-3 раза.

Устройство позволяет обрабатывать 64-разрядные числа за счет выполнения узлов обращения, сумматора, сдвигателя, логического блока 64-разрядными. Это повышает точность устройства.

Кроме того, выполняется дополнительная операция подсчета числа единиц.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности. Устройство содержит два узла обращения, сумматор, дешифратор, сдвигатель, формирователь маски, логический блок, блок управления, узел управления, формирователь признаков результата, формирователь прерывания, выходной коммутатор, выходной регистр. Новым является введение трех входных коммутаторов, формирователя временных стробов, блока сравнения, двух формирователей переноса, формирователя знака и цифр частного, семи коммутаторов, двух регистров, дополнительного выходного коммутатора, формирователя знака результата, формирователя конца операций, дополнительного узла обращения, дополнительного сумматора, формирователя значений грубого сдвига, формирователя значений точного сдвига. Введение новых блоков и связей позволяет повысить производительность, точность, расширить функциональные возможности устройства за счет аппаратной реализации операций умножения, деления, подсчета числа и за счет выполнения узлов обращения, сумматора, сдвигателя, логического блока 64-разрядными. 6 ил., 3 табл.

АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО, содержащее два узла обращения, сумматор, дешифратор, сдвигатель, формирователь маски, логический блок, блок управления, узел управления, формирователь признаков результата, формирователь прерываний, выходной коммутатор, выходной регистр, первый и второй информационные входы сумматора соединены с выходами первого и второго узлов обращения, соответственно, выход сумматора подключен к первым информационным входам выходного коммутатора, формирователя признаков результата, формирователя прерываний, второй и третий информационные входы которого соединены с входными шинами первого и второго операндов, вторые информационные входы выходного коммутатора и формирователя признаков результата подключены к выходу логического блока, первый выход узла управления соединен с входом формирователя маски, выход которого подключен к первому информационному входу блока управления, второй выход узла управления соединен с управляющим входом сдвигателя, вход дешифратора подключен к входной шине кода операций устройства, первый информационный вход узла управления соединен с входной шиной величины сдвига устройства, выход дешифратора соединен с вторыми информационными входами узла управления и блока управления, выход которого подключен к управляющим входам первого и второго узлов обращения, выходного коммутатора и выходного регистра, информационный вход которого соединен с выходом выходного коммутатора, выход выходного регистра подключен к выходной шине результата операций устройства, выход формирователя признаков результата соединен с выходной шиной кодов условий устройства, первый выход формирователя прерываний подключен к выходной шине прерывания переполнения при тегированных операциях устройства, отличающееся тем, что в устройство введены три входных коммутатора, формирователь временных стробов, блок сравнения, два формирователя переноса, формирователь знака и цифр частного, семь коммутаторов, два регистра, дополнительный выходной коммутатор, формирователь знака результата, формирователь конца операций, дополнительный узел обращения, дополнительный сумматор, формирователь значений грубого сдвига, формирователь значений точного сдвига, причем первые информационные входы первого входного коммутатора, первого формирователя переноса, формирователя знака и цифр частного, пятого коммутатора, третий информационный вход формирователя признаков результата подключены к входной шине первого операнда, информационный вход третьего входного коммутатора, первые информационные входы второго входного коммутатора, седьмого коммутатора, вторые информационные входы первого формирователя переносов, формирователя знака и цифр частного, пятого коммутатора, четвертый информационный вход формирователя признаков результата соединены с входной шиной второго операнда, третий информационный вход первого формирователя переноса подключен к входной шине входного переноса, первый информационный вход формирователя временных стробов, третий информационный вход блока управления соединены с входной шиной системного сброса, второй информационный вход формирователя временных стробов, четвертый информационный вход блока управления соединены с шиной начала операции, первые информационные входы формирователя знака результата, четвертого и шестого коммутаторов, вторые информационные входы первого и второго входных коммутаторов подключены к шине логического "0", второй информационный вход формирователя знака результата соединен с шиной логической "1", выход первого входного коммутатора подключен к входу первого узла обращения, выход второго входного коммутатора соединен с входом второго узла обращения, выход сумматора подключен к первому информационному входу дополнительного выходного коммутатора, к третьим информационным входам формирователя знака и цифр частного, пятого коммутатора, к информационному входу первого коммутатора, к входу формирователя значений грубого сдвига, к третьему информационному входу пятого коммутатора, выход которого соединен с входом первого регистра, выход которого подключен к третьим информационным входам первого и второго входных коммутаторов, к четвертому информационному входу первого формирователя переноса, выход выходного регистра соединен с вторым информационным входом дополнительного выходного коммутатора, с четвертыми информационными входами первого входного коммутатора, пятого коммутатора, с пятыми информационными входами первого формирователя переноса, формирователя признаков результата, выход третьего входного коммутатора подключен к шестому информационному входу первого формирователя переноса, к пятому информационному входу блока управления, к шестому информационному входу которого, к первому информационному входу блока сравнения, к седьмому информационному входу первого формирователя переноса, к управляющему входу третьего входного коммутатора подключен первый выход формирователя временных стробов, второй выход которого соединен с шестым информационным входом формирователя признаков результата, с седьмым информационным входом блока управления, с восьмым информационным входом первого формирователя переноса, с первым информационным входом формирователя конца операций, второй информационный вход которого, третий информационный вход формирователя знака результата, четвертые информационные входы формирователя знака и цифр частного, формирователя прерываний, седьмой информационный вход формирователя признаков результата, девятый информационный вход первого формирователя переноса подключены к третьему информационному выходу формирователя временных стробов, выход дешифратора соединен с информационным входом второго формирователя переноса, с четвертым информационным входом формирователя знака результата, с пятыми информационными входами формирователя знака и цифр частного, формирователя прерываний, с восьмым информационным входом формирователя признака результата, с десятым информационным входом первого формирователя переноса, с третьими информационными входами формирователя временных стробов, формирователя конца операций, четвертый информационный вход которого и четвертый информационный вход формирователя временных стробов подключены к выходу блока сравнения, выход формирователя знака и цифр частного соединен с третьим информационным входом дополнительного выходного коммутатора, с пятым информационным входом формирователя знака результата, с одиннадцатым входом первого формирователя переноса, выход которого подключен к третьему информационному входу сумматора, выход формирователя знака результата соединен с четвертым информационным входом дополнительного выходного коммутатора, выход которого подключен к третьему информационному входу выходного коммутатора, второй выход формирователя прерываний соединен с пятыми информационными входами формирователя временных стробов, формирователя конца операций, с выходной шиной прерывания деления на 0 устройства, выход формирователя конца операций подключен к шестому информационному входу формирователя временных стробов, к выходной шине конца многотактных операций устройства, первый выход сдвигателя соединен с входом формирователя значения точного сдвига, выход которого подключен к первым информационным входам второго и третьего коммутаторов, к второму информационному входу шестого коммутатора, выход формирователя значения грубого сдвига соединен с вторыми информационными входами второго, третьего и четвертого коммутаторов, третий информационный вход которого и третий информационный вход шестого коммутатора подключены к входной шине величины сдвига устройства, второй информационный вход блока сравнения, третьи информационные входы второго и третьего коммутаторов, четвертые информационные входы четвертого и шестого коммутаторов соединены с выходом дополнительного сумматора, первый информационный вход которого подключен к выходу дополнительного узла обращения, информационный вход которого соединен с выходом второго регистра, информационный вход которого подключен к выходу второго коммутатора, выход третьего коммутатора соединен с вторым информационным входом дополнительного сумматора, третий информационный вход которого соединен с выходом второго формирователя переноса, выход шестого коммутатора подключен к третьему информационному входу узла управления, четвертый информационный вход которого соединен с выходом четвертого коммутатора, пятый, шестой, седьмой информационные входы узла управления подключены соответственно к входной шине номера байта, к первой управляющей шине, к второй управляющей шине устройства, выход пятого коммутатора соединен с информационным входом сдвигателя, второй выход которого подключен к первому управляющему входу логического блока, второй управляющий вход которого соединен с выходом седьмого коммутатора, второй информационный вход которого подключен к выходу формирователя маски, выход логического блока соединен с четвертым информационным входом второго коммутатора, управляющие входы второго регистра первого и второго входных коммутаторов, первого, второго, третьего, четвертого, пятого, шестого коммутаторов, формирователя временных стробов, дополнительного выходного коммутатора, дополнительного узла обращения, второго формирователя переноса соединены с выходом блока управления, управляющий вход логического блока, управляющий вход седьмого коммутатора подключены к выходу узла управления.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Y.G.Catanzaro | |||

| "Optimizing Compiler for the SPARC Architecture" | |||

| - The SPARC Technical Papers: New York, 1991, pp | |||

| Трансляция, предназначенная для телефонирования быстропеременными токами | 1921 |

|

SU249A1 |

Авторы

Даты

1995-05-10—Публикация

1992-12-30—Подача