Изобретение относится к технике автоматического управления и регулирования и может быть использовано в системах автоматического управления объектами с переменными параметрами.

Цель изобретения повышение качества адаптируемых коэффициентов за счет выполнения требований на гладкость значений коэффициентов. Поставленная цель достигается тем, что в устройство для адаптивной идентификации объекта, содержащее объект управления, три задатчика, последовательно включенные первый амплитудно-импульсный модулятор, второй блок вычитания и третий блок памяти, последовательно включенные второй амплитудно-импульсный модулятор, третий блок вычитания и четвертый блок памяти, последовательно включенные третий амплитудно-импульсный модулятор и четвертый блок вычитания, первый и второй сумматоры, первый и второй блок памяти, пятый и шестой сумматоры, пятый, шестой и седьмой блоки памяти, блок расчета корректировок первого варианта, включающий первый блок вычитания и блок расчета корректировок второго варианта, причем блоки расчета корректировок первого и второго вариантов включают соответственно первый и четвертый функциональные блоки, каждый из которых состоит из двух квадраторов, третьего сумматора и четвертого задатчика, второй и пятый функциональные блоки, каждый из которых состоит из двух блоков умножения и четвертого сумматора, третий и шестой функциональные блоки, каждый из которых состоит из последовательно включенных второго блока уменьшения, первого блока деления, первого ограничителя и первого масштабирующего блока, последовательно включенных четвертого блока умножения, второго блока деления, второго ограничителя и второго масштабирующего блока, вторые входы второго, третьего и четвертог блоков вычитания подключены к выходам соответственно первого, второго и третьего задатчиков, а выходы к первому, второму и третьему входам блока расчета корректировок первого варианта, первый и второй выходы которого подключены к вторым входам соответственно первого и второго сумматоров, выход первого сумматора соединен с четвертым входом блока расчета корректировок первого варианта, выход второго сумматора соединен с пятым входом блока расчета корректировок первого варианта, входы первого и второго блоков памяти подключены к выходам соответственно первого и второго сумматоров, а выходы к первым входам соответственно первого и второго сумматоров, выходы третьего и четвертого блоков памяти соединены соответственно с первым и вторым входами блока расчета корректировок второго варианта, выходы пятого и шестого сумматоров подключены соответственно к первому и второму выходам устройства, первый вход блока расчета корректировок первого варианта соединен с первыми входами первого, второго и третьего функциональных блоков, второй вход с вторыми входами первого, второго и третьего функциональных блоков, третий вход с вторым входом первого блока вычитания, выход которого подключен к третьему входу третьего функционального блока, четвертый и пятый входы блока расчета корректировок первого варианта подключены соответственно к третьему и четвертому входам второго функционального блока, первый вход первого блока вычитания соединен с выходом второго функционального блока, четвертый вход третьего функционального блока соединен с вторым выходом первого функционального блока, первый и второй выходы третьего функционального блока являются соответственно первым и вторым выходами блока расчета корректировок первого варианта, первый вход блока расчета корректировок второго варианта соединен с первыми входами четвертого, пятого и шестого функциональных блоков, второй вход с вторыми входами четвертого, пятого и шестого функциональных блоков, четвертый вход шестого функционального блока соединен с вторым выходом четвертого функционального блока, первый и второй входы первого и четвертого функциональных блоков через первый и второй квадраторы соединены соответственно с первым и вторым входами третьего сумматора, первый и второй входы второго и пятого функциональных блоков подключены к первым входам соответственно первого и третьего блоков умножения, выходы которых соединены соответственно с первым и вторым входами четвертого сумматра, выход которого является выходом второго и пятого функциональных блоков, вторые входы первого и третьего блоков умножения являются соответственно третьим и четвертым входами второго и пятого функциональных блоков, первый и второй входы третьего и шестого функциональных блоков подключены к первым входам соответственно второго и четвертого блоков умножения, вторые входы которых соединены с третьим входом третьего и шестого функциональных блоков, четвертый вход третьего и шестого функциональных блоков соединен с вторыми входами первого и третьего блоков деления, выходы первого и второго масштабирующих блоков являютсясоединен с вторыми входами первого и третьего блоков деления, выходы первого и второго масштабирующих блоков являются соответственно первым и вторым выходами третьего и шестого функциональных блоков, введены три датчика, восьмой, девятый, десятый, одиннадцатый и двенадцатый блоки памяти, третий и четвертый масштабирующие блоки, в блок расчета корректировок второго варианта пятый, шестой, седьмой и восьмой блоки вычитания, в первый и четвертый функциональные блоки пятый блок умножения, седьмой сумматор и пятый задатчик, входы девятого и десятого блоков памяти соединены с выходми соответственно первого и второго блоков памяти, а выходы соответственно с третьим и четвертым входами блока расчета корректировок второго варианта, первый и второй выходы которого подключены к первым входам соответственно пятого и шестого сумматоров, вторые входы пятого и шестого сумматоров соединены с выходами соответственно одиннадцатого и двенадцатого блоков памяти, входы которых подключены к выходам соответственно первого и второго сумматоров, выходы одиннадцатого и двенадцатого блоков памяти являются соответственно третьим и четвертым выходами идентификатора, выходы пятого и шестого сумматоров подключены к входам соответственно шестого и седьмого блоков памяти, входы пятого и восьмого блоков памяти соединены с выходами соответственно шестого и седьмого блоков памяти, а выходы соответственно с седьмым и восьмым входами блока расчета корректировок второго варианта, входы третьего и четвертого масштабирующих блоков подключены к выходам соответственно шестого и седьмого блоков памяти, а выходы соответственно к пятому и шестому входам блока расчета корректировок второго варианта, в котором третий, пятый и седьмой входы являются соответственно первым, вторым и третьим входами седьмого блока вычитания, выход которого подключен к третьему входу пятого функционального блока, четвертый, шестой и восьмой входы блока расчета корректировок второго варианта соединены соответственно с первым, вторым и третьим входами восьмого блока вычитания, выход которого подключен к четвертому входу пятого функционального блока, первые входы пятого и шестого блоков вычитания в блоке расчета корректировок второго варианта соединены соответственно с первым и вторым выходами шестого функционального блока, третий вход которого подключен к выходу пятого функционального блока, вторые входы пятого и шестого блоков вычитания соединены с выходами соответственно седьмого и восьмого блоков вычитания, а выходы пятого и шестого блоков вычитания являются соответственно первым и вторым выходами блока расчета корректировок второго варианта, пятый вход шестого функционального блока соединен с первым выходом четвертого функционального блока, пятый вход третьего функционального блока соединен с первым выходом первого функционального блока, в первом и четвертом функциональных блоках первый вход пятого блока умножения соединен с выходом третьего сумматора, второй вход пятого блока умножения с выходом четвертого задатчика, а выход с первым входом седьмого сумматора, второй вход которого подключен к выходу пятого задатчика, а выход является вторым выходом первого и четвертого функциональных блоков, первый выход которых соединен с выходом четвертого задатчика, пятый вход третьего и шестого функциональных блоков подключены к вторым входам первого и второго масштабирующих блоков, первый и второй входы объекта управления подключены к входам соответственно первого и второго датчиков, а выход к входу третьего датчика, выходы первого, второго и третьего датчиков соединены с входами соответственно первого, второго и третьего амплитудно-импульсных модуляторов.

Введение новых блоков и связей позволяет повысить качество адаптируемых коэффициентов за счет выполнения требований на гладкость значений коэффициентов. Эти блоки и связи известны, однако их совокупность позволяет проявить новое свойство, что приведет к повышению качества идентификации и, следовательно, позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

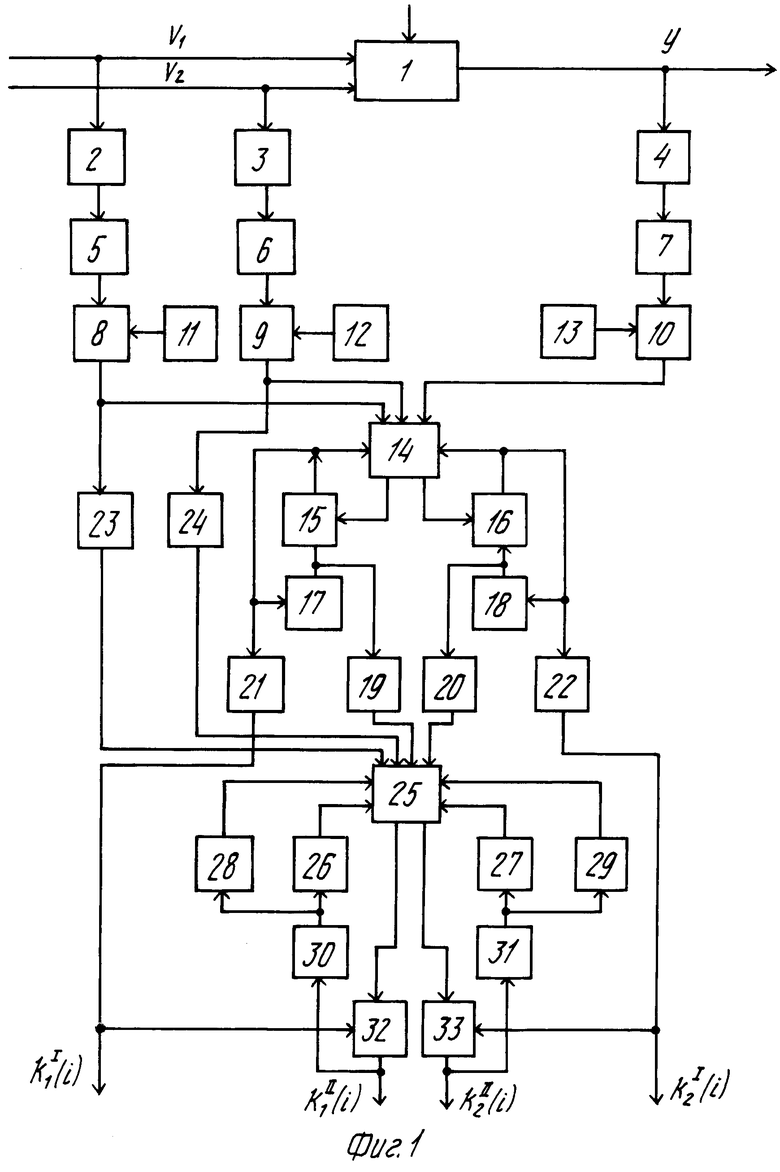

На фиг. 1 приведена схема многовариантного идентификатора и приняты обозначения: V1, V2 первая и вторая входные переменные объекта; Y выходная переменная объекта; ν неконтролируемые возмущения, действующие на объект; k1I(i), k2I(i) первый вариант адаптивных коэффициентов на i-м шаге; k1II(i), k2II(i) второй вариант адаптируемых коэффициентов на i-м шаге.

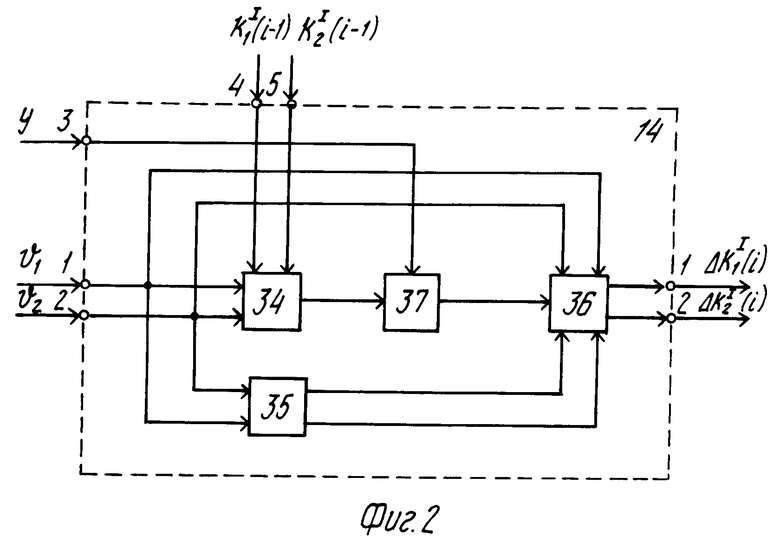

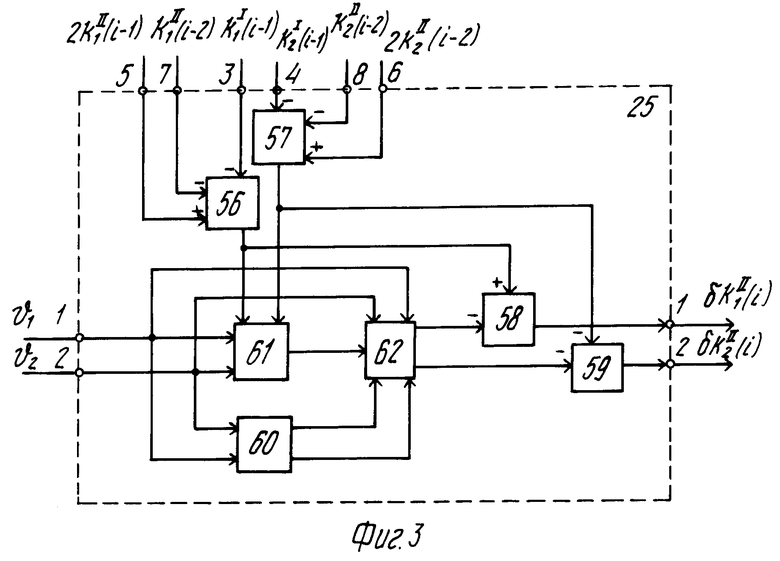

На фиг. 2 приведена схема блока расчета корректировок первого варианта; на фиг. 3 схема блока расчета корректировок второго варианта и приняты обозначения: v1, v2 приращения входных переменных относительно среднего уровня; y приращение выходной переменной относительно среднего уровня; Δk1I(i), Δk2I(i) первый вариант корректировок адаптируемых коэффициентов на i-м шаге; δk1II(i), δ k2II(i) второй вариант корректировок адаптируемых коэффициентов на i-м шаге; k1I(i-1), k2I(i-1) первый вариант адаптируемых коэффициентов на (i-1)-м шаге; 2k1II(i-1), 2k2II(i-1) второй вариант адаптируемых коэффициентов на (i-1)-м шаге; k1II(i-2), k2II(i-2) второй вариант адаптируемых коэффициентов на (i-2)-м шаге.

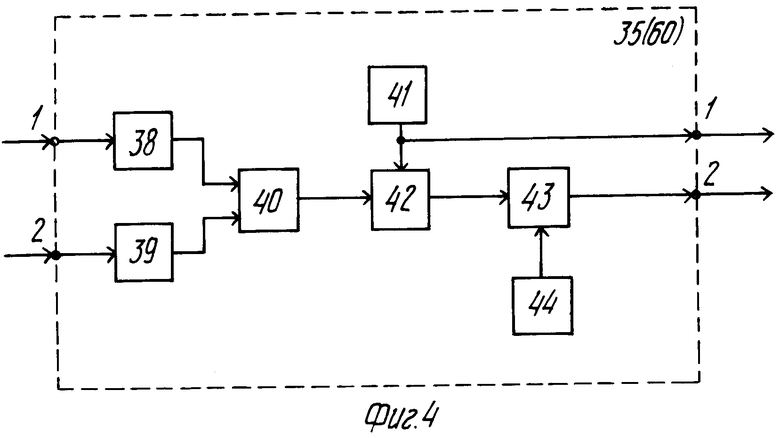

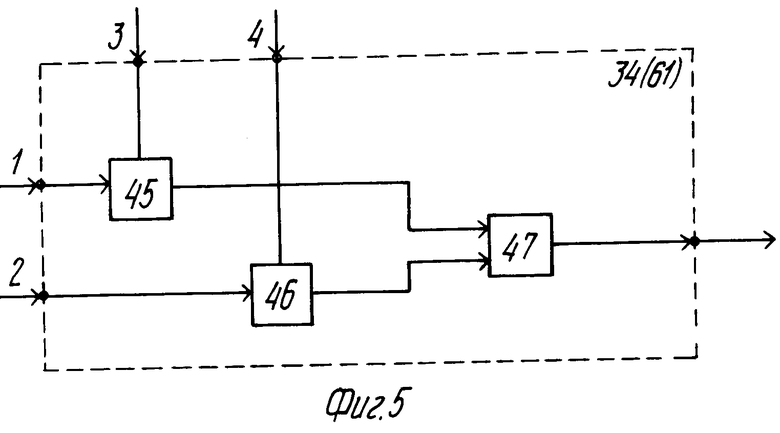

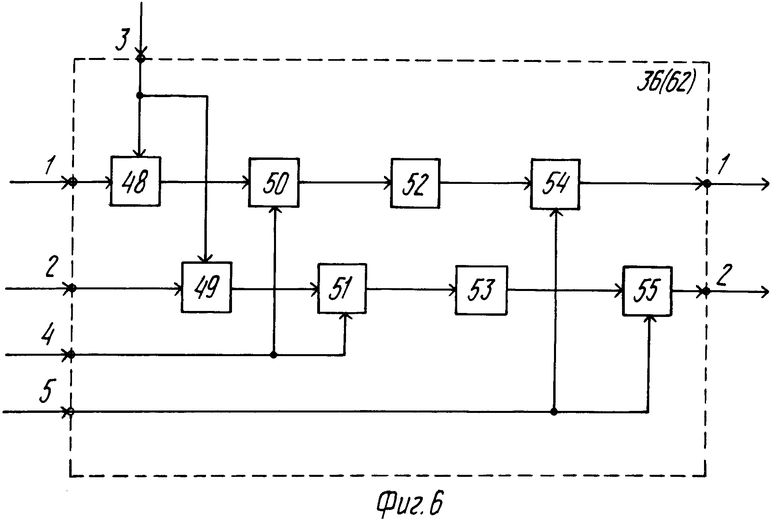

На фиг. 4 приведена схема первого и четвертого функциональных блоков; на фиг. 5 схема второго и пятого функциональных блоков, на фиг. 6 схема третьего и шестого функциональных блоков.

Многовариантный идентификатор содержит объект управления 1, первый 2, второй 3 и третий 4 датчики, первый 5, второй 6 и третий 7 амплитудно-импульсные модуляторы, второй 8, третий 9 и четвертый 10 блоки вычитания, первый 11, второй 12 и третий 13 задатчики, блок расчета 14 корректировок первого варианта, первый 15 и второй 16 сумматоры, первый 17, второй 18, девятый 19, десятый 20, одиннадцатый 21, двенадцаты 22, третий 23 и четвертый 24 блоки памяти, блок расчета 25 корректировок второго варианта, пятый 26 и восьмой 27 блоки памятьи, третий 28 и четвертый 29 масштабирующие блоки, шестой 30 и седьмой 31 блоки памяти, пятый 32 и шестой 33 сумматоры, второй 34, первый 35 и третий 36 функциональные блоки, первый 37 блок вычитания, первый 38 и второй 39 квадраторы, третий 40 сумматор, четвертый 41 задатчик, пятый блок 42 умножения, седьмой 43 сумматор, пятый 44 задатчик, первый 45 и третий 46 блоки умножения, четвертый 47 сумматор, второй 48 и четвертый 49 блоки умножения, первый 50 и второй 51 блоки деления, первый 52 и второй 53 ограничители, первый 54 и второй 55 масштабирующие блоки, седьмой 56, восьмой 57, пятый 58 и шестой 59 блоки вычитания, четвертый 60, пятый 61 и шестой 62 функциональные блоки.

Входные переменные V1 и V2 поступают на объект 1, а также на первый 2 и второй 3 датчики, а затем на первый 5 и второй 6 амплитудно-импульсные модуляторы. Выходной сигнал объекта 1 подается на вход третьего датчика 4, а затем на третий амплитудно-импульсный модулятор 7. Амплитудно-импульсные модуляторы осуществляют дискретное преобразование аналоговых входных и выходного сигналов объекта 1, в результате чего на их выходах получают последовательности амплитудно-модулированных импульсов V1(i), V2(i) и Y(i) в i-е моменты времени.

Выходные импульсы амплитудно-импульсных модуляторов 5, 6 и 7 поступают на первые входы соответственно второго 8, третьего 9 и четвертого 10 блоков вычитания, где из них вычитаются импульсы средних значений V1, V2 и Y, поступающие с выходов соответственно первого 11, второго 12 и третьего 13 задатчиков. На выходах второго 8, третьего 9 и четвертого 10 блоков вычитания получаются импульсы v1, v2 и y об отклонениях переменных от их средних значений. Импульсы с v1, v2 и y подаются на первый, второй и третий входы блока 14 расчета корректировок первого варианта.

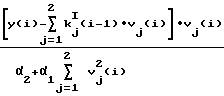

В блоке 14 расчета корректировок первого варианта реализуется процедура

Δk

(1)

(1)

y (2) где ΔkjI(i) первый вариант корректировки j-го коэффициента на i-м шаге;

(2) где ΔkjI(i) первый вариант корректировки j-го коэффициента на i-м шаге;

α1 α2 показатели, характеризующие соответственно гладкость и точность адаптируемых коэффициентов, выбираемые в процессе наладки идентификатора,

j для данного устройства равна "2", но по аналогии можно сделать устройство и для j > 2.

Для реализации процедуры (1), (2) импульсы с первого и второго входов поступают соответственно на первый и второй входы первого функционального блока 35 и через первый 38 и второй 39 квадраторы идут на третий сумматор 40, а затем на первый вход пятого блока 42 умножения. На второй вход этого же блока 42 умножения поступает импульс о величине показателя α1 выражения (2) с выхода четвертого задатчика 41. Поступившие в пятый блок 42 умножения импульсы перемножаются и в седьмом сумматоре 43 складываются с импульсом о величине показателя α2, поступившим с выхода пятого задатчика 40. В результате на выходе седьмого сумматора 43 получается импульс о величине знаменателя выражения (2), который идет на второй выход первого функционального блока 35, а на его первый выход импульс о величине показателя α1, с выхода четвертого задатчика 41. Для получения числителя выражения (2) импульсы с первого и второго входов блока 14 расчета корректировок первого вариванта поступают соответственно на первый и второй входы второго функционального блока 34 и третьего функционального блока 36. Во втором функциональном блоке 34 импульс с первого входа об оценке V1(i) умножается в первом блоке 45 умножения на импульс с четвертого входа блока 14 расчета корректировок первого варианта об оценке k1I(i-1) и подается на четвертый сумматор 47. Аналогично импульс со второго входа об оценке V2(i) умножается в третьем блоке 46 умножения на импульс с пятого входа блока 14 расчета корректировок первого варианта об оценке k2I(i-1) и подается на четвертый сумматор 47. Полученный выходной импульс второго функционального блока 34 о модельной оценке (i)

(i)  k

k

Импульс о величине Δk1I(i) с первого выхода блока 14 расчета корректировок первого варианта суммируется в первом сумматоре 15 с импульсом об оценке k1I(i-1) с первого блока 17 памяти и в результате получается

k1I(i) k1I(i-1) + Δk1I(i) (4) импульс о значении первого варианта первого коэффициента на i-м шаге. Этот импульс поступает на четвертый вход блока 14 расчета корректировок первого варианта и на вход первого блока 17 памяти, где осуществляется задержка импульса на шаг, равный 1. Аналогично определяется с помощью второго сумматора 16 и второго блока 18 памяти импульс об оценке k2I(i).

Для определения второго варианта адаптируемых коэффициентов импульсы с выходов второго 9 и третьего 9 блоков вычитания, а также с выходов первого 17 и второго 18 блоков памяти задерживаются соответственно в третьем 23 и четвертом 24, девятом 19 и десятом 20 блоках памяти на интервал времени, необходимый для срабатывания схемы получения первого варианта адаптируемых коэффициентов, и подаются на первый, второй, третий и четвертый входы блока 25 расчета корректировок первого варианта.

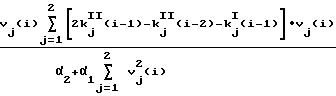

В блоке 25 расчета корректировок второго варианта реализуется процедура

δkjII(i) [2kjII(i-1) kjII(i-2) kjI(i-1)] ΔkjII(i), (5)

Δk

(6)

(6)

y (7) где δkjII(i) второй вариант корректировок j-го адаптируемого коэффициента на i-м шаге.

(7) где δkjII(i) второй вариант корректировок j-го адаптируемого коэффициента на i-м шаге.

Эта процедура позволяет адаптировать коэффициенты таким образом, чтобы выполнять требования на гладкость изменения самих значений коэффициентов.

Для реализации процедуры (5), (6) и (7) в состав блока 25 расчета корректировок второго варианта введены четвертый 60, пятый 61 и шестой 62 функциональные блоки, устройство и работа которых аналогичны устройству и работе первого 35, второго 34 и третьего 36 функциональных блоков и рассмотрены выше. Отличие состоит лишь в том, что на третий вход пятого функционального блока 61 поступает импульс о величине [2k1II(i-1) k1II(i-2) k1I(i-1)] для первого коэффициента, который формируется в седьмом блоке 56 вычитания. Аналогичный импульс для второго коэффициента формируется в восьмом блоке 57 вычитания и подается на четвертый вход пятого функционального блока 61. В результате на выходе пятого функционального блока 61 получается импульс о модельной оценке (i)

(i)

2k

2k vj(i) (8) который поступает на третий вход шестого функционального блока 62. Затем выходной импульс об оценке Δ k1II(i) для первого коэффициента с первого выхода шестого функционального блока 62 подается на первый вход пятого блока 58 вычитания, на второй вход которого приходит импульс о величине [2k1II(i-1) k1II(i-2) k1I(i-1)] с выхода седьмого блока 56 вычитания. Таким образом, в пятом блоке 58 вычитания реализуется процедура (5) и выходной импульс о втором варианте корректировки первого коэффициента δk1II(i) поступает на первый вход блока 25 расчета корректировок второго варианта. На второй выход блока 25 расчета корректировок второго варианта приходит импульс о величине δ k2II(i), который формируется аналогично первому коэффициенту в шестом блоке 59 вычитания.

vj(i) (8) который поступает на третий вход шестого функционального блока 62. Затем выходной импульс об оценке Δ k1II(i) для первого коэффициента с первого выхода шестого функционального блока 62 подается на первый вход пятого блока 58 вычитания, на второй вход которого приходит импульс о величине [2k1II(i-1) k1II(i-2) k1I(i-1)] с выхода седьмого блока 56 вычитания. Таким образом, в пятом блоке 58 вычитания реализуется процедура (5) и выходной импульс о втором варианте корректировки первого коэффициента δk1II(i) поступает на первый вход блока 25 расчета корректировок второго варианта. На второй выход блока 25 расчета корректировок второго варианта приходит импульс о величине δ k2II(i), который формируется аналогично первому коэффициенту в шестом блоке 59 вычитания.

Затем импульс о δk1II(i) с первого выхода блока 25 расчета корректировок второго варианта суммируется в пятом сумматоре 32 с импульсом о k1I(i) с выхода одиннадцатого блока 21 памяти, где он был задержан на время срабатывания схемы первого варианта. В итоге получается

k1II(i) k1I(i) + δ k1II(i) (9) импульс о значении второго варианта первого коэффициента на i-м шаге.

Этот импульс поступает на вход шестого блока 30 памяти, где задерживается на шаг, равный единице, затем в третьем масштабирующем блоке 28 умножается на 2 и поступает на пятый вход блока 25 расчета корректировок второго варианта. В пятом блоке 26 памяти импульс с выхода шестого блока 30 памяти задерживается еще на один такт, и в результате подучается импульс о k1II(i-2), который подается на седьмой вход блока 26 расчета корректировок второго варианта.

Аналогично в шестом сумматоре 33 формируется импульс о втором варианте второго адаптируемого коэффициента k2II(i) на i-м шаге. При этом импульс о k1II(i-2), поступающий на второй вход шестого сумматора 33, сначала задерживается в двенадцатом блоке 22 памяти на время, необходимое для срабатывания схемы первого варианта. Импульсы о 2k2II(i-1) и k2II(i-2), подаваемые соответственно на шестой и восьмой входы блока 25 расчета корректировок второго варианта, формируются аналогично импульсам первого коэффициента. Для этих целей используются четвертый масштабирующий блок 29, а также седьмой 31 и восьмой 27 блоки памяти.

Импульсы о первом варианте первого k1I(i) и второго k2I(i) адаптируемых коэффициентов поступают соответственно на третий и четвертый выходы многовариантного идентификатора, а импульсы о втором варианте первого k1II(i) и второго k2II(i) коэффициентов поступают соответственно на первый и второй выходы многовариантного идентификатора.

По аналогии может быть определено и большее число коэффициентов для большего числа вариантов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивной идентификации объекта | 1985 |

|

SU1305633A2 |

| Устройство для адаптивной идентификации объекта | 1983 |

|

SU1177794A1 |

| РЕГУЛЯТОР | 1990 |

|

RU2015520C1 |

| ТРЕНАЖЕР ОПЕРАТОРОВ СИСТЕМ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1990 |

|

RU2047909C1 |

| Адаптивный прогнозатор производственных показателей | 1989 |

|

SU1658175A1 |

| ТРЕНАЖЕР ОПЕРАТОРА СИСТЕМ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012065C1 |

| Устройство для коррекции массы кокса | 1987 |

|

SU1534057A1 |

| Адаптивный прогнозатор | 1982 |

|

SU1049866A1 |

| Устройство для коррекции массы кокса | 1987 |

|

SU1468917A1 |

| Управляемый сглаживающий фильтр | 1982 |

|

SU1061250A1 |

Изобретение относится к технике автоматического регулирования и управления, может быть использовано в системах автоматического управления объектами с переменными параметрами. Цель - повышение качества адаптируемых коэффициентов. Сущность изобретения: устройство содержит три датчика, три амплитудно-импульсных модулятора, три блока вычитания, три задатчика, блок расчета корректировок первого варианта, два сумматора, восемь блоков памяти, два блока расчета корректировок второго варианта, два масштабирующих блока. 6 ил.

МНОГОВАРИАНТНЫЙ ИДЕНТИФИКАТОР, содержащий объект управления, три задатчика, последовательно включенные первый амплитудно-импульсный модулятор, второй блок вычитания и третий блок памяти, последовательно включенные второй амплитудно-импульсный модулятор, третий блок вычитания и четвертый блок памяти, последовательно включенные третий амплитудно-импульсный модулятор и четвертый блок вычитания, первый и второй сумматоры, первый и второй блоки памяти, пятый и шестой сумматоры, пятый, шестой и седьмой блоки памяти, блок расчета корректировок первого варианта, включающий первый блок вычитания, и блок расчета корректировок второго варианта, причем блоки расчета корректировок первого и второго вариантов включают соответственно первый и четвертый функциональные блоки, каждый из которых состоит из двух квадраторов, третьего сумматора и четвертого задатчика, соответственно второй и пятый функциональные блоки, каждый из которых состоит из двух блоков умножения и четвертого сумматора, соответственно третий и шестой функциональные блоки, каждый из которых состоит из последовательно включенных второго блока умножения, первого блока деления, первого ограничителя и первого масштабирующего блока, последовательно включенных четвертого блока умножения, второго блока деления, второго ограничителя и второго масштабирующего блока, вторые входы второго, третьего и четвертого блоков вычитания подключены к выходам соответственно первого, второго и третьего задатчиков, а выходы к первому, второму и третьему входам блока расчета корректировок первого варианта, первый и второй выходы которого подключены к вторым входам соответственно первого и второго сумматоров, выход первого сумматора соединен с четвертым входом блока расчета корректировок первого варианта, выход второго сумматора соединен с пятым входом блока расчета корректировок первого варианта, входы первого и второго блоков памяти подключены к выходам соответственно первого и второго сумматоров, а выходы к первым входам соответственно первого и второго сумматоров, выходы третьего и четвертого блоков памяти соединены соответственно с первым и вторым входами блока расчета корректировок второго варианта, выходы пятого и шестого сумматоров подключены соответственно к первому и второму выходам устройства, первый вход блока расчета корректировок первого варианта соединен с первыми входами первого, второго и третьего функциональных блоков, второй вход с вторыми входами первого, второго и третьего функциональных блоков, третий вход с вторым входом первого блока вычитания, выход которого подключен к третьему входу третьего функционального блока, четвертый и пятый входы блока расчета корректировок первого варианта подключены соответственно к третьему и четвертому входам второго функционального блока, первый вход первого блока вычитания соединен с выходом второго функционального блока, четвертый вход третьего функционального блока соединен с вторым входом первого функционального блока, первый и второй выходы третьего функционального блока являются соответственно первым и вторым выходами блока расчета корректировок первого варианта, первый вход блока расчета корректировок второго варианта соединен с первыми входами четвертого, пятого и шестого функциональных блоков, второй вход с вторыми входами четвертого, пятого и шестого функциональных блоков, четвертый вход шестого функционального блока соединен с вторым выходом четвертого функционального блока, первый и второй входы первого и четвертого функциональных блоков через первый и второй квадраторы соединены соответственно с первым и вторым входами третьего сумматора, первый и второй входы второго и пятого функциональных блоков подключены к первым входам соответственно первого и третьего блоков умножения, выходы которых соединены соответственно с первым и вторым входами четвертого сумматора, выход которого является выходом второго и пятого функциональных блоков, вторые входы первого и третьего блоков умножения являются соответственно третьим и четвертым входами второго и пятого функциональных блоков, первый и второй входы третьего и шестого функциональных блоков подключены к первым входам соответственно второго и четвертого блоков умножения, вторые входы которых соединены с третьими входами третьего и шестого функциональных блоков, четвертые входы третьего и шестого функциональных блоков соединены с вторыми входами первого и второго блоков деления, выходы первого и второго масштабирующих блоков являются соответственно первым и вторым выходами третьего и шестого функциональных блоков, отличающийся тем, что в него введены три датчика, восьмой двенадцатый блоки памяти, третий и четвертый масштабирующие блоки, в блок расчета корректировок второго варианта введены пятый восьмой блоки вычитания, в первый и четвертый функциональные блоки пятый блок умножения, седьмой сумматор и пятый задатчик, входы девятого и десятого блоков памяти соединены с выходами соответственно первого и второго блоков памяти, а выходы соответственно с третьим и четвертым входами блока расчета корректировок второго варианта, первый и второй выходы которого подключены к первым входам соответственно пятого и шестого сумматоров, вторые входы пятого и шестого сумматоров соединены с выходами соответственно одиннадцатого и двенадцатого блоков памяти, входы которых подключены к выходам соответственно первого и второго сумматоров, выходы одиннадцатого и двенадцатого блоков памяти являются соответственно третьим и четвертым выходами идентификатора, выходы пятого и шестого сумматоров подключены к входам соответственно шестого и седьмого блоков памяти, входы пятого и восьмого блоков памяти соединены с выходами соответственно шестого и седьмого блоков памяти, а выходы соответственно с седьмым и восьмым входами блока расчета корректировок второго варианта, входы третьего и четвертого масштабирующих блоков подключены к выходам соответственно шестого и седьмого блоков памяти, а выходы соответственно к пятому и шестому входам блока расчета корректировок второго варианта, в котором третий, пятый и седьмой входы являются соответственно первым, вторым и третьим входами седьмого блока вычитания, выход которого подключен к третьему входу пятого функционального блока, четвертый, шестой и восьмой входы блока расчета корректировок второго варианта соединены соответственно с первым, вторым и третьим входами восьмого блока вычитания, выход которого подключен к четвертому входу пятого функционального блока, первые входы пятого и шестого блоков вычитания в блоке расчета корректировок второго варианта соединены соответственно с первым и вторым выходами шестого функционального блока, третий вход которого подключен к выходу пятого функционального блока, вторые входы пятого и шестого блоков вычитания соединены с выходами соответственно седьмого и восьмого блоков вычитания, а выходы пятого и шестого блоков вычитания являются соответственно первым и вторым выходами блока расчета корректировок второго варианта, пятый вход шестого функционального блока соединен с первым выходом четвертого функционального блока, пятый вход третьего функционального блока с первым выходом первого функционального блока, в первом и четвертом функциональных блоках первый вход пятого блока умножения соединен с выходом третьего сумматора, второй вход с выходом четвертого задатчика, а выход с первым входом седьмого сумматора, второй вход которого подключен к выходу пятого задатчика, а выход является вторым выходом первого и четвертого функциональных блоков, первый выход которых соединен с выходом четвертого задатчика, пятые входы третьего и шестого функциональных блоков подключены к вторым входам первого и второго масштабирующих блоков, первый и второй входы объекта управления подключены к входам соответственно первого и второго датчиков, а выход к входу третьего датчика, выходы первого, второго и третьего датчиков соединены с входами соответственно первого, второго и третьего амплитудно-импульсных модуляторов.

| Устройство для адаптивной идентификации объекта | 1983 |

|

SU1177794A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1995-06-27—Публикация

1991-06-27—Подача