чета корректировки, вторым входом десятого сумматора и первым входом шестого сумматора, выходы третьего, . четвертого и пятого блоков памяти подключены к первому, второму и третьему входам второго блока расчета корректировки, четвертый вход которого соединен с выходом восьмого сумматора, а пятый вход - с выходом десятого сумматора, первый вход седьмого сумматора подключен к первому выхрду второго блока расчета корректировки, второй вход - к выходу шестого блока памяти, а выход - к второму входу пятого сумматора, первый вход девятого сумматора подключен к второму выходу второго блока расчета корректировки, второй вход к выходу седьмого блока памяти, а выход - к второму входу шестого сумматора, выход пятого сумматора соединен с первым выходом устройства, выход шестого сумматора - -с вторым выходом устройства, первый вход блока расчета корректировки соединен с первыми входами первого и второго блоков умножения и через первый квадратор с первым входом третьего сумматора, второй вход блока расчета корректировки соединен с первыми входами третьего и четвертого блоков умножения и через второй квадратор с вторым входом третьего сумматора,третий вход которого подключен к выходу четвертого задатчика, а выход - к первым входам первого и второго блоков деления, третий вход блока расчета корректировки соединен с первым входом первого блока сравнения, четвертый вход через первый блок умножения подключен к первому входу четвертого суматора, пятый вход через третий блок умножения подключен к второму входу четвертого сумматора, выход которого через первый блок сравнения соединён с вторыми входами второго и четвертого блоков умножения, выход второго блока умножения соединен с вторым входом первого блока деления,выход четвертого блока умножения - с вторым входом второго блока деления, выход первого ограничителя через первый масштабирующий „ блок подключен к первому выходу блока расчета корректировют, выход второго ограничителя через второй масштабирующий блок подключен к второму выходу блока расчета корректировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивной идентификации объекта | 1985 |

|

SU1305633A2 |

| МНОГОВАРИАНТНЫЙ ИДЕНТИФИКАТОР | 1991 |

|

RU2038630C1 |

| Система автоматического регулирования | 1987 |

|

SU1483429A1 |

| Адаптивный прогнозатор | 1982 |

|

SU1049866A1 |

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| Интерполирующий фильтр | 1985 |

|

SU1241421A2 |

| Система автоматического регулирования | 1987 |

|

SU1476433A1 |

| Устройство для определения момента повалки конвертора | 1981 |

|

SU977503A1 |

| Устройство для коррекции массы кокса | 1987 |

|

SU1534057A1 |

| РЕГУЛЯТОР | 1990 |

|

RU2015520C1 |

УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ ИДЕНТИФИКАЦИИ ОБЪЕКТА, содержащее три амплитудно-импульсных модулятора первый и второй блоки памяти, первый второй и третий сумматоры, четыре блока умножения, два масштабирующих блока, объект управления, первый и второй входы которого связаны с входами соответственно первого и второго амплитудно-импульсных модуляторов, выход объекта управления подключен к входу третьего амплитудно-импульсного модулятора, вход первого блока памяти соединен с выходом первого сумматора, а выход - с первым входом первого сумматора, вход второго блока памяти соединен с выходом второго сумматора, а выход - с первым входом второго сумматора, о т л л и чающееся тем, что, с целью повьшения точности адаптации, в него введены три задатчика, пятый и шестой сумматоры, первый блок расчета корректировки, включающий в себя четвертый задатчик, -два квадратора, четвертый сумматор, блок срав- нения, последовательно включенные первый блок деления и первый ограничитель, последовательно включенные . второй блок деления и второй ограничитель, второй блок расчета корректировки, последовательно включенные второй блок сравнения и третий блок памяти, последовательно включенные третий блок сравнения и четвертый блок памяти, последовательно включенные четвертый блок сравнения и пятый tg блок памяти, последовательно вклю(Л ченные седьмой сумматор, шестой блок памяти и восьмой сумматор, последовательно включенные девятый сумматор, седьмой блок памяти и десятый сумматор, первые входы второго, третьего и четвертого блоков сравнения подключены к выходам соответст венно первого, второго и третьего ам.сг-х «Ч литудно-импульсных модуляторов, ВТО- Ч рые входы - к выходам соответственно ;о первого,второго и третьего задатчи4 ков, а выходы - к первому, второму и третьему входам первого блока рас-. чета корректировки, первый и BTopoft выходы которого подключены к вторым входам соответственно первого и второго сумматоров, выход первого сумматора соединен с четвертым входом первого блока расчета корректировки, вторым входом восьмого сумматора и первым входом пятого сумматора, выход второго сумматора соединен с пятым входом первого блока рас

Изобретение относится к автоматическому управлению и регулированию и может быть использовано в системах автоматического управления объектами с переменными параметрами.

Целью изобретения является повышение точности адаптации.

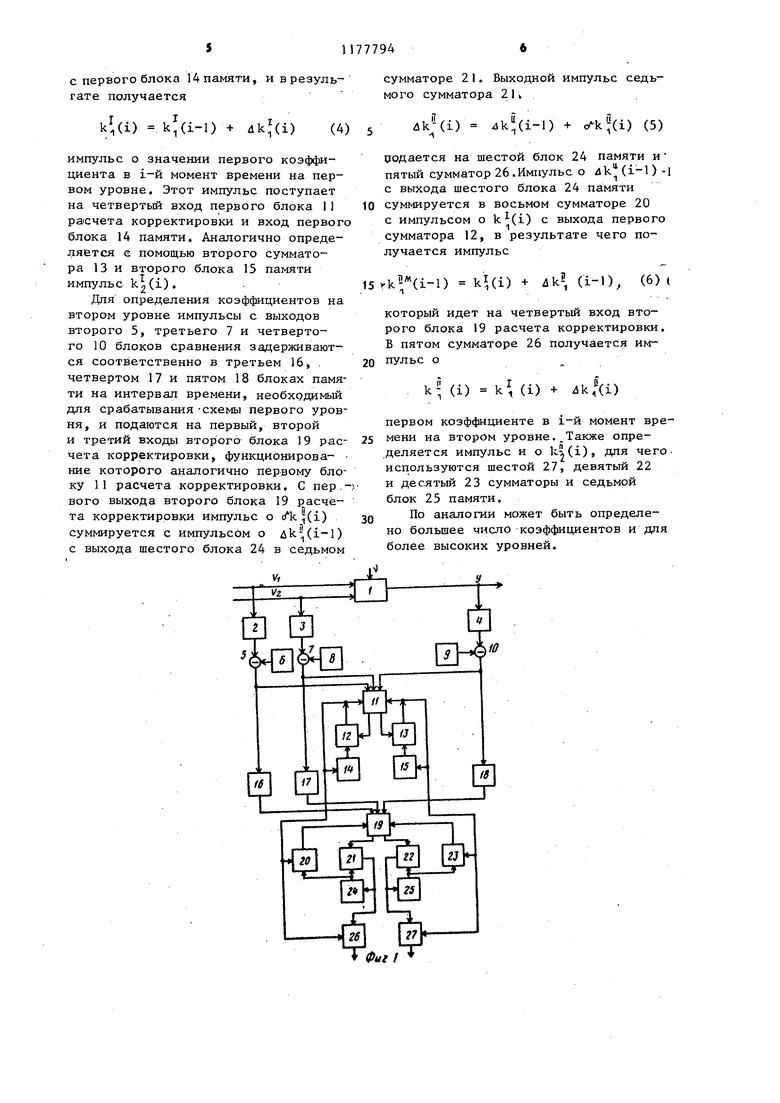

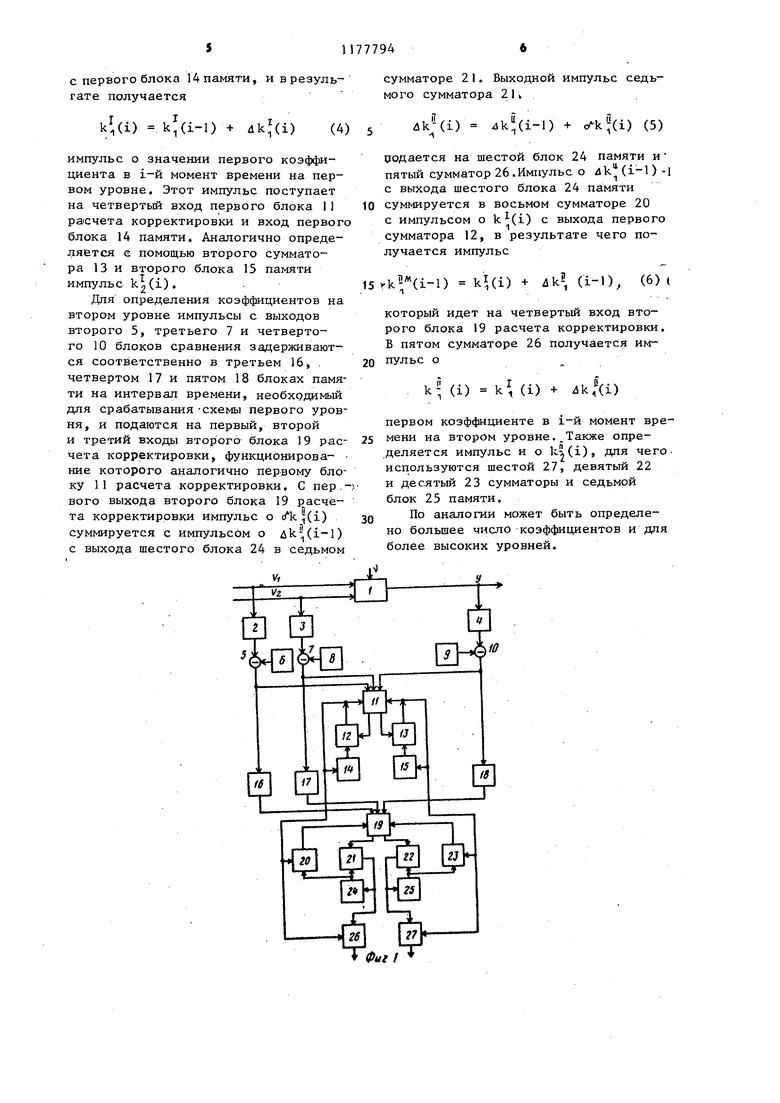

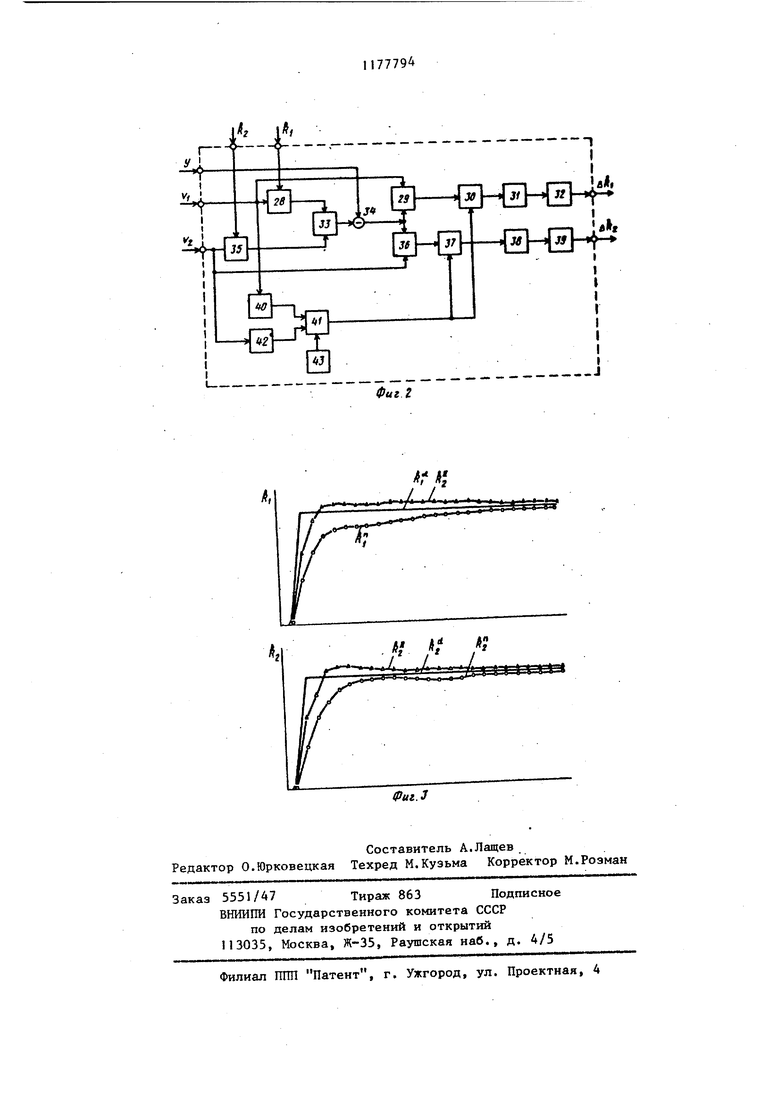

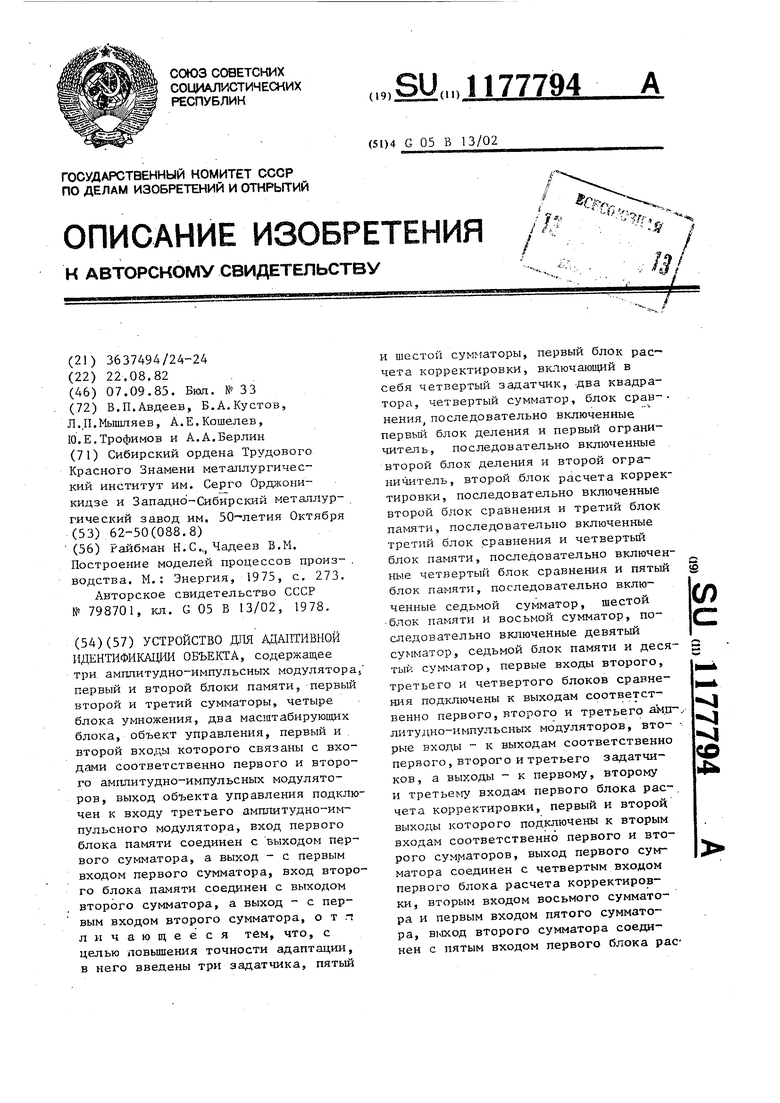

На фиг,1 приведена схема устройства для адаптивной идентификации объекта (V и V первая и вторая входные переменные объекта; Y - выходная переменная объекта; V - неконтролируемые возмущения, действующие на объект); на фиг,2 - схема блока расчета корректировки,(v, и Vj - приращение выходной переменной относительно среднего уровня; у приращение выходной переменной относительно среднего уровня; ky и k2 .чдаптируемые коэффициенты; 4k, д. 4k2 - корректировки коэффициентов ; па фиг.З - диаграммы, поясняюище работу устройства.

Устройство содержит объект I управления, первый 2, второй 3 и

третий 4 амплитудно-импульсные модуляторы, второй блок 5 сравнения, первый задатчик 6, третий блок 7 сравнения, второй задатчик 8, третий задатчик 9, четвертый блок 10

сравнения, первый блок 11 расчета корректировки , первый 12 и второй 13 сумматоры, первый 14, второй 15, третий 16, четвертый 17 и пятый 18 блоки памяти, второй блок 19 расчетакорректировки, восьмой 20, седьмой 21j девятый 22 и десятый 23 сумматоры, шестой 24 и седьмой 25 блоки памяти, пятый 26 и шестой 27 сумматоры, первый блок 28 умножения,

второй блок 29 умножения, первый блок 30 деления, первый ограничитель 31, первый масштабирующий блок 32, четвертый сумматор 33, первый блок 34 сравнения, третий блок 35 умножения, четвертый блок 36 умножения, второй блок 37 деления, второй ограничитель 38, второй масштабирую11Ц1й блок 39, первый квадратор 40, третий сумматор 41, второй квад ратор 42 и четвертый задатчик 43, Устройство работает следующим образом. Входные переменные: V и V поступают на объект 1, а также на пер вый 2 и второй 3 амплитудно-импульс ные модуляторы. Выходной сигнал Y о екта 1 подается на вход третьего ам литудно-импульсного модулятора 4, , Амплитудно-импульсные модуляторы ос ществляют дискретное преобразование аналоговых входных и выходного сигн ла объекта 1, в результате чего на их выходах получаются последовательн ти амплитудно-модулированныхимпульсову,(1), V(i) и Y(i), Вы содные импульсы амплитудно-импульсных модуляторов 2-4 поступаю на первые входы соответственно второго 5, третьего 7 и четвертого 10 блоков сравнения, где из них вычитаются импульсы о средних значениях V , V, и Y, поступающие с выходов соответственно первого 6, второго 8 и третьего 9 задатчиков. На выходах второго 5, третьего 7 и четвертого 10 блоков сравнения получаются импульсы V , V и у об отклонениях переменных от их средних значений. Импульсы о у, , Vj и у подаются на входы первого блока 11 расчета корректировки, который предназначен для вычисления корректировок адап тируемых коэффициентов Ц и k. В блоке 11 расчета корректировок реализуется процедура 4j(i) при ( J 1 .. т«х .(i) np.l., b(0-Z ;(.(,-) - - J J j d + vht) где uk ;(i) - корректировка j-ro коэф фициента на i-м шаге; 94 и d - постоянные коэффициенты, выбираемые в процессе НсШадки устройства, Для реализации процедуры (1 ) и (2) импульсы с первого и второго входов соответственно через первый 40 и второй 42 квадраторы идут на третий сумматор 41, на этот же сумматор пoдaetcя импульс о величине коэффициента d выражения (2) с выхода четвертого задатчика 43, Поступившие на третий сумматор 41 суммируются, и на выходе получается импульс о величине знаменателя, выражения (2). Для получения числителя выражения (2) импульс с первого входа о v(i) умножается в первом блоке 28 умножения на импульс с четвертого входа о k(i-l) и подается на четвертый сумматор 33, Аналогично импульс с второго входа о V2(i) умножается в третьем блоке 35 умножения на импульс с пятого входа о 2(1) и подается на четвертый сумматор 33, Выходной импульс четвертого сумматора 33 о модельной оценке 2 y(i) I k (i-l) v..(i) (3) J J вычитается в первом блоке 34 сравне-i ния из импульса о y(i) с третьего входа блока расчета корректировки. Во втором блоке 29 умножения импульс о V (i) умножается на импульс с выхода первого блока 34 сравнения, и в результате получается импульс-о числителе выражения (2 ) для первого коэффициента, .Этот импульс делится в первом блоке 30 делении на выходной импульс третьего сумматора 41 и поступает на первый ограничитель 31, где реализуется выражение (1), и затем умножается в первом масштабирующем блоке 32 на коэффициент f , На выходе первого масштабирующего блока получается импульс о величине dk (i) который идет на первый выход блока расчета корректировки. Таким же образом с помощью четвертого блока 36 умножения, второго блока 37 деления, второго ограничителя 38 и второго масштабирующего блока 39 рассчитывается импульс о величине dkjC) который идет на второй выход блока асчета корректировки, Импульс о 4k(i) с первого выода первого блока 11 расчета коректировки суммируется в первом суматоре 12 с импульсом о k. (i-l) с первого блока 14 памяти, и в результате получается ) kj(i-i) + dkjd) (4 импульс о значении первого коэффициента в i-й момент времени на первом уровне. Этот импульс поступает на четвертый вход первого блока 11 расчета корректировки и вход первог блока 14 памяти. Аналогично определяЁтся с помощью второго сумматора 13 и второго блока 15 памяти импульс k(i). . Для определения коэффициентов на втором уровне импульсы с выходов второго 5, третьего 7 и четвертого 10 блоков сравнения задерживаются соответственно в третьем 6, четвертом 17 и пятом 18 блоках памяти на интервал времени, необходимый для срабатывания-схемы первого уровня, и подаются на первый, второй и третий входы второго блока 19 расчета корректировки, функционирова- ние которого аналогично первому блоку 11 расчета корректировки. С пер.вого выхода второго блока 19 р асчета корректировки импульс о /k(i) суммируется с импульсом о Ak-(i-l) с выхода шестого блока 24 в седьмом

Фиг I сумматоре 21. Выходной импульс седьмого сумматора 21k 4k-(i) 4k(i-l) + (i) (5) л подается на шестой блок 24 памяти ипятый сумматор 26.Импульс о dk(i-l) -i с выхода шестого блока 24 памяти суммируется в восьмом сумматоре 20 с импульсом о k(i) с выхода первого сумматора 12, в результате чего получается импульс kf(i-l) ki(i) + 4k (i-1) (6) I который идет на четвертый вход второго блока 19 расчета корректировки. В пятом сумматоре 26 получается импульс о k (i) k, (i) -н 4kf(i) первом коэффициенте в i-й момент времени на втором уровне.Также определяется импульс и о k(i), для чего, используются шестой 27, девятый 22 и десятый 23 сумматоры и седьмой блок 25 памяти. По аналогии может быть определено большее число коэффициентов и для более высоких уровней.

г

| Райбман Н.С.,, Чадеев В.М | |||

| Построение моделей процессов произ- | |||

| водства | |||

| М.: Энергия, 1975, с | |||

| ТЕЛЕФОННЫЙ АППАРАТ, ОТЗЫВАЮЩИЙСЯ ТОЛЬКО НА ВХОДЯЩИЕ ТОКИ | 1920 |

|

SU273A1 |

| Адаптивное устройство для идентификацииОб'ЕКТА упРАВлЕНия | 1978 |

|

SU798701A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-09-07—Публикация

1983-08-22—Подача