Изобретение относится к автоматическому управлению и регулированию и может быть использовано для построения систем управления объектами с большими запаздываниями, подверженными влиянию неконтролируемых параметрических возмущений. Динамика каналов регулирования объекта аппроксимируется оператором:

Y(P) =

, где ki - коэффициенты усиления; Тi - постоянные времени; τi - транспортные запаздывания. Объект имеет N управляющих входов и один выход. Каналы запаздывания характеризуются незначительными изменениями τi, Ti и существенными изменениями ki. Причем τ1< τ2<...< τN и τi>Тп.п.i, где Tп.п.i - интервал эффективной памяти i-го канала регулирования, Тп.п.i= 3-4Ti.

, где ki - коэффициенты усиления; Тi - постоянные времени; τi - транспортные запаздывания. Объект имеет N управляющих входов и один выход. Каналы запаздывания характеризуются незначительными изменениями τi, Ti и существенными изменениями ki. Причем τ1< τ2<...< τN и τi>Тп.п.i, где Tп.п.i - интервал эффективной памяти i-го канала регулирования, Тп.п.i= 3-4Ti.

Примером описанного класса объектов может служить увлажнение агломерационной шихты, при этом выходной переменной может быть влажность агломерационной шихты, регулирующими воздействиями - расходы воды в барабане-смесителе и в барабане-окомкователе.

Известна система автоматического регулирования [1], содержащая исполнительный орган, объект управления, блок формирования траектории управлений, состоящий из широтно-импульсного модулятора, первого масштабирующего блока, второго запоминающего блока сравнения, первого интегратора, первого компаратора и первого задатчика, второй и первый датчики, блок расчета текущих управлений, состоящий из первого блока задержки, второго блока сравнения, блока умножения, первого блока сравнения и первого запоминающего блока, блок адаптации, состоящий из четвертого запоминающего блока, второго блока задержки, первого фильтра низкой частоты, сумматора, второго фильтра низкой частоты, четвертого блока сравнения, пятого запоминающего блока, второго масштабирующего блока, третьего запоминающего блока, третьего блока задержки, первого блока определения модуля, второго задатчика, седьмого, шестого и пятого блоков сравнения, первого ключа, второго и третьего компараторов, второго блока определения модуля, четвертого блока задержки, третьего интегратора, блока деления, второго интегратора, третьего задатчика и второго ключа.

Недостатком известной системы автоматического регулирования является невозможность использования ее для регулирования объектами с N регулирующими каналами.

Наиболее близким по технической сущности и достигаемому результату к заявляемому устройству является регулятор [2], содержащий первый блок задержки, первое и второе форсирующие звенья, последовательно включенные первый блок сравнения, фильтр низкой частоты, обратную модель третьего канала регулирования без запаздывания, сумматор, первый экстраполятор, первый масштабирующий блок, второй блок задержки и третий блок задержки, последовательно включенные второй, экстраполятор, второй блок сравнения, второй масштабирующий блок и четвертый блок задержки, последовательно включенные третий экстраполятор и блок вычитания, причем выход сумматора соединен с входами второго и третьего экстраполяторов, выход второго блока задержки - с вторым входом второго блока сравнения, первый и второй входы регулятора подключены к первому и второму входам первого блока сравнения, выходы третьего и четвертого блоков задержки соединены с вторым и третьим входами блока вычитания, выход первого масштабирующего блока соединен с первым выходом регулятора, вход первого форсирующего звена соединен с выходом второго масштабирующего блока, а выход - с вторым выходом регулятора, выход второго реального форсирующего звена соединен с выходом блока вычитания, а выход - с третьим выходом регулятора, выход третьего экстраполятора подключен через первый блок задержки к второму входу сумматора. Регулирующие воздействия в масштабе регулирующего воздействия по третьему каналу регулирования формируются на основе восстановленного эквивалентного образцового управления путем его экстраполяции и вычитания регулирующих воздействий по каналам с большим запаздыванием. Затем полученные значения регулирующих воздействий по второму и первому каналам регулирования пересчитываются в соответствующийа масштаб с учетом различия динамики соответственно между вторым и третьим каналами регулирования, а также первым и третьим каналами регулирования соответственно в первом и втором реальных форсирующих звеньях.

Недостатками известного регулятора являются низкая точность при изменении коэффициентов усиления по каналам регулирования и, как следствие, ошибки восстановления образцового эквивалентного управления и пересчета регулирующих воздействий в соответствующие масштабы с использованием прямых и обратных моделей каналов регулирования.

Цель изобретения - повышение точности регулирования.

Цель достигается тем, что в регулятор, содержащий первый блок задержки, последовательно соединенные первый блок сравнения и первое реальное форсирующее звено, последовательно соединенные первый сумматор, первый экстраполятор, первый масштабирующий блок и второй блок задержки, последовательно соединенные второй экстраполятор, второй блок сравнения, второе реальное форсирующее звено и первый блок умножения, причем выход второго экстраполятора соединен с входом первого блока задержки, выход которого соединен с первым входом первого сумматора, выход которого соединен с входом второго экстраполятора, выход второго блока задержки соединен с вторым входом второго блока сравнения, первый и второй входы первого блока сравнения соединены соответственно с первым и вторым входами регулятора, выход первого масштабирующего блока и выход первого блока умножения соединены соответственно с первым и вторым выходами регулятора, введены первый блок деления и устройства формирования сигнала на идентификацию каналов регулирования, интегрирования переменных регулирования и расчета коэффициентов передачи моделей каналов регулирования, входы которого соединены с соответствующими выходами устройства интегрирования переменных регулирования, первый выход соединен с первым входом устройства интегрирования переменных регулирования, второй выход - с вторым входом первого блока умножения, третий выход - с вторым входом первого блока деления, второй вход которого соединен с выходом первого реального форсирующего звена, выход - с вторым входом первого сумматора, при этом первый вход, второй и первый выходы регулятора соединены соответственно с вторым, третьим и четвертым входами устройства интегрирования переменных регулирования, пятый вход которого соединен с выходом устройства формирования сигнала на идентификацию каналов регулирования, первый и второй входы которого соединены соответственно с выходом первого блока сравнения и вторым входом регулятора, причем блок формирования сигнала на идентификацию каналов регулирования содержит первый и второй задатчики, последовательно соединенные третий блок задержки, третий блок сравнения, второй масштабирующий блок определения модуля, первый компаратор и элемент И, последовательно соединенные блок определения знака, первый фильтр низкой частоты, второй блок определения модуля и второй компаратор, вход третьего элемента задержки и второй вход третьего блока сравнения соединены с вторым входом устройства формирования сигнала на идентификацию каналов регулирования, первым входом которого является вход блока определения знака, а выходом - выход элемента И, второй вход которого соединен с выходом второго компаратора, второй вход которого и второй вход первого компаратора соединены с соответствующими задатчиками, устройство интегрирования переменных регулирования содержит четвертый, пятый, шестой и седьмой блоки задержки, первый, второй и третий элементы НЕ, источник постоянного сигнала, последовательно соединенные второй фильтр низкой частоты, первый запоминающий блок, четвертый блок сравнения, первый интегратор, второй запоминающий блок и первый ключ, последовательно соединенные восьмой блок задержки, пятый блок сравнения, второй блок умножения, второй интегратор, шестой блок сравнения, третий интегратор, второй ключ и седьмой блок сравнения, последовательно соединенные третий фильтр низкой частоты, третий запоминающий блок, восьмой блок сравнения, четвертый интегратор, четвертый запоминающий блок и третий ключ, последовательно соединенные четвертый фильтр низкой частоты, пятый запоминающий блок, девятый блок сравнения, пятый интегратор, четвертый ключ, шестой запоминающий блок, десятый блок сравнения и пятый ключ, вход четвертого блока задержки, второй вход первого запоминающего блока, первый управляющий вход задания начальных условий первого интегратора, вход первого элемента НЕ, вход блока задержки, первый управляющий вход задания начальных условий четвертого интегратора, управляющий вход третьего запоминающего блока и вход шестого блока задержки объединены и подключены к пятому входу устройства интегрирования переменных регулирования, выход четвертого блока задержки соединен с управляющими входами второго и четвертого блоков запоминания, выход источника постоянного сигнала соединен с вторыми информационными входами первого, третьего, четвертого и пятого интеграторов, выход первого элемента НЕ соединен с вторыми управляющими входами задания начальных условий первого и четвертого интеграторов, выход пятого блока задержки соединен с первыми управляющими входами задания начальный условий третьего интегратора, седьмого блока задержки, шестого запоминающего блока, управляющими входами первого и четвертого ключей, второго элемента НЕ и первым управляющим входом второго интегратора с заданием начальных условий, выход второго интегратора соединен с вторым входом пятого блока сравнения, выход пятого блока запоминания соединен с вторым входом шестого блока сравнения, выход пятого ключа соединен с вторым входом седьмого блока сравнения, выход второго элемента НЕ соединен с вторыми управляющими входами задания начальных условий второго, третьего и четвертого интеграторов, выход седьмого блока задержки соединен с управляющими входами второго и пятого ключей, выход шестого блока задержки соединен с входом третьего элемента НЕ, вторым входом пятого запоминающего блока и первым управляющим входом задания начальных условий пятого интегратора, второй управляющий вход задания начальных условий которого соединен с выходом третьего элемента НЕ, выход пятого интегратора соединен с вторым выходом десятого блока сравнения, выход первого ключа является первым выходом устройства интегрирования переменных регулирования, вторым выходом которого является выход седьмого блока сравнения, третьим выходом - выход третьего ключа, четвертым выходом - выход седьмого блока задержки, соединенного с управляющим входом третьего ключа, пятым выходом - выход пятого блока задержки, шестым выходом - выход четвертого ключа, вход четвертого фильтра низкой частоты, второй вход девятого блока сравнения и второй информационный вход второго интегратора объединены и являются вторым входом устройства интегрирования переменных регулирования, четвертым входом которого являются объединенные входы второго фильтра низкой частоты, второй вход четвертого блока сравнения и вход восьмого блока задержки, третьим входом - объединенные вход третьего фильтра низкой частоты и второй вход восьмого блока сравнения, первым входом является второй вход второго блока умножения, устройство расчета коэффициентов передачи моделей каналов регулирования содержит девятый и десятый блоки задержки, последовательно соединенные второй блок деления, одиннадцатый блок сравнения, третий масштабирующий блок, второй сумматор, седьмой запоминающий блок и одиннадцатый блок задержки, последовательно соединенные третий блок деления, двенадцатый блок сравнения, четвертый масштабирующий блок, третий сумматор, восьмой запоминающий блок, четвертый блок деления и девятый блок запоминания, выход которого является вторым выходом устройства расчета коэффициентов передачи моделей каналов регулирования, третьим выходом которого является выход седьмого блока запоминания, первым - выход восьмого блока запоминания, первым входом - первый вход третьего блока деления, второй вход которого является шестым входом, вторым входом - первый вход второго блока деления, второй вход которого является третьим входом устройства расчета коэффициентов передачи моделей каналов регулирования, четвертым входом которого является вход десятого блока задержки, выход которого соединен с управляющими входами девятого блока запоминания и седьмого блока запоминания, выход которого соединен с вторым входом второго сумматора и вычитающим входом одиннадцатого блока сравнения, выход восьмого блока запоминания соединен с вторым входом третьего сумматора и вычитающим входом двенадцатого блока сравнения, а управляющий вход соединен с выходом девятого блока задержки, вход которого является пятым входом устройства расчета коэффициентов передачи моделей каналов регулирования, первый, второй, третий, четвертый, пятый и шестой выходы устройства интегрирователя переменных регулирования соединены соответственно с первым, вторым, третьим, четвертым, пятым и шестым входами устройства расчета коэффициентов моделей канала регулирования.

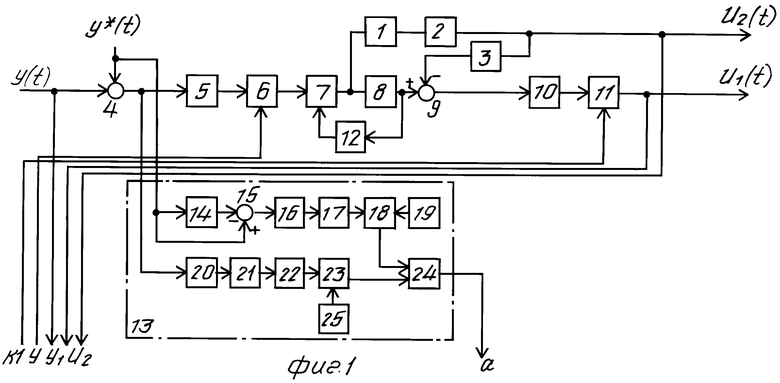

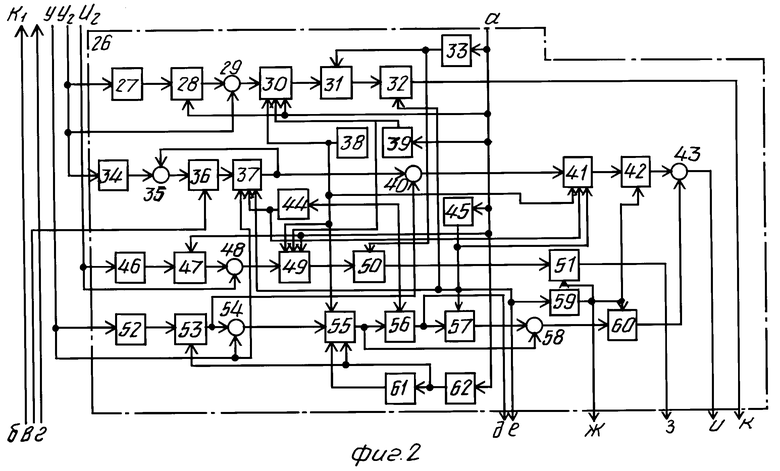

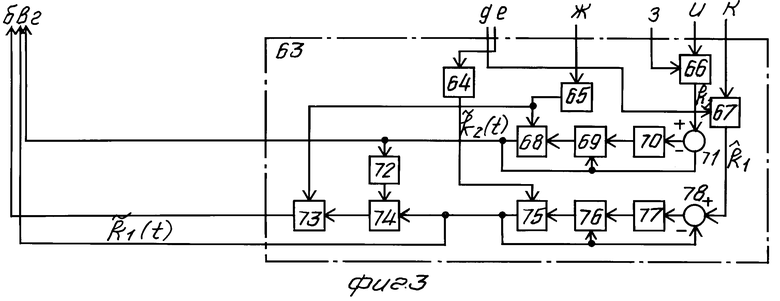

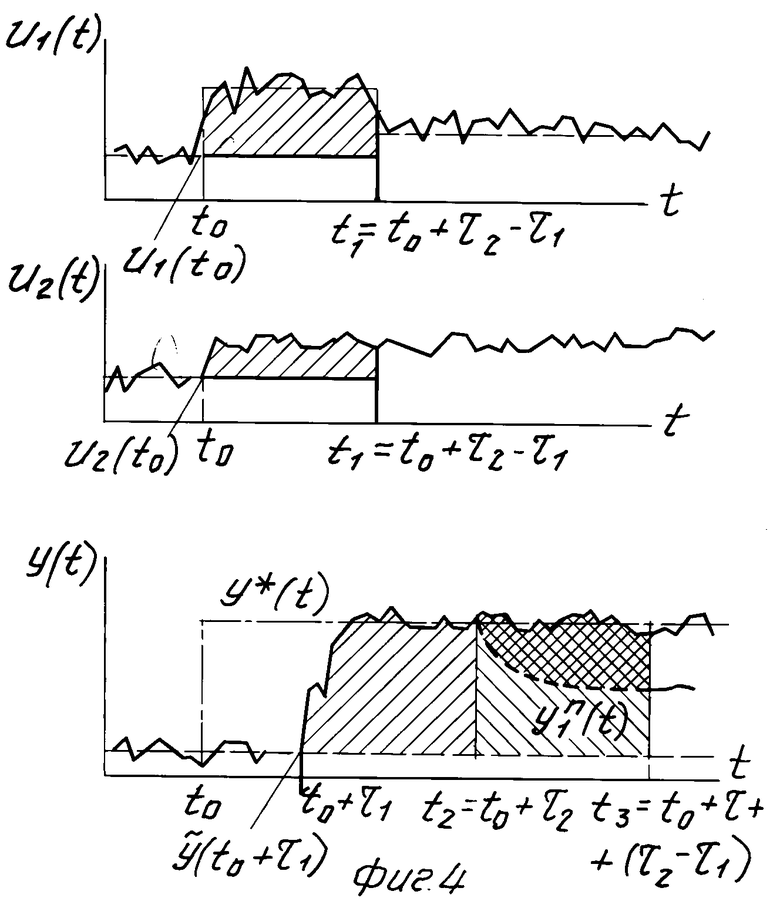

На фиг. 1, 2, 3 изображена структурная схема предлагаемого регулятора; на фиг.4 - динамика входных и выходных переменных в процессе идентификации каналов регулирования.

Регулятор содержит первый экстраполятор 1, первый масштабирующий блок 2, второй блок 3 задержки, первый блок 4 сравнения, первое реальное форсирующее звено 5, первый блок 6 деления, первый сумматор 7, второй экстраполятор 8, второй блок 9 сравнения, второе реальное форсирующее звено 10, первый блок 11 умножения, первый блок 12 задержки, устройство 13 формирования сигнала на идентификацию каналов регулирования, содержащий третий блок 14 задержки, третий блок 15 сравнения, второй масштабирующий блок 16, первый блок 17 определения модуля, первый компаратор 18, первый задатчик 19, блок 20 определения знака, первый фильтр 21 низкой частоты, второй блок 22 определения модуля, второй компаратор 23, элемент И 24, второй задатчик 25, устройство 26 интегрирования переменных регулирования, содержащий второй фильтр 27 низкой частоты, первый блок 28 запоминания, четвертый блок 29 сравнения, первый интегратор 30 с заданием начальных условий, второй блок 31 запоминания, первый ключ 32, четвертый блок 33 задержки, восьмой блок 34 задержки, пятый блок 35 сравнения, второй блок 36 умножения, второй интегратор 37 с заданием начальных условий, источник 38 постоянного сигнала, первый элемент НЕ 39, шестой блок 40 сравнения, третий интегратор 41 с заданием начальных условий, второй ключ 42, седьмой блок 43 сравнения, второй элемент НЕ 44, пятый блок 45 задержки, третий фильтр 46 низкой частоты, третий блок 47 запоминания, восьмой блок 48 сравнения, четвертый интегратор 49 с заданием начальных условий, четвертый блок 50 запоминания, третий ключ 51, четвертый фильтр 52 низкой частоты, пятый блок 53 запоминания, девятый блок 54 сравнения, пятый интегратор 55 с заданием начальных условий, четвертый ключ 56, шестой блок 57 запоминания, десятый блок 58 сравнения, седьмой блок 59 задержки, пятый ключ 60, третий элемент НЕ 61 и шестой блок 62 задержки, устройство 63 расчета коэффициента передачи моделей каналов регулирования, содержащий девятый блок 64 задержки, десятый блок 65 задержки, второй блок 66 деления, третий блок 67 деления, седьмой блок 68 запоминания, первый сумматор 69, третий масштабирующий блок 70, одиннадцатый блок 71 сравнения, одиннадцатый блок 72 задержки, девятый блок 73 запоминания, четвертый блок 74 деления, восьмой блок 75 запоминания, второй сумматор 76, четвертый масштабирующий блок 77, двенадцатый блок 78 сравнения.

На фигурах приняты следующие обозначения: Y(t), Y*(t) - фактическое и заданное значения регулируемой переменной,  (t),

(t),  (t) - оценки значений коэффициентов передачи моделей каналов регулирования,

(t) - оценки значений коэффициентов передачи моделей каналов регулирования,  (t),

(t),  (t) - сглаженные значения коэффициентов передачи моделей каналов регулирования, U1(t), U2(t) - регулирующие воздействия по первому и второму каналам регулирования, τ1, τ2 - запаздывания в моделях первого и второго каналов регулирования, U1(to), U2(to) - значения первого и второго управляющих воздействий в момент to изменения задания Y*(t), Y(to+ τ1) - значение выходной переменной в момент времени to+ τ1, t - текущее время.

(t) - сглаженные значения коэффициентов передачи моделей каналов регулирования, U1(t), U2(t) - регулирующие воздействия по первому и второму каналам регулирования, τ1, τ2 - запаздывания в моделях первого и второго каналов регулирования, U1(to), U2(to) - значения первого и второго управляющих воздействий в момент to изменения задания Y*(t), Y(to+ τ1) - значение выходной переменной в момент времени to+ τ1, t - текущее время.

Регулятор работает следующим образом.

Сигналы с входов регулятора о фактическом Y(t) и заданном Y*(t) значениях регулируемой переменной поступают на входы первого блока 4 сравнения, на выходе которого формируется сигнал об ошибке регулирования ε (t). Полученный сигнал ε (t) с выхода первого блока 4 сравнения поступает на обратную модель второго канала регулирования, реализованную в виде последовательно соединенных первого реального форсирующего звена 5 и первого блока 6 деления. С выхода первого блока деления сигнал об ошибке регулирования в масштабе второго управляющего входа подается на первый вход первого сумматора 7, где суммируется с сигналом об экстраполированном значении эквивалентного управляющего воздействия, задержанном в блоке 12 задержки на время τ2 запаздывания в первом канале регулирования. На выходе первого сумматора 7 получается сигнал об образцовом эквивалентном управлении Uτb в масштабе второго регулирующего воздействия. Сигнал Uτb экстраполируется в первом экестраполяторе 1 на время запаздывания во втором канале регулирования. Для расчета регулирующего воздействия по второму каналу регулирования сигнал с выхода первого экстраполятора 1 умножается в первом масштабирующем блоке 2 на коэффициент α2, определяющий долю второго регулирующего воздействия. На выходе первого масштабирующего блока 2 получается сигнал о втором регулирующем воздействии U2(t).

Для расчета первого регулирующего воздействия сигнал об образцовом эквивалентном управлении экстраполируется во втором экстраполяторе 8 на время запаздывания в первом канале регулирования τ1. Из сигнала об экстраполированном значении управления вычитается во втором блоке 9 сравнения сигнал о значении второго регулирующего воздействия, задержанного во втором блоке 3 задержки на время τ2- τ1. С выхода второго блока 9 сравнения сигнал о первом регулирующем воздействии пересчитывается в масштаб первого канала регулирования, для чего сигнал подается на вход второго реального форсирующего звена 10 и далее на первый блок 11 умножения. Таким образом реализуется звено с передаточной функцией

G(P) = k·  ; k = k2/k1, представляющей собой произведение передаточных функций прямой модели второго канала регулирования и обратной модели первого канала регулирования.

; k = k2/k1, представляющей собой произведение передаточных функций прямой модели второго канала регулирования и обратной модели первого канала регулирования.

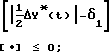

Сигнал So на уточнение коэффициентов k1, k2 формируется в устройстве 13 формирования сигнала на идентификацию каналов регулирования. Динамика работы устройства 13 формирования сигнала So на идентификацию каналов регулирования описывается следующими выражениями:

So(t)=S1(t)  S2(t); (1)

S2(t); (1)

S1(t) =

(2)

(2)

Δ Y*(t)=Y*(t)-Y*(t-Δt);

S2(t) =

>0; (3)

>0; (3)

σ (t)=sign ε (t); ε (t)=Y*(t)-Y(t), где δ1 и δ2 - заданные значения;  (t) - сглаженное значение знаковой функции σ (t).

(t) - сглаженное значение знаковой функции σ (t).

Выражение (2) определяет условие (S1(t)=1) минимально необходимого для проведения идентификации изменения величины заданного значения регулируемой переменной. Выражение (3) определяет условие стабильности процесса регулирования (S2=1).

Для реализации выражения (2) сигнал о заданном значении регулируемой переменной с второго входа первого блока 4 сравнения поступает на второй вход устройства 13 формирования сигнала на идентификацию каналов регулирования, соединенного с входом третьего блока 14 задержки, где задерживается на время Δt, определяемое как время, необходимое для срабатывания ключей и блоков запоминания. С выхода третьего блока 14 задержки сигнал Y*(t- Δ t) поступает на первый вход третьего блока 15 сравнения, где сравнивается с сигналом о текущем значении Y*(t). Сигнал Δ Y*(t)=Y*(t)-Y*(t- Δt) с выхода третьего блока 15 сравнения умножается на коэффициент 1/2 во втором масштабирующем блоке 16. Далее сигнал с выхода второго масштабирующего блока 16 поступает на вход первого блока 17 определения модуля. На выходе первого блока определения модуля формируется сигнал  ΔY*(t)

ΔY*(t) , который поступает на первый вход первого компаратора 18. На второй вход первого компаратора поступает сигнал о минимально требуемой величине δ1изменения заданного значения регулируемой переменной с выхода первого задатчика 19. На выходе первого компаратора 18 формируется сигнал S1=1, если

, который поступает на первый вход первого компаратора 18. На второй вход первого компаратора поступает сигнал о минимально требуемой величине δ1изменения заданного значения регулируемой переменной с выхода первого задатчика 19. На выходе первого компаратора 18 формируется сигнал S1=1, если  ΔY*(t)

ΔY*(t) > δ1, и S1=0, если

> δ1, и S1=0, если  ΔY*(t)

ΔY*(t) ≅ δ1, который поступает на первый вход элемента И 24.

≅ δ1, который поступает на первый вход элемента И 24.

Для реализации выражения (3) сигнал об ошибке регулирования ε (t) c выхода первого блока 4 сравнения поступает на первый вход устройства 13 формирования сигнала на идентификацию каналов регулирования, соединенный с входом блока 20 определения знака. На выходе блока определения знака формируется сигнал σ (t), представляющий собой знаковую функцию σ (t)=sign ε (t), который поступает на вход фильтра 21 низкой частоты, где сглаживается. Таким образом, на выходе фильтра 21 низкой частоты формируется сигнал σ (t), представляющий аналог автокорреляционной функции.

При стабильном процессе регулирования отклонения Y(t) от Y*(t) будут как положительные, так и отрицательные и, следовательно, знаки ошибок регулирования чередуются. Сглаженное значение  (t) стремится к нулю.

(t) стремится к нулю.

Появление существенных возмущений ведет на интервале переходного процесса к постоянному (в смысле знака отклонения) смещению регулируемой переменной относительно ее заданного значения. Функция  (t) в этом случае стремится к +1 или -1, что и характеризует нестабильность процесса регулирования.

(t) в этом случае стремится к +1 или -1, что и характеризует нестабильность процесса регулирования.

Пороговое значение функции  (t) по модулю, по достижении которого процесс регулирования считается нестабильным, задается вторым задатчиком 25, сигнал которого поступает на второй вход второго компаратора 23. На первый вход второго компаратора поступает сигнал об абсолютном значении

(t) по модулю, по достижении которого процесс регулирования считается нестабильным, задается вторым задатчиком 25, сигнал которого поступает на второй вход второго компаратора 23. На первый вход второго компаратора поступает сигнал об абсолютном значении  (t) с выхода второго блока 22 определения модуля.

(t) с выхода второго блока 22 определения модуля.

На выходе второго компаратора 23 формируется сигнал S2=1, если δ2>  (t)

(t) , и S2=0, если δ2≅

, и S2=0, если δ2≅  (t)

(t) , который поступает на второй вход элемента И 24. На выход элемента И 24 формируется сигнал So=1 или So=0 в зависимости от конкретных условий в соответствии с выражением (1).

, который поступает на второй вход элемента И 24. На выход элемента И 24 формируется сигнал So=1 или So=0 в зависимости от конкретных условий в соответствии с выражением (1).

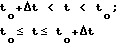

Сигнал So на выходе элемента И 24 при выполнении условий минимально необходимого изменения величины заданного значения регулируемой переменной и стабильности процесса регулирования в некоторый момент времени to имеет вид импульса с единичной амплитудой и длительностью Δt:

So=

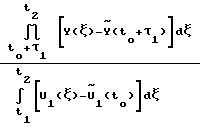

Расчет коэффициентов передачи каналов регулирования  (t),

(t),  (t) в устройстве 63 расчета коэффициентов передачи каналов регулирования выполняется по выражениям

(t) в устройстве 63 расчета коэффициентов передачи каналов регулирования выполняется по выражениям (t) =

(t) =

; (4)

; (4) (t) =

(t) =  ; (5)

; (5)

t1= to+ τ2- τ1; t2=to+ τ2; t3=t2+ τ2- τ1, где Y(ζ) - значение регулируемой переменной; U1(ζ ), U2(ζo) - текущие значения первого и второго регулирующих воздействий;  (to),

(to),  (to) - сглаженные значения первого и второго регулирующих воздействий в момент времени to;

(to) - сглаженные значения первого и второго регулирующих воздействий в момент времени to;  (to+ τ1) - сглаженное значение регулируемой переменной в момент времени to+ τ1; Yм1( ζ) - текущее модельное значение выходной переменной первого канала регулирования; ζ - переменная интегрирования.

(to+ τ1) - сглаженное значение регулируемой переменной в момент времени to+ τ1; Yм1( ζ) - текущее модельное значение выходной переменной первого канала регулирования; ζ - переменная интегрирования.

Интегрирование U1(t), U2(t) и Y(t) на соответствующих интервалах времени осуществляется в устройстве 26 интегрирования переменных регулирования.

Интегрирование изменений регулирующих воздействий U1(t) и U2(t) на интервале [to; to+ τ2- τ1] выполняется следующим образом.

Сигналы о регулирующих воздействиях U1(t), U2(t) и сигнал о регулируемой переменной Y(t) поступают соответственно на четвертый, третий и второй входы устройства 26 интегрирования переменных регулирования, соединенные с входами второго 27, третьего 46 и четвертого 52 фильтров низкой частоты. На выходе фильтров низкой частоты формируется соответственно текущие сглаженные значения  (t),

(t),  (t),

(t),  (t).

(t).

В момент времени to по сигналу So=1, поступающему на пятый вход устройства 26 интегрирования переменных регулирования, соединенного с управляющими входами первого 28 и третьего 47 блоков запоминания, с выхода элемента И 24 сигналы с выходов второго 27 и третьего 46 фильтров низкой частоты о сглаженных значениях  (to) и

(to) и  (to), поступающие на входы первого 28 и третьего 47 блоков запоминания, запоминаются в этих блоках.

(to), поступающие на входы первого 28 и третьего 47 блоков запоминания, запоминаются в этих блоках.

В этот же момент времени to по сигналам, поступающим на первые и вторые управляющие входы первого 30 и четвертого 49 интеграторов с заданием начальных условий соответственно с выхода элемента И 24 So=1 и первого элемента НЕ So=0, интеграторы переводятся в режим задания нулевых начальных условий. Сигнал о величине начальных условий поступает с выхода источника 38 постоянного сигнала на вторые информационные входы первого 30 и четвертого 49 интеграторов с заданием начальных условий.

В момент времени to+ Δ t первый 30 и четвертый 49 интеграторы с заданием начальных условий сигналами с выходов элемента И So(to+Δ t)=0 и первого элемента НЕ So(to+ Δ t)=1 переводятся в режим интегрирования сигналов с выходов соответственно четвертого 29 и восьмого 48 блоков сравнения. Сигнал с выхода четвертого 29 блока сравнения представляет собой разницу между сигналами с выходов первого блока 28 запоминания и первого блока 11 умножения, сигнал с выхода восьмого блока 48 сравнения получается как разница сигналов с выходов третьего блока 47 запоминания и первого масштабирующего блока 2.

В момент времени to+ τ2- τ1 по сигналу So, задержанному в четвертом блоке 33 задержки на время τ2- τ1, выходные сигналы первого 30 и четвертого 49 интеграторов с заданием начальных условий запоминаются во втором 31 и четвертом 50 блоках запоминания.

Интегрирование изменения регулируемой переменной Y(t) выполняется следующим образом.

По сигналу So=τ1 с выхода элемента И 24, задержанному в шестом блоке 62 задержки на время τ1, в пятом блоке 53 запоминания запоминается сигнал с выхода четвертого фильтра 52 низкой частоты о величине  (to+ τ1).

(to+ τ1).

В то же время сигналы So(to+ τ1)=1 с выхода шестого блока 62 задержки и So(τo+ τ1)= 0 переводят пятый интегратор 55 с заданием начальных условий в режим задания нулевых начальных условий. Сигнал о величине начального условия поступает на второй информационный выход пятого интегратора 55 с заданием начальных условий с выхода источника 38 постоянного сигнала.

Изменение сигналов So(t+ τ1+ Δt) и So(to+ τ1+ Δt) с момента времени to+ τ1+ Δt переводит пятый интегратор 55 в режим интегрирования сигнала о разнице между Y(t) и  (to+ τ1) с выхода девятого блока 54 сравнения, на первый и второй входы которого соответственно поступают сигналы с выхода четвертого фильтра 52 низкой частоты и первого входа первого блока 4 сравнения.

(to+ τ1) с выхода девятого блока 54 сравнения, на первый и второй входы которого соответственно поступают сигналы с выхода четвертого фильтра 52 низкой частоты и первого входа первого блока 4 сравнения.

В момент времени to+ τ2 по сигналу So=1 с выхода пятого блока 45 задержки, поступающему на управляющие входы первого 32 и четвертого 56 ключей, сигналы с выхода первого ключа 32 о величине интеграла [U1(ζ)-

[U1(ζ)- (to)]dζ (6) и с выхода четвертого ключа 56 о величине интеграла

(to)]dζ (6) и с выхода четвертого ключа 56 о величине интеграла [Y(ζ)-

[Y(ζ)- (to+τ1)] dζ (7) поступают соответственно на первый и шестой входы устройства 63 расчета коэффициентов передачи каналов регулирования, соединенные соответственно с первым и вторым входами третьего блока 67 деления. Таким образом реализуется расчет

(to+τ1)] dζ (7) поступают соответственно на первый и шестой входы устройства 63 расчета коэффициентов передачи каналов регулирования, соединенные соответственно с первым и вторым входами третьего блока 67 деления. Таким образом реализуется расчет  (t) в соответствии с выражением (4).

(t) в соответствии с выражением (4).

Сигнал о величине интеграла (7) в момент времени to+ τ2запоминается в шестом блоке 57 запоминания.

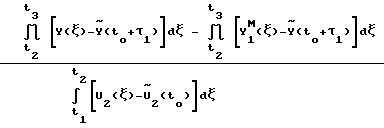

Величина интеграла [Y(ζ)-

[Y(ζ)- (to+τ1)]dζ; (8)

(to+τ1)]dζ; (8)

t2= to+ τ2; t3=t2+ τ2- τ1 определяется следующим образом. Из сигнала о текущем значении интеграла изменений регулируемой переменной с выхода пятого интегратора 55 с заданием начальных условий поступает на второй вход десятого блока 58 сравнения, где из него вычитается сигнал о величине интеграла (7), поступающий с выхода шестого блока 57 запоминания. В момент времени t3на выходе десятого блока 58 сравнения сигнал равен интегралу от регулируемой переменной Y(t) на интервале [to+ τ2; to+ τ2+ τ2- τ1].

Определение интеграла

Y

Y (to+τ1)

(to+τ1) dζ (9) осуществляется следующим образом.

dζ (9) осуществляется следующим образом.

Сигнал с выхода первого блока 11 умножения о величине U1(t) поступает на третий вход устройства 26 интегрирования переменных регулирования и через блок 34 задержки поступает на первый вход пятого блока 35 сравнения, где из него вычитается сигнал с выхода второго интегратора 37 с заданием начальных условий. Сигнал с выхода пятого блока 35 сравнения поступает на второй блок 36 умножения, где умножается на коэффициент передачи первого канала регулирования, и далее на вход второго интегратора 37 с заданием начальных условий. Таким образом формируется сигнал Yм1(t) на выходе второго интегратора 37 с заданием начальных условий.

Начальные условия второму интегратору 37 с заданием начальных условий задаются по сигналам с выходов пятого блока 45 задержки и второго элемента НЕ 44 в момент времени to+ τ2. Сигнал с выхода пятого блока 45 задержки представляет собой сигнал So(to) с выхода элемента И 24, задержанный в пятом блоке 45 задержки на время τ2. Сигнал с выхода второго элемента НЕ 44 S5(to+ τ2)>So(to+ τ2). На второй информационный вход второго интегратора 37 с заданием начальных условий в качестве начальных условий поступает сигнал с первого входа первого блока 4 сравнения. Таким образом, начальное значение второго интегратора 37 с заданием начальных условий устанавливается равным величине Y(to+ τ2).

Сигнал Uм1(t) с выхода второго интегратора 37 с заданием начальных условий поступает на первый вход шестого блока 40 сравнения, на второй вход которого поступает сигнал о величине  (to+ τ1) с выхода пятого блока 53 запоминания. Сигнал о разности Yм1(t)-

(to+ τ1) с выхода пятого блока 53 запоминания. Сигнал о разности Yм1(t)- (to+ τ1) поступает на вход третьего интегратора 41 с заданием начальных условий. Начальные условия третьего интегратора 41 с заданием начальных условий задаются аналогично тому, как это описано выше для первого 30, четвертого 49 и пятого 55 интеграторов с заданием начальных условий.

(to+ τ1) поступает на вход третьего интегратора 41 с заданием начальных условий. Начальные условия третьего интегратора 41 с заданием начальных условий задаются аналогично тому, как это описано выше для первого 30, четвертого 49 и пятого 55 интеграторов с заданием начальных условий.

Сигнал с выхода пятого блока 45 задержки So(to+ τ2)=1 и сигнал с выхода второго элемента НЕ 44 S6(to+ τ2) So(to+ τ2) поступают на управляющие входы третьего интегратора 41 с заданием начальных условий и переводят его в режим задания начальных условий. Значение начального условия задается сигналом с выхода источника 38 постоянного сигнала, поступающим на второй информационный вход третьего интегратора 41 с заданием начальных условий. В момент времени to+ τ2+ Δt сигналами So(t+τ 2+ Δ t)=0 и S6(t+ τ2+ Δt)=1 третий интегратор 41 с заданием начальных условий переводится в режим интегрирования сигнала с выхода шестого блока 40 сравнения.

В момент времени t3 по сигналу So(to)=1 c выхода элемента И 24, задержанному в пятом 45 и седьмом 59 блоках задержки на время τ2+ τ2- τ1, поступающему на управляющие входы второго 42 и пятого 60 ключей, на входы седьмого блока 43 сравнения поступают сигналы о величине интегралов [Y(ζ)-

[Y(ζ)- (to+τ1)]dζ

(to+τ1)]dζ

и

Y

Y (to+τ1)

(to+τ1) dζ.

dζ.

Cигнал о разнице с выхода седьмого блока 43 сравнения поступает на второй вход устройства 63 расчета коэффициентов передачи каналов регулирования, соединенного с первым входом второго блока 66 деления, на второй вход которого через третий вход устройства 63 расчета коэффициентов передачи каналов регулирова- ния поступает сигнал о величине интеграла  [U2(t)-

[U2(t)- (to)] dζ c третьего выхода устройства 26 интегрирования переменных регулирования. На выходе второго блока 66 деления получается сигнал о величине

(to)] dζ c третьего выхода устройства 26 интегрирования переменных регулирования. На выходе второго блока 66 деления получается сигнал о величине  (t).

(t).

Значение коэффициентов передачи  (t),

(t),  (t) определяются по выражениям

(t) определяются по выражениям (t2+Δt) =

(t2+Δt) =  (t2)+γ1[

(t2)+γ1[ (t2)-

(t2)- (t2)];

(t2)];

(10) (t2+Δt) =

(t2+Δt) =  (t2)+γ2[

(t2)+γ2[ (t)-

(t)- (t2)].

(t2)].

Реализация выражений (10) осуществляется следующим образом.

Сигналы с выходов второго 66 и третьего 67 блоков деления поступают на первые входы соответственно одиннадцатого 71 и двенадцатого 78 блоков сравнения, на вторые входы которых поступают сигналы с выходов седьмого 68 и восьмого 75 блоков запоминания соответственно о величине коэффициентов передачи  (t2) и

(t2) и  (t2). Cигналы с выходов одиннадцатого 71 и двенадцатого 78 блоков сравнения умножаются в третьем 70 и четвертом 77 масштабирующих блоках соответственно на коэффициенты γ1 и γ2. Сигналы с выходов третьего и четвертого масштабирующих блоков поступают на первые входы первого 69 и второго 76 сумматоров, где суммируются с сигналами с выходов соответственно седьмого 68 и восьмого 75 блоков запоминания.

(t2). Cигналы с выходов одиннадцатого 71 и двенадцатого 78 блоков сравнения умножаются в третьем 70 и четвертом 77 масштабирующих блоках соответственно на коэффициенты γ1 и γ2. Сигналы с выходов третьего и четвертого масштабирующих блоков поступают на первые входы первого 69 и второго 76 сумматоров, где суммируются с сигналами с выходов соответственно седьмого 68 и восьмого 75 блоков запоминания.

Сигналы  (t2+ Δt) и

(t2+ Δt) и  (t2+ Δt) поступают на входы седьмого 68 и восьмого 75 блоков запоминания, где запоминаются по сигналу So(to+ τ2)+1, задержанному на время Δt в девятом 64 и десятом 65 блоках задержки.

(t2+ Δt) поступают на входы седьмого 68 и восьмого 75 блоков запоминания, где запоминаются по сигналу So(to+ τ2)+1, задержанному на время Δt в девятом 64 и десятом 65 блоках задержки.

С выходов седьмого 68 и восьмого 75 блоков запоминания, соединенных с первым и вторым выходами устройства 63 расчета коэффициентов передачи каналов регулирования, сигналы поступают соответственно на вторые входы первого 6 блока деления и первого 11 блока умножения.

Расчет коэффициента k=k2/k1 осуществляется следующим образом. Сигнал с выхода седьмого блока 68 запоминания задерживается в одиннадцатом блоке 72 задержки на время τ2- τ1. С выхода одиннадцатого блока 72 задержки сигнал поступает на второй вход четвертого блока 74 деления, на первый вход которого поступает сигнал с выхода восьмого блока 75 запоминания. Сигнал о величине k с выхода четвертого блока 74 деления запоминается в девятом блоке 73 запоминания по сигналу с выхода десятого блока 65 задержки.

Применение предлагаемого регулятора для управления процессом непрерывного дозирования компонентов аглошихты способствует повышению производительности агломашины и снижению удельного расхода топлива за счет стабилизации расходов компонентов.

Для оценки эффективности предлагаемого регулятора было проведено имитационное моделирование системы управления непрерывным дозированием компонентов агломерационной шихты с предлагаемым регулятором. Результаты испытаний показали, что применение предлагаемой системы позволяет в сравнении с системой-прототипом снизить ошибку дозирования компонентов шихты на 40-60% (отн. ). Качество регулирования оценивалось по среднемодульному критерию. Это дает возможность повысить производительность агломашины площадью 312 м2 примерно на 1% и снизить удельный расход коксика примерно на 0,2 кг/т.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕНАЖЕР ОПЕРАТОРА СИСТЕМ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012065C1 |

| ТРЕНАЖЕР ОПЕРАТОРОВ СИСТЕМ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1990 |

|

RU2047909C1 |

| Регулирующее устройство | 1981 |

|

SU980069A1 |

| Система регулирования для объектов с запаздыванием | 1985 |

|

SU1295365A1 |

| Система автоматического регулирования | 1987 |

|

SU1483429A1 |

| Адаптивная система регулирования объекта с нестационарной характеристикой,например,дуговой сталеплавильной печи | 1983 |

|

SU1068891A1 |

| Адаптивный прогнозатор | 1982 |

|

SU1049866A1 |

| Прогнозирующий регулятор с переменной структурой | 1981 |

|

SU980068A1 |

| Система управления | 1984 |

|

SU1244636A1 |

| Адаптивная система регулирования многомерного объекта | 1981 |

|

SU1174901A1 |

Изобретение относится к автоматическому управлению и регулированию и может быть использовано для построения систем управления с большими запаздываниями, подверженных влиянию неконтролируемых параметрических возмущений. Изобретение позволяет повысить точность регулирования. Введение в регулятор блока формирования сигнала на идентификацию каналов регулирования, блока интегрирования переменных и блока расчета коэффициентов при достаточных изменениях задающего воздействия и стабильности процесса регулирования позволяет осуществлять уточнение коэффициентов моделей передачи каналов регулирования. 4 ил.

РЕГУЛЯТОР, содержащий первый блок задержки, последовательно соединенные первый блок сравнения и первое реальное форсирующее звено, последовательно соединенные первый сумматор, первый экстраполятор, первый масштабирующий блок и второй блок задержки, последовательно соединенные второй экстраполятор, второй блок сравнения, второе реальное форсирующее звено и первый блок умножения, выход второго экстраполятора соединен с входом первого блока задержки, выход которого соединен с первым входом первого сумматора, выход которого соединен с входом второго экстраполятора, выход второго блока задержки соединен с вторым входом второго блока сравнения, первый и второй входы первого блока сравнения соединены соответственно с первым и вторым входами регулятора, выходы первых масштабирующего блока и блока умножения соединены соответственно с первым и вторым выходами регулятора, отличающийся тем, что, с целью повышения точности регулирования, в него введены первый блок деления, устройство формирования сигнала на идентификацию каналов регулирования, устройство интегрирования переменных регулирования и устройство расчета коэффициентов передачи моделей каналов регулирования, входы которого соединены с соответствующими выходами устройства интегрирования переменных регулирования, первый выход соединен с первым входом устройства интегрирования переменных регулирования, второй выход - с вторым входом первого блока умножения, третий выход - с вторым входом первого блока деления, второй вход которого соединен с выходом первого реального форсирующего звена, выход - с вторым входом первого сумматора, первый вход, второй и первый выходы регулятора соединены соответственно с вторым, третьим и четвертым входами устройства интегрирования переменных регулирования, пятый вход которого соединен с выходом устройства формирования сигнала на идентификацию каналов регулирования, первый и второй входы которого соединены соответственно с выходом первого блока сравнения и вторым входом регулятора, причем блок формирования сигнала на идентификацию каналов регулирования содержит первый и второй задатчики, последовательно соединенные третий блок задержки, третий блок сравнения, второй масштабирующий блок, первый блок определения модуля, первый компаратор и элемент И, последовательно соединенные блок определения знака, первый фильтр низкой частоты, второй блок определения модуля и второй компаратор, вход третьего блока задержки и второй вход третьего блока сравнения соединены с вторым входом устройства формирования сигнала на идентификацию каналов регулирования, первым входом которого является вход блока определения знака, а выходом - выход элемента И, второй вход которого соединен с выходом второго компаратора, второй вход которого и второй вход первого компаратора соединены с соответствующими задатчиками, устройство интегрирования переменных регулирования содержит четвертый - седьмой блоки задержки, первый, второй и третий элементы НЕ, источник постоянного сигнала, последовательно соединенные второй фильтр низкой частоты, первый запоминающий блок, четвертый блок сравнения, первый интегратор, второй запоминающий блок и первый ключ, последовательно соединенные восьмой блок задержки, пятый блок сравнения, второй блок умножения, второй интегратор, шестой блок сравнения, третий интегратор, второй ключ и седьмой блок сравнения, последовательно соединенные третий фильтр низкой частоты, третий запоминающий блок, восьмой блок сравнения, четвертый интегратор, четвертый запоминающий блок и третий ключ, последовательно соединенные четвертый фильтр низкой частоты, пятый запоминающий блок, девятый блок сравнения, пятый интегратор, четвертый ключ, шестой запоминающий блок, десятый блок сравнения и пятый ключ, вход четвертого блока задержки, второй вход первого запоминающего блока, первый управляющий вход задания начальных условий первого интегратора, вход первого элемента НЕ, вход пятого блока задержки, первый управляющий вход задания начальных условий четвертого интегратора, управляющий вход третьего запоминающего блока и вход шестого блока задержки объединены и подключены к пятому входу устройства интегрирования переменных регулирования, выход четвертого блока задержки соединен с управляющими входами второго и четвертого блоков запоминания, выход источника постоянного сигнала соединен с вторыми информационными входами первого, третьего, четвертого и пятого интеграторов, выход первого элемента НЕ соединен с вторыми управляющими входами задания начальных условий первого и четвертого интеграторов, выход пятого блока задержки соединен с первым управляющим входом задания начальных условий третьего интегратора, седьмого блока задержки, шестого запоминающего блока, управляющими входами первого и четвертого ключей, второго элемента НЕ и первым управляющим входом задания начальных условий, второго интегратора выход второго интегратора соединен с вторым входом пятого блока сравнения, выход пятого блока запоминания - с вторым входом шестого блока сравнения, выход пятого ключа - с вторым входом седьмого блока сравнения, выход второго элемента НЕ - с вторыми управляющими входами задания начальных условий второго, третьего и четвертого интеграторов, выход седьмого блока задержки - с управляющими входами второго и пятого ключей, выход шестого блока задержки - с входом третьего элемента НЕ, вторым входом пятого запоминающего блока и первым управляющим входом задания начальных условий пятого интегратора, второй управляющий вход задания начальных условий которого соединен с выходом третьего элемента НЕ, выход пятого интегратора - с вторым выходом десятого блока сравнения, выход первого ключа является первым выходом устройства интегрирования переменных регулирования, вторым выходом которого является выход седьмого блока сравнения, третьим выходом - выход третьего ключа, четвертым выходом - выход седьмого блока задержки, соединенного с управляющим входом третьего ключа, пятым выходом - выход пятого блока задержки, шестым выходом - выход четвертого ключа, вход четвертого фильтра низкой частоты, второй вход девятого блока сравнения и второй информационный вход второго интегратора объединены и являются вторым входом устройства интегрирования переменных регулирования, четвертым входом которого являются объединенные входы второго фильтра низкой частоты, второй вход четвертого блока сравнения и вход восьмого блока задержки, третьим входом - объединенные вход третьего фильтра низкой частоты и второй вход восьмого блока сравнения, первым входом является второй вход второго блока умножения, устройство расчета коэффициентов передачи моделей каналов регулирования содержит девятый и десятый блоки задержки, последовательно соединенные второй блок деления, одиннадцатый блок сравнения, третий масштабирующий блок, второй сумматор, седьмой запоминающий блок и одиннадцатый блок задержки, последовательно соединенные третий блок деления, двенадцатый блок сравнения, четвертый масштабирующий блок, третий сумматор, восьмой запоминающий блок, четвертый блок деления и девятый блок запоминания, выход которого является вторым выходом устройства расчета коэффициентов передачи моделей каналов регулирования, третьим выходом которого является выход седьмого блока запоминания, первым выходом - выход восьмого блока запоминания, первым входом - первый вход третьего блока деления, второй вход которого является шестым входом устройства, вторым входом - первый вход второго блока деления, второй вход которого является третьим входом устройства расчета коэффициентов передачи моделей каналов регулирования, четвертым входом которого является вход десятого блока задержки, выход которого соединен с управляющими входами девятого блока запоминания и седьмого блока запоминания, выход которого соединен с вторым входом второго сумматора и вычитающим входом одиннадцатого блока сравнения, выход восьмого блока запоминания соединен с вторым входом третьего сумматора и вычитающим входом двенадцатого блока сравнения, а управляющий вход соединен с выходом девятого блока задержки, вход которого является пятым входом устройства расчета коэффициентов передачи моделей каналов регулирования, первый - шестой выходы устройства интегрирования переменных регулирования соединены соответственно с одноименными входами устройства расчета коэффициентов передачи моделей каналов регулирования.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оптическая система | 1984 |

|

SU1185300A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1994-06-30—Публикация

1990-06-21—Подача