Изобретение относится к системам передачи информации и может быть использовано для обмена информацией комплексов управления объектами различного назначения, в частности, в режиме непрерывной передачи от нескольких пользователей по одному радиоканалу.

Известна система телесигнализации с временным разделением каналов [1] содержащая группу периферийных устройств, соединенных через линию связи с приемным устройством.

Каждое периферийное устройство содержит блоки приема тактовых импульсов и синхроимпульсов, регистр сдвига, селективный элемент и инвертор.

Данная система имеет следующие недостатки:

система работает в жестком режиме постоянного последовательного опроса каждого периферийного устройства, причем каждому периферийному устройству выделено конкретное время в каждом цикле опроса независимо от того, имеется у него информация для передачи или нет. Это снижает гибкость системы;

при увеличении количества периферийных устройств (более 16) требуется изменение аппаратных средств, как периферийных, так и приемного устройства;

система передает функционально ограниченную информацию ("1" Да или "0" Нет).

Известная система передачи информации [2] выбранная в качестве прототипа, состоящая из последовательно соединенных контролируемых пунктов, каждый из которых содержит n датчиков, первичный преобразователь информации, приемник линейного сигнала, блок ввода информации в информационную линию, роль которого может выполнять универсальный регистр сдвига, блок формирования линейного сигнала, блок обнаружения синхросигнала, блок задержки синхросигнала, блок обнаружения линейного сигнала, генератор импульсов и блок формирования синхросигнала.

Однако данная система статичная, не обладает информационной гибкостью в части регулирования количества передаваемой информации, а при интенсивном поступлении данных от источников информации (датчиков) в условиях ограниченных возможностей информационной емкости приемной части не обеспечивает нормальной работы системы по доставке данных в приемную часть.

В условиях постоянного наличия данных для передачи на каждом источнике информации в системе-прототипе будет постоянно происходить передача данных от источников информации (ИИ), начинающих первыми декодирование сигналов вызова (запроса на передачу) от приемной стороны. В таких условиях какая-либо часть источников информации системы не сможет передать имеющуюся информацию в приемную часть системы, т.е. нормально функционировать, поэтому возникает необходимость ограничить количество ИИ в зависимости от реальной интенсивности потока информации, поступающего на объекты источников информации.

Изобретение решает задачу повышения информационной гибкости системы путем регулирования количества передаваемой информации и обеспечения равных возможностей обработки информации от каждого источника информации системы в условиях непрерывного (интенсивного) поступления информации при ограниченной емкости приемной стороны системы.

Поставленная задача достигается тем, что в каждый источник информации введены дешифратор, элемент задержки, первый и второй ключи, блок стробирования, элемент сравнения, блок буферной памяти, элемент ИЛИ, формирователь маркерного импульса, блок задания режима блокировки и дешифратор снятия блокировки, вход блока выделения синхросигнала, первые входы дешифратора, первого ключа, дешифратора снятия блокировки и вход элемента задержки объединены и являются первым входом источника информации, выход блока выделения синхросигнала подключен к первому входу дешифратора снятия блокировки и второму входу дешифратора, выход которого соединен с первым входом блока задания режима блокировки, выход которого соединен с первым входом второго ключа и блока буферной памяти, а через блок стробирования с вторым входом первого ключа, выход которого подключен к первому входу формирователя маркерного импульса и к первому входу элемента сравнения, выход которого соединен с вторым входом формирователя маркерного импульса, выход которого подключен к первому входу элемента ИЛИ, выход генератора тактовых импульсов соединен с вторым входом блока буферной памяти, первый выход которого подключен к третьему входу формирователя маркерного импульса, к второму входу элемента сравнения и к второму входу второго ключа, выход элемента задержки соединен с третьим входом второго ключа, выход которого подключен к второму входу элемента ИЛИ, выход элемента ИЛИ является выходом источника информации, второй выход блока буферной памяти соединен с третьим входом элемента ИЛИ, первый выход дешифратора снятия блокировки соединен с вторым входом блока задания режима блокировки, третий вход которого соединен с вторым выходом дешифратора снятия блокировки и третьим выходом блока буферной памяти, третий вход которой является вторым входом источника информации, при этом первый вход первого источника информации является первым входом системы, а первый вход каждого последующего источника информации соединен с выходом предыдущего, а вторые входы источника информации являются информационными входами системы, причем выход последнего источника информации является выходом системы.

Введение в заявленную систему новых блоков с соответствующими связями позволяет повысить информационную гибкость системы в условиях интенсивного поступления информации при ограниченной информационной емкости приемной стороны; за счет регулирования количества передаваемой информации и создания равных условий возможностей обработки информации для каждого источника информации.

Кроме того, вводится следующая структура пакета данных, передаваемая каждым источником информации: информационный пакет (случайная или фиксированная длительность), первое маркерное сообщение (2 байта), состоящее из маркера (1 байт) и служебной части маркерного сообщения (1 байт). Маркер представляет собой специальную кодовую комбинацию, не используемую для передачи информации. В конкретном техническом решении может быть использована комбинация из 8 единиц. Служебная часть первого маркерного сообщения, например, состоит из двух сегментов равной длины по 4 бита каждый; в первом сегменте содержится информация о максимальном числе ИИ, которые могут передавать информацию на данном цикле опроса всех ИИ системы, а во втором сегменте текущее число N ИИ системы, уже передавших информационные пакеты на данном цикле. Информационные пакеты от ИИ обрабатываются, например, восьмипроцессорной вычислительной системой. Поэтому в данном случае максимальное число ИИ, которое могут передать свои пакеты за один цикл опроса, не превышает 8, т.е. Lmax=8, для кодирования которого требуется 4 бита.

На разных циклах опроса значение L может быть также различно и определяется числом освободившихся процессоров к моменту начала цикла опроса ИИ.

Кроме вышеназначенной структуры первого маркерного сообщения, из приемной части вычислительной системы (ВС) выдается второе маркерное сообщение (16 бит), состоящее из второго маркера (8 бит) и служебной части (8 бит), в которой передается количество блокировок запросов от ВС, т.е. выдается внешняя установка блокировки количества запросов на передачу от ИИ, которая может меняться в зависимости от условий работы: интенсивности поступающей информации от ИИ, количества ИИ и реальной емкости приемной стороны ВС, при этом данное решение может приниматься (вырабатываться) в процессе (реальной) работы системы при передаче информации и устанавливаться во все ИИ.

В начальный момент работы системы из ВС поступает сигнал блокировки (маркерное сообщение) во все ИИ, устанавливая в каждом ИИ (одно и то же для каждого ИИ) определенное количество запросов (найденное по условиям работы системы или выбранное конкретно), которое далее будeт игнорироваться каждым ИИ, но игнорироваться только после первого запpоса, который достигнет ИИ и при котором будет передано имеющееся в ИИ сообщение в приемную часть ВС (последнее обеспечивается третьим выходом блока буферной памяти, на котором появляется импульс через время, равное времени передачи маркерного сообщения, и в том случае, если в блоке памяти нет данных для передачи).

После первого запроса и передачи имеющегося сообщения в каждом ИИ включается блок режима блокировки, который игнорирует последующие m запросов, при этом значение m было установлено в ИИ (в блоке режима) в момент подачи сообщения (о снятии) блокировки.

Тем самым последующие запросы направляются к последующим ИИ системы, причем после первого запроса каждого последующего ИИ происходит выдача имеющейся информации и в нем включается блок режима блокировки, который далее начинает игнорировать последующие запросы. И так для каждого последующего ИИ. Тем самым будет ограничена возможность монопольного захвата магистрали передачи информации в системе передачи и обеспечены равные возможности обслуживания ИИ по передаче информации в приемную часть.

После установки количества запросов, которое должно быть проигнорировано ИИ, каждый ИИ передает (после получения первого маркерного сообщения) на последующий ИИ "новое" первое маркерное сообщение, служебная часть которого содержит информацию о числе ИИ, которые еще могут передать информацию (так как имеются свободные процессоры в приемной ВС). После того как это непрерывно уменьшающееся число достигнет нуля, остальные ИИ начать передачу на данном одиночном цикле опроса (запроса) не смогут. При этом учитывается и режим блокировки, при котором последующий ИИ не может передавать имеющуюся информацию, если он ее уже передавал на предыдущем одиночном цикле опроса.

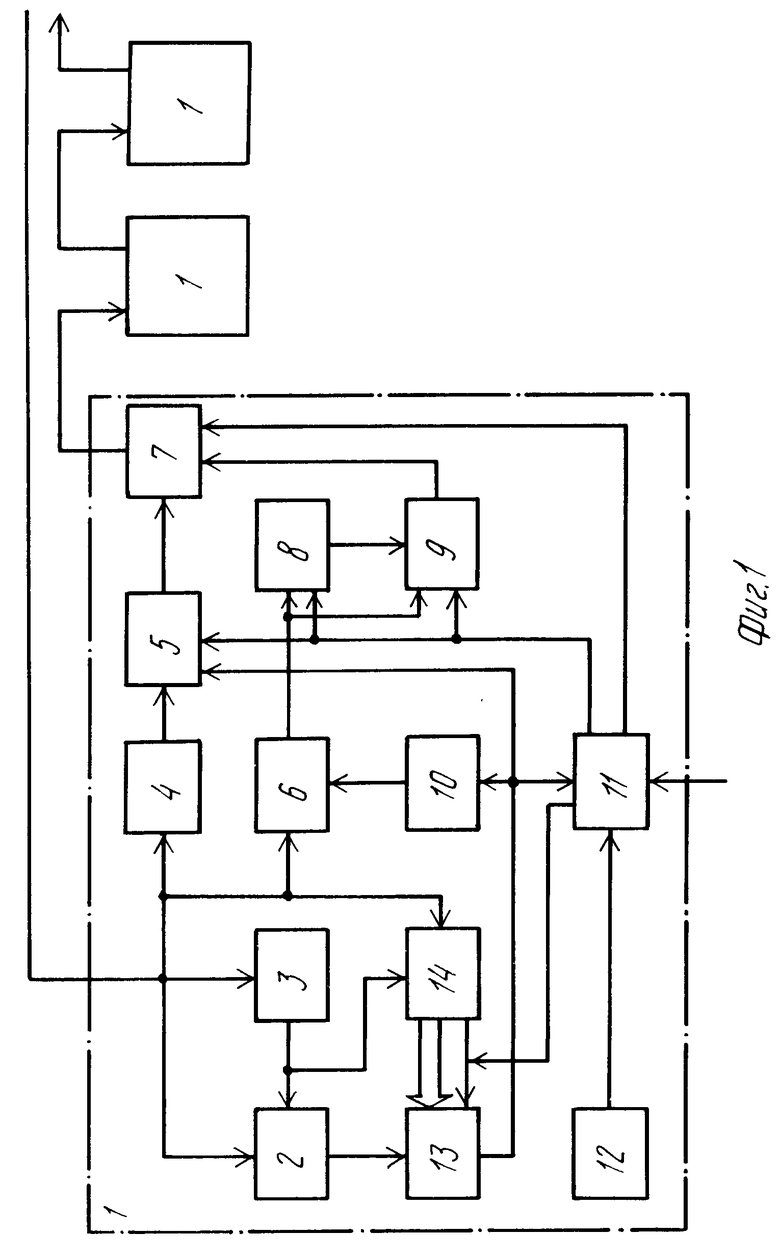

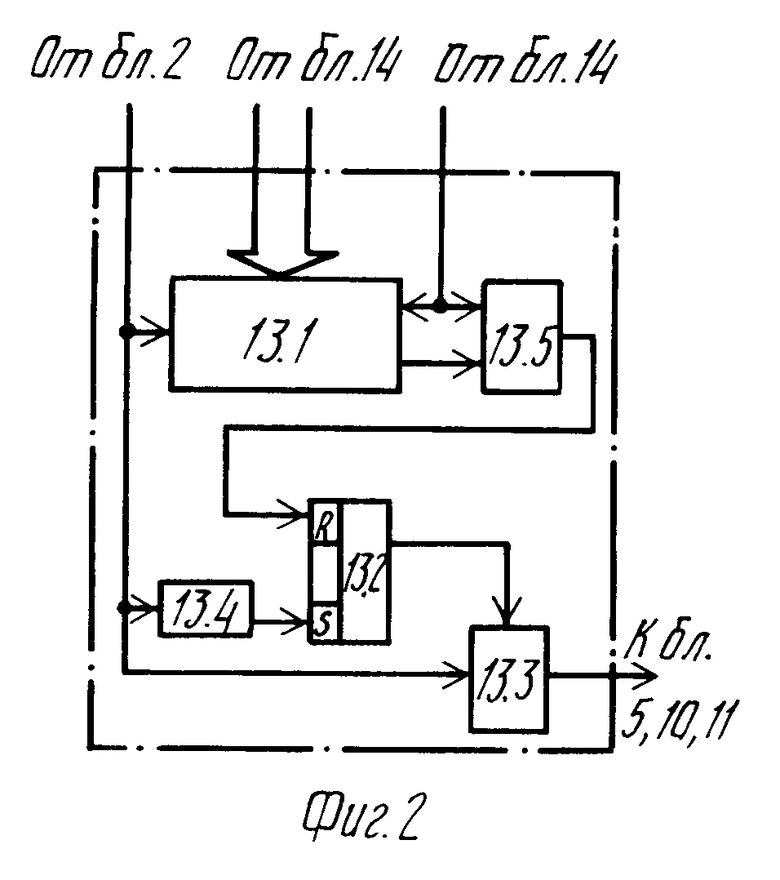

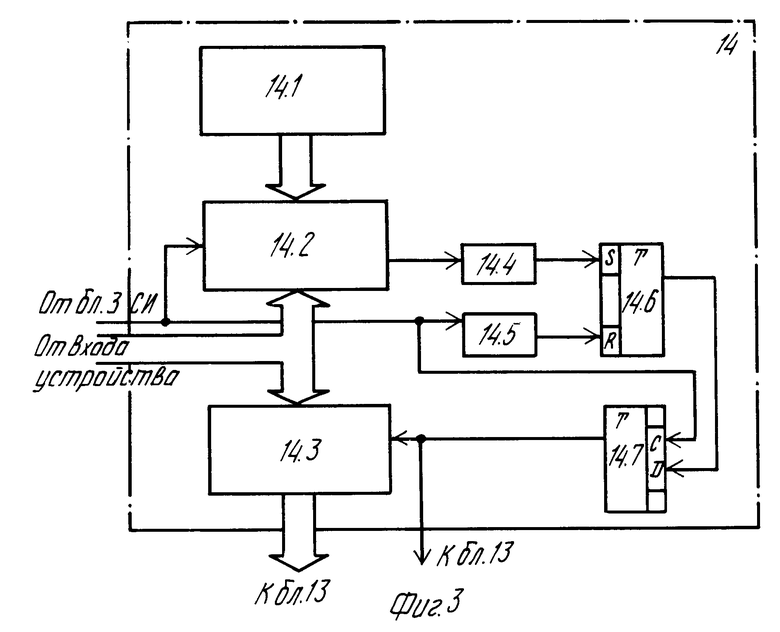

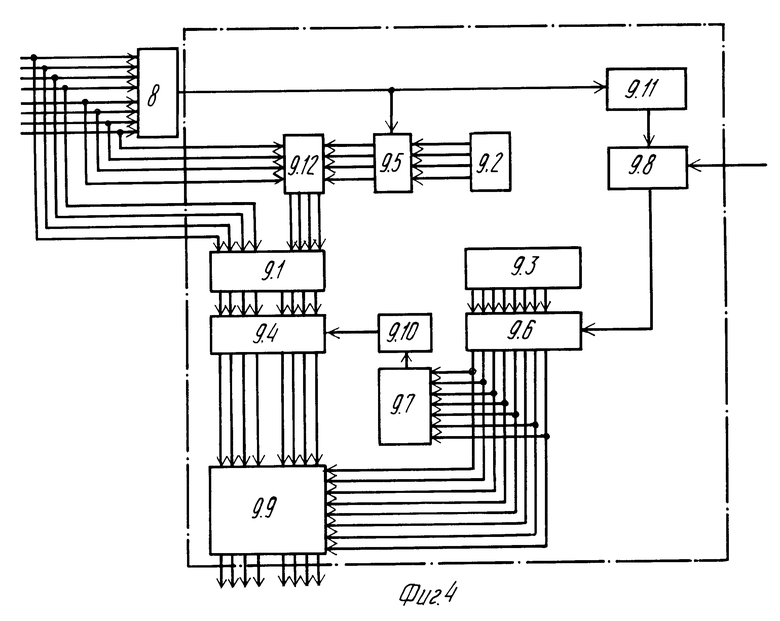

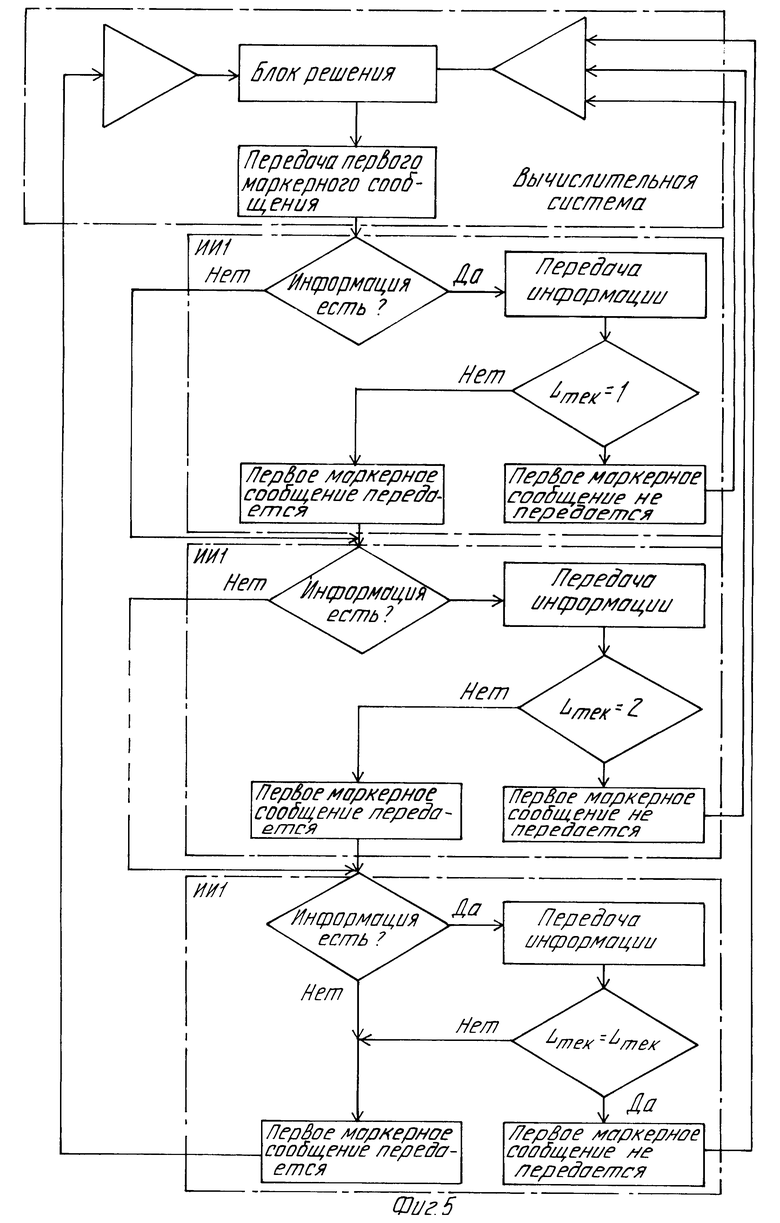

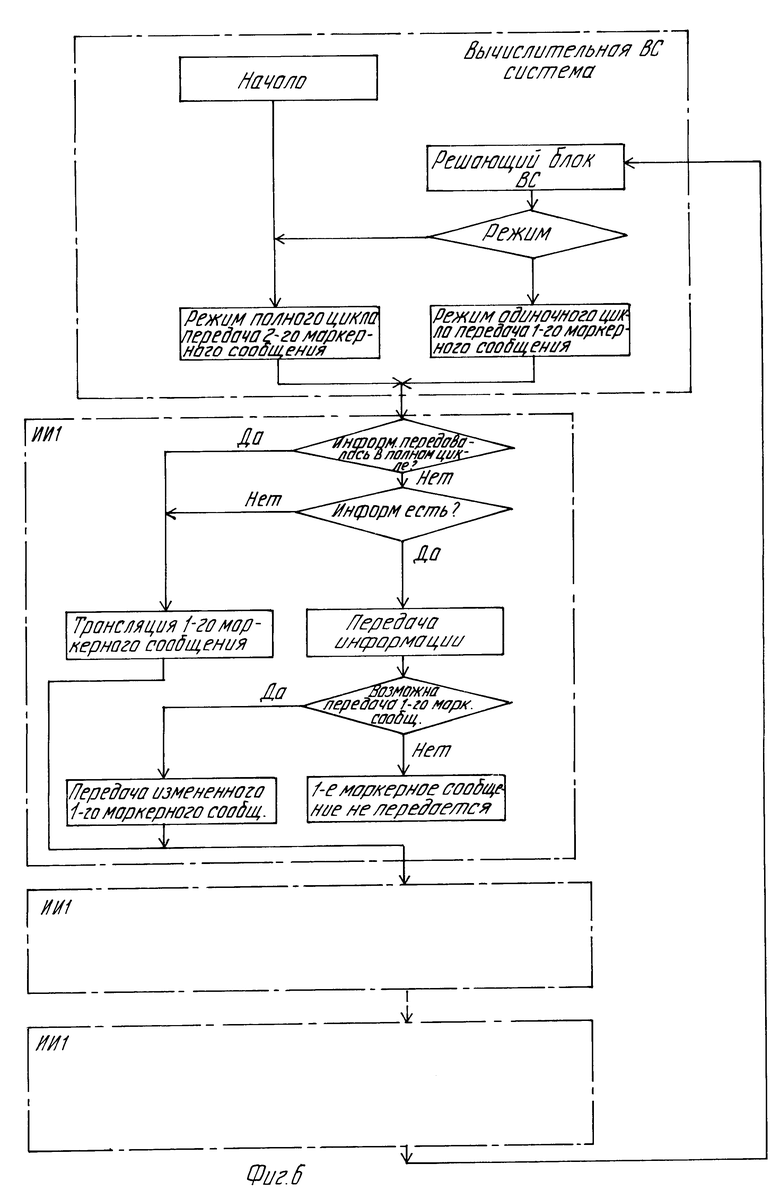

На фиг.1 представлена блок-схема заявляемой системы; на фиг.2 функциональная схема блока задания режима блокировки; на фиг.3 схема дешифратора снятия блокировки; на фиг.4 блок-схема формирователя маркерного импульса; на фиг. 5 блок-схема укрупненного алгоритма одиночного цикла работы системы; на фиг.6 блок-схема укрупненного алгоритма полного цикла работы системы.

Система состоит из последовательно соединенных источников информации (ИИ) 1, каждый из которых содержит дешифратор 2, блок 3 выделения синхросигнала, элемент задержки 4, ключи 5 и 6, элемент ИЛИ 7, элемент сравнения 8, формирователь 9 маркерного импульса, блок 10 стробирования, блок 11 буферной памяти, генератор 12 тактовых импульсов, блок 13 задания режима блокировки и дешифратор 14 снятия блокировки.

Формирователь 9 маркерного импульса содержит регистры 9.1, 9.2, 9.3, группы элементов И 9.4, 9.5, 9.6, элементы И 9.7, 9.8, группы элементов ИЛИ 9.9, формирователи 9.10, 9.11 импульсов, сумматоры 9.12.

Блок 13 задания режима блокировки содержит управляемый счетчик 13.1, RS-триггер 13.2, коммутатор 13.3, линию задержки 13.4 и схему ИЛИ 13.5.

Дешифратор 14 снятия блокировки содержит регистр 14.1 (структуры) сигнала блокировки, элемент сравнения 14.2, блок ключей 14.3, два элемента задержки 14.4, 14.5, RS-триггер 14.6, DC-триггер 14.7.

В системе использован принцип последовательно-параллельной передачи информации, т. е. информация передается последовательно по байтам, а сам байт-параллельно по восьми информационным линиям. Структура пакета данных, передаваемого каждым ИИ, следующая: информационный пакет (случайная или фиксированная длительность), далее маркерное сообщение, состоящее из маркера и служебной части маркерного сообщения. Маркер представляет собой кодовую комбинацию, не используемую для передачи информации. Служебная часть маркерного сообщения состоит из двух частей, в первой части содержится информация о максимальном числе ИИ 1, которые могут передавать информацию на данном цикле опроса совокупности ИИ 1, а во второй части текущее число М ИИ 1, уже передавших информационные пакеты на данном цикле. Информационные пакеты от ИИ 1 обрабатываются процессорной вычислительной системой. Поэтому максимальное число ИИ 1, которые могут передавать свои пакеты за один одиночный цикл опроса, не превышает N, т.е. Lmax=N.

На разных одиночных циклах опроса значение L может быть различно и определяться числом освободившихся процессоров к моменту начала цикла опроса ИИ 1.

Первоначально внешний контроллер вычислительной системы выдает сообщение (о снятии) блокировки, устанавливая требуемое количество блокировок запросов на передачу от ИИ 1. Структура сообщения о блокировке состоит из двух частей: первая маркера блокировки, которая представляет специальную кодовую комбинацию, не используемую при передаче данных, вторая количество блокировок запросов. Дешифратор 14 производит дешифрацию первой части сообщения о блокировке и устанавливает значение второй части, поступающей в параллельном коде в блок 13 режима блокировки. Такая установка производится в каждом ИИ 1. Структура сообщения о блокировке поступает на внешний контроллер, свидетельствуя об исправности информационной магистрали системы.

Режим одиночного цикла системы.

Рассмотрим работу системы в режиме одиночного цикла (фиг.5).

Одиночный цикл опроса ИИ 1 начинается с передачи ВС (внешним контроллером вычислительной системы) первого маркерного сообщения, служебная часть которого имеет следующий вид: первый сегмент (4 бата) Lтек 1, где Lтек число свободных процессоров к этому моменту времени, второй ноль. Эта информация передается в параллельном виде и поступает первоначально на первый вход первого ИИ 1. Если у первого ИИ 1 есть информация, то он передает сначала ее, а потом, если Lтек>1 первое маркерное сообщение с М=1 (до этого М=0), где М значение второго сегмента, определяющее число ИИ 1, уже передавших информацию. Если Lтек=1, то первое маркерное сообщение не передается, т.е. остальные ИИ 1 начать передачу на данном одиночном цикле опроса не могут. Второй ИИ 1, получив первое маркерное сообщение от первого ИИ 1, также передает свою информацию (если она имеется), а затем, если Lтек=1, первое маркерное сообщение не передается. Аналогично работают в режиме одиночного цикла и все остальные ИИ 1.

В режиме одиночного цикла система работает следующим образом.

Информация (пакет данных), подлежащая передаче, поступает первоначально в блок 11 буферной памяти. Считывание и запись в блок 11 синхронизируется генератором 12.

Информационный пакет с выхода предыдущего ИИ 1 поступает на первый вход следующего ИИ 1 и далее проходит транзитом через все ИИ 1 на внешний контроллер ВС.

При поступлении же на вход следующего ИИ 1 первого маркерного сообщения, выработанного предыдущим ИИ 1 (если произведена выдача информации), дешифратор 2 этого ИИ 1 формирует сигнал разрешения считывания из блока 11. Импульс с выхода дешифратора 2 поступает также на вход блока 10 стробирования и первый вход ключа 5, закрывая его и препятствуя тем самым прохождению первого маркерного сообщения. При этом, если на этот ИИ 1 первое маркерное сообщение (т.е. запрос на передачу данных) поступает первый раз, импульс с дешифратора 2 беспрепятственно проходит через блок 13, поступая на блоки 10 и 5.

При следующих обращениях такая возможность будет запрещена, а количество таких обращений определяется ВС.

Далее на выходе блока 10 формируется стробимпульс определенной длительности, с помощью которого выделяется служебная часть первого маркерного сообщения, которое состоит из двух сегментов. Элемент 11 8 сравнивает содержимое сегментов, т.е. величины L и М. Если М<L-1, то после окончания считывания данных из блока 11 буферной памяти блоком 9 по сигналу блока 11 считывается маркер с новым текущим значением второго сегмента служебной части, увеличенным на единицу. Если же на входе элемента 8 сравнения М=L-1, то это означает, что данный ИИ 1 последним передает информацию и маркер после считывания данных из блока 11 этого ИИ 1 не передается. Следовательно, в этом случае последующие ИИ 1 не получат разрешения на передачу информации в канал связи.

Формирователь 9 работает следующим образом.

При поступлении на вход элемента 8 сравнения служебной части первого маркерного сообщения, выделенной с помощью стробирующего блока 10, производится сравнение величин L-1 и М. Если М<L-1, т.е. данный ИИ 1 будет передавать информацию не последним, на выходе элемента 8 появляется импульс. Элемент 8 сравнения является нетактируемым, и импульс на его выходе появляется в момент поступления на его входе сигналов (соответственно величин L-1 и М) и существует до тех пор, пока на входах элемента 8 присутствует сигнал.

Значение L-1 сразу записывается в соответствующие разряды регистра 9.1, а в другие 4 разряда записывается (при наличии импульса на выходе элемента 8) значение М, увеличенное на единицу. Эта операция осуществляется с помощью сумматора 9.12, не первую группу входов которого поступает старое значение М, а на вторую число 0001 (т.е. единица в двоичном коде), записанное в регистре 9.2. Таким образом, содержимое регистра 9.1 есть новое содержимое служебной части первого маркерного сообщения. Считывание информации из регистра 9.1 производится по сигналу от формирователя 9.10 импульса после окончания передачи маркера, который записан в регистре 9.1 и представляет собой набор из 8 единиц. Элемент И 9.7 служит для защиты маркера и срабатывает только при наличии на всех его входах единиц. Формирователь 9.10 импульса запускается задним фронтом импульса с выхода элемента 9.7. Считывание из регистра 9.3 осуществляется по импульсу из блока 11 буферной памяти, который пропускается элементом И 9.8 только при условии М<L-1, т.е. при наличии импульса на выходе элемента 8 сравнения. На второй вход элемента И 9.8 подается импульс с выхода формирователя 9.11 (расширителя импульса), длительность которого соответствует максимальной длительности пакета информации.

Таким образом, по окончании передачи пакета информации блоком 11 формирователь 9 передает вначале маркер, а затем служебную часть первого маркерного сообщения с новым значением М и старым L-1. При этом группа элементов ИЛИ 9.9 служит для объединения одноименных выходов регистров 9.1 (группы элементов И 9.4) и 9.3 (группы элементов И 9.6).

Если импульс на выходе элемента 8 сравнения отсутствует, то формирователь 9.11 не запускается и на вход групп элементов И 9.5 импульс не подается. Вследствие этого передача первого маркерного сообщения после передачи данных ИИ 1 пакета информации не производится.

Режим полного (многократного) цикла (фиг.6).

Первоначально (в начале каждого полного цикла) ВС через внешний контроллер выдает второе маркерное сообщение о блокировке, устанавливая требуемое количество блокировок запросов на передачу ИИ 1.

Структура второго маркерного сообщения о блокировке состоит из двух частей: первая маркера блокировки, который представляет собой кодовую комбинацию, не используемую при передаче данных, а вторая количество блокировок запросов. Дешифратор 14 производит распознавание первой части сообщения и обеспечивает установку значения второй части сообщения, поступающей в параллельном коде в блок 13 режима блокировки. Такая установка производится в каждом ИИ 1, так как второе маркерное сообщение проходит через все ИИ 1 при установке блокировки запросов. Структура сообщения о блокировке (второе маркерное сообщение) возвращается по цепочке в приемную ВС через внешний контроллер, свидетельствуя об исправности информационной магистрали и о проведенной операции блокировки запросов всех ИИ 1.

Далее начинается одиночный цикл работы системы, описанный выше. Максимальное число одиночных циклов полного цикла для нашего случая не может быть более 8.

Однако при следующем одиночном цикле, если не все ИИ передали свою информацию, первым ИИ 1 становится тот ИИ 1, который не получил первое маркерное сообщение, разрешающее передачу данных, или не имел информации и не проводил ее передачу. При этом все, что сказано о ИИ 1 в части работы и условий передачи данных и первого маркерного сообщения, справедливо для данного и следующих за ним ИИ 1 в последовательной цепочке ИИ системы передачи.

Возможны и следующие одиночные циклы опроса, при которых производится передача данных, начиная с тех ИИ 1, которые ее еще не выдали.

В том случае, если начиная с какого-то одиночного цикла опроса ни один (ни тот, с которого опрос начинается, ни последующие за ним) ИИ 1 не выдает данных, то ВС формирует сообщение о блокировке, а затем начинает новый полный цикл с выдачи второго маркерного сообщения во все ИИ 1. И далее начинается одиночный цикл работы системы передачи с выдачи первого маркерного сообщения.

Причем возможны случаи, когда после выдачи первого маркерного сообщения ни один ИИ 1 не выдает информацию. В этом случае необходимо повторить выдачу первого маркерного сообщения (т.е. провести новый опрос ИИ 1 при условии подачи до этого в ИИ 1 второго маркерного сообщения).

Однако в условиях интенсивного поступления в ИИ 1 данных это происходит крайне редко и система работает в основном постоянно, обеспечивая равные условия для передачи данных от любого ИИ 1, входящего в систему.

Возможен одиночный цикл работы системы, когда при обращении ВС с запросом на передачу все ИИ 1 (если число ИИ 1 не больше количества процессоров в ВС) могут быть обслужены в этом одиночном цикле работы системы. В этом случае ВС начинает новый цикл с выдачи второго маркерного сообщения.

Формирование сообщения о блокировке ВС происходит в следующих случаях:

в одном или нескольких одиночных циклах обращения ВС отработали все ИИ 1, причем в каждом одиночном цикле должен быть обслужен хотя бы один ИИ 1;

при обращении ВС, начиная с того ИИ 1, с которого производится одиночный цикл работы системы, ни один ИИ 1 не выдает данных.

Эти случаи должны контpолироваться в приемной части ВС и при их наличии должно быть выдано второе маркерное сообщение о блокировке, что и обеспечивает равные условия для всех ИИ 1 при передаче и последующей обработке поступающей информации в приемной части ВС.

Таким образом, в начале работы, а также, когда создаются случаи, описанные выше, ВС выдает второе маркерное сообщение о блокировке, которое состоит из двух частей: в первой маркер сообщения о (снятии) блокировке, во второй количество блокируемых запросов на передачу.

После дешифрации первой части сообщения о (снятии) блокировке в блоке 14 с его выхода поступает сигнал на вход блока 13 (фиг.2) и через схему ИЛИ 13.5 проходит на R-вход RS-триггера 13.2, тем самым снимается сигнал блокировки с коммутатора 13.3, позволяя при очередном обращении к ИИ 1 на передачу данных пропустить сигнал с выхода дешифратора 2 и обеспечить работу ИИ 1, как было описано выше. Сигнал обращения с дешифратора 2 поступает также на счетный вход управляемого делителя 13.1 и через линию задержки 13.4 на S-вход RS-триггера 13.2, тем самым обеспечивая на его выходе появление сигнала блокировки коммутатора 13.3, и препятствуя прохождению при последующих обращениях сигналов с дешифратора 2, которые, однако, будут поступать на счетный вход управляемого делителя 13.1 и после прихода соответствующего количества обращений на выходе управляемого делителя 13.1 появляется сигнал, который через схему ИЛИ 13.5 поступит на R-вход RS-триггера 13.2, тем самым будет снят сигнал блокировки с коммутатора 13.3, что обеспечит при последующем обращении прохождение сигнала с дешифратора 2.

Одновременно вторая часть сообщения о (снятии) блокировке поступает (параллельным кодом) с параллельного выхода дешифратора 14 на параллельный вход блока 13 для установки количества блокируемых запросов (обращений) на передачу данных в управляемый счетчик 13.1.

Тем самым по результатам работы системы приемная часть системы в процессе этой работы может менять количество блокируемых запросов (обращений), обеспечивая оперативное регулирование пропускной способности ИИ 1 и в целом всей системы в зависимости от интенсивности поступающей информации на ИИ 1 в блоке памяти 11 и реальной функционирующей емкости (количество работающих микропроцессоров) приемной стороны.

Блок 14 дешифратора блокировки работает следующим образом.

Как сказано ранее, структура сигнала блокировки состоит из двух частей: в первой маркер сообщения о (снятии) блокировке, во второй количество блокируемых запросов на передачу, причем первая часть идет под первый синхроимпульс (СИ), вторая часть под второй СИ.

Вначале на вход дешифратора 14 блокировки поступает первая часть сообщения блокировки маркер блокировки на схему сравнения 14.2 и блок ключей 14.3. Под такт первого СИ в схеме сравнения 14.2 происходит сравнение эталонной структуры маркера блокировки, постоянно поступающей на второй (параллельный) вход схемы сравнения 14.2 с регистра 14.1, и структуры маркера блокировки, поступающей из приемной части. В случае совпадения этих структур на выходе схемы сравнения 14.2 появляется сигнал, который через линию задержки 14.4 поступает на S-вход RS-триггера 14.6. При этом на выходе RS-триггера появляется сигнал лог."1", который устанавливается на D-входе D-триггера 14.7, но несколько позже, что определяется линией задержки 14.4 синхросигнала, поступающего с блока 3 выделения синхросигналов. Под второй такт СИ приходит вторая часть сообщения блокировки, которая поступает на входы схемы сравнения 14.2 и блока ключей 14.3.

При этом вторым СИ, поступившим на С-вход D-триггера, на выходе D-триггера устанавливается сигнал лог."1", который поступает на вход разрешения блока ключей 14.3, обеспечивая тем самым, прохождение структуры второй части сообщения блокировки на выход дешифратора, при этом выход D-триггера является выходом установки сигнала блокировки дешифратора 14. Длительность сигнала с D-триггера определяется линией задержки 14.5.

Система передачи информации может быть использована для обмена информацией комплексов управления объектами различного назначения, в частности, в режиме непрерывной передачи от нескольких пользователей по одному радиоканалу. Изобретение решает задачу повышения информационной гибкости системы в условиях непрерывного интенсивного поступления информации при ограниченной информационной емкости приемной стороны системы. Система состоит из последовательно соединенных источников информации, каждый из которых содержит дешифратор, блок выделения синхросигнала, элемент задержки, два ключа, элемент ИЛИ, элемент сравнения, формирователь маркерного импульса, блок стробирования, блок буферной памяти, генератор тактовых импульсов, блок режима блокировки и дешифратор снятия блокировки. 6 ил.

СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ, содержащая последовательно соединенные источники информации, каждый из которых содержит блок выделения синхросигналов, генератор тактовых импульсов, отличающаяся тем, что в каждый источник информации введены дешифратор, элемент задержки, первый и второй ключи, блок стробирования, элемент сравнения, блок буферной памяти, элемент ИЛИ, формирователь маркерного импульса, блок задания режима блокировки и дешифратор снятия блокировки, вход блока выделения синхросигнала, первые входы дешифратора, первого ключа, дешифратора снятия блокировки и вход элемента задержки объединены и являются первым входом источника информации, выход блока выделения синхросигнала подключен к первому входу дешифратора снятия блокировки и второму входу дешифратора, выход которого соединен с первым входом блока задания режима блокировки, выход которого соединен с первым входом второго ключа и блока буферной памяти, а через блок стробирования с вторым входом первого ключа, выход которого подключен к первому входу формирователя маркерного импульса и первому входу элемента сравнения, выход которого соединен с вторым входом формирователя маркерного импульса, выход которого подключен к первому входу элемента ИЛИ, выход генератора тактовых импульсов соединен с вторым входом блока буферной памяти, первый выход которого подключен к третьему входу формирователя маркерного импульса, второму входу элемента сравнения и второму входу второго ключа, выход элемента задержки соединен с третьим входом второго ключа, выход которого подключен к второму входу элемента ИЛИ, выход элемента ИЛИ является выходом источника информации, второй выход блока буферной памяти соединен с третьим входом элемента ИЛИ, первый выход дешифратора снятия блокировки соединен с вторым входом блока задания режима блокировки, третий вход которого соединен с вторым выходом дешифратора снятия блокировки и третьим выходом блока буферной памяти, третий вход которого является вторым входом источника информации, при этом первый вход первого источника информации является первым входом системы, а первый вход каждого последующего источника информации соединен с выходом предыдущего, вторые входы источника информации являются информационными входами системы, причем выход последнего источника информации является выходом системы.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Система передачи информации | 1980 |

|

SU930334A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1995-06-27—Публикация

1993-01-11—Подача