Изобретение относится к электросвязи и может быть использовано при испытаниях телеграфных каналов и устройств, проверки исправляющей способности приемников дискретных сигналов.

Известно устройство для формирования испытательного текста, которое содержит задающий генератор, блок добавления и вычитания импульсов, делитель, два триггера, стартстопный распределитель, текстовой распределитель, первый и второй блоки памяти, два элемента И, два элемента ИЛИ, реле.

Недостатком данного устройства являются значительное количество аппаратных средств, ограничение функциональных возможностей по созданию различных видов и комбинаций искажений.

Известно также устройство для формирования испытательного текста, выбранное в качестве прототипа и содержащее задающий генератор, блок добавления и вычитания импульсов, делитель, два триггера, стартстопный и текстовой распределитель, два блока памяти, два элемента И, два элемента ИЛИ, реле и блок внесения искажений.

Недостатки данного устройства аппаратная сложность и ограниченные функциональные возможности, низкая надежность.

Изобретение решает задачу упрощения устройства и расширения его функциональных возможностей.

Поставленная задача достигается тем, что в устройство введены управляемый делитель, блок установки кода скорости, блок ввода, переключатель и блок установки данных, первый вход которого соединен с входом переключателя и с выходом управляемого делителя, первый вход которого соединен с выходом задающего генератора, а второй вход управляемого делителя соединен с выходом блока установки кода скорости, параллельный выход которого соединен с параллельным входом управляемого делителя, причем выход переключателя соединен с выходом блока установки данных и с входом блока памяти, параллельный вход которого соединен с параллельным выходом блока ввода, выход которого соединен с вторым входом блока установки данных, причем выход блока памяти является выходом устройства, при этом блок установки данных содержит RS-триггер, коммутатор и счетчик, вход которого соединен с выходом коммутатора и выходом блока, первый вход которого соединен с первым входом коммутатора, второй вход которого соединен с выходом RS-триггера, R-вход которого соединен с выходом счетчика, а S-вход RS-триггера с вторым входом блока.

Введение в заявляемое устройство новых блоков с соответствующими связями позволяет получить ему новые свойства, отличные от свойств прототипа и аналогичных устройств, а именно упрощение устройства и расширение его функциональных возможностей.

Расширение функциональных возможностей обеспечивается за счет возможности создания различных (любых) видов и комбинаций искажений.

Работа предлагаемого устройства (его сущность) основана на способе, включающем следующие операции.

1. Набор и запись каждой элементарной посылки исходного испытательного текста производится в q разрядов памяти, причем в разряды, соответствующие искаженным частям сигнала, записывают двоичные символы, значения которых противоположны значениям исходной элементарной посылки.

2. Вывод записанной в память последовательности двоичных символов производят синхронно со скоростью в q раз выше заданной скорости исходного испытательного текста.

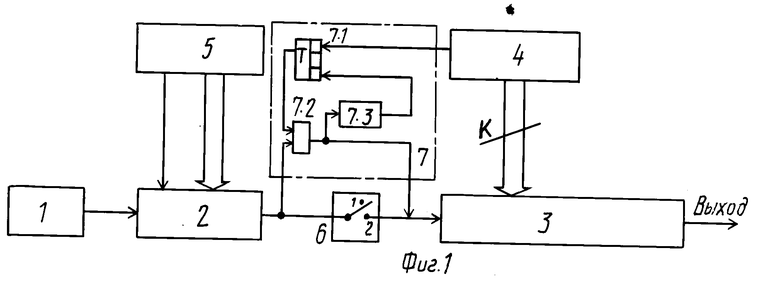

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 диаграмма, поясняющая работу предлагаемого устройства, на которой изображены: а исходный (неискаженный) испытательный текст с заданными частями, подлежащими искажению (искаженные части сигнала отмечены знаком И; б разряды регистра, заполненные элементарными двоичными сигналами, записанными в соответствии со способом; в последовательность выводимых двоичных символов; г искаженный испытательный текст; v скорость выводимой (искаженной) информации.

Устройство для формирования испытательного текста содержит задающий генератор 1, управляемый делитель 2, блок памяти 3, блок ввода 4 данных, блок 5 установки кода скорости, переключатель 6, блок 7 установки данных.

Выход задающего генератора 1 через управляемый делитель 2 соединен с входами блока 7 установки данных и переключателя 6, выход которого соединен с выходом блока 7 установки данных и входом блока 3 памяти, выход которого является выходом устройства. Выход блока 5 установки кода скорости соединен с вторым входом управляемого делителя 2, параллельный вход которого соединен с параллельным выходом блока 5. Параллельный вход блока 3 памяти соединен с параллельным выходом блока 4 ввода, выход которого соединен с вторым входом блока 7 установки данных.

Блок 7 установки данных содержит RS-триггер 7.1, выход которого соединен с первым входом коммутатора 7.2, второй вход которого является входом блока 7 и соединен с входом переключателя 6, а выход через счетчик 7.3 соединен с R-входом RS-триггера 7.1 и является выходом блока 7. S-вход RS-триггера 7.1 является другим входом блока 7 и соединен с выходом блока 4 ввода.

Блок 3 памяти представляет собой последовательный регистр сдвига, разрядность которого определяется требуемым объемом испытательного текста с обратной (внутренней) связью вход-выход регистра.

В качестве блока 4 может быть использована электронно-пишущая машинка (ЭПМ) с параллельным выводом данных.

В качестве блока 5 использован набор переключателей (тумблеров).

Устройство работает следующим образом.

После включения питания с помощью блока 5 устанавливается комбинация, которая определяет выход импульсов определенной (тактовой) частоты с делителя 2, что в конечном счете определяет (с учетом выбранного q) и скорость выводимого с устройства испытательного текста). Выход блока 5 является выходом синхроимпульса, который обеспечивает синхронную установку комбинации, выставленной на параллельном выходе блока 5.

При этом скорость выводимого испытательного текста с устройства определяется из следующего соотношения:

v  (cм. фиг.2), где v скорость выдачи испытательного текста с устройства;

(cм. фиг.2), где v скорость выдачи испытательного текста с устройства;

τ2 период тактовой частоты, которая устанавливается на выходе делителя 2 с помощью блока 5;

q количество разрядов, в которые записывается элементарная посылка каждого знака текста (с учетом необходимых искажений).

Импульсы установленной тактовой частоты с делителя 2 поступают на вход переключателя 6, который в исходном (не рабочем) состоянии разомкнут и не пропускает импульсы тактовой частоты на вход блока 3 памяти. Кроме того, импульсы с делителя 2 поступают на первый вход блока 7 установки данных.

С помощью блока 4 производится набор структуры испытательного текста в блок 3. При этом каждая элементарная посылка каждого знака испытательного текста должна быть представлена q разрядами и записана в q разрядов блока памяти 3, с учетом необходимых искажений в том или ином разряде блока из q разрядов.

Выход блока 4 является выходом синхроимпульсов и обеспечивает с помощью блока 7 синхронную установку и продвижение на К разрядов (где К является разрядностью параллельной шины данных от блока 4 к блоку 3) структуры элементарной посылки (или ее части) в блоке 3.

Блок 7 обеспечивает (для продвижения структуры элементарной посылки или ее части по последовательному регистру блока 3) выдачу К-импульсов. Синхроимпульс (СИ) с выхода блока 4 поступает вместе с К-параллельной структурой данных (комбинации элементарной посылки из q разрядов или части этих разрядов). СИ поступает на S-вход RS-триггера 7.1 и тем самым обеспечивает на выходе триггера 7.1 установку логич. "1", которая поступает на коммутатор 7.2 и открывает прохождение импульсов тактовой частоты на выход счетчика на К 7.3 и выход блока 7, а с него на сдвигающий вход блока памяти 3. Это обеспечивает сдвиг на К-разрядов структуры данных, записанных в первые К-разрядов блока 3. Продвижение структуры данных именно на К-разрадов определяется счетчиком 7.3. При поступлении на его вход К-ого импульса на его выходе появляется логич."1", которая поступает на R-вход RS-триггера 7.1 и обнуляет его. Логич."0" на выходе триггера 7.1 обеспечивает запрет прохождения импульсов тактовой частоты на сдвигающий (С-вход) последовательного регистра блока 3. При следующем вводе следующей части или целой структуры элементарной посылки с блока 4 в блок 3 и появлении очередного СИ на выходе блока 4 описанная работа блока 7 повторяется вновь.

Перед вводом данная структура испытательного текста должна быть предварительно подготовлена перед набором с блока ввода 4 с учетом требуемых искажений.

Если в качестве блока ввода 4 выбрана ЭПМ с 5-ти разрядным параллельным выходом данных (при существовании выхода СИ), а принято решение записать каждую элементарную посылку в разрядах, количество которых, например, определено равным 10, что соответствует 10% искажению элементарной посылки. В этом случае для ввода каждой элементарной посылки в блок памяти необходимо нажать 2 выбранные клавиши (буквы, цифры, регистры) на ЭПМ. Следовательно, для ввода одного знака в коде МТК-2, в каждом знаке которого содержится 5 элементарных посылок, необходимо нажать 10 соответствующих (возможно одной и той же клавиши по 10 раз) клавиш, а для ввода 5 знаков соответственно 50 и т.д.

После того как проведен ввод структуры испытательного текста в блок 3 замыкается переключатель 6 (переводится из 1-го во 2-е положение) и с делителя 2 начинают поступать импульсы установленной тактовой частоты в блок 3 и тем самым обеспечивают вывод структуры испытательного текста на выход устройства. По окончании вывода испытательного текста переключатель 6 переводится в положение 1.

Необходимо еще раз отметить, что если в качестве блока памяти используется последовательный регистр с обратной связью (выход-вход), то предварительный набор структуры испытательного текста делается один раз, которая для испытаний используется многократно.

Основное и существенное отличие данного устройства от прототипа это значительное сокращение аппаратных средств при расширении функциональных возможностей в части создания всех возможных комбинаций искажений (преобладаний, дроблений) и всех возможных структур испытательного текста.

Сокращение аппаратных средств обеспечивает и повышение надежности данных устройств.

Если в качестве блока ввода используется ЭВМ (микро-ЭВМ), то это значительно упрощает возможности ввода, автоматизирует процесс организации предварительной последовательности структур элементарных посылок и сокращает время ввода структуры испытательного текста в память устройства.

Использование: в электросвязи при испытаниях телеграфных каналов и устройств, проверки исправляющей способности приемников дискретных сигналов. Сущность изобретения: устройство содержит задающий генератор 1, делитель 2, блок 3 памяти, блок 4 ввода данных, блок 5 установки кода скорости, переключатель 6 и блок 7 установки данных. Устройство при сокращении аппаратных средств обеспечивает и повышает надежность. 2 ил.

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИСПЫТАТЕЛЬНОГО ТЕКСТА содержащее задающий генератор, блок памяти и делитель, отличающееся тем, что введены блок установки кода скорости, блок ввода данных, блок установки данных и переключатель, выход которого подключен к тактовому входу блока памяти, вход данных испытательного текста которого соединен с соответствующим выходом блока ввода данных, выход синхроимпульсов которого подключен к первому входу блока установки данных, второй вход которого соединен с выходом делителя, который выполнен управляемым, и входом переключателя, а выход подключен к тактовому входу блока памяти, управляемый вход делителя соединен с выходом синхроимпульсов блока установки кода скорости, информационные выходы которого подключены к информационным входам делителя, вход задания которого соединен с выходом задающего генератора, выход блока памяти является выходом устройства, кроме того, блок установки данных выполнен в виде последовательно соединенных коммутатора, выход которого является выходом блока, счетчика и RS-триггера, S-вход которого является первым входом блока, выход RS-триггера подключен к одному входу коммутатора, другой вход которого является вторым входом блока.

| Устройство для формирования испытательного текста | 1987 |

|

SU1464295A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-10-10—Публикация

1992-04-28—Подача