Изобретение относится к электросвязи и может использоваться для проверки исправляющей способности приемников дискретных сигналов.

Известно устройство для формирования испытательного текста, которое содержит задающий генератор, блок добавления и вычитания импульсов, делитель, два триггера, стартстопный и текстовой распределители, два блока памяти, два элемента И, два элемента ИЛИ, реле и блок внесения искажений. Недостатком этого устройства является сложность и ограниченные функциональные возможности.

Известно устройство для контроля исправляющей способности приемников дискретных сигналов, содержащее задающий генератор, делитель частоты, блок формирования управляющего сигнала, блок искажений, формирователь испытательных сигналов, формирователь сигналов дроблений, блок ввода дроблений, коммутатор, общую шину, приемопередатчик, дешифратор адресов, регистр управления, формирователь управляющего сигнала, регистр состояния, блок формирования синхросигналов, блок состояния.

Это устройство имеет значительное количество аппаратных средств и ограниченные функциональные возможности по созданию различных видов и комбинаций искажений, достаточно трудоемкую установку конкретных значений искажений сигналов информации.

Цель изобретения упрощение устройства за счет сокращения аппаратных средств и расширение функциональных возможностей, а именно создание различных видов и комбинаций искажений.

Для этого в устройство введен блок преобразования кода, первый вход которого соединен с выходом управляемого делителя, а выход соединен с вторым входом коммутатора, параллельный вход которого соединен с параллельными входами-выходами блока преобразования кода и параллельным входом управляемого делителя частоты, причем второй, третий, четвертый и пятый выходы дешифратора адресов соответственно соединены с третьим входом коммутатора, вторым и третьим входами блока преобразования кода и вторым входом управляемого делителя частоты.

Предложенное устройство обеспечивает значительное сокращение аппаратных средств за счет исключения формирователя испытательного сигнала, формирователя сигналов дроблений, блока ввода дроблений, регистров состояния и управления, блока формирования управляющего сигнала, блока искажений, блока формирования синхросигналов, блока состояния и введения в устройство блока преобразования кода.

В основе работы устройства лежит способ, заключающийся в следующем:

1. Набор и запись каждой элементарной посылки исходного испытательного текста производится в q разрядов памяти, причем в разряды, соответствующие искаженным частям сигнала, записывают двоичные символы, значения которых противоположны значениям исходной элементарной посылки.

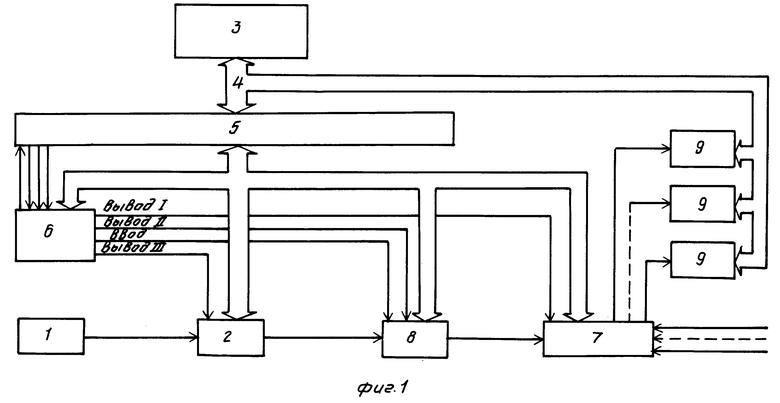

Вторые параллельные входы-выходы приемопередатчика 5 соединены с параллельными входами-выходами дешифратора адресов 6, делителя 2, блока 8 преобразования кода 8 и коммутатора 7.

Первый, второй и третий входы дешифратора адресов 6 соединены соответственно с первым, вторым и третьим выходами приемопередатчика 5, вход которого соединен с первым выходом дешифратора 6, второй третий, четвертый и пятый выходы которого соединены соответственно с вторым входом делителя 2, с вторым и третьим входами преобразователя кода 8, с третьим входом коммутатора 7, выходы которого являются выходами устройства.

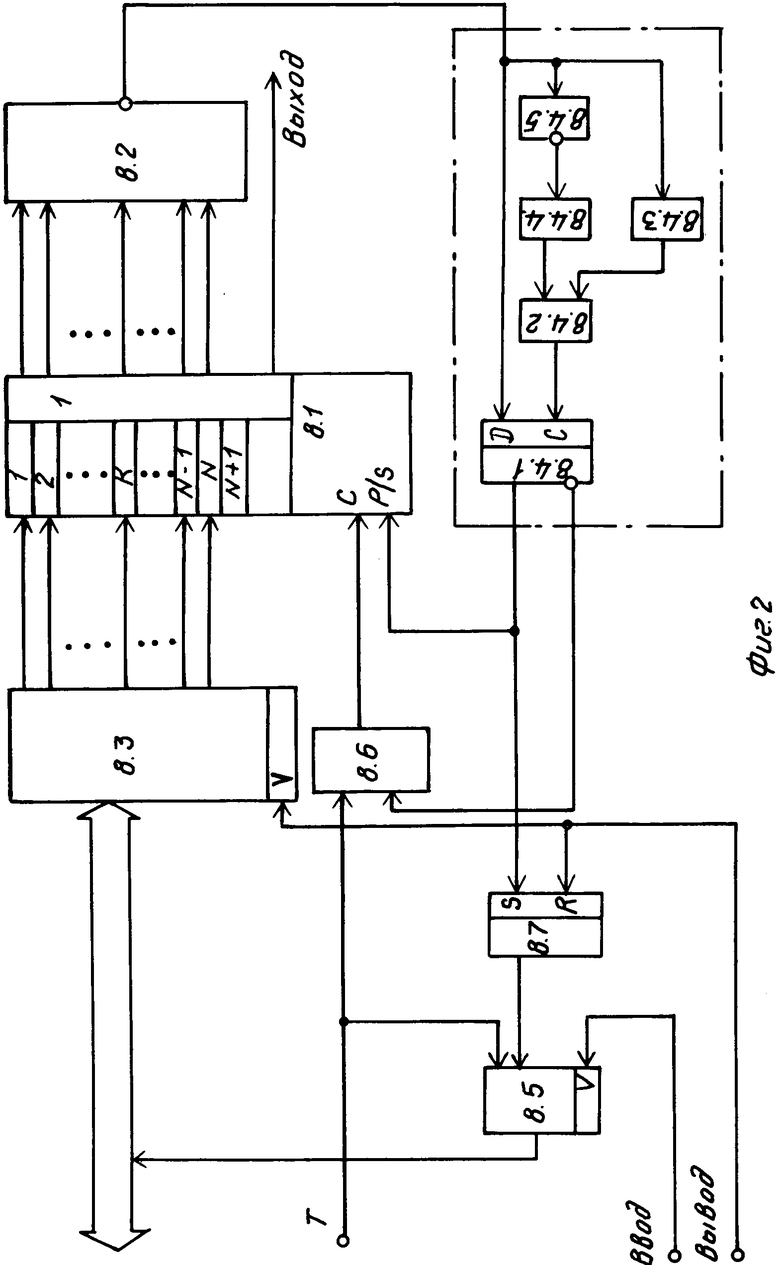

Преобразователь кода (см. фиг.2) содержит регистр сдвига 8.1, дешифратор нуля 8.2, входной регистр 8.3, блок импульсов управления 8.4, коммутатор 8.5, элемент И 8.6, RS-триггер 8.7.

Блок импульсов управления 8.4 содержит D-триггер 8.4.1, схему ИЛИ 8.4.2, первый и второй дифференцирующие элементы 8.4.3, 8.4.4 и инвертор 8.4.5.

Принцип работы устройства заключается в следующем.

Каждая элементарная посылка исходного испытательного текста (причем исходный испытательный текст для каждого приемника находится в определенной области памяти формирователя 3 управляющего сигнала) преобразуется (в соответствии с программой блока 3) в q разрядов памяти, соответствующих количеству разрядов блока 8 преобразователя кода, при этом в соответствии с программой в разряды, которые должны соответствовать искаженным частям сигнала, записывают двоичные символы, противоположные значениям исходной элементарной посылки. При этом q определяет степень точности величины искажений и количество разрядов, используемых в блоке 8 преобразователя кода.

2. Вывод записанной в память последовательности двоичных символов производят синхронно со скоростью в q раз выше заданной скорости исходного испытательного текста.

На фиг.1 приведена структурная схема предложенного устройства; на фиг.2 структурная схема преобразователя кода; на фиг.3 алгоритм работы устройства; на фиг.4 диаграмма, поясняющая работу устройства, где а исходный (неискаженный) испытательный текст с заданными частями, подлежащими искажению (искаженные части сигнала отмечены знаком "И"); б разряды регистра, заполненные элементарными двоичными сигналами, записанными в соответствии со способом; в последовательность выводимых двоичных символов; г искаженный сигнал (V скорость выводимой (искаженной) информации).

Устройство (см. фиг.1) содержит задающий генератор 1, управляемый делитель 2, формирователь 3 управляющего сигнала, общую шину 4, приемопередатчик 5, дешифратор адресов 6, коммутатор 7 и блок 8 преобразователя кода 8. На чертеже также показаны контролируемые приемники 9 дискретных сигналов.

Выход генератора 1 соединен с последовательно соединенными делителем 2, блоком 8 преобразования кода и коммутатором 7, входы которого являются входами устройства. Другие входы устройства соединены с параллельными входами-выходами формирователя 3 и приемопередатчика 5.

При этом вывод записанной в q разрядов блока преобразователя кода последовательности двоичных символов производят синхронно со скоростью в q раз выше заданной скорости исходного испытательного текста.

Следовательно, каждая элементарная посылка исходного испытательного текста (бит информации) записывается в q разрядах блока 8 преобразователя кода, а частота продвижения Т, поступающая с управляемого делителя 2 на блок 8, должна быть в q раз выше требуемой скорости выдачи информации.

В памяти ОЗУ блока 3 для каждого приемника имеется свой исходный испытательный текст (или он должен быть заранее набран введен в память). Для каждого приемника имеется своя программа преобразования каждой элементарной посылки (или может быть принят какой-то иной закон) исходного текста в q разрядов блока 8 с учетом необходимой скорости, которая определяется из соотношения

v  где Т частота, поступающая с делителя частоты в блок 8;

где Т частота, поступающая с делителя частоты в блок 8;

V скорость передачи в бит/c;

q количество разрядов регистра блока 8, которое выбирается исходя из необходимой (степени) точности искажений дискретных сигналов.

Одновременно с включением питания с задающего генератора 1 импульсы поступают на вход управляемого делителя 2, где формируются импульсы с частотой, которая требуется для достижения необходимой скорости передачи.

На управляющем входе делителя 2 в это время установлен нулевой код режима устройства, при котором импульсы не поступают на вход блока 8. При подаче на управляющий вход делителя 2 необходимого кода режима устройства импульсы заданной частоты начинают поступать на первый вход блока 8.

Установка необходимого режима устройства обеспечивается блоком 3, в качестве которого может быть использована микроЭВМ ("Электроника-60М или "Электроника-81Б" и т.д.). Код режима устройства выводится из памяти формирователя 2 в виде управляющего слова.

Блоки 2, 7 и 8 имеют свои адреса обращения. При обращении блока 3 к блоку 2 по шине данных, поступающей с блока 3 через шину 4 и блок 5, на параллельном входе блока 2 устанавливается комбинация, обеспечивающая при поступлении сигнала "Вывод Ш" требуемую частоту импульсов с периодом Т, которые поступают на вход блока 8.

При обращении блока 3 и блоку 7 с блока 3 через шину 4 и блок 5 поступают данные и на параллельном входе блока 7 устанавливается комбинация, обеспечивающая выбор требуемого контролируемого приемника.

Дешифратор 6 адресов обеспечивает дешифрацию трех адресов:

первого при обращении к блоку 2,

второго при обращении к блоку 7,

третьего при обращении к блоку 8.

Блок (формирователь) 3 работает в двух режимах: "Вывод", когда с блока 3 направляется информация в блоки 2, 7 и 8, и "Ввод", когда в блок 3 поступает информация (флаг) от блока 8 о возможности подачи части (порции) или всей структуры сигнала контрольной информации.

РЕЖИМ "ВЫВОД"

В режиме "Вывод" блок 3 через приемопередатчик 5 выставляет (по шине данных) адрес и сигналы управления, которые поступают соответственно на информационный вход и управляющий вход дешифратора 6. Дешифратор 6, распознав свой адрес, при наличии сигнала "Вывод" на управляющем входе дешифратора 6 устанавливает сигнал "Вывод" ("Вывод III") на первый вход управляемого делителя 2 (или коммутатора 7, или блока преобразования 8 в зависимости от того, какой адрес выбран блоком 3 при обращении). При этом блок 3 заканчивает адресную часть цикла "Вывод". Во второй (информационной) части цикла "Вывод" блок 3 устанавливает информацию (комбинацию сигналов для установки требуемой частоты в блоке 2, или комбинацию сигналов для установки требуемого для контроля приемника в блоке 7, или необходимую часть (порцию), или всю структуру сигнала контрольной информации), которая через приемопередатчик 5 поступает соответственно на информационные входы или управляемого делителя 2 или коммутатора 7 или блока преобразователя кода 8.

По сигналу "Вывод" ("вывод III" или "Вывод I", или "Вывод II") информация, установленная на информационном входе блока 2 (или блока 7, или блока 8), записывается в соответствующие регистры перечисленных блоков. После установки управляющей (или испытательной для блока 8) информации по сигналу "Вывод" от блока 3 дешифратор 6 формирует управляющий сигнал (СИП) и передает его через приемопередатчик 5 в блок 3 о завершении приема блока информации в блок 2 (или блок 7, или блок 8). Получив этот сигнал блок 3 снимает сигнал "Вывод", что обеспечивает окончание передачи блока информации.

РЕЖИМ "ВВОД"

В режиме "Ввод" блок 3 в первой части цикла осуществляет передачу третьего адреса (адреса блока 8). Во второй части формирует сигнал "Ввод", который через приемопередатчик 5 и дешифратор 6 поступает на вход управления блока 8. По этому сигналу значение состояния блока 8 (сообщение флаг о возможности установки следующей части (порции) или всей структуры испытательной информации) через приемопередатчик записывается в блок 3.

После приема флага блоком 3 по сигналу "Ввод" дешифратор 6 формирует управляющий сигнал (СИП) и передает его через приемопередатчик 5 в блок 3, сообщая о завершении передачи флага в блок 3. Получив этот сигнал блок 3 снимает сигнал "Ввод", завершая тем самым прием значения состояния (флага) блока 8.

Рассмотрим работу блока преобразователя кода 8. Входы "Ввод" (ВВОД) и "Вывод" (ВЫВОД II) блока преобразователя кода являются входами управления и подключаются к соответствующим выходам дешифратора адресов 6 ВВОД и ВЫВОД II. Кроме того, вход Т импульсов сдвига преобразователя кода 8 подключен к выходу управляемого делителя 2, а информационные параллельные входы выходы блока 8 соединены с вторыми параллельными входами-выходами приемопередатчика 5 и подключены к входному регистру 8.3 и коммутатору 8.5. блока 8.

Регистр сдвига 8.1 содержит вход сдвига С и вход переключения режимов P/S, последний обеспечивает переключение регистра 8.1 из режима сдвига в режим асинхронного параллельного ввода информации и параллельной асинхронной записи блока информации в регистр сдвига 8.1 (путем установки логич. 1 на вход P/S).

Входной регистр 8.3 содержит V вход для синхронизации (установки) записи. Управляющим входом коммутатора 8.5 является его вход V. Вход ВЫВОД (запись) блока преобразователя кода 8 соединен с входом регистра 8.3 и входом R RS-триггера 8.7. Вход ВВОД (чтение) блока 8 соединен с управляющим входом V коммутатора 8.5. Информационные параллельные входы-выхо- ды блока 8 соединены с N-входами регистра 8.3 и выходом коммутатора 8.5. Выходы регистра 8.3 соединены с первыми N-входами регистра сдвига 8.1, первые N выходов которого соединены с дешифратором нуля 8.2, выход которого соединен с входом блока импульсов управления 8.4. Первый (прямой) выход блока 8.4 соединен с Р/S входом регистра сдвига 8.1 и S-выходом RS-триггера 8.7, выход которого соединен с первым входом коммутатора 8.5, а второй (инвертируемый) выход блока 8.4 соединен с вторым входом элемента И 8.6. Вход импульсов сдвига Т соединен с первым входом элемента И 8.6, выход которого соединен с С-входом регистра 8.1.

Блок 8.4 содержит вход, который соединен с выходом дешифратора нуля 8.2, а в схеме блока 8.4 этот вход соединен с D-выходом D-триггера 8.4.1 и входами инвертора 8.4.5 и первого дифференцирующего элемента 8.4.3, выход которого соединен с первым входом схемы ИЛИ 8.4.2, второй вход которой соединен с выходом второго дифференцирующего элемента 8.4.4, вход которого соединен с выходом инвертора 8.4.5. Причем выход схемы 8.4.2 соединен с С-входом D-триггера 8.4.1, инвертируемый и прямой выходы которого являются выходами блока импульсов управления 8.4.

Блок 8 преобразователя кода 8 работает в трех режимах: записи; преобразования (продвижения) и чтения.

Кроме информации и сигналов "Вывод II" и "Ввод" от дешифратора 6, в блок преобразователя кода на вход Т поступают импульсы сдвига, определяющие скорость вывода последовательного кода.

Блок информации параллельного кода поступает в преобразователь в формате следующей структуры: разряд К формата содержит логич. "1", разряды младшие К заполнены логич. "0" (если К не является первым разрядом формата блока), а в разрядах старше К записываются (устанавливаются) биты информации, подлежащие преобразованию в последовательный код, причем старший разряд формата соответствует старшему разряду информации. Логич. "1" в разряде К определяет размер блока информации (количество разрядов в блоке).

РЕЖИМ (ОПЕРАЦИЯ) ЗАПИСИ

В исходном состоянии, когда на информационных входах-выходах отсутствует информация (или информация равна логич. "0"), причем в К-м разряде, определяющем размер блока, также присутствует логич. "0", регистр сдвига 8.1 находится в режиме параллельного ввода информации, на выходе блока преобразователя кода 8 логич. "0", а с помощью RS-триггера 8.7 устанавливается сигнал флаг логич. "1" РАЗРЕШЕНИЕ в N-м разряде информационных вводов-выходов, свидетельствующий о возможности проведения режима (операции) записи.

В исходном состоянии импульсы сдвига Т, поступающие на вход Т блока 8, не проникают на С-вход регистра 8.1, так как на втором входе схемы И 8.6 отсутствует логич. "1".

На выходе регистра 8.3 установлен блок информации, который был выдан последним в операции, предшествующей данной (вновь проводимой) операции.

Основным условием начала записи информации (кроме подачи импульсов сдвига Т) является появление логич. "1" в разряде К блока информации.

Появление блока информации (с логич. "1" в разряде К) на информационной шине и следующего за ним сигнала "Вывод" обеспечивает установку в регистр 8.3 блока информации по переднему фронту сигнала "Вывод", поступающему на V-вход регистра 8.3, причем RS-триггер 8.7 устанавливается в "0" состояние, а режим параллельного ввода блока информации в регистр сдвига 8.7 из регистра 8.3 обеспечивается наличием логич. "1" на P/S входе регистра 8.1, поступающей с прямого выхода блока 8.4.

Тем самым на N выходах регистра сдвига 8.1 появляется блок информации, в котором на К-входе (если разряды блока информации соответствуют логич. "0") появляется логич. "1", что приводит к появлению (в исходном состоянии на выходе дешифратора нуля 8.2 присутствовала логич. "1") на выходе дешифратора нуля 8.2 логич. "0", который устанавливается на входе инвертора 8.4.5 блока 8.4 и входе первого дифференцирующего элемента (ДЭ) 8.4.3, который обеспечивает выдачу "отрицательного" импульса соответствующего логич. "0". В то время, как на выходе инвертора 8.4.5 происходит изменение (перепад) от уровня логич. "0" до уровня логич. "1", второй ДЭ 8.4.4 производит выдачу "положительного" импульса, соответствующего переходу на выходе дешифратора нуля 8.2 от логич. "1" к логич. "0". Импульс с второго ДЭ 8.4.4 через схему ИЛИ 8.4.2 поступает на С-вход D-триггера 8.4.1 блока 8.4 и тем самым устанавливает на прямом выходе D-триггера 8.4.1 логич. "0", а на инвертируемом логич. "1". Тем самым регистр сдвига 8.1 (на P/S логич. "0") переводится в режим последовательного сдвига информации. Появление логич. "1" на втором входе схемы И 8.6 обеспечивает прохождение импульсов сдвига Т на С-вход регистра сдвига 8.1 для начала (организации) следующего режима (операции) преобразования параллельного кода в последовательный.

По очередному сигналу "Вывод" информационный блок, установленный на информационных входах-выходах формирователя управляющего сигнала 3, переписывается в регистр 8.3, и далее операция (режим) записи повторяется (конечно после выдачи информационного блока из 1-N разрядов регистра сдвига 8.1).

РЕЖИМ (ОПЕРАЦИЯ) ПРЕОБРАЗОВАНИЯ (ПРОДВИЖЕНИЯ)

После записи блока информации в регистр сдвига 8.1 и появления на инвертируемом выходе D-триггера 8.4.1 блока 8.4 логич. "1", обеспечивающей прохождение импульсов сдвига Т через схему И 8.6 на С-вход регистра 8.1 (на P/S входе регистра 8.1 установлен логич. "0", т.е. режим последовательного сдвига), начинается продвижение титов блока информации по регистру 8.1. После того, как логич. "1", установленная в К-разряде, переходит из N-го разряда в N+1 (и на выход преобразователя), дешифратор нуля 8.2 переходит из "0" состояния на выходе в "1"-е, тем самым на D-входе D-триггера 8.4.1 блока 8.4 появляется логич. "1", а первый ДЭ 8.4.3 обеспечивает выдачу импульса-сигнала логич. "1", который через схему ИЛИ 7.4.2 поступает на С-вход D-триггера 8.4.1 блока 8.4, тем самым устанавливая на прямом выходе D-триггера 8.4.1 блока 8.4 логич. "1", которая переводит регистр 8.1 в режим параллельного приема информации, тем самым прекращается поступление импульсов Т на С-вход регистра 8.1 и может быть вновь проведена операция (режим) записи, описанная выше.

При этом момент начала операции записи может быть определен блоком 3 с помощью сигнала "Ввод" при появлении логич. "1" в N-м разряде на информационных входах-выходах, т.е. появление сигнала флага "Разрешение". Тем самым блоком 3 может быть вновь установлен на информационных входах-выходах новый блок информации и по сигналу "Вывод" введен в регистр 8.3. Причем после введения данного блока информации сигнал флаг "Разрешение" будет снят сигналом "Вывод", поступающим от блока 6 на R вход RS-триггера 8.7. Тем самым подготавливаются условия для проведения режима (операции) чтения сигнала Разрешение и сигнала "Т" (импульсов сдвига), поступающих на вход коммутатора 8.5.

РЕЖИМ (ОПЕРАЦИЯ) ЧТЕНИЯ

Сигналы "Разрешение" и "Т", установленные на входах коммутатора 8.5 по сигналу "Ввод", поступающему на V-вход коммутатора 8.5, устанавливаются на коммутируемых выходах блока 8.5, подключенных к информационным входам-выходам блока 8.

Таким образом, эти сигналы устанавливаются (выставляются) на информационных входах-выходах и снимаются блоком 3 для последующей обработки.

Следовательно, установка очередного сигнала "Ввод" (для обеспечения получения блоком 3 перечисленных сигналов) производится при наличии логич. "1" сигнала "Разрешение". Только в этом случае блоком 3 может быть проведена операция (режим) записи в пределах времени от предыдущей установки блока информации в регистр 8.3 до выхода этого блока информации из разрядов 1.N регистра 8.1 в любой момент времени (по готовности программ блока 3). В этих же пределах времени может быть проведена и операция (режим) чтения (многократно).

После установки нулевого блока данных на информационных входах-выходах во все разряды (включая и К-разряд) блок 8 устанавливается в исходное состояние.

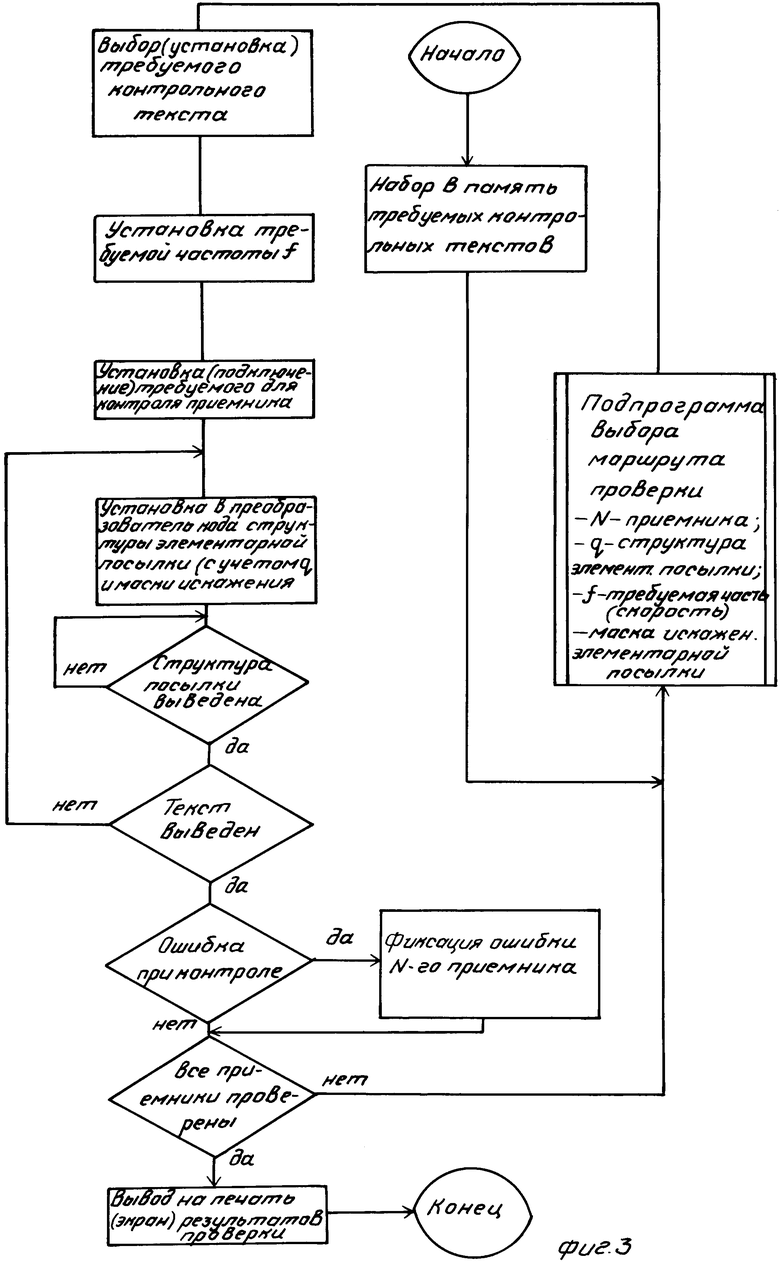

На фиг.3 представлен один из возможных алгоритмов взаимодействия блока 3 и блоков устройства.

Вначале производится набор в память блока 3 исходных требуемых контрольных текстов для каждого проверяемого приемника.

Далее в память блока 3 вводится подпрограмма "ВЫБОР МАРШРУТА ПРОВЕРКИ", которая определяет очередность проверки приемников (установка N-го приемника) и учитывает скорость выдачи (а для блоков 9 приема) испытательного сигнала (f требуемая частота и q структура элементарной посылки), характер искажений (маска искажения элементарной посылки).

Производится запуск программы блока 3 и последовательно начинается установка:

требуемого контрольного текста (программно),

требуемой частоты f (в блоке 2),

требуемого для контроля приемника (в блоке 7),

требуемой структуры элементарной посылки с учетом необходимого q и маски искажений элементарной посылки (в блоке 8).

Последняя операция производится многократно до тех пор пока не будет выведен весь контрольный текст для данного проверяемого приемника.

Как только структура элементарной посылки (с учетом q и маски искажений) установлена в блок 8, начинается ее вывод из блока 8 через коммутатор 7 в приемник 9, а также начинается оценка (программно) выведена ли структура элементарной посылки (т.е. появился сигнал флаг "Разрешение"). Если появился сигнал-флаг "Разрешение", программно производится оценка выведен ли весь текст для данного приемника 9. Если текст не выведен, вновь повторяется установка следующего блока структуры элементарной посылки, и так до тех пор, пока не будет выведен весь текст. Если весь текст выведен, программно производится оценка качества контроля данного приемника (так как блок 3 связан по шине 4 с приемниками 9 и получает от них такие сведения). Если обнаружена ошибка, она фиксируется в памяти блока 3 и далее (как и в случае отсутствия ошибки контроля) производится оценка все ли приемники 9 проверены. Если они проверены не все, то в соответствии с подпрограммой "ВЫБОР МАРШРУТА ПРОВЕРКИ" производится новый цикл проверки следующего приемника 9.

Если все приемники 9 проверены, производится вывод на печать (или экран дисплея) результатов проверки.

Блок 3 построен на основе микроЭВМ, в состав блока также входит устройство индикации и управления (дисплей). Остальные блоки построены на микросхемах 559, 533 и 564 серий.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИСПЫТАТЕЛЬНОГО ТЕКСТА | 1992 |

|

RU2045816C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1993 |

|

RU2038634C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ЦИФРОВЫХ СИГНАЛОВ | 1991 |

|

RU2020764C1 |

| УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ ИСТОЧНИКА ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2020560C1 |

| УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ ИСТОЧНИКА ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2020561C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1989 |

|

SU1755286A2 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Использование: электросвязь, а именно при испытаниях телеграфных каналов и устройств проверки исправляющей способности приемников дискретных сигналов. Сущность изобретения: устройство для контроля исправляющей способности приемников дискретных сигналов содержит задающий генератор 1, управляемый делитель 2, формирователь 3 управляющих сигналов, общую шину 4, приемопередатчик 5, дешифратор адреса 6, коммутатор 7 и блок 8 преобразования кода. Устройство позволяет сократить аппаратные средства за счет исключения ряда блоков и введение блока преобразования кода. Показаны контролируемые объекты 9, 3-5-2-8-7-9, 3-5-6-2, 1-2, 6-8, 5-8, 5-7, 3-9, 6-5. 4 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ, содержащее последовательно соединенные формирователь управляющих сигналов и приемопередатчик, три информационных выхода которых подключены к соответствующим входам дешифратора адреса, первый выход которого подключен к информационному входу приемопередатчика, управляющие входы-выходы формирователя управляющих сигналов являются управляющими входами-выходами объектов контроля, коммутатор, последовательно соединенные задающий генератор и управляемый делитель, управляющие входы-выходы которого объединены с управляющими входами-выходами коммутатора, дешифратора адреса и приемопередатчика через шину обмена, первые входы коммутатора являются входами устройства, а выходы информационными входами контролируемых объектов, отличающееся тем, что в него введен блок преобразования кода, управляемые входы-выходы которого соединены с соответствующими выходами-входами приемопередатчика, выход управляемого делителя подключен к первому входу блока преобразования кода, выход которого подключен к второму входу коммутатора, третий вход которого соединен с выходом сигнала "Режим вывод I" дешифратора адреса, выход сигнала "Режим вывод II" которого подключен к второму входу блока преобразования кода, третий вход которого соединен с выходом сигнала "Режим ввод" дешифратора адреса, выход сигнала "Режим вывод III" которого подключен к второму входу управляемого делителя, при этом блок преобразования кода выполнен в виде элемента И и последовательно соединенных входного регистра, параллельные входы-выходы которого являются управляющими входами-выходами и блока регистра сдвига, дешифратора нуля, блока импульсов управления, RS-триггера и коммутатора, выход которого подключен к управляющим входам-выходам блока, S-вход RS-триггера объединен с P/S-входом регистра сдвига, C-вход которого соединен с выходом элемента И, R-вход RS-триггера объединен с V-входом входного регистра и является входом сигнала "Режим вывод II" блока, инвертирующий выход блока импульсов управления подключен к первому входу элемента И, второй вход которого объединен с вторым входом коммутатора и является первым входом блока, третий вход коммутатора является входом сигнала "Режим ввод" блока, выходом которого являются соответствующий выход регистра сдвига, кроме того, блок импульсов управления блока преобразования кода выполнен в виде последовательно соединенных инвертора, первого дифференцирующего элемента, элемента ИЛИ, второй вход которого соединен с выходом второго дифференцирующего элемента, и D-триггера, выходы которого являются выходом блока, D-вход входом блока импульсов управления и объединен с входами инвертора и второго дифференцирующего элемента.

| Устройство для контроля исправляющей способности приемников дискретных сигналов | 1987 |

|

SU1499518A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-07-20—Публикация

1992-04-29—Подача