Изобретение относится к электросвязи и может быть использовано в высокоскоростных модемах для кодирования информационных сигналов сверточным кодом.

Известно устройство для сверточного кодирования, содержащее регистр сдвига, первый сумматор, второй сумматор и переключатель [1]

Известно устройство для формирования сверточно-кодированных сигналов, содержащее три линии задержки, два сумматора и блок выбора сигнальной точки [2]

Недостатками известных устройств являются низкая помехоустойчивость генерируемых сверточно-кодированных последовательностей при невысоких отношениях сигнал/шум ( ≅ 20 дБ), а также их чувствительность к скачкам фазы несущего колебания, равным n π/2, где n 1,2,3, при наличии которых в канале связи становится невозможным правильное декодирование принимаемой последовательности.

Наиболее близким к изобретению по технической сущности является устройство для кодирования сверточным кодом, выходные сигналы которого нечувствительны к скачкам фазы несущего колебания в канале связи, кратным 90о [3] содержащее первый блок постоянной памяти, первый и второй выход которого через первую и вторую линии задержки подсоединены соответственно к третьему и четвертому входам первого блока постоянной памяти, последовательно соединенные третью линию задержки, первый сумматор, второй сумматор, четвертую линию задержки, третий сумматор, четвертый сумматор, пятую линию задержки, второй блок постоянной памяти, а также пятый сумматор, первый умножитель и второй умножитель, при этом выход пятого сумматора соединен с вторым входом первого сумматора, входами пятого сумматора являются первый и второй выходы первого блока постоянной памяти, а выход пятой линии задержки является объединенным первым входом третьей линии задержки, первого умножителя и второго умножителя, вторыми входами первого умножителя и второго умножителя являются соответственно выход третьего сумматора и второй выход первого блока постоянной памяти, выходы первого умножителя и второго умножителя подсоединены соответственно к вторым входам второго и четвертого сумматоров, первый выход первого блока постоянной памяти является вторым входом третьего сумматора и третьим входом второго блока постоянной памяти, четвертый вход которого соединен с вторым выходом первого блока постоянной памяти, причем первые и вторые входы первого и второго блоков постоянной памяти являются информационными входами, а выходы второго блока постоянной памяти являются выходами устройства.

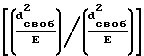

Устройство формирует сигналы, закодированные сверточным кодом, которые позволяют передавать 4 информационных бита (m 4), за один интервал модуляции. Применяемый для сверточного кодирования код со скоростью R  /

/ +1 2/3 обеспечивает асимптотический энергетический выигрыш от кодирования (АЭВК) 4 дБ по сравнению с некодированной передачей методом квадратурно-амплитудной модуляции КАМ-16. АЭВК обусловлен величиной свободного расстояния (минимальное евклидово расстояние) между двумя любыми передаваемыми сверточно-кодированными последовательностями сигналов, равной

+1 2/3 обеспечивает асимптотический энергетический выигрыш от кодирования (АЭВК) 4 дБ по сравнению с некодированной передачей методом квадратурно-амплитудной модуляции КАМ-16. АЭВК обусловлен величиной свободного расстояния (минимальное евклидово расстояние) между двумя любыми передаваемыми сверточно-кодированными последовательностями сигналов, равной  . Сигналы, закодированные сверточным кодом, являются нечувствительными к скачкам фазы несущего колебания в канале связи, кратным 90о. Это достигается за счет выполненного определенным образом [3] назначения подмножеств сигнальных точек, полученных в результате разбиения [1,4] исходного ансамбля сигналов, переходам графа состояний, соответствующего назначения бит сигнальным точкам ансамбля сигналов и применения операции дифференциального кодирования.

. Сигналы, закодированные сверточным кодом, являются нечувствительными к скачкам фазы несущего колебания в канале связи, кратным 90о. Это достигается за счет выполненного определенным образом [3] назначения подмножеств сигнальных точек, полученных в результате разбиения [1,4] исходного ансамбля сигналов, переходам графа состояний, соответствующего назначения бит сигнальным точкам ансамбля сигналов и применения операции дифференциального кодирования.

Для декодирования последовательности сигналов, закодированных сверточным кодом, на приеме используется декодер максимального правдоподобия с мягким решением [5,6] Решающее правило такого декодера можно сформулировать следующим образом. В качестве решения принимается такая информационная последовательность } которая дала бы на выходе второго блока постоянной памяти последовательность сигналов

} которая дала бы на выходе второго блока постоянной памяти последовательность сигналов } наиболее близкую к принимаемой

} наиболее близкую к принимаемой } по евклидовому расстоянию

} по евклидовому расстоянию -

- min

min ,

,

при этом }∈c

}∈c где С совокупность всех возможных последовательностей на выходе второго блока постоянной памяти. Характеристики "мягкого" декодирования зависят от свободного расстояния

где С совокупность всех возможных последовательностей на выходе второго блока постоянной памяти. Характеристики "мягкого" декодирования зависят от свободного расстояния

dсвоб= min ,

,

при этомSn} ≠Pn} Sn}Pn} ∈c.

Предположим, что сигнальные последовательностиSn} иPn} с минимальным евклидовым расстоянием между ними dсвоб порождаются соответственно двоичными последовательностямиan} иan'} Тогда вероятность того, что вместо переданной последовательностиan} будет декодирована последовательностьan'} определяется как

Pr({  }Pn}

}Pn} {Sn}) Pr({

{Sn}) Pr({ }a

}a }

} {an}) Q(d

{an}) Q(d 2σ), где Q интеграл вероятностей;

2σ), где Q интеграл вероятностей;

σ среднеквадратическое отклонение шума.

При отношении сигнал/шум, стремящемуся к бесконечности, вероятностью того, что в качестве решения будет принята последовательностьSn'} расположенная на расстоянии большем, чем dсвобот действительно переданной последовательностиSn} можно пренебречь по сравнению с вероятностью того, что в качестве решения будет принята последовательность на расстоянии dсвоб отSn} Поэтому

P N(dсвоб)·Q(dсвоб/2σ), (1) где N(dсвоб) число ошибочных последовательностей, находящихся на расстоянии dсвоб от действительно переданной последовательностиSn} которое зависит от структуры графа переходов [4]

N(dсвоб)·Q(dсвоб/2σ), (1) где N(dсвоб) число ошибочных последовательностей, находящихся на расстоянии dсвоб от действительно переданной последовательностиSn} которое зависит от структуры графа переходов [4]

Как видно из (1), определяющее влияние на помехозащищенность сверточно-кодированной последовательности сигналов оказывает свободное расстояние dсвоб. АЭВК, обусловленный величиной свободного расстояния, составляет 4 дБ. Однако в каналах с аддитивным белым гауссовым шумом (АБГШ) при скачках фазы несущего колебания, кратных 90о, выигрыш от кодирования значительно снижается при малых и средних отношениях сигнал/шум (15-18 дБ). Так, например, при вероятности ошибки Рош 10-4выигрыш от кодирования составляет около 2,5 дБ.

Таким образом, кодированная сверточным кодом последовательность сигналов, формируемая устройством-прототипом, обладает невысокой помехозащищенностью, обусловленной величиной свободного расстояния.

Целью изобретения является повышение помехозащищенности формируемой устройством последовательности сигналов, а следовательно, и энергетического выигрыша от кодирования в каналах со скачками фазы несущего колебания, кратными 90о, при малых и средних отношениях сигнал/шум (с/ш).

Цель достигается тем, что устройство для кодирования сверточным кодом, содержащее первый блок постоянной памяти, первый и второй входы которого являются одноименными информационными входами устройства, первый выход первого блока постоянной памяти соединен через первый элемент задержки с третьим входом первого блока постоянной памяти и непосредственно с первыми входами первого и второго сумматоров и второго блока постоянной памяти, второй выход первого блока постоянной памяти соединен через второй элемент задержки с четвертым входом первого блока постоянной памяти и непосредственно с вторыми входами первого сумматора и второго блока постоянной памяти, третий и четвертый входы и выходы которого являются соответственно одноименными информационными входами и выходами устройства, выход второго сумматора соединен с первым входом первого умножителя, выход которого соединен с первым входом третьего сумматора, четвертый сумматор, выход которого через третий элемент задержки соединен с вторым входом первого умножителя и первым входом второго умножителя, четвертый элемент задержки, выход которого соединен с первым входом пятого сумматора, и пятый элемент задержки, снабжено дополнительными инверторами, шестым сумматором и шестым элементом задержки, выход первого сумматора соединен с вторым входом третьего сумматора, выход которого соединен с вторым входом пятого сумматора, выход которого через последовательно соединенные пятый элемент задержки и первый инвертор соединен с вторым входом второго сумматора и первым входом четвертого сумматора, входы второго инвертора и шестого элемента задержки подключены к выходу третьего элемента задержки, выход шестого элемента задержки соединен с входом четвертого элемента задержки, выход второго инвертора соединен с пятым входом второго блока постоянной памяти, вход третьего инвертора подключен к второму выходу первого блока постоянной памяти, выход соединен с вторым входом второго умножителя, выход которого соединен с первым входом шестого сумматора, второй вход которого подключен к первому выходу первого блока постоянной памяти, выход соединен с вторым входом четвертого сумматора.

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается наличием новых блоков: инверторов, шестой линии задержки, шестого сумматора и их связями с остальными элементами схемы.

Таким образом, предлагаемое устройство соответствует критерию "новизна".

Сравнение предлагаемого решения с другими техническими решениями показывает, что инверторы, линия задержки и сумматор широко известны [7]

Однако при их введении в указанной связи с остальными элементами схемы в предлагаемое устройство для кодирования сверточным кодом достигается повышение помехозащищенности сигналов, формируемых устройством, в каналах со скачками фазы несущего колебания, кратными 90о, путем реализации большего свободного расстояния между любыми двумя кодированными последовательностями сигналов по сравнению с прототипом. Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

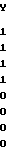

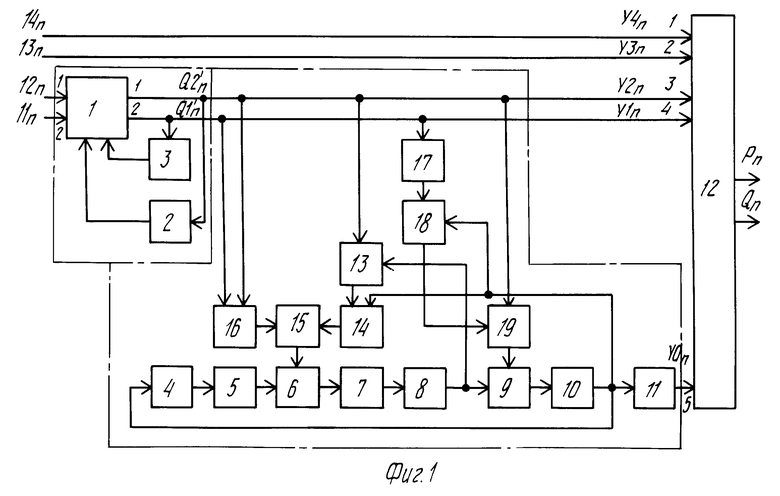

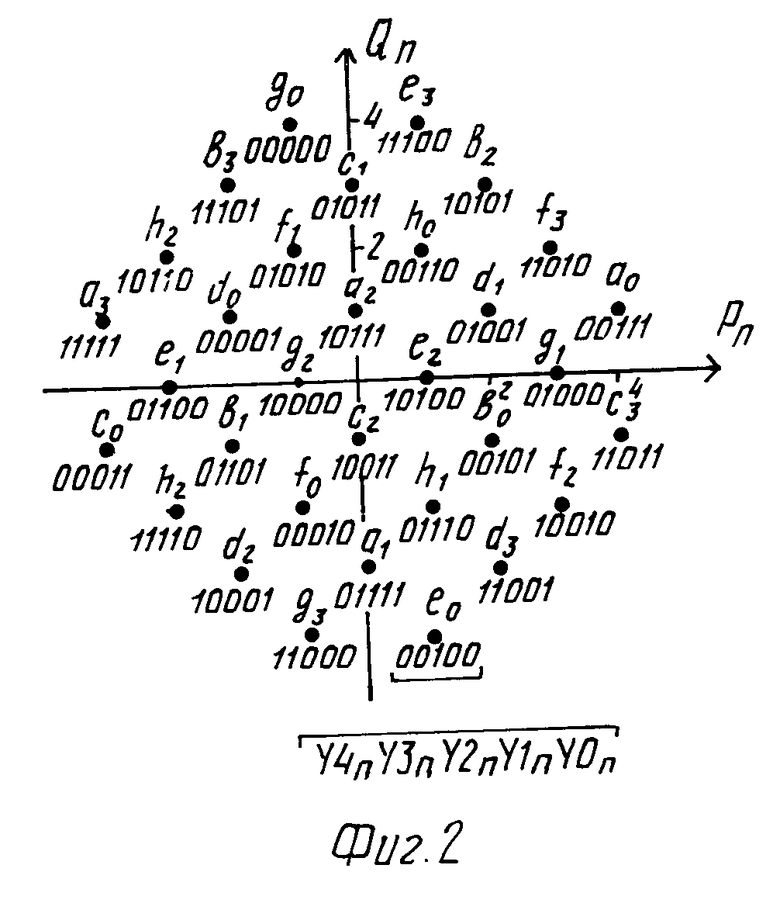

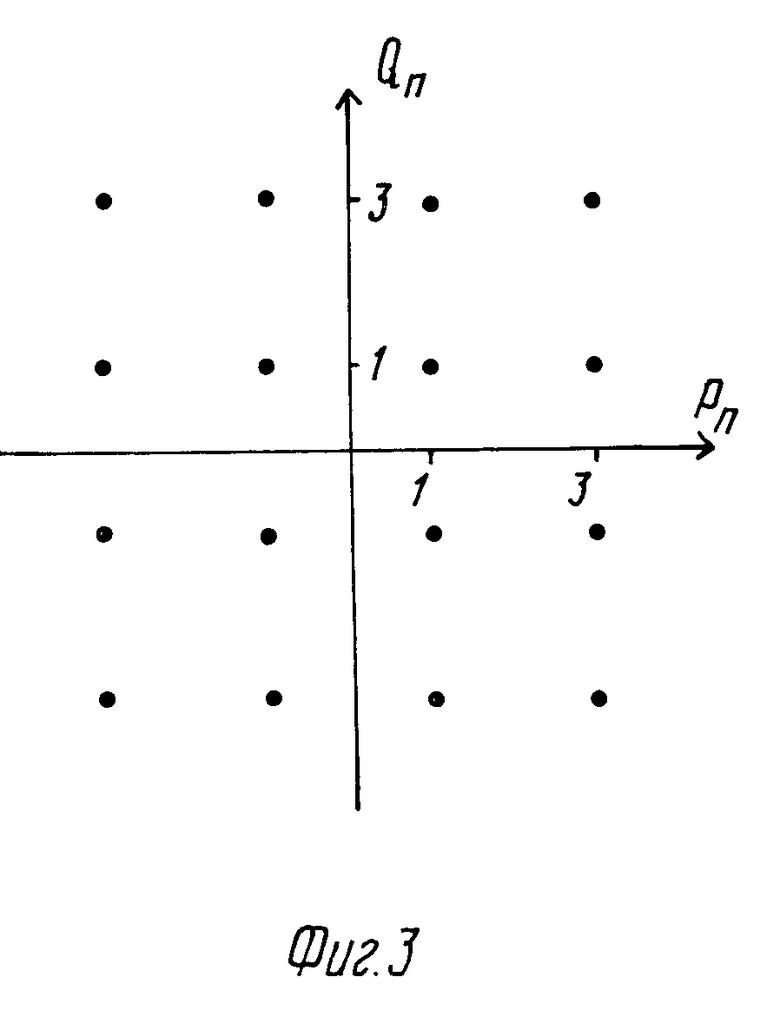

На фиг.1 представлена структурная электрическая схема устройства для кодирования сверточным кодом; на фиг.2 и 3 тридцатидвух- и шестнадцатиточечные ансамбли сигналов; на фиг.4 граф переходов сверточного кодера.

Устройство для кодирования сверточным кодом содержит первый блок 1 постоянной памяти, первую линию 2 задержки, вторую линию 3 задержки, представляющие собой дифференциальный кодер, последовательно соединенные шестую линию 4 задержки, четвертую линию 5 задержки, пятый сумматор 6, пятую линию 7 задержки, первый инвертор 8, четвертый сумматор 9, третью линию 10 задержки, второй инвертор 11, второй блок 12 постоянной памяти и последовательно соединенные второй сумматор 13, первый умножитель 14, третий сумматор 15, а также первый сумматор 16 и последовательно соединенные третий инвертор 17, второй умножитель 18 и шестой сумматор 19.

Устройство работает следующим образом.

На информационные входы устройства в момент времени n поступают информационные биты I1n, I2n, I3n, I4n (m 4). Два бита I4n, I3nпоступают прямо на четвертый и третий входы второго блока постоянной памяти и обозначаются как Y4n и Y3n, а биты I2n и I1n подаются на первый и второй входы дифференциального кодера.

В таблице представлены данные, описывающие работу дифференциального кодера.

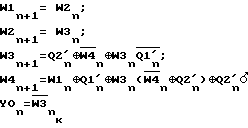

Применение операции дифференциального кодирования позволяет сделать формируемую устройством последовательность сигналов, кодированную сверточным кодом, нечувствительной к скачкам фазы несущего колебания, кратным 90о. Возможность применения дифференциального кодирования обеспечивается специфическим назначением бит Y4n, Y3n, Y2n, Y1n, Y0nсигнальным точкам ансамбля сигналов. С выхода дифференциального кодера биты Q2n'Q1n' поступают на сверточный кодер, содержащий последовательно соединенные шестую линию 4 задержки, четвертую линию 5 задержки, пятый сумматор 6, пятую линию 7 задержки, первый инвертор 8, четвертый сумматор 9, третью линию 10 задержки, второй инвертор 11 и последовательно соединенные второй сумматор 13, первый умножитель 14, третий сумматор 15, а также первый сумматор 16 и последовательно соединенные третий инвертор 17, второй умножитель 18 и шестой сумматор 19. Работу сверточного кодера описывают следующие логические функциональные зависимости

⊕ сумма по mod 2.

Они связывают последующее состояние W1n+1, W2n+1, W3n+1, W4n+1 и выходной бит Y0n кодера с текущим состоянием W1nW2nW3nW4n и входными битами кодера Q2n'Q1n'. Данные выражения получены путем минимизации с помощью диаграмм Вейча полных функциональных зависимостей, обусловленных графом переходов и назначением бит YIn, I 0,1.4 сигнальным точкам ансамбля сигналов. Граф переходов (фиг. 4) отображает работу сверточного кодера как конечного автомата с памятью.

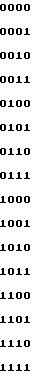

Каждому переходу, выходящему из одного состояния и ведущему в последующее, назначается определенная совокупность сигнальных точек из ансамбля сигналов, называемая подмножеством. Получение этих подмножеств основано на идее отображения путем разбиения множества [1,2,4] При этом проводится последовательное разбиение исходного расширенного сигнального множества (алфавита сигналов) на вложенные подмножества, причем расстояние между элементами подмножества (сигнальными точками) на каждом шаге разбиения возрастает, а число элементов в нем убывает. В качестве исходного расширенного сигнального множества применяется тридцатидвухточечное крестообразное созвездие (32-CR) (фиг.2). Оно является расширенным, поскольку для передачи m 4 некодированных информационных бит по каналу за интервал модуляции методом квадратурно-амплитудной модуляции (КАМ) было бы достаточно иметь ансамбль сигналов, состоящий из 16 точек (16-QA) (фиг.3). Применение сверточного кодирования к входным информационным битам Q2n'Q1n'(m=2) ведет к появлению дополнительного избыточного пятого бита Y0n. Поэтому ансамбль сигналов должен иметь M 2m+1 32 точки. В данном случае применяется ансамбль сигналов 32-CR, обладающий 90-градусной симметричностью, что является необходимым условием для обеспечения нечувствительности формируемой устройством последовательности сигналов, кодированных сверточным кодом, к скачкам фазы, кратным 90о.

Использование подхода, основанного на разбиении исходного сигнального множества на вложенные подмножества, ведет к разбиению исходного тридцатидвухточечного сигнального множества на 2 = 8(

= 8( 2 число входных бит сверточного кодера) вложенных подмножеств А, В, С, D, E, F, G, H (фиг.2).

2 число входных бит сверточного кодера) вложенных подмножеств А, В, С, D, E, F, G, H (фиг.2).

Разбиение проводится в ( +1) 3 шага. На первом шаге разбиения получается два подмножества (фиг.2) A∪B∪C∪D и E∪F∪G∪ H (U знак объединения) с минимальным евклидовым расстоянием Δ1=

+1) 3 шага. На первом шаге разбиения получается два подмножества (фиг.2) A∪B∪C∪D и E∪F∪G∪ H (U знак объединения) с минимальным евклидовым расстоянием Δ1=  =2 где Δo- минимальное евклидово расстояние для исходного сигнального множества Δo=

=2 где Δo- минимальное евклидово расстояние для исходного сигнального множества Δo=  .

.

На втором шаге разбиения получаются подмножества A U B, C U D, E U F, G U H Δ2=  Δ1= 2

Δ1= 2 . На последнем шаге разбиения имеем восемь подмножеств A, B, C, D, E, F, G, H с Δ3=

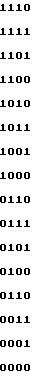

. На последнем шаге разбиения имеем восемь подмножеств A, B, C, D, E, F, G, H с Δ3=  Δ2= 4. При вращении сигнального множества по часовой стрелке на 90о подмножества A, B, C, D, E, F, G, H переходят соответственно в подмножества E, F, G, H, C, D, A, B. При вращении на 180о подмножества A, B, C, D, E, F, G, H переходят соответственно в C, D, A, B, G, H, E, F, а при 270о в G, H, E, F, A, B, C, D. Построение графа переходов базировалось на следующих правилах [3, 4]

Δ2= 4. При вращении сигнального множества по часовой стрелке на 90о подмножества A, B, C, D, E, F, G, H переходят соответственно в подмножества E, F, G, H, C, D, A, B. При вращении на 180о подмножества A, B, C, D, E, F, G, H переходят соответственно в C, D, A, B, G, H, E, F, а при 270о в G, H, E, F, A, B, C, D. Построение графа переходов базировалось на следующих правилах [3, 4]

а) граф переходов должен быть симметричен и все переходы в нем должны выполняться с одинаковой частотой;

б) переходам, начинающимся в одном состоянии и ведущим в различные состояния, необходимо ставить в соответствие сигналы одного из подмножеств, полученных на первом шаге разбиения;

в) сигналы из этих же подмножеств назначаются переходам, выходящим из различных состояний и ведущих в одно и то же состояние;

г) если обозначить q состояний кодера через i 0,1,q-1, то для того, чтобы кодер, и как результат, последовательность сигналов, были прозрачны к фазовой неопределенности в канале вязи, кратной 90о, должны существовать функции однозначного соответствия fl:0,1,q-1} _→0,1,q-1} l 1, 2, 3 такие, что выполняется следующее утверждение. Для каждого перехода из состояния i в состояние j, i, j ∈0,1,q-1} обозначим через ХО группу сигнальных элементов одного из полученных в результате разбиения подмножества, а через Х1, Х2 и Х3 группы сигнальных элементов, полученные из ХО посредством вращения по часовой стрелке соответственно на 90, 180 и 270о. Тогда каждому переходу из состояния fl(i) в состояние fl(j), l 1, 2, 3 назначается группа сигнальных элементов Xl, l 1, 2, 3 соответственно.

Граф переходов представлен на фиг.4. Функции однозначного соответствия имеют вид

f1:

f2:

f2:

f3:

f3:

Для графа переходов (фиг. 4) квадрат свободного расстояния равен 12. Действительно, если по каналу передается последовательность сигнальных точек, принадлежащих, например, подмножеству А (нулевое состояние), то ближайшей к ней будет последовательность из сигнальных точек, принадлежащих подмножествам B-D (рассматривается решетчатая диаграмма, получающаяся при развертке графа переходов во времени). С учетом минимального расстояния между точками подмножеств А и В, А и D ( ΔAB= 2 , ΔAB=2 фиг.2) квадрат свободного расстояния между рассматриваемыми последовательностями будет равен dсвоб2 ΔAB2+ΔAD2 12. Если за правильную последовательность выбрать любую другую, то также найдется последовательность, отстоящая от нее на расстоянии

, ΔAB=2 фиг.2) квадрат свободного расстояния между рассматриваемыми последовательностями будет равен dсвоб2 ΔAB2+ΔAD2 12. Если за правильную последовательность выбрать любую другую, то также найдется последовательность, отстоящая от нее на расстоянии  .

.

Свободное расстояние позволяет оценить АЭВК по сравнению с некодированной передачей методом КАМ-16. Тогда, с учетом нормировки по средней мощности, для АЭВК имеем [2, 4]

Gc= 10lg 10lg

10lg 4,7712∂Б.

4,7712∂Б.

С выхода сверточного кодера выходные биты, обозначенные как Y0n, Y1n, Y2n, поступают соответственно на 5, 2 и 1 входы второго блока постоянной памяти, на 3 и 4 входы которого подаются некодированные информационные биты, обозначенные через Y3n и Y4n. В соответствии с входной последовательностью бит YIn, I 0,1. 4 в блоке осуществляется выбор для передачи по каналу одной из точек алфавита сигналов (фиг.2).

Для обеспечения нечувствительности сигнальных элементов ансамбля сигналов к скачкам фазы несущего колебания, кратным 90о, назначение бит YIn, I 0,1.4 сигнальным элементам выполнено с соблюдением следующих правил (фиг.2):

1. Сигнальным элементам в каждом из 2m+1 23 8 подмножеств A, B, C, D, E, F, G, H назначаются одни и те же значения бит Y2n, Y1n, Y0n.

2. Группа, состоящая из бит Y2n, Y1n, соответствующих множествам сигнальных элементов, назначенных переходам, выходящим из одного и того же состояния графа переходов, содержит все возможные комбинации бит Y2nY1n.

3. Kаждому из четырех cигнальных элементов группы, у которой каждый поcледующий элемент может быть получен из предыдущего путем вращения по чаcовой cтрелке на 90о, назначаютcя различные значения битовой пары Y2nY1n;

4. Назначение некодированных информационных бит Y4nY3n сигнальным элементам ансамбля сигналов может производиться произвольно. В данном случае сигнальным элементам группы, состоящей из четырех элементов, получаемых из первого путем вращения на 90, 180 и 270о по часовой стрелке соответственно назначаются одинаковые биты Y4n, Y3n. Применяется следующее назначение бит Y2n, Y1n, Y0n, удовлетворяющее первым трем пунктам вышеизложенных правил:

Подмножеств :

:  2n

2n 1n

1n On

On

Для работы дифференциального кодера используется последовательность 11, 10, 01, 00, состоящая из различных битовых пар Y2nY1n и назначаемая согласно третьего пункта вышеизложенных правил последовательности сигнальных элементов группы, у которой каждый последующий элемент может быть получен из предыдущего путем вращения по часовой стрелке на 90о.

В соответствии с входными битами YIn, I 0,1.4 во втором блоке 12 постоянной памяти однозначно определяется сигнальная точка и на выходы блока 12 поступают сигналы Qn и Pn, соответствующие координатам синфазной и квадратурной составляющих сигнальной точки.

Втоpой блок 12 постоянной памяти представляет собой постоянное запоминающее устройство (ПЗУ), хранящее значения сигнальных элементов. Входные биты YIn, I= 0,1.4 для блока 12 образуют код адреса сигнального элемента в ПЗУ. Примеры реализации блока 12 представлены на рис. 5.17, 18, с.182, 183 [7]

Результаты моделирования предлагаемого устройства для кодирования сверточным кодом показали, что по сравнению с прототипом в каналах с аддитивным белым гауссовым шумом при скачках фазы несущего колебания, кратных 90о, при малых и средних отношениях с/ш (15-18 дБ) оно обеспечивает значительное повышение помехозащищенности формируемой последовательности сигналов за счет увеличения свободного расстояния между сигнальными последовательностями. Так, например, кодовый выигрыш по сравнению с некодированной передачей (КАМ-16) в канале с АБГШ, фазовой неоднозначностью, кратной 90о, и скоростью передачи информации 9600 бит/с составляет порядка 3,6 дБ при Рош 10-4, что примерно на 1,1 дБ больше кодового выигрыша, обеспечиваемого устройством-прототипом в тех же условиях.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СВЕРТОЧНЫМ КОДОМ | 1991 |

|

RU2038696C1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| Устройство синхронизации опорного колебания высокоскоростного модема | 1991 |

|

SU1800634A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ ПЕРЕДАЧ | 1995 |

|

RU2099786C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Устройство адаптивной коррекции межсимвольных искажений | 1984 |

|

SU1290542A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО МАГНИТНОЙ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОГО СИГНАЛА (ВАРИАНТЫ) | 1994 |

|

RU2127913C1 |

Изобретение относится к электросвязи и может быть использовано в высокоскоростных модемах для кодирования информационных сигналов сверточным кодом. Цель изобретения - повышение помехозащищенности формируемой устройством последовательности сигналов в каналах со скачками фазы несущего колебания, кратными 90°, путем увеличения свободного расстояния между последовательностями сигналов, кодированных сверточным кодом. Для этого в устройство для кодирования сверточным кодом, содержащее первый блок постоянной памяти, первый элемент задержки, первый сумматор, второй сумматор, второй блок постоянной памяти, второй элемент задержки, первый умножитель, третий сумматор, четвертый сумматор, третий элемент задержки, второй умножитель, четвертый элемент задержки, пятый сумматор и пятый элемент задержки, вводятся инверторы, шестой сумматор и шестой элемент задержки. 4 ил., 1 табл.

УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СВЕРТОЧНЫМ КОДОМ, содержащее первый блок постоянной памяти, первый и второй входы которого являются одноименными информационными входами устройства, первый выход первого блока постоянной памяти соединен через первый элемент задержки с третьим входом первого блока постоянной памяти и непосредственно с первыми входами первого и второго сумматоров и второго блока постоянной памяти, второй выход первого блока постоянной памяти соединен через второй элемент задержки с четвертым входом первого блока постоянной памяти и непосредственно с вторыми входами первого сумматора и второго блока постоянной памяти, третий и четвертый входы и выходы которого являются соответственно одноименными информационными входами и выходами устройства, выход второго сумматора соединен с первым входом первого умножителя, выход которого соединен с первым входом третьего сумматора, четвертый сумматор, выход которого через третий элемент задержки соединен с вторым входом первого умножителя и первым входом второго умножителя, четвертый элемент задержки, выход которого соединен с первым входом пятого сумматора, пятый элемент задержки, отличающееся тем, что, с целью повышения помехозащищенности формируемой устройством последовательности сигналов, в него введены инверторы, шестой сумматор и шестой элемент задержки, выход первого сумматора соединен с вторым входом третьего сумматора, выход которого соединен с вторым входом пятого сумматора, выход которого через последовательно соединенные пятый элемент задержки и первый инвертор соединен с вторым входом второго сумматора и первым входом четвертого сумматора, входы второго инвертора и шестого элемента задержки подключены к выходу третьего элемента задержки, выход шестого элемента задержки соединен с входом четвертого элемента задержки, выход второго инвертора соединен с пятым входом второго блока постоянной памяти, вход третьего инвертора подключен к второму выходу первого блока постоянной памяти, выход соединен с вторым входом второго умножителя, выход которого соединен с первым входом шестого сумматора, второй вход которого подключен к первому выходу первого блока постоянной памяти, выход соединен с вторым входом четвертого сумматора.

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Микросхемы и их применение | |||

| Справ | |||

| пособие /Под ред.В.А.Батушева, В.Н.Вениаминова, В.Г.Ковалева и др | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и доп | |||

| М.: Радио и связь, 1983, с.272. | |||

Авторы

Даты

1995-06-27—Публикация

1991-08-15—Подача