Изобретение относится к электросвязи и может быть использовано в высокоскоростных модемах для формирования сверточно-кодированных сигналов.

Известно устройство для сверточного кодирования, содержащее регистр сдвига, первый сумматор, второй сумматор и переключатель [1]

Известно также устройство для формирования сверточно-кодированных сигналов, содержащее первую линию задержки, вторую линию задержки, третью линию задержки, первый сумматор, второй сумматор и блок выбора сигнальной точки [2]

Недостатками этих устройств являются низкая помехозащищенность генерируемых сверточно-кодированных последовательностей при невысоких отношениях сигнал/шум (< 20 дБ), а также их чувствительность к скачкам фазы несущего колебания, равным nπ /2, где n 1, 2, 3, при наличии которых в канале связи становится невозможным правильное декодирование принимаемой последовательности.

Наиболее близким к изобретению по технической сущности является устройство для формирования сверточно-кодированных сигналов, нечувствительных к скачкам фазы несущего колебания в канале связи, кратным 90о, содержащее блок постоянной памяти, первый и второй выход которого через первую и вторую линии задержки подсоединены соответственно к третьему и четвертому входам блока постоянной памяти, последовательно соединенные третью линию задержки, первый сумматор, второй сумматор, четвертую линию задержки, третий сумматор, четвертый сумматор, пятую линию задержки, блок выбора сигнальной точки, а также пятый сумматор, первый умножитель и второй умножитель, при этом выход пятого сумматора соединен с вторым входом первого сумматора, входами пятого сумматора являются первый и второй выходы блока постоянной памяти, а выход пятой линии задержки является объединенным первым входом третьей линии задержки, первого умножителя и второго умножителя, вторыми входами первого умножителя и второго умножителя являются соответственно выход третьего сумматора и второй выход блока постоянной памяти, выходы первого умножителя и второго умножителя подсоединены соответственно к вторым входам второго сумматора и четвертого сумматора, первый выход блока постоянной памяти является вторым входом третьего сумматора и третьим входом блока выбора сигнальной точки, четвертый вход которого соединен с вторым выходом блока постоянной памяти, причем первые и вторые входы блока постоянной памяти и блока выбора сигнальной точки являются информационными входами, а выходы блока выбора сигнальной точки являются выходами устройства [3]

Устройство формирует сверточно-кодированные сигналы, которые позволяют передавать 4 информационных бита (m 4) за один интервал модуляции. Применяемый для сверточного кодирования код со скоростью R  /

/ +1 2/3 обеспечивает асимптотический энергетический выигрыш от кодирования (АЭВК) 4 дБ по сравнению с некодированной передачей методом квадратурно-амплитудной модуляции КАМ-16.

+1 2/3 обеспечивает асимптотический энергетический выигрыш от кодирования (АЭВК) 4 дБ по сравнению с некодированной передачей методом квадратурно-амплитудной модуляции КАМ-16.

АЭВК обусловлен величиной свободного расстояния (минимальное евклидово расстояние) между двумя любыми передаваемыми сверточно-кодированными последовательностями сигналов, равной  .

.

Сверточно-кодированные сигналы являются нечувствительными к скачкам фазы несущего колебания в канале связи, кратным 90о. Это достигается за счет выполненного определенным образом устройства-прототипа назначения подмножеств сигнальных точек, полученных в результате разбиения [1, 4] исходного ансамбля сигналов переходам графа состояний, соответствующего назначения бит сигнальным точкам ансамбля сигналов и применения операции дифференциального кодирования.

Для декодирования сверточно-кодированной последовательности сигналов на приеме используется декодер максимального правдоподобия с мягким решением [5, 6] Решающее правило такого декодера можно сформулировать следующим образом. В качестве решения принимается такая информационная последовательность } которая дала бы на выходе блока выбора сигнальной точки последовательность сигналов

} которая дала бы на выходе блока выбора сигнальной точки последовательность сигналов } наиболее близкую к принимаемой

} наиболее близкую к принимаемой } по евклидовому расстоянию

} по евклидовому расстоянию -

- min

min

при этом }∈c где с совокупность всех возможных последовательностей на выходе блока выбора сигнальной точки.

}∈c где с совокупность всех возможных последовательностей на выходе блока выбора сигнальной точки.

Характеристики "мягкого" декодирования зависят от свободного расстояния

dсвоб= min

при этомSn} ≠{Pn} Sn}Pn} ∈ c.

Предположим, что сигнальные последовательностиSn} иPn} с минимальным евклидовым расстоянием между ними dсвоб порождаются соответственно двоичными последовательностямиan} иan'} Тогда вероятность того, что вместо переданной последовательностиan} будет декодирована последовательностьan'} определяется как

P {

{  }Pn}

}Pn} {Sn}

{Sn} P

P {

{ }a

}a }

} {an}

{an} Q(d

Q(d 2σ), где Q интервал вероятностей;

2σ), где Q интервал вероятностей;

σ- среднеквадратическое отклонение шума.

При отношении сигнал/шум, стремящемуся к бесконечности, вероятностью того, что в качестве решения будет принята последовательностьSn'} расположенная на расстоянии большем, чем dвобот действительно переданной последовательностиSn} можно пренебречь по сравнению с вероятностью того, что в качестве решения будет принята последовательностьPn} на расстоянии dсвоб отSn} Поэтому

P N(dсвоб)·Q(dсвоб/2σ), (1) где N(dсвоб) число ошибочных последовательностей, находящихся на расстоянии dсвоб от действительно переданной последовательностиSn} и зависит от структуры графа переходов [4]

N(dсвоб)·Q(dсвоб/2σ), (1) где N(dсвоб) число ошибочных последовательностей, находящихся на расстоянии dсвоб от действительно переданной последовательностиSn} и зависит от структуры графа переходов [4]

Как видно из (1), определяющее влияние на помехозащищенность сверточно-кодированной последовательности сигналов оказывает свободное расстояние dсвоб. АЭВК, обусловленный величиной свободного расстояния, составляет 4 дБ. Однако в каналах с аддитивным белым гауссовым шумом (АБГШ) и при скачках фазы несущего колебания, кратных 90о, выигрыш от кодирования значительно снижается при малых и средних отношениях сигнал/шум (С/Ш) (15-20 дБ). Так, например, при вероятности ошибки Рош 10-4 выигрыш от кодирования составляет около 2,5 дБ.

Таким образом, сверточно-кодированная последовательность сигналов, формируемая устройством, обладает невысокой помехозащищенностью, обусловленной величиной свободного расстояния.

Кроме того, использование операции дифференциального кодирования ведет к размножению ошибок при выполнении обратной операции декодирования в приемнике модема в случае ошибочного решения декодера максимального правдоподобия (декодера Витерби).

Целью изобретения является повышение помехозащищенности устройства и устранение операции дифференциального кодирования, ведущей к размножению ошибок при дифференциальном декодировании в приемнике модема в случае ошибочного решения декодера Витерби и повышение за счет этого энергетического выигрыша от кодирования в каналах со скачками фазы несущего колебания, кратными 90о, при малых и средних отношениях С/Ш.

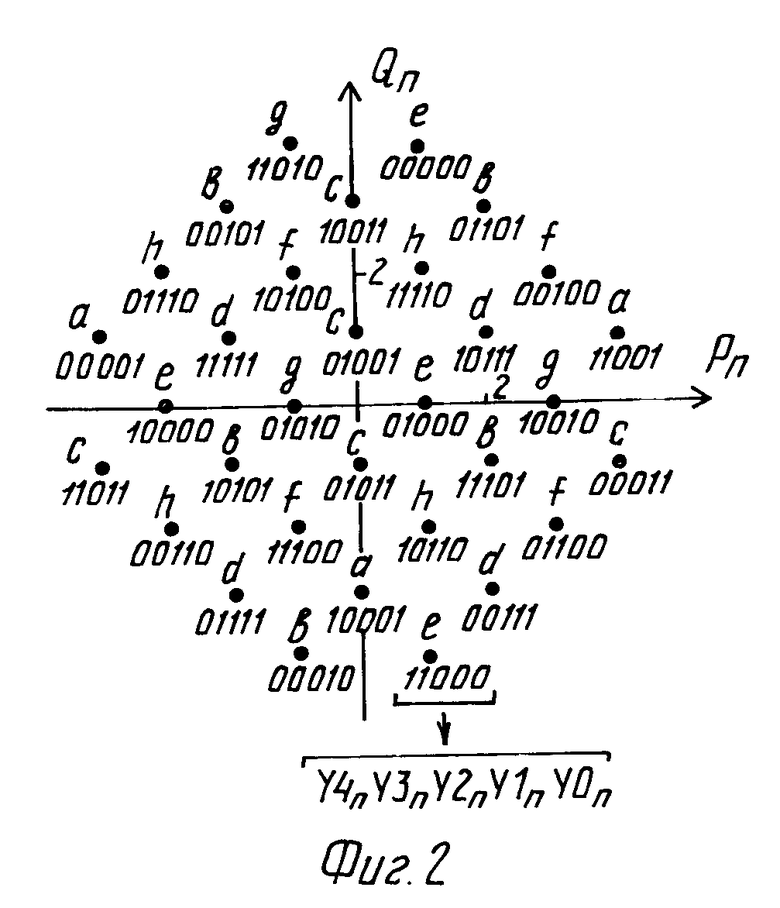

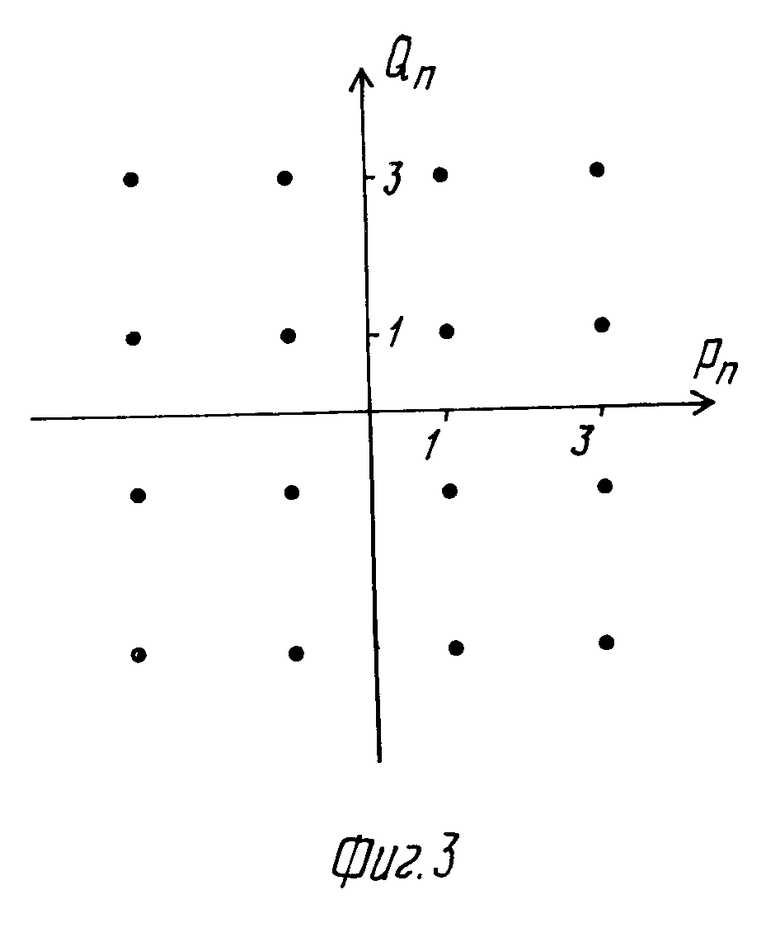

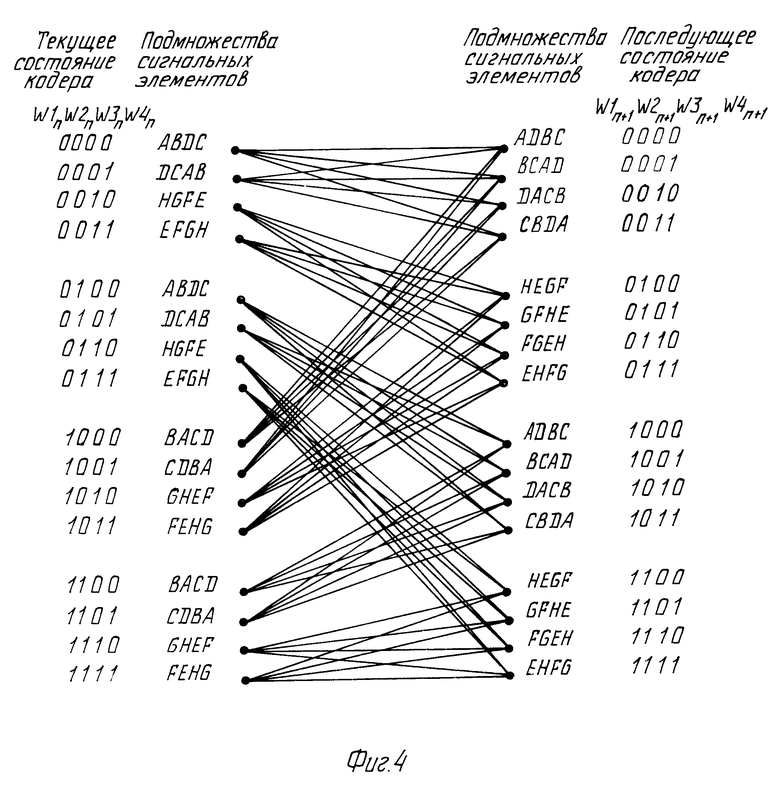

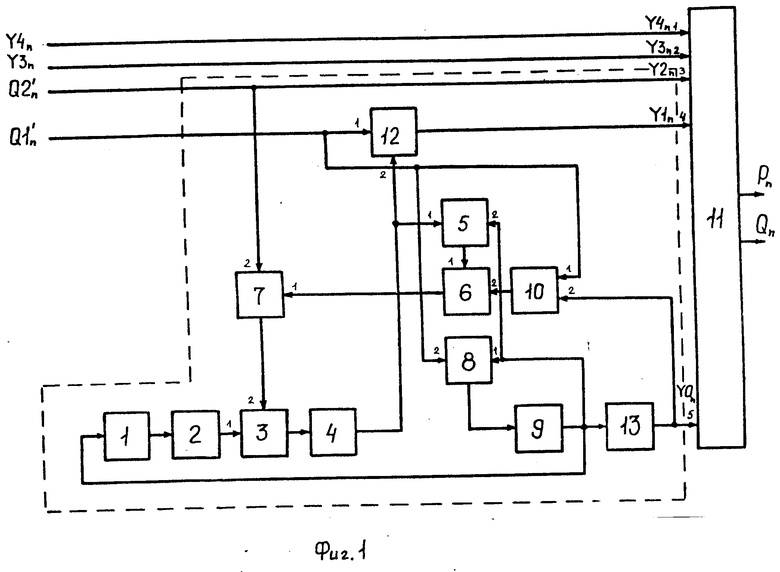

На фиг. 1 представлена структурная электрическая схема устройства для кодирования сверточным кодом; на фиг.2 и 3 тридцатидвух- и шестнадцатиточечные ансамбли сигналов; на фиг.4 граф переходов сверточного кодера.

Устройство содержит первый элемент 1 задержки, второй элемент 2 задержки, первый сумматор 3, третий элемент 4 задержки, второй сумматор 5, третий сумматор 6, четвертый сумматор 7, пятый сумматор 8, четвертый элемент 9 задержки, умножитель 10, блок 11 постоянной памяти, шестой сумматор 12 и инвертор 13.

Устройство работает следующим образом.

На информационные входы устройства в момент времени n поступают информационные биты Q1n', Q2n', Y3n, Y4n (m 4). Биты Y3n, Y4n подаются непосредственно на первый и второй входы блока 11, а биты Q1n', Q2n' на сверточный кодер, содержащий последовательно соединенные первый элемент 1 задержки, второй элемент 2 задержки, первый сумматор 3, третий элемент 4 задержки, второй сумматор 5, третий сумматор 6, четвертый сумматор 7, а также последовательно соединенные пятый сумматор 8, четвертый элемент 9 задержки и инвертор 13, а также умножитель 10 и шестой сумматор 12. Работу кодера описывают следующие логические функциональные зависимости

W1n+1 W2n;

W2n+1 W3n;

W3n+1= W3n⊕ Q1 ;

;

W4n+1= W1n⊕ W3n⊕ W4n⊕  Q1

Q1 ⊕ Q2

⊕ Q2 ;

;

Y1n= W4n⊕ Q1 ;

;

Y1n= .

.

Они связывают последующее состояние W1n+1W2n+1W3n+1W4n+1 и выходные биты Y1n и Y0n кодера с текущим состоянием W1nW2nW3nW4n и выходными битами кодера Q2n' и Q1n'. Данные выражения получены путем минимизации с помощью диаграмм Вейча полных функциональных зависимостей, обусловленных графом переходов и назначением бит YIn, I 0,1,4 сигнальным точкам ансамбля сигналов. Граф переходов отображает работу сверточного кодера как конечного автомата с памятью.

Каждому переходу, выходящему из одного текущего состояния и ведущего в последующее, назначается совокупность сигнальных точек из ансамбля сигналов, называемая подмножеством. Получение этих подмножеств основано на идее отображения путем разбиения множеств [1, 2, 4] При этом проводится последовательное разбиение исходного расширенного сигнального множества (алфавита сигналов) на вложенные подмножества, причем расстояния между элементами подмножества (сигнальными точками) на каждом шаге разбиения возрастают, а число элементов в нем убывает. В качестве исходного расширенного сигнального множества применяется тридцатидвухточечное крестообразное созвездие (32-CR), показанное на фиг. 2. Оно является расширенным, поскольку для передачи m 4 некодированных информационных бит по каналу за интервал модуляции методом квадратурно-амплитудной модуляции (КАМ) было бы достаточно иметь ансамбль сигналов (фиг. 3), состоящий из 16 точек (16-QA). Применение сверточного кодирования к входным информационным битам Q2n'Q1n' ведет к появлению дополнительного избыточного пятого бита Y0n. Поэтому ансамбль сигналов должен иметь М 2m+1 32 точки. В данном случае применяется ансамбль сигналов 32-CR, обладающий 90-градусной симметричностью, что является необходимым условием для обеспечения нечувствительности формируемой поcледовательноcти сигналов к скачкам фазы, кратным 90о. Исследование подхода, основанного на разбиении исходного сигнального множества на вложенные подмножества, ведет к разбиению исходного тридцатидвухточечного сигнального множества на 2m+1=23=8 ( 2 число входных бит сверточного кодера) вложенных подмножеств A, B, C, D, E, F, G, H (фиг.2).

2 число входных бит сверточного кодера) вложенных подмножеств A, B, C, D, E, F, G, H (фиг.2).

Разбиение проводится в ( +1) 3 шага. На первом шаге разбиения получается два подмножества (фиг.2): A U B U C U D и E U FU G U H ( U- знак объединения) с минимальным евклидовым расстоянием Δ1=

+1) 3 шага. На первом шаге разбиения получается два подмножества (фиг.2): A U B U C U D и E U FU G U H ( U- знак объединения) с минимальным евклидовым расстоянием Δ1=  = 2 где Δо минимальное евклидово расстояние для исходного сигнального множества, Δo=

= 2 где Δо минимальное евклидово расстояние для исходного сигнального множества, Δo=  На втором шаге разбиения получаются подмножества A U B, C U D, E U F, G U H с Δ2=

На втором шаге разбиения получаются подмножества A U B, C U D, E U F, G U H с Δ2=  Δ1= 2

Δ1= 2 На последнем шаге разбиения имеем восемь подмножеств A, B, C, D, E, F, G, H с Δ3=

На последнем шаге разбиения имеем восемь подмножеств A, B, C, D, E, F, G, H с Δ3=  Δ2=4 При вращении сигнального множества по часовой стрелке на 90о подмножеств A, B, C, D, E, F, G, H переходят соответственно в подмножества E, F, G, H, C, D, A, B. При вращении на 180о подмножества A, B, C, D, E, F, G, H переходят, соответственно, в C, D, A, B, G, H, E, F, а при 270о в G, H, E, F, A, B, C, D.

Δ2=4 При вращении сигнального множества по часовой стрелке на 90о подмножеств A, B, C, D, E, F, G, H переходят соответственно в подмножества E, F, G, H, C, D, A, B. При вращении на 180о подмножества A, B, C, D, E, F, G, H переходят, соответственно, в C, D, A, B, G, H, E, F, а при 270о в G, H, E, F, A, B, C, D.

Построение графа переходов базировалось на следующих правилах [3, 4]

а) граф переходов должен быть симметричен и все переходы в нем должны выполняться с одинаковой частотой;

б) переходам, начинающимся в одном состоянии и ведущим в различные состояния, необходимо ставить в соответствие сигналы одного из подмножеств, полученных на первом шаге разбиения;

в) сигналы из этих же подмножеств назначаются переходам, выходящим из различных состояний и ведущих в одно и то же состояние;

г) если обозначить q состояний кодера через i 0,1,q-1, то для того, чтобы кодер и, следовательно, последовательность сигналов были прозрачны к фазовой неопределенности в канале связи, кратной 90о, должны существовать функции однозначного соответствия fl:0,1,q-1} _→0,1,q-1} l 1,2,3 такие, что выполняется следующее утверждение. Для каждого перехода из состояния i в состояние j, iнj ∈ 0,1,q-1} обозначим через X0 группу сигнальных элементов одного из полученных в результате разбиения подмножества, а через Х1, Х2, Х3 группы сигнальных элементов, полученные из Х0 посредством вращения по часовой стрелке соответственно на 90, 180 и 270о. Тогда каждому переходу из состояния fl(i) в состояние fl(j), (l 1,2,3) назначается группа сигнальных элементов Xl(l 1,2,3) соответственно.

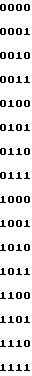

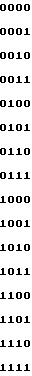

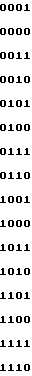

Граф переходов представлен на фиг.4. Функции однозначного соответствия имеют вид

f1:

1110 f2:

1110 f2:

f3:

f3:

Для графа переходов квадрат свободного расстояния равен 12. Действительно, если по каналу передается последовательность сигнальных точек, принадлежащих, например, подмножеству А (нулевое состояние), то ближайшей к ней будет последовательность из сигнальных точек, принадлежащих подмножествам B-D (рассматривается решетчатая диаграмма, получающаяся при развертке графа переходов во времени). С учетом минимального расстояния между точками подмножеств А и В, А и D ( ΔAB 2 , ΔAD 2, фиг.2) квадрат свободного расстояния между рассматриваемыми последовательностями будет равен dсвоб2 ΔAB2+ΔAD2= 12. Если за правильную последовательность выбрать любую другую, то также найдется последовательность, отстоящая от нее на расстоянии

, ΔAD 2, фиг.2) квадрат свободного расстояния между рассматриваемыми последовательностями будет равен dсвоб2 ΔAB2+ΔAD2= 12. Если за правильную последовательность выбрать любую другую, то также найдется последовательность, отстоящая от нее на расстоянии  .

.

Свободное расстояние позволяет оценить АЭВК по сравнению с некодированной передачей методом КАМ-16. Тогда, с учетом нормировки по средней мощности, для АЭВК имеем [2, 4]

G 10lg

10lg

10lg

4,771 дБ.

4,771 дБ.

C выхода сверточного кодера выходные биты, обозначенные как Y0n, Y1n и Y2n, поступают соответственно на пятый, четвертый и третий входы блока 11, на второй и первый входы которого подаются некодированные информационные биты, обозначенные через Y3n, Y4n. В соответствии с входной последовательностью бит YIn, I 0,1,4 блок 11 осуществляет выбор для передачи по каналу одной из точек алфавита сигналов (фиг.2).

Для обеспечения нечувствительности сигнальных элементов ансамбля сигналов к скачкам фазы несущего колебания, кратным 90о, без использования операции дифференциального кодирования и снижения сложности построения сверточного кодера назначение бит YIn, I 0,1,4 сигнальным элементам выполнено с соблюдением следующих правил (фиг.2):

а) каждой группе из четырех сигнальных элементов, получаемых путем вращения одного из них на 90, 180 и 270о по часовой стрелке, назначается одна и та же битовая комбинация Y4nY3nY2n;

б) сигнальным элементам в каждом из восьми подмножеств A, B, C, D, E, F, G, H назначаются одни и те же битовые комбинации Y2nY1nY0n;

Подмножества Y2n Y1n Y0n Подмножества Y2n Y1n Y0n

A 0 0 1 E 0 0 0

B 1 0 1 F 1 0 0

C 0 1 1 G 0 1 0

D 1 1 1 H 1 1 0

в) для каждого текущего состояния кодера и каждой входной битовой комбинации устройства обозначим через V 0 сигнальный элемент, соответствующий битовой комбинации Y4nY3nY2nY1nY0n. Затем обозначим через V1, V2, V3 сигнальные элементы, получаемые, когда V0 поворачивается на 90, 180 и 270о по часовой стрелке соответственно. Тогда сигнальные элементы, соответствующие битовой комбинации Y4nY3nY2nY1nY0n при текущем состоянии кодера fl(W1nW2nW3nW4n) (l 1,2,3) и при той же входной битовой комбинации Y4nY3nQ2n'Q1n' будут соответственно V1, V2 и V3.

В соответствии с входными битами YIn (I 0,1,4) в блоке 11 однозначно определяется сигнальная точка и на выходы блока 11 поступают сигналы Pn и Qn, соответствующие координатам синфазной и квадратурной составляющих сигнальной точки.

Блок 11 постоянной памяти хранит значение сигнальных элементов. Входные биты YIn (I 0,1,4) для блока 11 образуют код адреса сигнального элемента в ПЗУ. Примеры реализации блока 11 представлены на рис.5.17, 18, с.182, 283 [7]

Результаты моделирования предлагаемого устройства для формирования сверточно-кодированных сигналов показали, что по сравнению с прототипом в каналах с аддитивным белым гауссовым шумом и при скачках фазы несущего колебания, кратных 90о, при малых и средних отношениях С/Ш (15-20 дБ) оно обеспечивает значительное повышение помехозащищенности передаваемой последовательности сигналов за счет увеличения свободного расстояния между сигнальными последовательностями.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СВЕРТОЧНЫМ КОДОМ | 1991 |

|

RU2038695C1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| Устройство синхронизации опорного колебания высокоскоростного модема | 1991 |

|

SU1800634A1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ ПЕРЕДАЧ | 1995 |

|

RU2099786C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Кодек блочной сигнально-кодовой конструкции | 1989 |

|

SU1711337A1 |

| Устройство адаптивной коррекции межсимвольных искажений | 1984 |

|

SU1290542A1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЛОГАРИФМИЧЕСКОГО ОТНОШЕНИЯ ПРАВДОПОДОБИЯ С ПРЕДВАРИТЕЛЬНЫМ КОДИРОВАНИЕМ | 2002 |

|

RU2304352C2 |

Изобретение относится к электросвязи и может быть использовано в высоковольтных модемах для формирования сверточно-кодированных сигналов. Цель изобретения - повышение помехозащищенности устройства. Устройство содержит сумматоры 3, 5, 6, 7, 8 и 12,инвертор 13, элементы 1, 2, 4 и 9 и блок 11 постоянной памяти. 4 ил.

УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СВЕРТОЧНЫМ КОДОМ, содержащее последовательно соединенные первый элемент задержки, второй элемент задержки и первый сумматор, третий элемент задержки, выход которого соединен с первым входом второго сумматора, выход которого соединен с первым входом третьего сумматора, четвертый сумматор, выход которого соединен с вторым входом первого сумматора, умножитель, выход которого соединен с вторым входом третьего сумматора, пятый сумматор и блок постоянной памяти, выходы которого являются выходами устройства, первый и второй входы блока постоянной памяти являются одноименными входами устройства, третий вход блока постоянной памяти и второй вход четвертого сумматора объединены и являются третьим входом устройства, первый вход умножителя является четвертым входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены шестой сумматор, четвертый элемент задержки и инвертор, выход первого сумматора соединен с входом третьего элемента задержки, первый и второй входы и выход шестого сумматора подключены соответственно к четвертому входу устройства, выходу третьего элемента задержки и четвертому входу блока постоянной памяти, второй вход четвертого сумматора и первый вход пятого сумматора подключены соответственно к выходу третьего сумматора и четвертому входу устройства, выход пятого сумматора через четвертый элемент задержки соединен с входом первого элемента задержки, вторыми входами второго и пятого сумматоров и входом инвертора, выход которого соединен с вторым входом умножителя и пятым входом блока постоянной памяти.

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Микросхемы и их применение: Справ.пособие/В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и доп | |||

| М.: Радио связь, 1983, с.272. | |||

Авторы

Даты

1995-06-27—Публикация

1991-11-21—Подача