(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Кодер телевизионного сигнала | 1988 |

|

SU1569990A1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Кодер сигнала изображения | 1989 |

|

SU1730727A1 |

| Устройство для кодирования телевизионного сигнала | 1988 |

|

SU1559409A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1986 |

|

SU1424125A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПРОВЕРКИ ЗАВЕРЕННОГО ЦИФРОВЫМ ВОДЯНЫМ ЗНАКОМ ЭЛЕКТРОННОГО ИЗОБРАЖЕНИЯ | 2009 |

|

RU2411579C1 |

Изобретение относится к вычислительной технике. Его использование при построРнф ении цифровых телевизионных систем позволяет повысить информативность кодера за счет сокращения избыточности кодируемого сигнала. Это обеспечивается благодаря определению четырех разных классов кодируемых блоков, каждому из которых соответствует свой алгоритм синтеза выходного кодового слова. Кодер содержит аналого-цифровой преобразователь 1, блок 2 умножителей, блоки 3, 6 суммирования, узел 5 памяти, квантователь 4, блок 7 инвертирования, сумматор 8 модулей, блоки 9-11 буферной памяти, дешифраторы 12, 13, блоки 14, 15 коммутации, блок 16 кодирования. 4 з.п. ф-лы, 4 ил.

vi

со о VJ

ю

4

Изобретение относится к вычислительной технике и технике средств связи и может быть использовано при построении цифровых телевизионных систем для эффективного кодирования телевизионных (ТВ) изображений.

Основным требованием, предъявляемым к системам эффективного кодирования изображений, является обеспечение высокого качества изображений. В настоящее время практически важной задачей является задача четырехкратного сжатия потока, т.е. уменьшение затрат на кодирование элемента до 2 бит/элемент. Наилучшим кодером, обеспечивающим четырехкратное сжатие потока, является известный кодер с переменной скоростью кодирования. Кодер включает в себя блок предсказания, преобразователь кодов, буферное ЗУ и передатчик. В зависимости от заполнения буферного ЗУ в динамике работы и по результатам анализа, автоматически регулируется скорость обработки сигнала в блоке предсказания и преобразователе кодов.

Этот кодер осуществляет статическое кодирование ТВ изображений, т.е. обратимое кодирование и принципиально не приводит к ухудшению качества изображений. Вследствие нестационарности источника ТВ изображений емкость буферного ЗУ ока- зывается значительной - несколько кадров.

Однако большие аппаратурные затраты являются недостатком указанного кодера.

Наиболее близким к предлагаемому является устройство для кодирования телеви- зионного сигнала, содержащее аналого-цифровой преобразователь (АЦП), блок памяти, блок умножения, первый и второй блоки суммирования, блок инвертирования, сумматор модулей, квантователь, первый-третий буферные регистры, генератор контрольных символов, первый и второй дешифраторы, первый-третий блоки коммутации, первый и второй блоки задержки, блок кодирования и элемент ЗАПРЕТ.

Принцип работы устройства заключается в следующем.

В АЦП входной аналоговый сигнал преобразуется в цифровой видеосигнал. В блоке памяти цифровой видеосигнал от одного поля запоминается, а затем из неге последовательно считываются кодируег ле группы размерностью 2x2 элемента. Дл хаждой кодируемой группы вычисляются три пере- менные-среднеезначениеяркости кодиру-

1 4 емой группы У х, где х,-элементы

л , 1

кодируемой группы, полусумма модулей отклонений яркости олементов кодируемой

lai-x,l

от средней яркости 32 а также бинарная матрица знаков отклонений S размерностью 2x2, в которой единицы соответствуют тем элементам xi, которые больше или равны ai, а нули - тем элементам xi, которые меньше ai. Вычисление ai производится суммированием, результат которого снимается без двух младших разрядов. Вычисление аг аналогично вычислению ai с той лишь разницей, что суммирование элементов х; производится с инверсным значением ai и результат суммирования снимается без одного младшего разряда.

Вычисленные значения ai и 32 квантуются в квантователе с линейной шкалой квантования, причем на кодирование ai отводится семь разрядов выходного кодового слова.

В данном устройстве матрица знаковой функции S |С Ч размерностью 2x2

L Ч J

передается двумя разрядами, а именно разрядами Si и $2. Разряды 5з и SA исключаются из передачи. На приемной стороне исключенные разряды восстанавливаются следующим образом:

0| О 0. h О

1 1

О ,0

0;о;

1ч.

где;;,- восстановленные разряды матрицы знаковой функции.

Таким образом, в устройстве производится исключение диагональных контуров и линий, т.е матриц знаков:

1 1

1 1| 11 Oi Ю 1 |0 О

1 о| h lid о

Ю о

IP

Ю

о

V о

о 11 0|,Го 1 ю о Jo ii d oi

При реализации указанного устройства, соответствующего случаю внутрикадрового кодирования групп 2x2 элемента, при котором число уровней квантования среднего значения яркости а равно 128 (семь разрядов), число уровней квантования полусуммы разности 32 равно 8 (три разряда), число знаков разности - два, расход цифрового потока на информацию об одном элементе составляет 3 бит/элемент.

Переход от равнояркостного участка к контуру имеет маскирующее свойство, т.е. для человеческого глаза менее заметны неоднородности равнояркостного участка вблизи контура Поэтому точное семиразрядное кодирование в случае aai 0, aai-и 5 О, т.е. на границе равнояркостный участок - контур, является избыточным и в данном случае можно более грубо кодировать ai тремя разрядами, Текстура во фрагментах изображения также имеет маскирующее свойство, и поэтому на текстурных участках все параметры кодируемых групп можно кодировать более грубо.

Наличие избыточности является недостатком кодера-прототипа.

Целью изобретения является повышение информативности кодера за счет сокращения избыточности кодируемого сигнала.

Указанная цель достигается тем, что кодер сигнала изображения содержит аналого-цифровой преобразователь, вход которого является информационным входом кодера, блок умножителей, выходы которого соединены с входами первого блока суммирования, первый выходы которого подключены к первым входам квантователя. Выходы аналого-цифрового преобразователя соединены с информационными входами узла памяти, выходы которого подключены к первым входам второго блока суммирования и входам блока умножителей. Вторые выходы первого блока суммирования через блок инвертирования соединены с вторыми входами второго блока суммирования, выходы которого через сумматор модулей подключены к вторым входам квантователя, первые-третьи выходы которого соединены с информационными входами соответственно первого-третьего блоков буферной памяти. Кодер содержит также первый и второй дешифраторы, первый и второй блоки коммутации, первые выходы которых подключены соответственно к первым и вторым информационным входам блока кодирования, выход которого является выходом кодера. Первые управляющие входы блоков коммутации объединены, первые выходы второго блока буферной памяти подключены к входам первого дешифратора, выход которого соединен с вторым управляющим входом второго блока коммутации. Первые выходы третьего блока буферной памяти подключены к первым информационным входам второго блока коммутации, первые информационные входы первого блока коммутации подключены к первым выходам третьего блока буферной памяти, вторые выходы которого соединены с вторыми информационными входами первого и второго блоков коммутации, вторые выходы которого подключены соответственно к третьим и четвертым информационным входам блока кодирования. Третьи информационные входы первого блока коммутации

подключены к первым выходам второго блока буферной памяти, вторые выходы которого соединеныс третьими информационными входами второго блока

коммутации и входами второго дешифратора. Первые выходы первого блока буферной памяти подключены к пятым информационным входам блока кодирования и четвертым информационным входам второго блока

коммутации. Вторые выходы первого блока буферной памяти соединены с шестыми информационными входами блока кодирования и четвертыми информационными входами первого блока коммутации, второй

управляющий вход которого объединен с седьмым информационным входом блока кодирования и подключен к выходу первого дешифратора. Выход второго дешифратора соединен с первым управляющим входом

второго блока коммутации и восьмым информационным входом блока кодирования. Первый тактовый вход кодера сигнала изображения соединен с тактовым входом АЦП, тактовым входом узла памяти, тактовым входом квантователя и первыми тактовыми входами первого, второго и третьего блоков буферной памяти, вторые тактовые входы которых соединены с первым тактовым входом блока кодирования и с вторым

тактовым входом кодера сигнала изображения, третий тактовый вход которого соединен с вторым тактовым входом блока кодирования. Четвертый тактовый вход кодера сигнала изображения соединен с входом синхронизации узла памяти.

Предлагаемое устройство реализует адаптивное групповое кодирование ТВ изображений группами 2x2 с объединением групп парами в блоки. Для каждой группы каждого блока вычисляются три переменные ai - средняя яркость группы; аз - отклонение от средней яркости; S - матрица

знаков. В кодере-прототипе на кодирование ai отводится семь разрядов, на аа - три разряда, на S - два разряда, что соответствует сжатию потока видеоданных до 3 бит/элемент.

В предлагаемом устройстве все множество образующих изображение фрагментов разделяется на четыре класса. Деление осуществляется на основе анализа значений a2i и 32 j,, для двух групп, образующих блок.

Еслиаа j иаа |т, равны нулю, то данный блок

соответствует классу равнояркостных фраг ментов (ai ,) или фрагментов с плав

ным изменением яркости (аи ац-н).

Если 32| 0, а 32 i + 1 0, то данный блок соответствует переходу от равноярко- стного участка к контуру (класс равноярко- стный участок - контур). Если 32| 0, а 321 + 1 0, то данный блок соответствует переходу от контура к равнояркостному участку (класс контур - равнояркостный участок). Если 321 0, э 32 | +, 0, то блок соответствует текстурному участку (класс текстура).

Для определения, к кзкому классу принадлежит передаваемый блок, в выходном шестнадцэтиразрядном кодовом слове имеются два служебных бита. Оставшиеся четырнадцать информационных бит распределяются между группами блока в зависимости от класса блока. Если это класс равнояркостных учзстков, то на передачу зц отводится семь бит, на передачу ац+1 - семь бит. Если блок принадлежит к классу равнояркостный участок - контур, то, учитывая маскирующие свойства контура, параметр аи равнояркостной группы передается более грубо - тремя разрядами, а в контурной группе на ai i +1 отводится пять бит, на 321 +1 Ава бита, на Si+i - четыре бита. Аналогично распределяются четырнадцать информационных бит для класса контур - равнояркостный участок.

Если блок относится к классу текстура, то, учитывая мэскирующие свойства текстуры, все параметры кодируемых групп кодируются более грубо. На аи и ац+1 отводится по три бита, на &2 и 32 i + 1 по два бита, на Sj и Si+i по два бита. На приемной стороне исключенные из передачи два бита знаковой функции каждой группы восстанавливаются таким обрэзом, чтобы восстановленная матрица знаков соответствовала горизонтальным или вертикальным контурам. Восстановление матрицы знаков именно таким образом связано с тем, что вероятность появления в естественных изображениях наклонных контуров меньше, чем вероятность появления горизонтальных или вертикальных контуров. Диагональное зрение человека менее остро, поэтому ошибки декодирования менее заметны в диагональных направлениях. Восстэновление матриц знаков происходит следующим образом:

1 CM JO Тг ,1 1;( 0 ,0м .1 О О 0 .1 llj

где цы.

- восстановленные разряды матриВ кодере-прототипе на кодирование блока (т.е. двух групп, размерностью 2x2)

затрачивалось двадцать шесть бит, в предлагаемом устройстве на кодирование блока затрачивается шестнадцать бит. Адаптивный подход в распределении информационных бит выходного кодового слова на кодирование параметров групп позволяет сохранить высокое субъективное качество кодированных изображений при уменьшении цифрового потока с 3 бит/элемент до 2

0 бит/элемент.

В настоящее время основной тенденцией разработки алгоритмов эффективного кодирования ТВ изображений является адаптивный подход. Практически для всех

5 известных методов сжатия видеоинформации предложены адаптивные процедуры формирования кодовых слов. Например, .на международной выставке GeBIT в Ганновере (ФРГ) японсая фирма КК демонстрирова0 ла универсэльный процессор СР - 200, позволяющий выполнять следующие программы кодирования: адаптивное векторное квантование (АВК); трехмерное АВК; адаптивное усеченное блочное кодирова5 ние; адаптивное дискретное косинусное преобразование; ДИКМ с адаптивным квантованием.

В предлагаемом устройстве также реализовано адаптивное кодирование, при

0 этом двухступенчатое: первая ступень - адаптивное построение второй функции разложения для каждой кодируемой группы; вторая ступень - адаптивный синтез выходного кодового слова и зависимости от

5 класса сюжета. Существенным моментом устройства является разбиение кодируемых блоков на классы с адаптацией процесса кодирования к каждому классу.

Известны устройства группового коди0 рования с независимым кодированием групп и разбиением групп на классы.

В перечисленных устройствах классами являются: равнояркостные участки, участки с плавным изменением яркости, скачок яр5 кости и текстура. Разбиение на классы при независимом кодировании групп не позволяет идентифицировать контуры, т.е. участки изображения, приходящиеся на равнояркостную группу и группу с перепа0 дом яркости. Как следствие, точность кодирования контуров оказывается сравнимой с точностью кодирования, например, скачка яркости, т.е. когда соседняя группа не рав- нояркостная. В результате возможно оши5 бочное восстановление контуров. При объединении групп в блоки, как это сделано в предлагаемом устройстве, контуры выделяются и для групп с контуром передается полноразрядная матрица знаков, т.е. сохраняется направленность контуров.

Известны два устройства с объединением групп в блоки, В первом устройстве согласование между группами в блоке производится на основании статистических свойств кодируемого сюжета, т.е. без учета ограничений зрительного восприятия. Во втором устройстве также игнорируются особенности зрительного восприятия изображений, так как усилия разработчиков направлены на повышение эффективности путем устранения координатной избыточности кодируемых переменных.

Высокое качество кодированных изображений при сжатии потока может быть получено только за счет максимально возможного использования свойств зрительного анализатора человека. В предлагаемом устройстве использованы маскирующие свойства контуров; маскирующие свойства текстуры; меньшая разрешающая способность глаза в наклонных направлениях,чем в горизонтальных и вертикальных, а также способность глаза усреднять малые возмущения яркости.

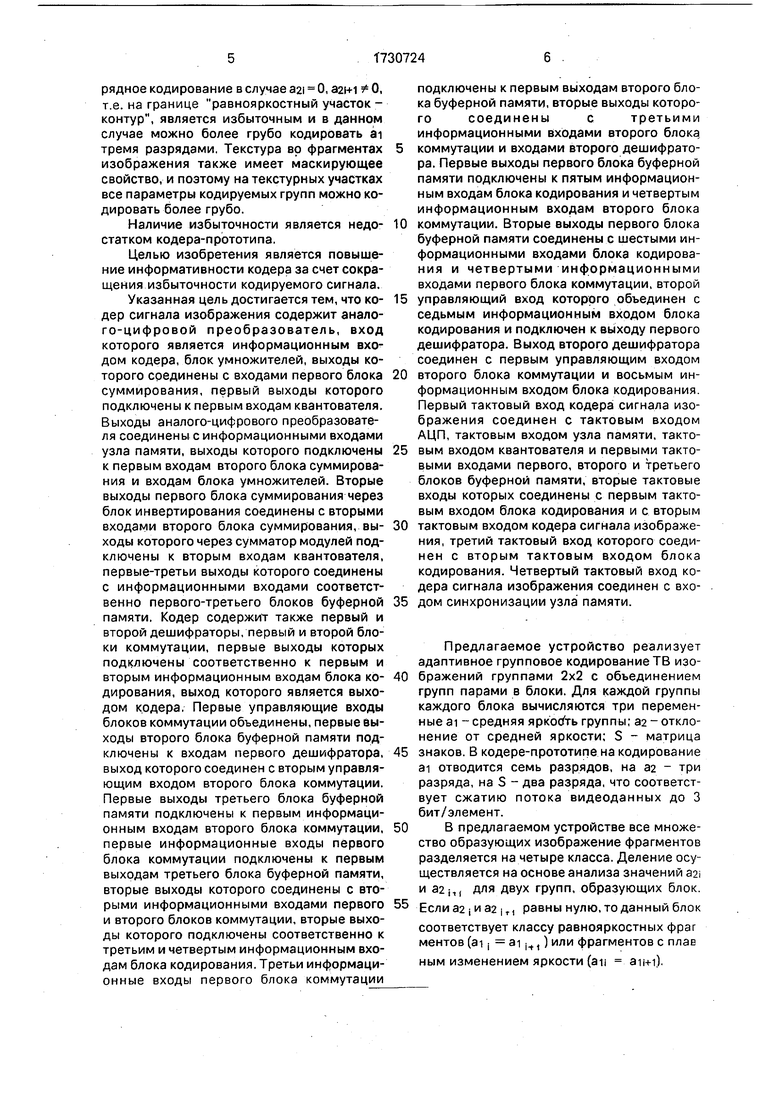

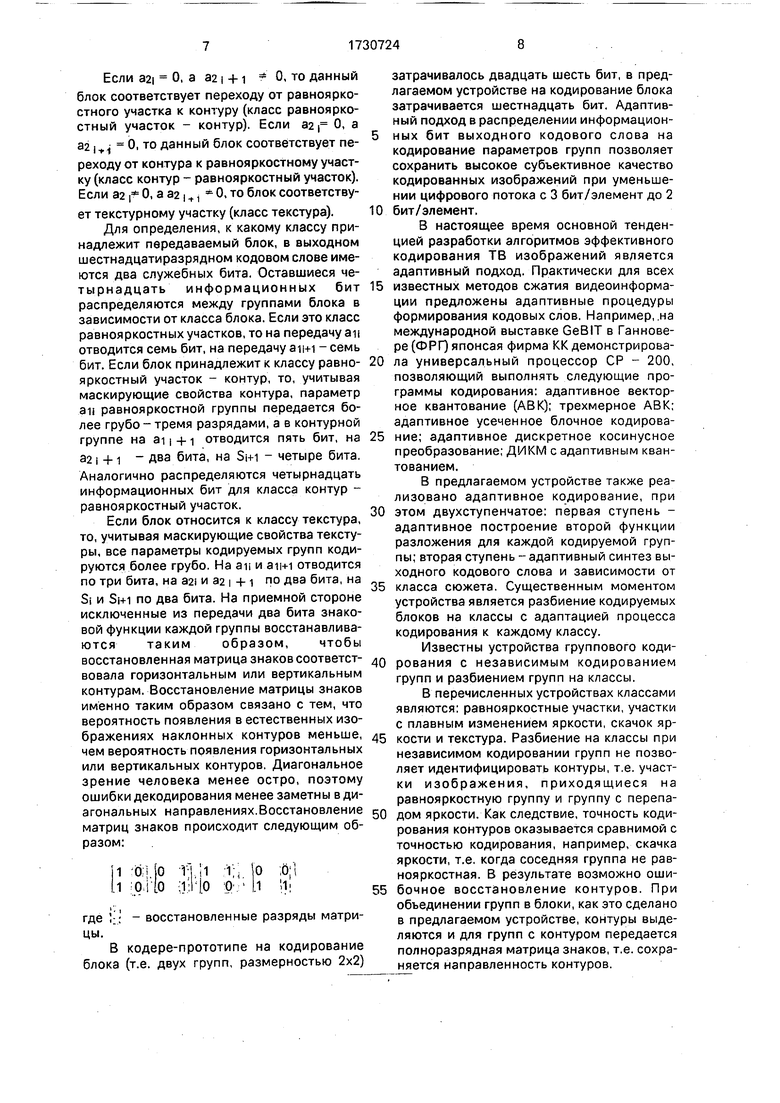

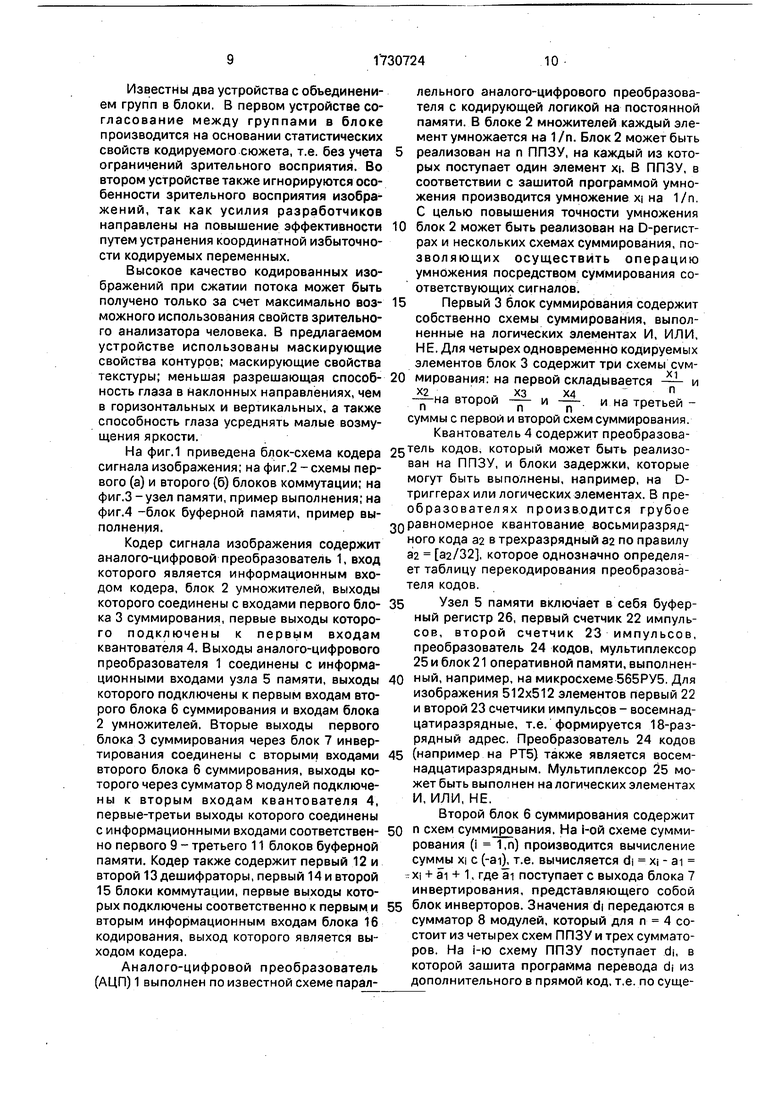

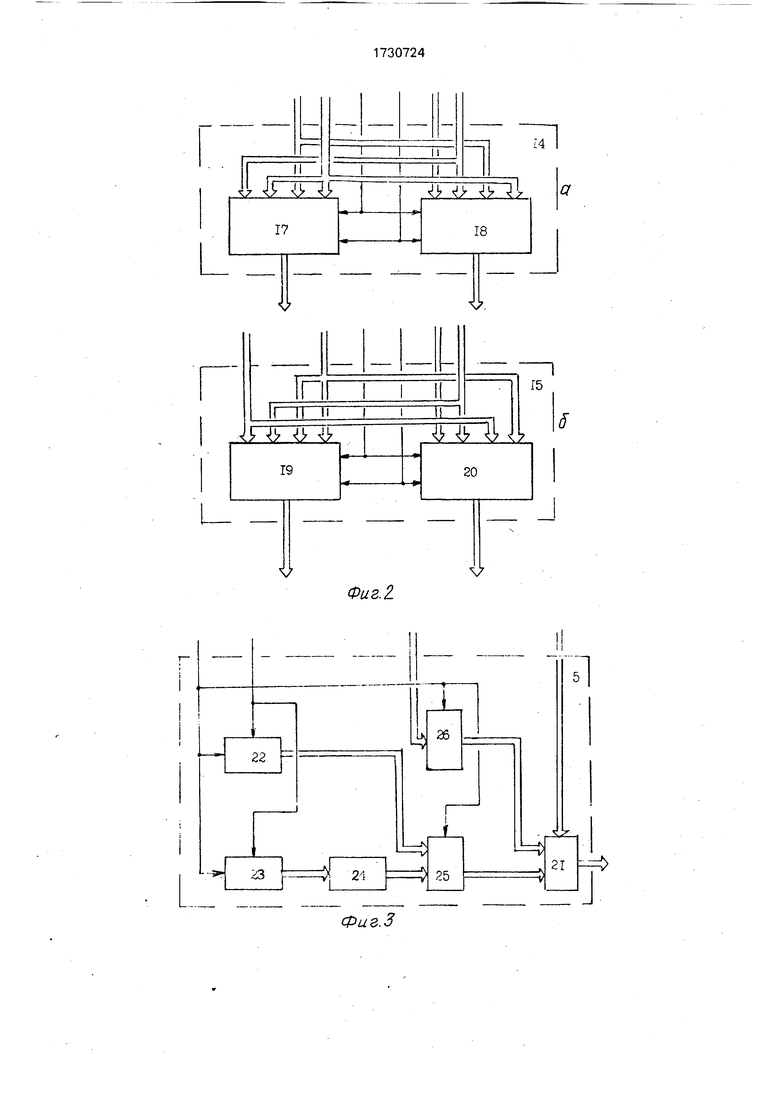

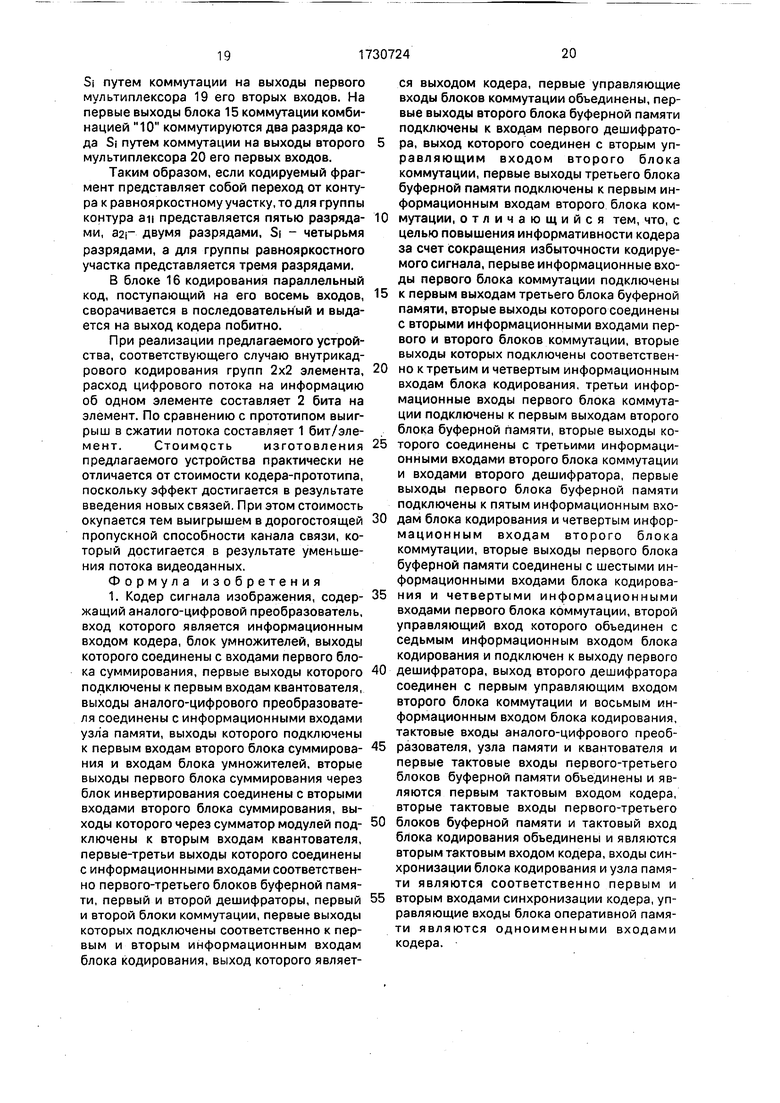

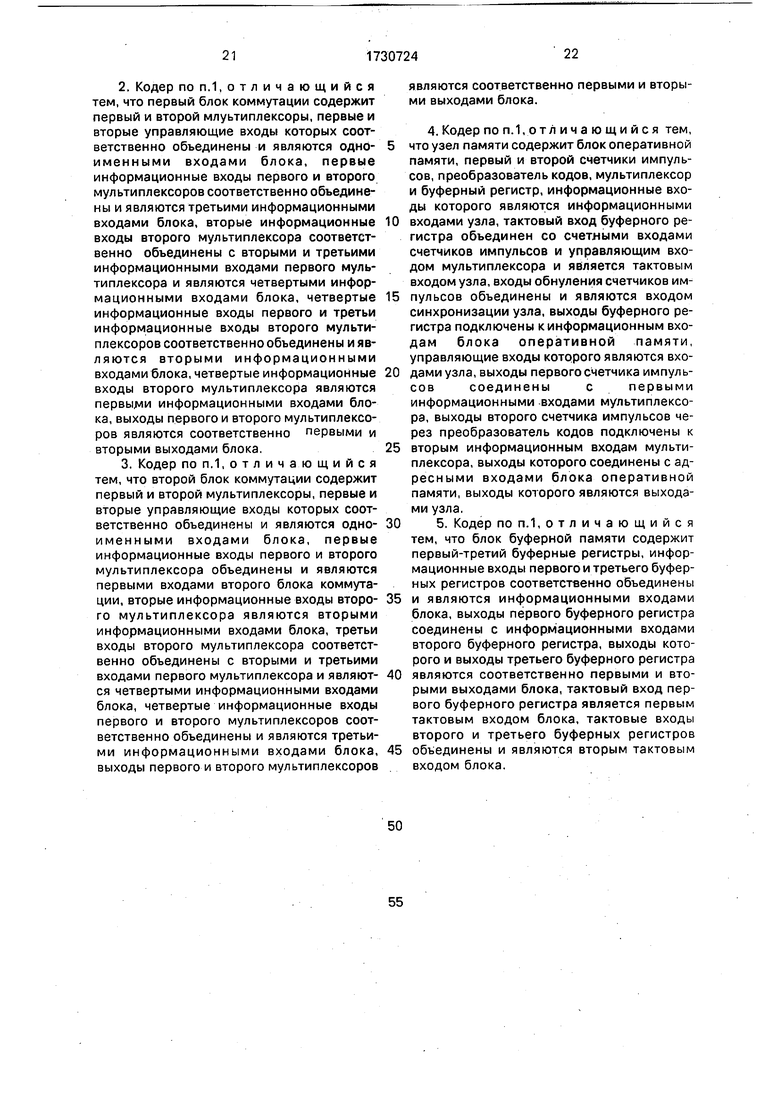

На фиг.1 приведена блок-схема кодера сигнала изображения; на фиг,2 -схемы первого (а) и второго (б) блоков коммутации; на фиг.З - узел памяти, пример выполнения; на фиг.4 -блок буферной памяти, пример выполнения.

Кодер сигнала изображения содержит аналого-цифровой преобразователь 1, вход которого является информационным входом кодера, блок 2 умножителей, выходы которого соединены с входами первого блока 3 суммирования, первые выходы которого подключены к первым входам квантователя 4. Выходы аналого-цифрового преобразователя 1 соединены с информационными входами узла 5 памяти, выходы которого подключены к первым входам второго блока б суммирования и входам блока 2 умножителей. Вторые выходы первого блока 3 суммирования через блок 7 инвертирования соединены с вторыми входами второго блока 6 суммирования, выходы которого через сумматор 8 модулей подключе- ны к вторым входам квантователя 4, первые-третьи выходы которого соединены с информационными входами соответственно первого 9 - третьего 11 блоков буферной памяти. Кодер также содержит первый 12 и второй 13 дешифраторы, первый 14 и второй 15 блоки коммутации, первые выходы которых подключены соответственно к первым и вторым информационным входам блока 16 кодирования, выход которого является выходом кодера.

Аналого-цифровой преобразователь (АЦП) 1 выполнен по известной схеме парал0

5

0

лельного аналого-цифрового преобразователя с кодирующей логикой на постоянной памяти. В блоке 2 множителей каждый элемент умножается на 1/п. Блок 2 может быть реализован на л ППЗУ, на каждый из которых поступает один элемент xi. В ППЗУ, в соответствии с зашитой программой умножения производится умножение xi на 1/п С целью повышения точности умножения блок 2 может быть реализован на D-регист- рах и нескольких схемах суммирования, по- зволяющих осуществить операцию умножения посредством суммирования соответствующих сигналов.

Первый 3 блок суммирования содержит собственно схемы суммирования, выполненные на логических элементах И, ИЛИ, НЕ. Для четырех одновременно кодируемых элементов блок 3 содержит три схемы суммирования: на первой складывается и

Х2ХЗХ4П

-на второй -jp и -jp и на третьей - суммы с первой и второй схем суммирования. Квантователь 4 содержит преобразова5 тель кодов, который может быть реализован на ППЗУ, и блоки задержки, которые могут быть выполнены, например, на D- триггерах или логических элементах. В пре- образователях производится грубое

Qравномерное квантование восьмиразрядного кода 32 в трехразрядный 32 по правилу 32 32/32, которое однозначно определяет таблицу перекодирования преобразователя кодов.

Узел 5 памяти включает в себя буферный регистр 26, первый счетчик 22 импульсов, второй счетчик 23 импульсов, преобразователь 24 кодов, мультиплексор 25иблок21 оперативной памяти,выполненный, например, на микросхеме 565РУ5. Для изображения 512x512 элементов первый 22 и второй 23 счетчики импульсов - восемнадцатиразрядные, т.е. формируется 18-разрядный адрес. Преобразователь 24 кодов

5 (например на РТ5) также является восемнадцатиразрядным. Мультиплексор 25 может быть выполнен на логических элементах И, ИЛИ, НЕ.

Второй блок 6 суммирования содержит

0 п схем суммирования. На i-ой схеме суммирования 0 1,п) производится вычисление суммы Xi с (-ai), т.е. вычисляется di xt - ai -xi + ai + 1, где зи поступает с выхода блока 7 инвертирования, представляющего собой

5 блок инверторов. Значения di передаются в сумматор 8 модулей, который для п 4 состоит из четырех схем ППЗУ и трех сумматоров. На i-ю схему ППЗУ поступает di, в которой зашита программа перевода d( из дополнительного в прямой код, т.е. по суще5

0

ству вычисление модуля di. На первой схеме суммирования складывается Idil и Id2l , на второй - Idal и Id4l , на третьей - суммы с выходов первого и второй схем суммирова1

ния, т.е. 32 тт 2 I xi - ai I. Вычислен i 1

ная сумма без младшего разряда (т.е. деленная на 2) подается на выход. Кроме того, на выход сумматора 8 модулей подает- ся матрица знаков, вычисляемая при определении модулей Ixrail. Коды ai, az и S поступают в квантователь 4.

Кодер сигнала изображения содержит первый 14 и второй 15 блоки коммутации, первые управляющие входы которых объединены, первые выходы второго блока 10 буферной памяти подключены к входам первого дешифратора 12, выход которого соединен с вторым управляющим входом второго блока 15 коммутации, Первые выходы третьего блока 11 буферной памяти под- ключены к первым информационным входам второго блока 15 коммутации. Первые информационные входы первого блока 14 коммутации подключены к первым выходам третьего блока 11 буферной памяти, вторые выходы которого соединены с вторыми информационными входами первого 14 и второго 15 блоков коммутации, вторые выходы которых подключены соответственно к третьим и четвертым информационным входам блока 16 кодирования. Третьи информационные входы первого блока 14 коммутации подключены к первым выходам второго блока 10 буферной памяти, вторые выходы которого соединены с третьими ин- формационныцми входами второго блока 15 коммутации и входами второго дешифратора 13. Первые выходы первого блока 9 бу- ферной памяти подключены к пятым информационным входам блока 16 кодирования и четвертым информационным входам второго блока 15 коммутации. Вторые выходы первого блока 9 буферной памяти соединены с шестыми информационными входами блока 16 кодирования и четвертыми информационными входами первого блока 14 коммутации, второй управляющий вход которого объединен с седьмым инфор- мационным входом блока 16 кодирования и подключен к выходу первого дешифратора 12. Выход второго дешифратора 13 соединен с первым управляющим входом второго блока 15 коммутации и восьмым и-нформационным входом блока 16 кодирования. Первый тактовый вход кодера сигнала изображения соединен с тактовым входом АЦП 1, тактовым входом узла 5 памяти, тактовым входом квантователя 4 и первыми

тактовыми входами первого 9, второго 10 и третьего 11 блоков буферной памяти, вторые тактовые входы которых соединены с первым тактовым входом блока 16 кодирования и с вторым тактовым входом кодера сигнала изображения, третий тактовый вход которого объединен с вторым тактовым входом блока 16 кодирования. Четвертый тактовый вход кодера сигнала изображения соединен с входом синхронизации узла 5 памяти.

Первый блок 9 буферной памяти содержит первый 27, второй 28 и третий 29 буферные регистры, представляющие собой три семиразрядных параллельных регистра. Входы первого 27 и третьего 29 регистра соединены между собой и подключены к первым выходам квантователя 4. Выход первого регистра 27 подключен к входам второго регистра 28. Первый регистр 27 тактируется частотой fraKT, а второй 28 и третий 29-частотой fraKT/2, что позволяет получить одновременно на выходах второго 28 и третьего 29 регистров коды аи и ац+1 средней яркости от последующей группы.

Второй блок 10 буферной памяти по устройству аналогичен первому с той лишь разницей, что вместо семиразрядных в нем используются двухразрядные регистры, Третий блок 11 буферной памяти по устройству аналогичен первому с той лишь разницей, что вместо семиразрядных в нем используются четырехразрядные параллельные регистры.

Дешифраторы 12 и 13 выполнены на элементах ИЛИ-2НЕ.

Первый блок 14 коммутации содержит первый 17 и второй 18 мультиплексоры, первые и вторые управляющие входы которых соответственно объединены и являются одноименными входами блока. Первые информационные входы первого 17 и второго 18 мультиплексоров соответственно объединены и являются третьими информационными входами блока 14. Вторые информационные входы второго мультиплексора 18 соответственно объединены с вторыми и третьими информационными входами первого мультиплексора 17 и являются четвертыми информационными входами блока 14. Четвертые информационные входы первого

17и третьи информационные входы второго

18мультиплексоров соответственно объединены и являются вторыми информационными входами блока 14. Четвертые информационные входы второго мультиплексора 18 являются первыми информационными входами блока 14. Выходы первого 17 и второго 18 мультиплексоров являются

соответственно первыми и вторыми выходами блока 14.

Второй блок 15 коммутации содержит перый 19 и второй 20 мультиплексоры, первые и вторые управляющие входы которых соответственно объединены и являются одноименными входами блока 15. Первые информационные входы первого 19 и второго 20 мультиплексора объединены и являются первыми входами второго блока 15 комму- тации, вторые информационные входы которого соединены с вторыми входами второго мультиплексора 20, третьи входы которого объединены с вторыми и третьими входами первого мультиплексора 19 и являются чет- вертыми информационными входами блока 15 коммутации, третьи информационные входы которого соединены с четвертыми входами первого 19 и второго 20 мультиплексоров, выходы которых являются пер- выми и вторыми выходами второго блока 15 коммутации,

Мультиплексоры 17 и 18 представляют собой два мультиплексора четыре в один, которые управляются двумя сигналами уп- равления. Мультиплексоры 19 и 20 аналогичны мультиплексорам 17 и 18.

Блок 16 кодирования содержит параллельно-последовательный D -регистр.

Управление блоками, входящими в ко- дер, осуществляется синхрогенератором(не показан). Синхрогенератор формирует следующие частоты: fT - тактовую, частоту группы fr/2, канальную TK,частоту полей fn.

Кодер сигнала изображения работает следующим образом.

Аналоговый телевизионный сигнал поступает на вход блока 1 АЦП, в котором преобрузуется в цифровой видеосигнал. В узле 5 памяти в результате задержки цифрового сигнала на время одного поля создается ряд цифровых сигналов, каждый из которых соответствует одному из элементов апертуры 2x2 элемента (т.е. группы сосед- них элементов изображения). После умножения в блоке 2 на весовые коэффициенты в первом блоке 3 суммирования вычисляется среднее значение яркости по кодируемой группе (коэффициент ai). Во втором блоке б суммирования из значения яркости каждого элемента группы вычисляется среднее значение яркости по группе (т.е. блоки 7 и 6 функционально образуют вычитатель). В сумматоре 8 модулей производится сложе- ние модулей разностей, полученных в блоке 6. Вычисленная сумма без младшего разряда (т.е. деленная на 2) подается на выход. Кроме того, на выход сумматора 8 модулей подается матрица знаков, вычисляемая при

определении модулей lxi-ail. Коды ai, 32 и 3 поступают в квантователь.

С первых выходов квантователя 4 семиразрядный код ai подается на входы первого блока 9 буферной памяти. С вторых выходов квантователя 4 двухразрядный код 32 подается на входы второго блока 10 буферной памяти, с третьих выходов квантователя 4 четырехразрядный код S подается на входы третьего блока 11 буферной памяти.

Первый блок 9 буферной памяти содержит три семиразрядных параллельных буферных регистре. Входы первого и третьего буферного регистров соединены между собой и являются входами первого блока 9 буферной памяти. Выходы первого буферного регистра подключены к входам второго буферного регистра. Выходы второго и третьего буферного регистра являются выходами первого блока 9 буферной памяти. Первый и второй буферные регистры тактируются частотой fr, а третьи - частотой fT/2. Код ai поступэет на входы первого и третьего регистров. Импульсами тактовой частоты код ai переписывается из первого буферного регистра во второй. На выходе второго буферного регистра код аи будет только через время, равное двум периодам тактовой частоты. За это время вычисляются другие параметры кодируемой группы, т.е. ац-ц, 32i+i, SH-L Код ац+1 подается на входы первого и третьего буферных регистров в тот момент, когда код аи присутствует на входах второго буферного регистра. Импульсами с частотой ттакт код aii и импульсами с частотой fr/2 код ац+1 одновременно переписывается на выходы второго и третьего регистров, т.е. на двух выходах первого 9 и блока буферной памяти присутствуют семиразрядные коды ац и ац+1 от следующей кодируемой группы.

Аналогично первому блоку 9 буферной памяти работают второй 10 и третий 11 блоки буферной памяти. На двух двухразрядных выходах второго блока 10 буферной памяти присутствуют одновременно коды 32 | и 32 ,., . На двух четырехразрядных выходах третьего блока 11 буферной памяти присутствуют одновременно коды Si и S(+i.

В первом 12 и втором 13 дешифраторах осуществляется анализ того фрагмента изображения, к которому принадлежит группа кодируемых элементов. На входы этих дешифраторов подаются коды 32 ;и 32 , +,. Если кодируемые группы принадлежат к равнояркостному участку изображения, т.е. все элементы в группе 2x2 равны между собой, то значения 32 | и аа j,f равны нулю и

сигналы на выходах дешифраторов 12 и 13

нули. Если кодируемые группы принадлежат текстурному участку, то для таких групп значения аа (И 32 j, отличны от нуля и сигналы на выходах дешифраторов 12 и 13 единицы. Если фрагмент изображения соответствует переходу от равнояркостного участка к контуру, то для группы равнояркостного участка 32 ( 0, а для группы, соответствующей контуру, Э21г1 0. Сигналы на

выходе дешифратора 12 - О, на выходе дешифратора 13 - 1. Если фрагмент изображения соответствует переходу от контура к равнояркостному участку, то 32j 0; 32 -f f 0 и сигналы на выходах дешифрато-

ров 12 и 13 - 1 и О соответственно.

Таким образом, комбинация выходных или управляющих сигналов дешифраторов определяет тип кодируемого фрагмента. Если комбинация управляющих сигналов 00, то кодируемый фрагмент соответствует равнояркостному участку или участку с плавным изменением яркости. Если комбинация управляющих сигналов 11, то кодируемый фрагмент соответствует текстуре, и если комбинация управляющих сигналов 01 или 10, то кодируемый фрагмент соответствует переходу равнояркостный участок - контур или контур - равнояркостный участок.

С вторых выходов первого блока 9 буферной памяти семиразрядный код a ai;

подается следующим образом: три старших разряда кода аи подаются на четвертые вход блока 16 кодирования, а четыре разряда подаются на пятые входы первого блока 14 коммутации. В блоке 14 коммутации два младших разряда кода ai | подаются на

вторые входы второго мультиплексора 18, а два оставшихся разряда подаются на вторые и третьи входы первого мультиплексора 17.

С первых выходов первого блока 9 буферной памяти . семиразрядный код aii+i

подается следующим образом: три старших разряда кода ai i+1 подаются на третьи

входы блока 16 кодирования, а четыре разряда подаются на четвертые входы второго блока 15 коммутации. В блоке 15 коммутации два младших разряда кода ai ,4-- подаются на четвертые входы второго мультиплексора 20, а два оставшиеся разряда подаются на третьи и четвертые входы первого 19 мультиплексора.

Управляющий бит с выхода первого 12 дешифратора подается на первый вход первого блока 14 коммутации, на пятый вход второго блока 15 коммутации и на пятыми

5

д

5

0

0

5

п 5

вход блока 16 кодирования. В блоках 14 и 15 коммутации управляющий бит подается на первые входы мультиплексоров 17-20.

Управляющий бит с выхода дешифратора 13 подается на второй вход второго блока

15коммутации, на четвертый вход первого блока 14 коммутации и на второй вход блока

16кодирования. В блоках 14 и 15 коммутации этот управляющий бит подается на вторые входы мультиплексоров 17-20.

С первых выходов второго 10 блока буферной памяти двухразрядный код 32j подается на третьи входы первого блока 14 коммутации. В этом блоке двухразрядный код 32 | подается на первые входы первого

17мультиплексора и на первые входы второго мультиплексора 18.

С вторых выходов второго блока 10 буферной памяти двухразрядный код a a2i-)-1

подается на третьи входы второго блока 15 коммутации. В этом блоке двухразрядный код аа j-f,) подается на первые входы первого мультиплексора 19 и на первые входы второго мультиплексора 20.

С первых выходов третьего блока 11 буферной памяти четырехразрядный код Si подается на первые входы второго блока 15 коммутации. Два разряда из четырехразрядного кода Si подаются на вторые входы первого блока 14 коммутации. В блоке 14 коммутации два разряда кода Si подаются на четвертые входы первого мультиплексора 17 и эти же разряды кода Si подаются на вторые входы второго 20 мультиплексора второго блока 15 коммутации. Два других разряда кода Si в блоке 15 коммутации подаются на вторые входы первого мультиплексора 19.

С вторых выходов третьего блока 11 буферной памяти четырехразрядный код Si+щодается на вторые входы первого блока 14 коммутации. Два разряда из четырехразрядного кода Зн-1 подаются на вторые входы второго блока 15 коммутации. В блоке 15 коммутации два разряда кода Si+i подаются на третьи входы второго мультиплексора 20 и эти же разряды кода Sj-м подаются на вторые и третьи входы второго мультиплексора 18 первого блока 14 коммутации. Два других разряда кода Si+i в блоке 14 коммутации подаются на четвертые входы первого мультиплексора 17.

Структура выходного кодового слова кодера сигнала изображения зависит от типа кодируемого фрагмента изображения. Если кодируемый фрагмент представляет собой текстуру, то в двух соседних группах 2x2 коды 32 ,и 32 j-f- отличны от нуля. Управляющие сигналы на выходах дешифраторов 12

и . Комбинация управляющих сигналов 11 скоммутирует на первые выходы первого блока 14 коммутации два разряда кода 32| путем коммутации на выходы первого мультиплексора 17 его первых входов. На вторые выходы блока 14 комбинацией 11 коммутруются два разряда кода Si путем коммутации на выходы второго мультиплексора 18 его четвертых входов.

Комбинация управляющих сигналов 11 коммутирует на вторые выходы второго блока 15 коммутации два разряда кода 32 i + 1 путем коммутации на выходы первого мультиплексора 19 его первых входов. На первые выходы блока 15 комбинацией 11 коммутируются два разряда кода Si+1 путем коммутации на выходы второго мультиплексора 20 его третьих входов.

Таким образом, если кодируемый фрагмент представляет собой текстуру, то ai| - средняя яркость кодируемой группы - представляется тремя разрядами; aai - отклонение от средней яркости - представляется двумя разрядами; Si - матрица знаков - представляется двумя разрядами. Для соседней группы ai j + i представляется тремя разрядами; 32 i + 1 - двумя разрядами; Si+1 - двумя разрядами.

Если кодируемый фрагмент представляет собой равнояркостный участок или участок с плавным изменением яркости, то в двух соседних группах 2x2 коды Э2| и 321 +1 равны нулю. Управляющие сигналы на выходах дешифраторов 12 и 13 - О. Комбинация управляющих сигналов 00 коммутирует на первые выходы первого блока 14 коммутации два разряда кода aij путем коммутации на выходы первого мультиплексора 17 его третьих входов. На вторые выходы блока 14 комбинацией 00 коммутируются два младших разряда кода aij путем коммутации на выходы второго мультиплексора 18 его вторых входов.

Комбинация управляющих сигналов 00 коммутирует на вторые выходы второго блока 15 коммутации два разряда кода ац+1 путем коммутации на выходы первого мультиплексора 19 его четвертых входов. На первые выходы блока 15 комбинацией 00 коммутируются два младших разряда кода 311 + 1 путем коммутации нэ выходы второго мультиплексора 20 его четвертых входов.

Таким образом, если кодируемый фрагмент представляет участок с плавным изме- нением яркости или равнояркостный участок, то aij - средняя яркость кодируе0

5

0

5

0

5

0

5

0

5

мой группы - представляется семью разрядами и 311 +1 - семью разрядами.

Если кодируемый фрагмент представляет собой переход от равнояркостного участка к контуру, т.е. одна кодируемая группа принадлежит к равнояркостному участку, а другая группа - к контуру, то в первой группе а2| 0,а во второй Э2| + 1 - 0. Управляющий сигнал на выходе дешифратора 12 - О, на выходе дешифратора 13 - 1. Комбинация управляющих сигналов 01 ком мути pyei на первые выходы первого блока 14 коммутации два разряда кода Si+1, путем коммутации на выходы первого мультиплексора 17 его четвертых входов. На вторые выходы блока 14 комбинацией 01 коммутируются два других разряда кода Si-и путем коммутации на выходы второго мультиплексора 18 его третьих входов.

Комбинация управляющих сигналов 01 коммутирует на вторые выходы второго блока 15 коммутации два разряда кода ai i + 1 путем коммутации на выходы первого мультиплексора 19 его третьих входов. На первые выходы блока 15 коммутации комбинацией 01 коммутируются два рязряда кода Э21+1 путем коммутации на выходы второго мультиплексора 20 его первых входов.

Таким образом, если кодируемый фрагмент представляет собой переход от равно- яркостного участка к контуру, то для равнояркостного участкэ aij представляется тремя разрядами, а для группы контура - ai | + 1 пятью разрядами; a2j +1 - двумя разрядами; ; SI-H - четырьмя разрядами, что позволяет более точно1 кодировать контуры.

Если кодируемый фрагмент представляет собой переход от контура к равнояркостному участку, т.е. одна кодируемая группа принадлежит к контуру, а другая группа - к равнояркостному участку, то в первой группе Э2, 0- а во второй 32 i + i 0. Управляющий сигнал на выходе дешифратора , на выходе дешифратора 13 - О. Комбинация управляющих сигналов 10 коммутирует на первые выходы первого блока 14 коммутации два разряда кода aij путем коммутации на выходы первого мультиплексора 17 его вторых входов. На вторые выходы блока 14 комбинация 10 коммутирует два разряда кода Э2| путем коммутации на выходы второго 18 мультиплексорэ его первых входов.

Комбинэция управляющих сигналов 10 коммутирует на вторые выходы второго блока 15 коммутации два разряда кода

Si путем коммутации на выходы первого мультиплексора 19 его вторых входов. На первые выходы блока 15 коммутации комбинацией 10 коммутируются два разряда кода Si путем коммутации на выходы второго мультиплексора 20 его первых входов.

Таким образом, если кодируемый фрагмент представляет собой переход от контура к равнояркостному участку, то для группы контура аи представляется пятью разряда- ми, ааг двумя разрядами, Si - четырьмя разрядами, а для группы равнояркостного участка представляется тремя разрядами.

В блоке 16 кодирования параллельный код, поступающий на его восемь входов, сворачивается в последовательн ый и выдается на выход кодера побитно.

При реализации предлагаемого устройства, соответствующего случаю внутрикад- рового кодирования групп 2x2 элемента, расход цифрового потока на информацию об одном элементе составляет 2 бита на элемент. По сравнению с прототипом выигрыш в сжатии потока составляет 1 бит/элемент. Стоимость изготовления предлагаемого устройства практически не отличается от стоимости кодера-прототипа, поскольку эффект достигается в результате введения новых связей. При этом стоимость окупается тем выигрышем в дорогостоящей пропускной способности канала связи, который достигается в результате уменьшения потока видеоданных.

Формула изобретения

являются соответственно первыми и вторыми выходами блока.

7

4Г7Л+

i

V

k и ч i i ii

Ґ

14 Ц 4

19

VV

.

i3

Фиг 3

a

18

v

11

15

ii

20

П

L

26

21

21

ff

L JT

Z1

28

Фие,4

7

29

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Устройство для кодирования телевизионного сигнала | 1989 |

|

SU1662001A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-30—Публикация

1990-04-17—Подача