Изобретение относится к электросвязи и может использоваться для приема дискретных сигналов, передаваемых по каналам связи со скоростью 2400 бит/с.

Наиболее близким к изобретению по технической сущности является цифровое устройство приема сигналов, содержащее блок вычисления ошибок, усилитель с АРУ, фазовращатель АЦП, адаптивный корректор, блок регулирования уровня, блок демодуляции и компенсации фазы, решающий блок и декодер.

Недостатком приемника цифрового адаптивного устройства преобразования сигналов является невозможность когерентного приема дискретных сигналов с "вращающейся фазой", используемых при передаче данных на скорости 2400 бит/с.

Задачей изобретения является расширение функциональных возможностей при работе на скорости 2400 бит/с.

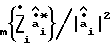

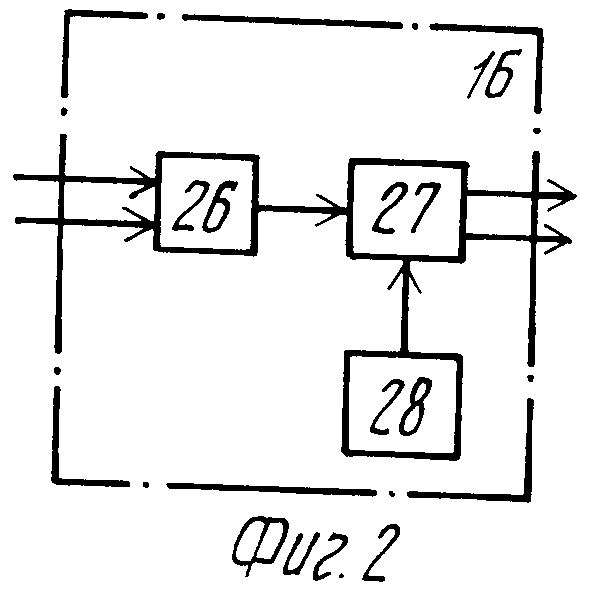

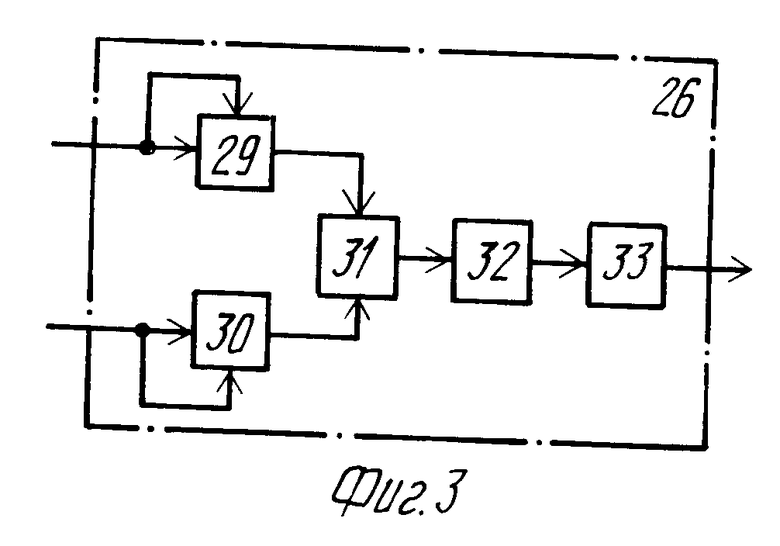

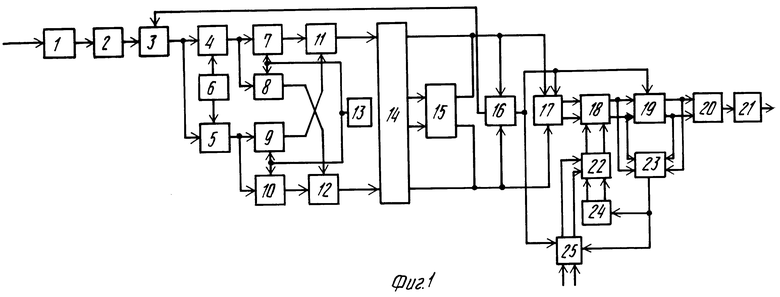

На фиг.1 изображена структурная электрическая схема цифрового приемника; на фиг. 2 схема блока выделения синхросигналов; на фиг.3 схема блока выделения тактовой частоты; на фиг.4а и б схемы коммутации несущей и фазового манипулятора соответственно.

Цифровой приемник дискретных сигналов с "вращающейся фазой" содержит полосовой фильтр 1, усилитель 2 с автоматической регулировкой уровня 2, аналого-цифровой преобразователь 3, первый и второй умножители 4 и 5, генератор 6, первый, второй, третий и четвертый фильтры нижних частот (ФНЧ) 7-10, первый и второй сумматоры 11 и 12, формирователь 13 сигнала коррекции фазы, блок 14 коммутации, преобразователь 15 сигнала с линейной частотной модуляцией, блок 16 выделения синхросигналов, адаптивный корректор 17, фазовращатель 18, решающий блок 19, декодер 20, дескремблер 21, фазовый манипулятор 22, блок 23 вычисления фазовой ошибки, блок 24 подстройки фазы несущего колебания и блок 25 коммутации несущей.

Блок 16 выделения синхросигналов содержит блок 26 выделения тактовой частоты, блок 27 подстройки такта и опорный генератор 28.

Блок 26 выделения тактовой частоты содержит первый и второй умножители 29 и 30, сумматор 31, полосовой фильтр 32 и компаратор 33.

Блок 25 коммутации несущей содержит первый ключ 34, компаратор 35, элемент И 36, триггер 37, второй, третий и четвертый ключи 38-40.

Фазовый манипулятор 22 содержит первый, второй, третий и четвертый умножители 41-44 и первый и второй сумматоры 45 и 46.

Цифровой приемник работает следующим образом.

При передаче данных по каналам тональной частоты (ТЧ) со скоростями 1200 и 2400 бит/с используются два вида фазоманипулированных сигналов: вариант А, при котором разность фаз между соседними посылками кратна π на скорости 1200 бит/с и π/2 при скорости 2400 бит/с, и вариант В с разностью фаз, кратной π /2, на скорости 1200 бит/с и π /4 на скорости 2400 бит/с. Сигналы вида В получили в литературе название сигналов с "вращающейся фазой" и используются при работе по каналам ТЧ ухудшенного качества с целью поддержания более стабильной работы системы тактовой синхронизации приемника дискретных сигналов.

Фазоманипулированный сигнал при скорости передачи 1200 бит/с можно представить следующим образом:

1. При варианте манипуляции А

Si Acos t+iπ+π

t+iπ+π  ηj(m)+ϕ(t)

ηj(m)+ϕ(t) , (1) где ωo круговая несущая частота;

, (1) где ωo круговая несущая частота;

ϕ(t) изменение фазы сигнала, вызванное его прохождением по каналу связи;

η(m) коэффициент, принимающий в данном случае значение 0,1.

2. При варианте манипуляции В

Si Acos t+i1

t+i1 +π

+π  (m)+

(m)+  + ϕ(t)

+ ϕ(t) . (2)

. (2)

Сравнивая (1) и (2) видим, что в структуре сигнала по варианту В появляется вращающаяся компонента i π/2, не несущая полезной информации, которую следует устранить в приемнике. При когерентном методе приема сигналов вида (1) и (2) в цифровом приемнике необходимо сформировать опорные колебания expj[ ωot+iπ+ϕ(t) для детектирования сигналов по варианту А и

expj t+i1

t+i1 + i

+ i +ϕ(t)

+ϕ(t) по варианту В.

по варианту В.

Из последнего выражения видно, что для приема сигналов с вариантом В манипуляции фазу опорного колебания в приемнике необходимо вращать на угол i π/2. Аналогичным образом можно показать, что при приеме сигналов со скоростью 2400 бит/с, манипулированных по варианту В, фазу опорного колебания в приемнике необходимо вращать на угол, кратный i π/4.

Вращение фазы опорного колебания в приемнике осуществляется вначале не каждый такт, а только по разрешающему сигналу Ui, полученному в результате вычисления разности фаз принимаемого и опорного колебания Δϕ равной для скорости 1200 бит/с (вариант В) следующей величине:

Δϕi=  i1

i1 -i

-i +

+ ηj(m). (3)

ηj(m). (3)

С другой стороны, фазовую ошибку, вычисляемую в цифровом приемнике дискретных сигналов, можно записать следующим образом:

sinΔϕi= I , (4) где Im{·} операция выделения мнимой части произведения;

, (4) где Im{·} операция выделения мнимой части произведения; комплексный сигнал на входе решающего блока приемника;

комплексный сигнал на входе решающего блока приемника; комплексно-сопряженная оценка сигнала на выходе решающего блока приемника.

комплексно-сопряженная оценка сигнала на выходе решающего блока приемника.

Из (3) и (4) следует равенство sin

sin i1

i1 i

i +

+  ηj(m)

ηj(m) . (5)

. (5)

В зависимости от соотношения фаз принимаемого и опорного колебаний Δϕi может принимать значения, кратные K1 π/2, где К1 0,1,2,3 для сигналов на скорости 1200 бит/с, манипулированных по варианту В, и кратные К2 π /4, где К2 0,1,7 для сигналов варианта В на скорости 2400 бит/с.

Тогда из (5) получаем следующий алгоритм формирования разрешающего сигнала Ui:

для сигналов со скоростью 1200 бит/с

Ui=

(6)

(6)

для сигналов со скоростью 2400 бит/с

Ui=

(7)

(7)

Рассмотренный выше алгоритм приема сигналов с "вращающейся фазой" реализован в предлагаемом устройстве.

Цифровой приемник работает следующим образом.

Поступающий из канала ТЧ фазоманипулированный сигнал фильтруется полосовым фильтром 1, затем усиливается усилителем 2 с автоматической регулировкой уровня до номинального значения и преобразуется в аналого-цифровом преобразователе 3 в цифровую форму. Цифровые отсчеты принимаемого сигнала с частотой mfтч (fтч тактовая частота приемника), вырабатываемой блоком 16 выделения синхросигналов, поступают на синхронный демодулятор, выполненный на первом 4 и втором 5 умножителях, генераторе 6, четырех ФНЧ 7-10, первом 11 и втором 12 сумматорах.

ФНЧ 7-10 представляют собой цифровые нерекурсивные фильтры, значения импульсных характеристик которых записаны в формирователь 13 сигнала коррекции фазы. ФНЧ 7-10 помимо последетекторной фильтрации выполняют функции компромиссного корректора неравномерности ГВЗ канала ТЧ.

Комплексная огибающая принимаемого сигнала в виде реальной составляющей на выходе сумматора 11 и мнимой составляющей на выходе сумматора 12 поступает на блок 14 коммутации, который в данном случае переключает входные сигналы соответственно на первый и четвертый выходы, подавая их тем самым на вход адаптивного корректора 17. Откоppектированные отсчеты реальной и мнимой составляющих принимаемого с частотой fтч с выхода адаптивного корректора 17 поступают соответственно на первый и второй входы фазовращателя 18, представляющего собой комплексный умножитель, построенный по структуре, аналогичной фазовому манипулятору 22. На третий и четвертый входы фазовращателя 18 подается определенным образом сформированное опорное колебание с выходов фазового манипулятора 22. Откорректированный по фазе сигнал поступает с выходов фазовращателя в виде двух составляющих на второй и третий входы решающего блока 19, представляющего собой пороговую схему в которой по отсчетам входных сигналов выносится решение о принятии того или иного информационного символа  .

.

Сигналы с выхода фазовращателя 18 поступают также на первый и второй входы блока 22 вычисления фазовой ошибки, на третий и четвертый входы которого одновременно приходят отсчеты  с выхода решающего блока 19.

с выхода решающего блока 19.

Блок 23 вычисления фазовой ошибки реализует алгоритм (4) оценки фазового рассогласования принимаемого и опорного колебаний. Полученная в блоке 23 вычисления фазовой ошибки оценка фазового рассогласования Δϕi подается в блок 24 подстройки фазы несущего колебания, реализующего алгоритм =

=  -γ1Δϕi-

-γ1Δϕi- (8) подстройки текущей фазы опорного колебания и алгоритм преобразования

(8) подстройки текущей фазы опорного колебания и алгоритм преобразования  ⇒ expj

⇒ expj  , осуществляемого, например, с помощью постоянного запоминающего устройства, входящего в состав блока 24 подстройки фазы несущего колебания.

, осуществляемого, например, с помощью постоянного запоминающего устройства, входящего в состав блока 24 подстройки фазы несущего колебания.

Ошибка фазового рассогласования с выхода блока 23 вычисления фазовой ошибки подается также на второй вход блока 25 коммутации несущей, в котором она поступает на вход компаратора 35, на второй вход которого с выхода ключа 34 подается пороговое напряжение Un1 или Un2 в зависимости от выбранной скорости работы приемника 1200 или 2400 бит/с. Коммутация первого ключа осуществляется логическими сигналами, поступающими на третий вход блока 25 коммутации несущей. В компараторе 35 осуществляется алгоритм сравнения фазовой ошибки с порогом и формирования разрешающего сигнала Ui в соответствии с выражениями (6) или (7). В зависимости от результатов сравнения на выходе компаратора 35 появляется сигнал логической "1" или логического "0", который подается на вход элемента И 36, на второй вход которого подаются импульсы тактовой частоты, привязанные к моментам манипуляции в принимаемом сигнале. Тактовая частота поступает с второго выхода блока 16 выделения синхросигналов. На третий вход элемента И 36 с четвертого входа блока 25 коммутации несущей подается логический "0", разрешающий прием сигналов, манипулированных по варианту В.

Разрешающий сигнал Ui, привязанный к моментам манипуляции в принимаемом сигнале, с выхода элемента И 36 подается на счетный вход С триггера 37. Значение разрешающего сигнала Ui определяется по алгоритму, описываемому выражениями (6) и (7). Если, например, при скорости передачи 1200 бит/с I

, т.е. если в i-ый момент времени разность фаз между принимаемый и опорным сигналами в приемнике близка к k π, соотношение (5), т.е. другими словами, если в i-ый тактовый момент времени фазы принимаемого и опорного сигнала совпадают с точностью до π то на выходе элемента И 36 формируется разрешающий сигнал Ui 1, по которому перебрасывается триггер 37, переключая сигналами с первого и второго выходов ключи 38 и 39 таким образом, чтобы на выходе ключа 38 присутствовал логический "0", а на выходе ключа 39 логическая "1", поступающие на их второй и третий входы соответственно с первого и второго выходов ключа 40. Одновременно на третий и четвертый входы фазового манипулятора 22 с выходов блока 24 подстройки фазы несущего колебания подается сигнал вида expj

, т.е. если в i-ый момент времени разность фаз между принимаемый и опорным сигналами в приемнике близка к k π, соотношение (5), т.е. другими словами, если в i-ый тактовый момент времени фазы принимаемого и опорного сигнала совпадают с точностью до π то на выходе элемента И 36 формируется разрешающий сигнал Ui 1, по которому перебрасывается триггер 37, переключая сигналами с первого и второго выходов ключи 38 и 39 таким образом, чтобы на выходе ключа 38 присутствовал логический "0", а на выходе ключа 39 логическая "1", поступающие на их второй и третий входы соответственно с первого и второго выходов ключа 40. Одновременно на третий и четвертый входы фазового манипулятора 22 с выходов блока 24 подстройки фазы несущего колебания подается сигнал вида expj = cos

= cos +jsin

+jsin . Предположим, что до момента прихода разрешающего сигнала Ui ключи 38 и 39 находились в таком положении, что на первом выходе блока 25 коммутации несущей и соответственно на первом входе фазового манипулятора 22 была логическая "1", на втором выходе блока 25 коммутации несущей и соответственно на втором входе фазового манипулятора 22 был логический "0". Тогда сигнал на выходе сумматора 45 фазового манипулятора 22 был бы пропорционален cos cos

. Предположим, что до момента прихода разрешающего сигнала Ui ключи 38 и 39 находились в таком положении, что на первом выходе блока 25 коммутации несущей и соответственно на первом входе фазового манипулятора 22 была логическая "1", на втором выходе блока 25 коммутации несущей и соответственно на втором входе фазового манипулятора 22 был логический "0". Тогда сигнал на выходе сумматора 45 фазового манипулятора 22 был бы пропорционален cos cos а на выходе сумматора 46 пропоpционален sin sin

а на выходе сумматора 46 пропоpционален sin sin

При переключении триггера 37 (Ui 1) сигнал на первом входе фазового манипулятора 22 становится равным логическому "0", а на втором входе логической "1". При этом сигнал на выходе сумматора 45 фазового манипулятора 22 будет пропорционален sin sin а на выходе сумматора 46 cos cos

а на выходе сумматора 46 cos cos т.е. произойдет поворот фазы опорного колебания, подаваемого на третий и четвертый входы фазовращателя 18, на π /2. Далее данный процесс будет автоматически повторяться, осуществляя тем самым вращение фазы опорного колебания в приемнике на угол, кратный π /2.

т.е. произойдет поворот фазы опорного колебания, подаваемого на третий и четвертый входы фазовращателя 18, на π /2. Далее данный процесс будет автоматически повторяться, осуществляя тем самым вращение фазы опорного колебания в приемнике на угол, кратный π /2.

Если же в i-ый тактовый момент I

±1, т.е. если разность фаз в i-ый момент времени между принимаемым и опорным колебаниями кратна π /2, то разрешающий сигнал на выходе элемента И 36 не появляется (логический "0"), триггер 37 не перебрасывается и соответственно ключи 38 и 39 остаются в исходном положении, сохраняя тем самым логическую "1" на первом входе фазового манипулятора 22 и логический "0" на его втором входе. Поворота фазы опорного колебания в данном случае не происходит.

±1, т.е. если разность фаз в i-ый момент времени между принимаемым и опорным колебаниями кратна π /2, то разрешающий сигнал на выходе элемента И 36 не появляется (логический "0"), триггер 37 не перебрасывается и соответственно ключи 38 и 39 остаются в исходном положении, сохраняя тем самым логическую "1" на первом входе фазового манипулятора 22 и логический "0" на его втором входе. Поворота фазы опорного колебания в данном случае не происходит.

Аналогичным образом предлагаемое устройство функционирует при скорости передачи 2400 бит/с.

Отличием от рассмотренного выше алгоритма в данном случае является сравнение фазовой ошибки с пороговым напряжением, равным в компараторе 35, и подача на входы ключей 38 и 39 напряжений, пропорциональных величине 0,707, которые поступают с выходов ключа 40 при его замыкании.

Для получения в приемнике импульсов тактовой частоты, приведенных к моментам манипуляции в принимаемом сигнале, служит блок 16 выделения синхросигналов, который работает следующим образом.

Реальная и мнимая составляющие комплексной огибающей принимаемого сигнала подаются на первый и второй входы блока 26 выделения тактовой частоты, в котором они возводятся в квадрат в умножителях 29 и 30 и складываются друг с другом, формируя таким образом на выходе сумматора 31 квадрат модуля комплексной огибающей. В спектре комплексной огибающей принимаемого сигнала содержится составляющая с частотой, равной тактовой, которая выделяется полосовым фильтром 32 и подается на компаратор 33, формирующий на своем выходе прямоугольные импульсы принимаемой тактовой частоты. Выделенные импульсы тактовой частоты подаются на первый вход блока 27 подстройки такта, на второй вход которого подаются импульсы высокой частоты с выхода опорного генератора 28. Блок 27 подстройки такта представляет собой дискретную систему фазовой автоподстройки частоты с импульсным управлением сигналами добавления и вычитания, в которой в качестве эталонного колебания используется выделенная из принимаемого сигнала тактовая частота.

Импульсы подстроенной под принимаемый сигнал тактовой частоты с второго выхода блока 16 выделения синхросигналов подаются в блок 25 коммутации несущей, привязывая тем самым разрешающий сигнал Ui к моментам манипуляции в принимаемом сигнале. Помимо этого импульсы с частотой mfтч (m 5-8) с первого выхода блока 16 выделения синхросигналов подаются на второй вход аналого-цифрового преобразователя 3 для дискретизации принимаемого сигнала при его преобразования в цифровой вид.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ АДАПТИВНЫЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2039416C1 |

| ЛИНИЯ РАДИОСВЯЗИ С ПОВТОРНЫМ ИСПОЛЬЗОВАНИЕМ ЧАСТОТЫ | 1999 |

|

RU2160506C2 |

| ЛИНИЯ РАДИОСВЯЗИ | 2002 |

|

RU2219660C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1987 |

|

SU1840226A1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ С ПОВЫШЕННОЙ ИНФОРМАЦИОННОЙ СКРЫТНОСТЬЮ | 1992 |

|

RU2033692C1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

| РАДИОЛИНИЯ СВЯЗИ С ПРОСТРАНСТВЕННЫМ РАЗДЕЛЕНИЕМ СИГНАЛА | 1999 |

|

RU2149506C1 |

| СИСТЕМА РАДИОСВЯЗИ | 1998 |

|

RU2150175C1 |

| ЛИНИЯ РАДИОСВЯЗИ | 1999 |

|

RU2160503C2 |

Использование: в электросвязи. Сущность изобретения: цифровой приемник содержит полосовой фильтр 1, усилитель 2 с АРУ, аналого-цифровой преобразователь 3, умножители 4 и 5, генератор 6, фильтры 7 - 10 низких частот, сумматоры 11 и 12, формирователь 13 сигнала коррекции фазы, блок 14 коммутации, преобразователь 15 сигнала с линейной частотной модуляцией, блок 16 выделения синхросигналов, адаптивный корректор 17, фазовращатель 18, решающий блок 19, декодер 20, дескремблер 21, фазовый манипулятор 22, блок 23 вычисления фазовой ошибки, блок 24 подстройки фазы несущего колебания и блок 25 коммутации несущей. 4 з.п. ф-лы, 4 ил.

| Цифровое устройство приема сигналов | 1986 |

|

SU1392629A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-06-27—Публикация

1991-07-02—Подача