Изобретение относится к области радиотехники и может быть использовано в широкополосных системах связи.

Известна схема следящего приемника широкополосного сигнала Г.И.Тузов Статистическая теория приема сложных сигналов. М.: Советское радио, 1977, с. 229 рис. 4.23. В этом приемнике назначение фазовращателя -первоначальное совмещение функций g(t - τ ), задежанной опорной последовательности с g(t - τo) модулирующей функцией. Ошибка фильтрации фазы этой системы равна

Ошибка в оценке задержки этой схемы составит

στ = (τи/n)σθ,

где τи - длительность элементарного импульса;

n - количество двоичных знаков информации;

στ, σθ - ошибки фильтрации для рассматриваемого сигнала.

Столь высокая точность оценки задержки объясняется тем, что в этой схеме ошибка запаздывания оценивается не по модулирующей функции, а по высокочастотному заполнению сигнала. Однако известно, что при оценке запаздывания по высокочастотному заполнению неизбежна неоднозначность отсчета. Огибавшая дискриминационной характеристики повторяет автокорреляционную функцию кода и имеет размах 2τи. А так как высокочастотное заполнение дискриминационной характеристики содержит 2n периодов несущего колебания, то имеется 2n точек устойчивого равновесия.

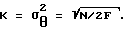

При этом, если переходный процесс завершился в точке б (см. фиг. 1) этой характеристики, то образуется статическая ошибка τcт, которая практически всегда будет больше среднеквадратического значения. Поэтому для рассматриваемого приемника статические ошибки по задержке будут определяющими (см.Г.И. Тузов Статистическая теория приема сложных сигналов. рис. 4.8 с. 190, рис. 4.16 с. 205, рис. 4.19 с. 212, рис. 4.20 с. 213, рис, 4.24 с. 234, рис. 4.25 с. 237).

Чтобы оценить величину статической ошибки, может быть использован обычный дискриминатор для модулирующей функции рассматриваемого сигнала, а для ее компенсации - цепочка, состоящая из интегратора и фазовращателя. На выходе синхронного детектора образуется модулирующая функция, которая поступает на дискриминатор задержки. Далее включен интегратор, выходное напряжение которого подается на управляемый фазовращатель.

Но этот приемник обладает существенными недостатками:

- при переходе из поиска в слежение он не работает, так как величина и знак измеряемого рассогласования копии и принимаемого сигнала зависит не только от самого рассогласования, а и от фазы несущего колебания, т.е. при ошибке равный 0 поступает команда - точно, при ошибке равной π - наоборот, при ошибке π/2 - команды нет. Все это равновероятно.

Таким образом, до срабатывания кольца фазовой автоподстройки работа временной подстройки не возможна, так как команды на подстройку по времени "произвольны";

- еще одним существенным недостатком данного приемника является то, что он работоспособен только в частном случае, когда fп.ч. = fнес., т.e, прием ведется по методу прямого усиления, но все современные приемники супергетеродинные и для них это равенство не выполняется.

Обработка сигнала на промежуточной частоте fп.ч. обуславливает тот факт, что для получения колебания с частотой fтак из гармонического колебания на промежуточной частоте fп.ч., необходимо его поделить на коэффициент К:

K =fп.ч./fтак..

С другой стороны, рассогласование по частотам между приемником и передатчиком, образовавшееся на несущей частоте, переносится на промежуточную. По этой причине относительный уход на частоте fп.ч. больше, чем на несущей в fнес/fп.ч. раза и для компенсации этого ухода должно быть в

К1 = fнес./fтак.,

т.е. K1 = К,

кроме fнес. = fп.ч..

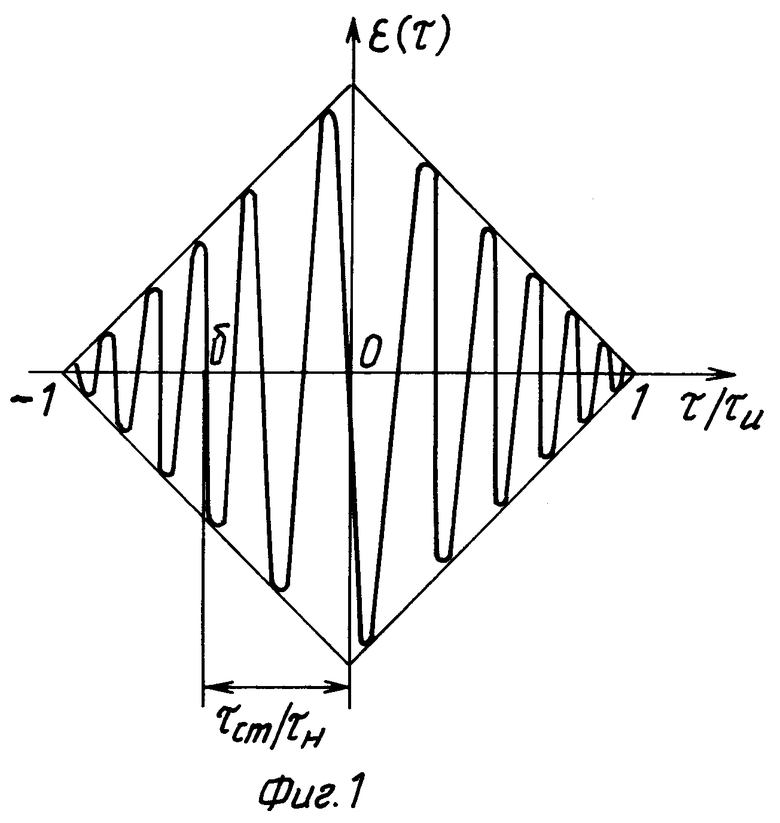

Наиболее близким к заявляемому является следящий приемник широкополосного сигнала, изображенный на рис. 4.18 с. 211 монографии Г.И.Тузова Статистическая теория приема сложных сигналов. М.: Советское радио, 1977. Структурная схема приемника-прототипа приведена на фиг. 2, где введены следующие обозначения:

1 - 5 - перемножители;

6 - фазовращатель на π/2;;

7, 11 - фильтры низкой частоты (ФНЧ);

8 - сумматор;

9, 12 - управляющие элементы;

10 - управляемый генератор;

13 - управляемый тактовый генератор;

14 - регистр сдвига генератора кода.

Генератор копий выполнен на основе регистра сдвига и совмещает в себе функции генератора и регистра сдвига, такое устройство в монографии Г.И.Тузова названо регистром сдвига генератора кода (с.185).

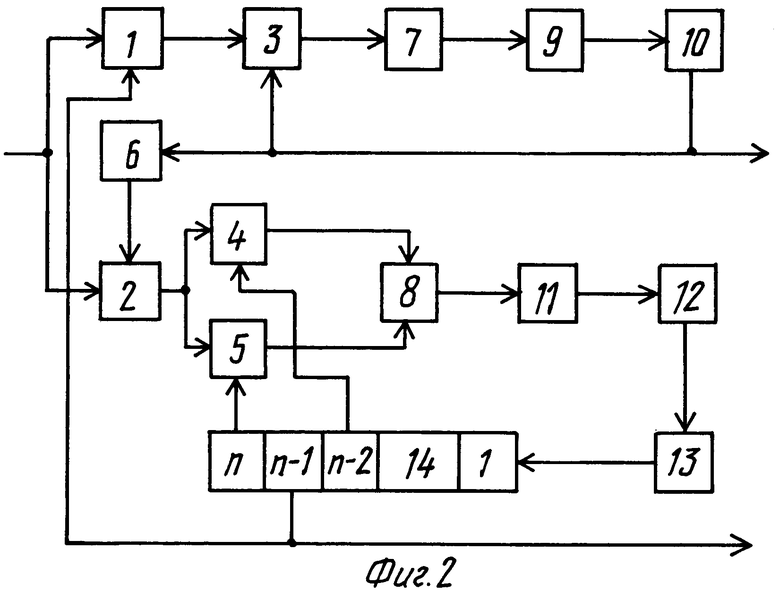

Для лучшего понимания работы заявляемого приемника, сделаем незначительные укрупнения в прототипе. Укрупненная структурная схема прототипа приведена на фиг. 3, где введены следующие обозначения:

1 - 4 - перемножители;

5 - фазовая автоподстройка частоты (ФАПЧ);

6 - фазовращатель на π/2;

7 - генератор управляемого напряжения (ГУН);

8 - сумматор;

9 - фильтр низкой частоты (ФНЧ);

10 - управляемый тактовый генератор;

11 - регистр сдвига генератора кода.

Вход приемника подключен к первым входам перемножителей 1 и 2, второй вход перемножителя 1 подключен к соответствующему выходу регистра сдвига генератора кода 11, выход перемножителя 1 соединен со входом ФАПЧ 5, выход которого соединен с входом ГУН 7, выход которого соединен со вторым входом ФАПЧ 5 непосредственно и со вторым входом перемножителя 2 через фазовращатель на π/2 6. Выход перемножителя 2 соединен с первыми входами перемножителей 3 и 4, вторые входы которых соединены с соответствующими выходами регистра сдвига генератора кода 11. Выходы перемножителей 3 и 4 соединены с первым и вторым входами сумматора 8, выход которого соединен с ФНЧ 9, выход которого соединен с тактовым генератором 10, выход которого соединен со входом регистра сдвига генератора кода 11.

Работает приемник-прототип, изображенный на фиг. 3 следующим образом.

На первые входы перемножителей 1 и 2 подается сигнал с корреляционных каналов поиска, на вторые входы перемножителей 1 и 2 подается опорная ПСП. На выходе первого перемножителя получаем несущую, которая подается на ФАПЧ 5 на другой вход которого подается сигнал опорной частоты. В ФАПЧ 5 сигнал перемножается, детектируется с разными весами, суммируется и подается на ГУН 7, который изменяет частоту до тех пор пока его частота не совпадает с частотой входного сигнала, а фаза не будет равна -π/2.

Сигнал опорной частоты через фазовращатель на π/2 подается на вход второго перемножителя, где перемножается с входным сигналом и подается на перемножители 3 и 4, на вторые входы которых подаются две ПСП, сдвинутые по задержке. На выходах перемножителей 3 и 4 получаем два синусоидальных сигнала, которые складываются в сумматоре 8. Затем происходят те же процессы, что и в ФАПЧ 5 по задержке.

Недостатком приемника-прототипа является низкая помехоустойчивость на этапе вхождения в синхронизм, это происходит из-за того, что для него статические ошибки по задержке становятся определяющими и, кроме того, для него присущ недостаток аналога: при переходе из поиска в слежение он не работает, так как нет квадратурного канала при подстройке фазы, команды на подстройку по времени "произвольны".

Для исключения этого недостатка в предлагаемый приемник, содержащий первый, второй, третий, четвертый перемножители, ФАПЧ, ГУН, фазовращатель на π/2, тактовый генератор, регистр сдвига генератора кода, выход которого соединен со вторым входом первого перемножителя, входы первого и второго перемножителей соединены со входом приемника, выход второго перемножителя соединен с первыми входами третьего и четвертого перемножителей, первый перемножитель, ФАПЧ и ГУН соединены последовательно, выход ГУН соединен с ФАПЧ и фазовращателем на π/2, введены пятый, шестой и седьмой перемножители, первый, второй, третий, четвертый интеграторы, первый и второй блоки вычисления модуля вектора, блок вычитания, таймер, ключ, блок принятия решений, делитель с переменным коэффициентом деления (ДПКД), блок управления коэффициентом деления ДПКД. Вход приемника соединен с пятым перемножителем, другой вход пятого и один из входов второго перемножителей соединены с соответствующими выходами регистра сдвига генератора кода, вход которого соединен с тактовым генератором через ДПКД, один из выходов ГУН соединен с перемножителями четвертым и седьмым непосредственно, а с перемножителями три и шесть через фазовращатель на π/2, выходы третьего и четвертого перемножителей соединены с первым и вторым интеграторами, выходы которых соединены с блоком вычисления модуля вектора, выход пятого перемножителя соединен со входами шестого и седьмого перемножителей, выходы которых соединены со входами третьего и четвертого интеграторов, выходы которых соединены со вторым блоком вычисления модуля вектора, выходы первого и второго блоков вычисления модуля вектора соединены с вычитавшим устройством. Выход ГУН, кроме того, соединен с фазовым детектором, другой вход которого соединен с выходом тактового генератора. Выходы фазового детектора и вычитающего устройства через ключ, управляемый таймером, соединены со схемой управления коэффициентом деления ДПКД. Выход схемы управления коэффициентом деления ДПКД соединен с соответствующим входом ДПКД. Выход тактового генератора, кроме того, соединен с регистром сдвига генератора кода через ДПКД.

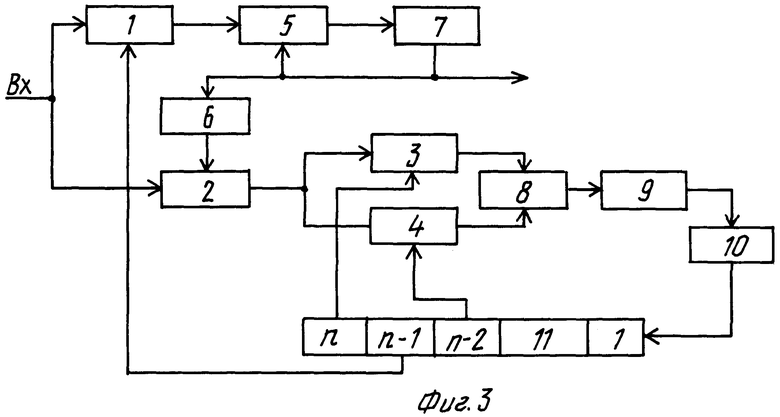

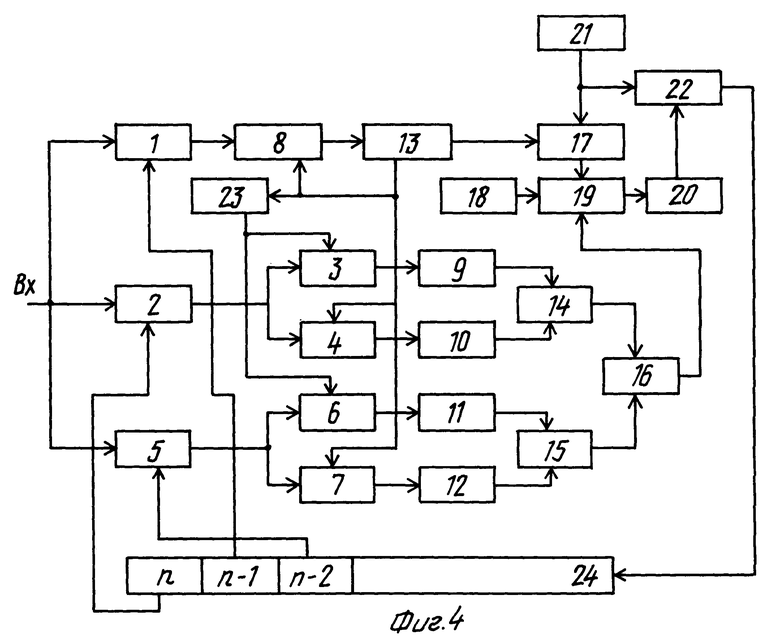

На фиг. 4 представлена структурная схема предлагаемого приемника, где введены следующие обозначения:

1 - 7 - перемножители;

8 - фазовая автоподстройка частоты (ФАПЧ);

9 - 12 - интеграторы;

13 - генератор управляемого напряжения (ГУН);

14,15 - блоки вычисления модуля вектора;

16 - вычитавшее устройство;

17 - блок принятия решений;

18 - таймер;

19 - ключ;

20 - блок управления коэффициентом деления ДПКД;

21 - тактовый генератор;

22 - делитель с переменным коэффициентом деления (ДПКД);

23 - фазовращатель на π/2;

24 - регистр сдвига генератора кода.

Схема предлагаемого приемника имеет следующие функциональные связи:

Вход приемника соединен с соответствующими входами перемножителей 1,2,5, вторые входы которых соединены с соответствующими выходами регистра сдвига генератора кода 24. Выход первого перемножителя соединен с последовательно соединенными ФАПЧ 8, ГУН 13 и блоком принятия решений 17. Выходы перемножителей 2 и 5 соединены со входами перемножителей 3,4,6,7. Выходы ГУН 13 непосредственно соединены с блоком принятия решений 17, ФАПЧ 8, перемножителями 4 и 7 и, через фазовращатель на π/2 - 23, с перемножителями 3 и 6. Выходы перемножителей 3 и 4 соединены с интеграторами 9 и 10, выходы которых подсоединены к соответствующим входам блока вычисления модуля вектора 14. Выходы перемножителей 6 и 7 соединены с интеграторами 11 и 12, выходы которых соединены с соответствующими входами второго блока вычисления модуля вектора 15. Выходы первого и второго блоков вычисления модуля вектора 14 и 15 подсоединены ко входам вычитающего устройства 16. Выходы вычитающего устройства 16 и блока принятия решений 17 через ключ 19 соединены с блоком управления коэффициентом деления ДПКД 20, выход таймера 18 подсоединен к входу управления ключа 19. Выход блока управления коэффициентом деления ДПКД 20 соединен с ДПКД 22. Выход тактового генератора 21 соединен с блоком принятия решений 17 непосредственно и с регистром сдвига генератора кода 24 через ДПКД 22.

Предлагаемый авторами приемник работает следующим образом.

При переходе от поиска к слежению на промежуточном этапе производят N подстроек с помощью вновь введенных квадратурных каналов подстройки по времени и определяют рассогласование по времени между копией и сигналом независимо от фазы принимаемого сигнала.

На первом этапе идет параллельно и независимо подстройка ФАПЧ и кольца временной подстройки, состоящего из блока управления коэффициентом деления ДПКД 20, таймера 18, ключа 19, ДПКД 22, тактового генератора 21 и перемножителей 2 и 5, двух квадратурных каналов, включающих в себя перемножители 3 - 7; интеграторы 9 - 12; блоки вычисления модуля вектора 14 и 15, вычитающее устройство 16 и регистр сдвига генератора кода 24.

Коэффициент деления ДПКД 22 корректируется на определенное время, а не постоянно.

Блок управления коэффициентом деления ДПКД 20 представляет собой схему, преобразующую аналоговую ошибку на выходе кольца временной подстройки в команды на изменение коэффициента деления ДПКД (коэффициент деления меняется на время в (+) или (-): на тоже время меняется коэффициент деления, но на различные величины). Таким образом, этот блок совмещает в себе свойства аналого-цифрового преобразователя (АЦП) и контролера. Примером конкретной реализации АЦП могут служить схемы, приведенные в справочниках: Б.Г.Федорков, В. А.Телец, В.П.Дегтяренко Микроэлектронные цифро- аналоговые и аналого-цифровые преобразователи. М.: Радио и связь, 1984, с. 94 рис. 58; Цифровые радиоприемные системы /Под ред. М.И.Жодзишского. М.: Радио и связь, 1990, с. 41-45.

Один из примеров конкретной реализации контролера приведен в справочнике фирмы " GEC PLESSEY SEMICONDUCTORS", 1995, с. 156.

Блок принятия решений 17 может представлять собой фазовый детектор или фазовый детектор, дополненный умножителем или делителем частоты в случае различия fгун и fтакт..

Блок вычисления модуля вектора содержит сумматоры, квадраторы и нелинейные элементы, порядок их включения может быть различным (Шумоподобные сигналы в системе передачи данных. /Под ред. В.Б.Пестрякова. М.: Сов. радио, 1973, с. 33 рис. 2.3.6; Расчет помехоустойчивости систем передачи дискретных сообщений. Справочник. В.И.Коржик и др. М.: Радио и связь, 1981, с. 68 рис. 2.3, с. 78 рис. 2.11).

Ошибка от блока принятия решений 17 подается через ключ 19 на блок управления коэффициентом деления ДПКД 20. Ключ 19 - это коммутатор с двух направлений на одно, управление на него подается с таймера 18. За время подстройки ошибка по фазе мала, ошибка по сдвигу тоже мала, тогда переходят от слежения с помощью кольца временной подстройки к слежению по времени только через постоянное изменение коэффициента деления ДПКД 22, при этом кольцо временной подстройки, работающее под воздействием выходного напряжения вычитающего устройства 16 "разомкнуто", а "замыкается" кольцо временной подстройки, работающее от выходного напряжения блока принятия решений 17. Так как ошибка временного положения устранена после первого этапа и периодически производится коррекция копии сигнала по ошибке в цепи временной подстройки, то на втором этапе произойдет подстройка по частоте также, как и в приемнике-прототипе.

Таким образом, предлагаемое техническое решение позволяет оценить величину статической ошибки по задержке и компенсировать ее.

Предложенный приемник вычисляет нестабильность не на промежуточной частоте fп.ч, а абсолютный уход на несущей частоте fнес, т.е. на более высокой частоте, что позволяет увеличить точность вхождения его в синхронизм.

И, кроме того, у него повышается помехоустойчивость этапа вхождения в синхронизм на 2 - 4 дБ.

Изобретение относится к области радиотехники и может быть использовано в широкополосных системах связи. Технический результат - повышение помехоустойчивости вхождения в синхронизм. Следящий приемник, содержащий семь перемножителей (1-7), четыре интегратора (9-12), два блока вычисления модуля вектора (14, 15), вычитающее устройство (16), регистр сдвига генератора кода (24), фазовращатель по π/2 (23), фазовую автоподстройку частоты (8), генератор управляемого напряжения (13), таймер (18), блок принятия решений (17), ключ (19), тактовый генератор (21), делитель с переменным коэффициентом деления (22), блок управления коэффициента деления ДПКД (20), позволяет оценить величину статической ошибки и компенсировать ее; при этом вычисляется абсолютный уход на несущей частоте, что увеличивает точность вхождения его в синхронизм. И, кроме того, у него повышается помехоустойчивость вхождения в синхронизм на 2-4 дБ. 4 ил.

Следящий приемник широкополосного сигнала, содержащий первый - четвертый перемножители, тактовый генератор, регистр сдвига генератора кода, блок фазовой автоподстройки частоты (ФАПЧ), генератор, управляемый напряжением (ГУН), и фазовращатель на π/2, при этом вход приемника соединен с входами первого и второго перемножителей, вторые входы которых соединены с соответствующими выходами регистра сдвига генератора кода, выход второго перемножителя подключен к параллельно соединенным третьему и четвертому перемножителям, причем выход первого перемножителя через ФАПЧ соединен с входом ГУН, выход которого соединен с входом фазовращателя на π/2 и вторым входом ФАПЧ, отличающийся тем, что введены пятый - седьмой перемножители, четыре интегратора, два блока вычисления модуля вектора, вычитающее устройство, таймер, ключ, блок принятия решений, делитель с переменным коэффициентом деления (ДПКД), блок управления коэффициентом деления ДПКД, причем вход приемника соединен с входом пятого перемножителя, второй вход которого соединен с соответствующим выходом регистра сдвига генератора кода, выход пятого перемножителя соединен с входами шестого и седьмого перемножителей, вторые входы четвертого и седьмого перемножителей соединены с выходом ГУН, а вторые входы третьего и шестого перемножителей - с выходом фазовращателя на π/2, выходы третьего, четвертого, шестого и седьмого перемножителей соединены с входами соответствующих интеграторов, выходы первого и второго интеграторов - с

входом первого блока вычисления модуля вектора, а выходы третьего и четвертого интеграторов - с входами второго блока вычисления модуля вектора, выход которого и выход первого блока вычисления модуля вектора соединены с входами вычитающего устройства, при этом выход тактового генератора соединен с входом блока принятия решений непосредственно и через ДПКД с регистром сдвига генератора кода первого перемножителя, ФАПЧ и ГУН, а к второму входу блока принятия решений подсоединен выход ГУН, выход блока принятия решений соединен с вторым входом ключа, выход вычитающего устройства - с первым входом ключа, вход управления которого соединен с выходом таймера, а выход ключа - с блоком управления коэффициентом деления ДПКД, выход которого соединен с вторым входом ДПКД.

| ТУЗОВ Г.И | |||

| Статистическая теория приема сложных сигналов | |||

| - М.: Советское радио, 1977, с.227 - 238, рис.4.23 | |||

| Устройство синхронизации псевдошумовых сигналов | 1985 |

|

SU1280704A2 |

| Устройство для синхронизации псевдошумовых сигналов | 1977 |

|

SU649150A2 |

| Устройство для слежения за задержкой импульсного псевдослучайного сигнала при приеме ансабля псевдослучайных сигналов | 1975 |

|

SU515298A1 |

| СПОСОБ ДИАГНОСТИКИ БОЛЕЗНИ ЖИЛЬБЕРА | 2003 |

|

RU2253867C1 |

| US 5317602 А, 31.05.1994 | |||

| US 4653076 А, 24.03.1987 | |||

| Электрический генератор с переменным числом оборотов и, примерно, постоянным напряжением | 1933 |

|

SU35295A1 |

| Способ получения резиновых смесей | 1954 |

|

SU102662A1 |

Авторы

Даты

2000-09-27—Публикация

1999-01-26—Подача