Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах, где необходимо деление частоты последовательности импульсов на пять, а также изменение коэффициента деления с пяти на три, например, в разного рода тренажерах, устройствах контроля, играх и т. д.

Известен делитель на пять, выполненный на вентилях И-НЕ/ИЛИ-НЕ.

Однако этот делитель имеет много запрещенных состояний и не может изменять коэффициент деления.

Известен делитель на пять, выполненный по схеме двухфазного пятистабильного счетчика.

Однако в работе этого счетчика имеют место соревнования фронтов и, кроме того, нет возможности изменять коэффициент деления частоты.

Известен делитель на пять, выполненный на вентилях И-НЕ/ИЛИ-НЕ по однофазной пятистабильной схеме.

Однако в этом делителе не предусмотрено изменение коэффициента деления и, кроме того, имеется внецикловое запрещенное состояние, в котором делитель перестает выполнять свои счетные функции.

Наиболее близким по технической сущности к заявляемому является делитель частоты импульсов. Данное техническое решение представляет собой делитель частоты импульсов, содержащий два триггера, вентиль и три разряда, каждый из которых состоит из триггера и вентиля, выходы которых соединены с первыми единичными входами триггеров соответствующих разрядов, первый вход вентиля первого разряда подключен к выходу вентиля второго разряда, первый вход которого соединен с инверсным выходом триггера третьего разряда, первый единичный вход которого подключен к нулевому входу триггера первого разряда, первый единичный вход которого соединен с первым единичным входом первого триггера и с первым входом вентиля, второй вход которого подключен к прямому выходу первого триггера, первый нулевой вход которого соединен с инверсным выходом второго триггера, нулевой вход которого подключен ко второму входу вентиля первого разряда и ко входной шине тактовых импульсов, а единичный вход к выходу вентиля, третий вход которого соединен со вторым единичным входом первого триггера, с первым входом вентиля третьего разряда и с инверсным выходом триггера второго разряда, первый нулевой вход которого подключен к второму входу вентиля третьего разряда. В состав известного делителя частоты импульсов входит также второй вентиль, входы которого соединены соответственно с прямым выходом второго триггера и с шиной управления, а выход подключен соответственно к одному из нулевых входов триггера третьего разряда и к одному из входов вентиля первого разряда. Данное устройство технологично, удобно для реализации в микроэлектронном исполнении, удобно позволяет изменять коэффициент деления частоты и в режиме деления частоты на пять формирует сигналы, имеющие по две пары перепадов (из нуля в единицу и из единицы в ноль) за период сигнала, что позволяет использовать делитель в режиме деления частоты на 2,5. Однако известный делитель частоты импульсов обладает их недостатками. Работа делителя усложнена и охватывает до пяти последовательных задержек в срабатывании вентилей. Схема деления довольно сложна, поскольку она включает пятнадцать вентилей И-НЕ или ИЛИ-НЕ, общее количество входов у которых равно 41. В режиме деления частоты на три делитель частоты импульсов не формирует сигналов, имеющих по две пары перепадов и, кроме того, может попадать в запрещенные состояния, из которых, правда, он выходит после поступления нескольких тактовых импульсов. По сути дела все это означает, что надежность работы известного делителя частоты импульсов невысока.

Задачей изобретения является повышение надежности работы устройства.

Поставленная задача решается тем, что в известный делитель частоты импульсов, содержащий два триггера, вентиль и три разряда, каждый из которых состоит из триггера и вентиля, выходы которых соединены с первыми единичными входами триггеров соответствующих разрядов, первый вход вентиля первого разряда подключен к выходу вентиля второго разряда, первый вход которого соединен с инверсным выходом триггера третьего разряда, первый единичный вход которого подключен к нулевому входу триггера первого разряда, первый единичный вход которого соединен с первым единичным входом первого триггера и с первым входом вентиля, второй вход которого подключен к прямому выходу первого триггера, первый нулевой вход которого соединен с инверсным выходом второго триггера, нулевой вход которого подключен ко второму входу вентиля первого разряда и ко входной шине тактовых импульсов, а единичный вход к выходу вентиля, третий вход которого соединен с вторым единичным входом первого триггера, с первым входом вентиля третьего разряда, с инверсным выходом триггера второго разряда, первый нулевой вход которого подключен ко второму входу вентиля третьего разряда, введен инвертор, вход которого соединен с прямым выходом второго триггера, а выход подключен к третьему входу вентиля третьего разряда и ко второму нулевому входу триггера второго разряда, инверсный выход которого соединен с вторым единичным входом триггера третьего разряда, прямой выход которого подключен к четвертому входу вентиля третьего разряда, выход которого соединен с третьим входом вентиля первого разряда, а второй выход с вторым входом вентиля первого разряда, четвертый вход которого подключен к первому входу вентиля второго разряда, а выход к второму входу вентиля второго разряда, третий вход которого соединен с нулевым входом триггера третьего разряда и с прямым выходом триггера первого разряда, второй единичный вход которого подключен к инверсному выходу первого триггера, второй нулевой вход которого соединен с шиной управления.

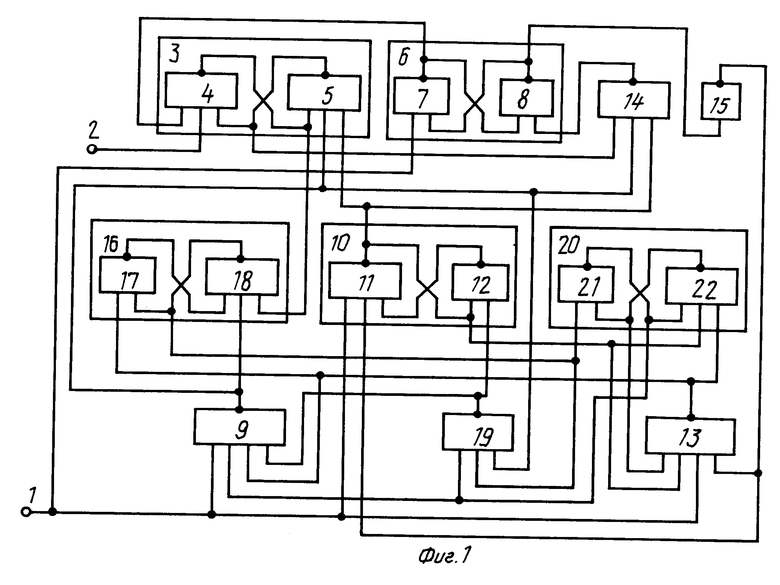

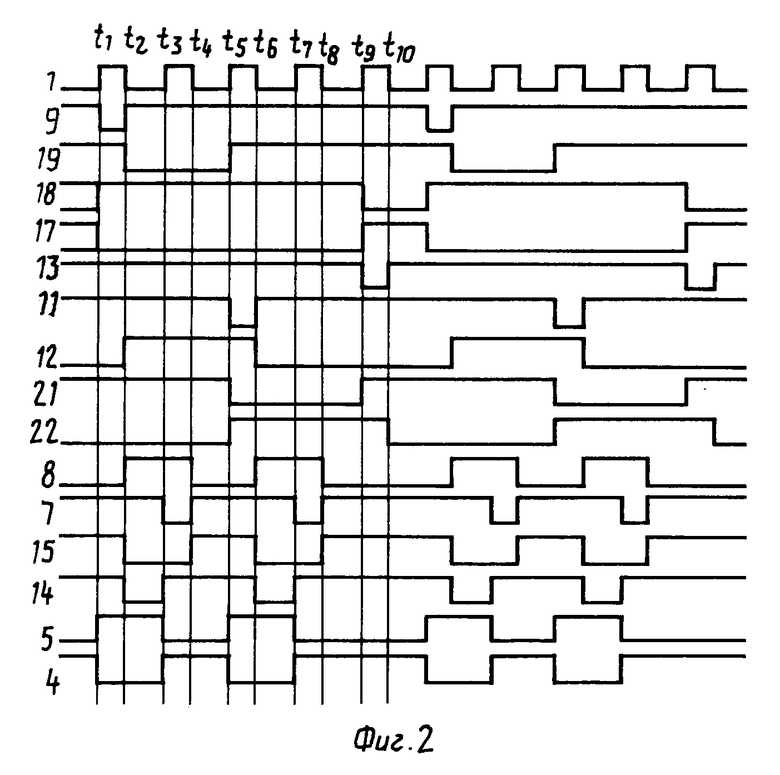

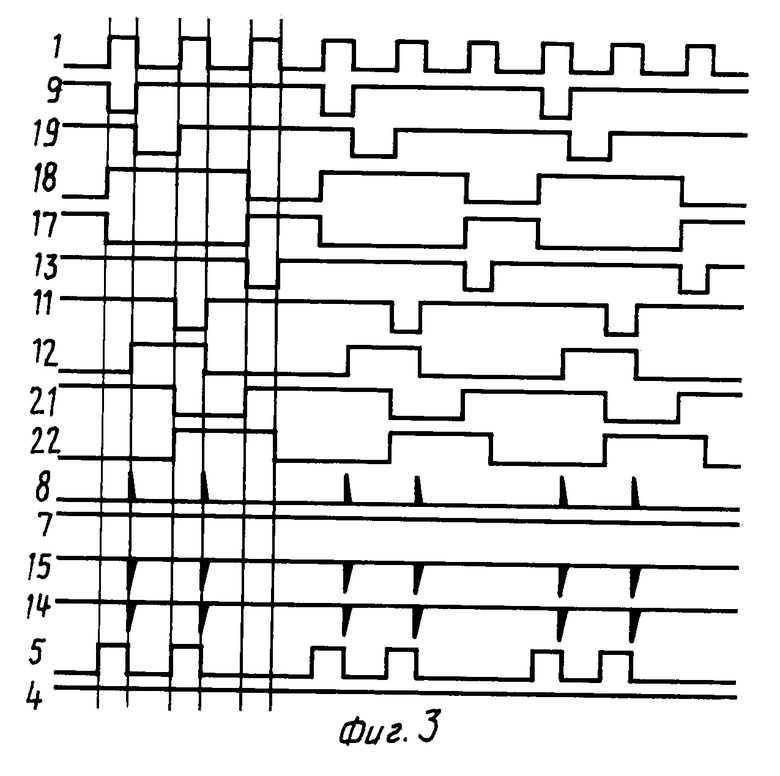

На фиг. 1 приведена схема электрическая принципиальная предлагаемого делителя частоты импульсов; на фиг. 2 и 3 временные диаграммы, поясняющие его работу в режимах деления на пять и на три соответственно.

Делитель частоты импульсов содержит следующие элементы.

Две входные шины: шина 1 тактовых импульсов и шина 2 управления 6. Первый триггер 3, состоящий из вентилей 4 и 5. Один из этого входов установки нуля соединен с шиной 2. Второй триггер 6, состоящий из вентилей 7 и 8. К входу установки нуля второго триггера включена шина 1 тактовых импульсов, а его инверсный выход соединен с одним из входов установки нуля первого триггера 3. Вентиль 9 первого разряда, один из входов которого соединен с шиной 1 тактовых импульсов, а выход подключен к одному из входов установки единицы первого триггера 3. Триггер 10 второго разряда, состоящий из вентилей 11 и 12. К одному из входов установки нуля триггера 10 второго разряда подключена шина 1 тактовых импульсов, а его инверсный выход соединен с одним из входов установки единицы первого триггера 3. Вентиль 13 третьего разряда, один из входов которого соединен с шиной 1 тактовых импульсов, а другой с инверсным выходом триггера 10 второго разряда. Выход вентиля 13 подключен к одному из входов вентиля 9 первого разряда.

Вентиль 14, входы которого соединены соответственно с прямым выходом первого триггера 3, с выходом вентиля 9 первого разряда и с инверсным выходом триггера 10 второго разряда. Выход вентиля 14 подключен к входу установки единицы второго триггера 6. Инвертор 15, вход которого подключен к прямому выходу второго триггера 6, а выход соединен с одним из входов установки нуля триггера 10 второго разряда и с одним из входов вентиля 13 третьего разряда. Триггер 16 первого разряда, состоящий из вентилей 17 и 18. К входу установки нуля триггера 16 первого разряда подключен выход вентиля 13 третьего разряда. Входы установки единицы триггера 16 соединены соответственно с инверсным выходом первого триггера 3 и с выходом вентиля 9 первого разряда. Вентиль 19 второго разряда, входы которого соединены соответственно с прямым выходом триггера 16 первого разряда и с выходом вентиля 9 первого разряда. Выход вентиля 19 подключен к входу установки единицы триггера 10 второго разряда и к одному из входов вентиля 9 первого разряда. Триггер 20 третьего разряда, состоящий из вентилей 21 и 22, ко входу установки нуля триггера 20 третьего разряда подключен прямой выход триггера 16 первого разряда. Входы установки единицы триггера 20 соединены соответственно с инверсным выходом триггера 10 второго разряда и с выходом вентиля 13 третьего разряда. Прямой выход триггера 20 подключен к одному из входов вентиля 13 третьего разряда, а инверсный выход к одному из входов вентилей первого 9 и второго 19 разрядов.

Все составные элементы делителя частоты импульсов являются стандартными, широко распространенными в технике и в дополнительных пояснениях не нуждаются.

В качестве вентилей могут быть использованы как элементы И-НЕ, так и элементы ИЛИ-НЕ. Для определенности на фиг. 1 приведено исполнение делителя на элементах И-НЕ, на фиг. 2 и 3 временные диаграммы, получаемые также на выходах элементов И-НЕ. Входной сигнал по шине тактовых импульсов обозначен на фиг. 2 и 3 номером (1) этой шины. Сигнал на шине 2 управления не приведен на фиг. 2 и фиг. 3, а все остальные диаграммы обозначены номерами элементов, на выходе которых они образуются.

Рассмотрим работу делителя в режиме деления на пять частоты тактовых импульсов, поступающих по шине 1 тактовых импульсов. Этот режим характеризуется наличием высокого, единичного сигнала на шине 2 управления, подключенной к одному из нулевых входов первого триггера 3 (состоящего из вентилей И-НЕ 4 и 5).

Работу начнем рассматривать перед подачей импульсов по шине 1 тактовых импульсов (т. е. при логическом нуле на шине 1). Этот логический ноль определяет наличие логических единиц на инверсном выходе второго триггера 6 (состоящего из вентилей И-НЕ 7 и 8), на выходе вентиля И-НЕ 9 первого разряда, на инверсном выходе вентиля И-НЕ 9 первого разряда, на инверсном выходе триггера 10 второго разряда (состоящего из вентилей И-НЕ 11 и 12), на выходе вентиля И-НЕ 13 третьего разряда.

На всех входах первого триггера 3 оказываются единичные сигналы, следовательно в нем может быть как единичное, так и нулевое содержимое. Предложим, что в исходный момент в первом триггере 3 нулевое содержимое, т. е. логический ноль на выходе вентиля И-НЕ 5 и логическая единица на выходе вентиля И-НЕ 4. Логический ноль на выходе вентиля 5 формирует логическую единицу на выходе вентиля 14. После этого на обоих входах вентиля 8 (входящего в состав второго триггера 6) оказываются единичные сигналы. На выходе вентиля 8 образуется сигнал логического нуля, формирующий логическую единицу на выходе инвертора 15.

Для триггера 16 первого разряда (состоящего из вентилей И-НЕ 17 и 18) наличие единичных выходных сигналов у вентилей 4, 9 и 13 означает присутствие логических единиц на всех входах. В триггере 16 первого разряда может быть как единичное, так и нулевое содержимое. Предположим, что в исходный момент в триггере 16 нулевое содержимое, то есть логический ноль на выходе вентиля И-НЕ 18 и логическая единица на выходе вентиля И-НЕ 17. Логический ноль на выходе вентиля 18 формирует логическую единицу на выходе вентиля И-НЕ 19 второго разряда и на инверсном выходе триггера 20 третьего разряда (состоящего из вентилей И-НЕ 21 и 22). На обоих входах И-НЕ 12 оказываются единичные сигналы (с выходов вентилей 11 и 19). На выходе вентиля 12 оказывается логический ноль. На всех входах вентиля 22 оказываются единичные сигналы (с выходов вентилей 11, 13 и 21). На выходе вентиля 22 оказывается логический ноль.

Таким образом, все выходные сигналы элементов делителя в исходный момент определены.

В момент t1 начала первого импульса, поступающего по шине 1 тактовых импульсов, на всех входах вентиля И-НЕ 9 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходах вентилей 14 и 19, а также устанавливающий логическую единицу в первом триггере 3 и в триггере 16 первого разряда (на выходах вентилей 5 и 18 появляются логические единицы, а на выходах вентилей 4 и 17 логические нули). Других изменений выходных сигналов элементов делителя в момент t1 не будет.

В момент t2 окончания первого импульса по шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля 9 первого разряда. После этого на всех входах сразу двух вентилей 14 и 19 оказываются единичные сигналы. На выходах этих вентилей появляются сигналы логического нуля. Логический ноль на выходе вентиля 14 формирует логическую единицу на выходе вентиля 8, которая, в свою очередь, вызывает появление логического нуля на выходе инвертора 15. Логический ноль на выходе вентиля 19 формирует логическую единицу на выходе вентиля 12. Других изменений выходных сигналов элементов делителя в момент t2 не будет.

В момент t3 начала второго импульса, поступающего на шине 1 тактовых импульсов, на обоих входах вентиля И-НЕ 7 оказываются единичные сигналы. На его выходе является логический ноль, подтверждающий логическую единицу на выходе вентиля 8 и формирующий нулевое содержимое первого триггера 3. При этом на выходе вентиля И-НЕ 4 появляется единичный сигнал, а на выходе вентиля 5 нулевой сигнал. Логический ноль на выходе вентиля 5 формирует логическую единицу на выходе вентиля 14. Других изменений выходных сигналов элементов делителя в момент t3 не будет.

В момент t4 окончания второго импульса на шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля И-НЕ 7. После этого на обоих входах вентиля 8 оказываются единичные сигналы. На выходе этого вентиля формируется логический ноль, который вызывает появление логической единицы на выходе инвертора 15. Других изменений выходных сигналов элементов делителя в момент t4 не будет.

В момент t5 начала третьего импульса, поступающего по шине 1 тактовых импульсов, на всех входах вентиля И-НЕ 11 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходах вентилей 12, 13, 14 и формирующий нулевое содержимое первого триггера 3 и триггера 20 третьего разряда. При этом на выходах вентилей 5 и 22 оказываются логические единицы, а на выходах вентилей 4 и 21 логические нули. Логический ноль на выходе вентиля 21 подтверждает единичный выходной сигнал вентиля 9 и устанавливает единичный выходной сигнал вентиля 19. Других изменений выходных сигналов элементов делителя в момент t5 не будет.

В момент t6 окончания третьего импульса на шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля И-НЕ 11. После этого на всех входах сразу двух вентилей 12 и 14 оказываются единичные сигналы. На выходах этих вентилей появляются сигналы логического нуля. Логический ноль на выходе вентиля 14 формирует логическую единицу на выходе вентиля 8, которая, в свою очередь, вызывает появление логического нуля на выходе инвертора 15. Других изменений выходных сигналов элементов делителя в момент t6 не будет.

В момент t7 начала четвертого импульса, поступающего по шине 1 тактовых импульсов, на обоих входах вентиля И-НЕ 7 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходе вентиля 8 и формирующий нулевое содержимое первого триггера 3. При этом на выходе вентиля И-НЕ 4 появляется единичный сигнал, а на выходе вентиля 5 нулевой сигнал. Логический ноль на выходе вентиля 5 формирует логическую единицу на выходе вентиля 14. Других изменений выходных сигналов элементов делителя в момент t7 не будет.

В момент t8 окончания четвертого импульса на шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля И-НЕ 7. После этого на обоих входах вентиля 8 оказываются единичные сигналы. На выходе этого вентиля формируется логический ноль, который вызывает появление логической единицы на выходе инвертора 15. Других изменений выходных сигналов элементов делителя в момент t8 не будет.

В момент t9 начала пятого импульса, поступающего по шине 1 тактовых импульсов, на всех выходах вентиля И-НЕ 13 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходах вентилей 9 и 22, а также формирующий нулевое содержимое триггера 16 первого разряда. При этом на выходе вентиля И-НЕ 17 появляется единичный сигнал, а на выходе вентиля 18 нулевой сигнал. Логический ноль на выходе вентиля 18 подтверждает логическую единицу на выходе вентиля 19 и формирует логическую единицу на выходе вентиля 21. Других изменений выходных сигналов элементов делителя в момент t9 не будет.

В момент t10 окончания пятого импульса по шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля И-НЕ 13. После этого на всех входах вентиля 22 оказываются единичные сигналы. На выходе этого вентиля формируется логической ноль. Других изменений выходных сигналов элементов делителя в момент t10 не будет, а все выходные сигналы элементов совпадают с аналогичными сигналами в исходный момент (до подачи импульсов по шине 1 тактовых импульсов). Это означает, что далее работа делителя будет полностью повторять рассмотренную выше.

Рассмотрим теперь, могут ли существовать в данном делителе запрещенные комбинации. Выше было показано, что в отсутствии импульсов на шине 1 тактовых импульсов на всех входах первого триггера 3 оказываются единичные сигналы. Если предположить, что в этом триггере оказалось нулевое содержимое, то, как было показано выше, на выходах вентилей 4, 7, 9, 11, 13, 14 и 15 оказываются единичные сигналы, а на выходах вентилей 5 и 6 нулевое. Это означает, что на всех входах триггера 16 первого разряда присутствуют единичные сигналы. Триггер 16 может иметь как нулевое, так и в единичное содержимое. Выше рассматривался случай нулевого содержимого триггера 16. Рассмотрим теперь, что будет при единичном содержимом триггера 16. При этом на выходе его вентиля 18 оказывается единичный сигнал, а на выходе вентиля 17 нулевой сигнал. Таким образом, на всех входах триггера 20 третьего разряда оказываются единичные сигналы, т. е. существуют две возможности: нулевое содержимое триггера 20 и единичное содержимое того же триггера. Если в триггере 20 нулевое содержимое, то на выходе его вентиля 22 оказывается логический ноль, а на выходе вентиля 21 логическая единица. Таким образом, на всех входах вентиля И-НЕ 19 второго разряда оказываются единичные сигналы (с выходов вентилей 9, 18 и 21). На выходе вентиля 19 образуется сигнал логического нуля, формирующий логическую единицу на выходе вентиля 12. Таким образом, все выходные сигналы элементов делителя оказались определенными. Они полностью совпадают с сигналами в промежутке времени между t4 и t5, то есть мы получили нормальное цикловое разрешенное состояние выходных сигналов элементов. Предположим теперь, что при тех же условиях в триггере 20 не нулевое, а единичное содержимое. То есть, на выходе вентиля 22 присутствует логическая единица, а на выходе вентиля 21 логический ноль. Этот логический ноль формирует единичный сигнал на выходе вентиля И-НЕ 19, и на обоих входах вентиля 12 оказываются единичные сигналы, то есть на выходе вентиля 12 оказывается логический ноль. Таким образом опять определены все выходные сигналы элементов делителя. Они полностью совпадают с сигналами в промежутке времени между t8 и t9, то есть мы получили нормальное цикловое разрешенное состояние выходных сигналов элементов. То есть, при нулевом содержимом первого триггера 3 могут быть получены только три нормальных цикловых состояния выходных сигналов делителя. Предположим теперь, что в первом триггере 3 не нулевое, а единичное содержимое, то есть логическая единица на выходе вентиля 5 и логический ноль на выходе вентиля 4. Этот логический ноль формирует единичный выходной сигнал вентиля 18. Кроме того, на всех трех входах вентиля 14 оказываются единичные сигналы (с выходов вентилей 5, 9 и 11). На выходе вентиля 14 оказывается сигнал логического нуля, формирующий единичный выходной сигнал вентиля 8 и, соответственно, нулевой выходной сигнал инвертора 15. Выходной сигнал инвертора 15 вызывает появление единичного сигнала на выходе вентиля 13 третьего разряда. При этом оказывается, что на обоих входах вентилей 17 присутствуют единичные сигналы (с выходов вентилей 13 и 18). На выходе вентиля 17 формируется сигнал логического нуля. На всех входах триггера 20 третьего разряда присутствуют логические единицы (с выходов вентилей 11, 13 и 18). В этом триггере возможно как нулевое, так и единичное содержимое. Пусть сначала в триггере 20 присутствует нулевое содержимое (логический ноль на выходе вентиля 22 и логическая единица на выходе вентиля 21). При этом на всех входах вентиля 19 оказываются единичные сигналы. На его выходе формируется логический ноль, устанавливающий логическую единицу на выходе вентиля 12. Таким образом опять определены все выходные сигналы элементов делителя. Они полностью совпадают с сигналами в промежутке времени между t2 и t3, т. е. мы получили нормальное цикловое разрешенное состояние выходных сигналов элементов. Если же в триггере 20 присутствует не нулевое, а единичное содержимое (логическая единица на выходе вентиля 22 и логический ноль на выходе вентиля 21), то логический ноль на выходе вентиля 21 вызывает появление сигнала логической единицы на выходе вентиля 19. На обоих входах вентиля 12 оказываются логические единицы (с выходов вентилей 11 и 19) и на его выходе формируется сигнал логического нуля. Таким образом опять определены все выходные сигналы элементов делителя. Они полностью совпадают с сигналами в промежутке времени между t6 и t7, то есть мы получили нормальное цикловое разрешенное состояние выходных сигналов элементов. Все это означает, что в делителе возможно существование только разрешенных цикловых состояний и никакие запрещенные режимы работы появиться в принципе не могут.

Таким образом полностью рассмотрена работа делителя в режиме деления частоты импульсов на пять. Рассмотрим теперь работу делителя в режиме деления частоты на три, что определяется наличием логического измененного сигнала логической единицы на выходе вентиля 4. При отсутствии импульсов на шине 1 тактовых импульсов (то есть при наличии логического нуля на этой шине) формируются логические единицы на выходах четырех вентилей: 7, 9, 11 и 13. Таким образом, на всех входах вентиля 5 оказываются единичные сигналы (с выходов вентилей 4, 9 и 11). На выходе вентиля 5 образуется логический ноль, формирующий логическую единицу на выходе вентиля 14. На обоих входах вентиля 8 оказываются единичные сигналы (с выходов вентилей 7 и 14), а на выходе вентиля 8 появляется логический ноль, формирующий единичный сигнал на выходе инвертора 15. На всех входах триггера 16 первого разряда оказываются единичные сигналы (с выходов вентилей 4, 9 и 13). В триггере 16 возможно либо единичное, либо нулевое содержимое. Предположим, что в исходный момент в триггере 16 нулевое содержимое, то есть логический ноль на выходе вентиля И-НЕ 18 и логическая единица на выходе вентиля И-НЕ 17. Логический ноль на выходе вентиля 18 формирует логическую единицу на выходе вентиля И-НЕ 19 второго разряда и на инверсном выходе триггера 20 третьего разряда (состоящего из вентилей И-НЕ 21 и 22). На обоих входах вентиля И-НЕ 12 оказываются единичные сигналы (с выходов вентилей 11 и 19). На выходе вентиля 12 оказывается логический ноль. На всех входах вентиля 22 оказываются единичные сигналы (с выходов вентилей 11, 13 и 21). На выходе вентиля 22 оказывается логический ноль.

Таким образом, все выходные сигналы элементов делителя в исходный момент определены.

В момент t1 начала первого импульса, поступающего по шине 1 тактовых импульсов, на всех входах вентиля И-НЕ 9 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходах вентилей 14 и 19, а также устанавливающий логическую единицу на выходе вентиля 5. Кроме того логический ноль на выходе вентиля 9 устанавливает в триггере 16 первого разряда единичное содержимое (на выходе вентиля 18 появляется логическая единица, а на выходах вентиля 17 логический ноль). Других изменений выходных сигналов элементов делителя в момент t1 не будет.

В момент t2 окончания первого импульса на шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля 9 первого разряда. После этого на всех входах сразу трех вентилей 5, 14 и 19 оказываются единичные сигналы. На выходах этих вентилей появляются сигналы логического нуля. Логический ноль на выходе вентиля 14 формирует логическую единицу на выходе вентиля 8, которая, в свою очередь, вызывает появление логического нуля на выходе инвертора 15. Логический ноль на выходе вентиля 5 формирует логическую единицу на выходе вентиля 14, после чего на обоих входах вентиля 8 оказываются единичные сигналы. На выходе вентиля 8 образуется сигнал логического нуля, формирующий сигнал логической единицы на выходе инвертора 15. То есть в момент t2 на выходах вентилей 14 и 8, а также на выходе инвертора 15 возникают кратковременные выбросы. В ряде случаев из-за их кратковременности выбросы могут и отсутствовать. Логический ноль на выходе вентиля 19 формирует логическую единицу на выходе вентиля 12. Других изменений выходных сигналов элементов делителя в момент t2 не будет.

В момент t3 начала второго импульса, поступающего по шине 1 тактовых импульсов, на всех входах вентиля И-НЕ 11 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходах вентилей 12, 13 и 14 и формирующий логическую единицу на выходе вентиля 5. Кроме того логический ноль на выходе вентиля 11 устанавливает нулевое содержимое триггера 20 третьего разряда. При этом на выходе вентиля 22 оказывается логическая единица, а на выходе вентиля 21 логический ноль. Логический ноль на выходе вентиля 21 подтверждает единичный выходной сигнал вентиля 9 и устанавливает единичный выходной сигнал вентиля 19. Других изменений выходных сигналов элементов делителя в момент t3 не будет.

В момент t4 окончания второго импульса на шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля И-НЕ 11. После этого на всех входах сразу трех вентилей 5, 12 и 14 оказываются единичные сигналы. На выходах этих вентилей появляются сигналы логического нуля. Логический ноль на выходе вентиля 14 формирует логическую единицу на выходе вентиля 8, которая, в свою очередь, вызывает появление логического нуля на выходе инвертора 15. Логический ноль на выходе вентиля 5 формирует логическую единицу на выходе вентиля 14, после чего на обоих входах вентиля 8 оказываются единичные сигналы. На выходе вентиля 8 образуется сигнал логического нуля, формирующий сигнал логической единицы на выходе инвертора 15. Т. е. в момент t4 на выходах вентилей 14 и 8, а также на выходе инвертора 15 возникают кратковременные выбросы. В ряде случаев из-за их кратковременности выбросы могут и отсутствовать. Других изменений логических сигналов элементов делителя в момент t4 не будет.

В момент t5 начала третьего импульса, поступающего по шине 1 тактовых импульсов, на всех входах вентиля И-НЕ 13 оказываются единичные сигналы. На его выходе появляется логический ноль, подтверждающий логическую единицу на выходах вентилей 9 и 22, а также формирующий нулевое содержимое триггера 16 первого разряда. При этом на выходе вентиля И-НЕ 17 появляется единичный сигнал, а на выходе вентиля 18 нулевой сигнал. Логический ноль на выходе вентиля 18 подтверждает логическую единицу на выходе вентиля 19 и формирует логическую единицу на выходе вентиля 21. Других изменений выходных сигналов элементов делителя в момент t5 не будет.

В момент t6 окончания третьего импульса на шине 1 тактовых импульсов логический ноль на шине 1 вызывает появление логической единицы на выходе вентиля И-НЕ 13. После этого на всех входах вентиля 22 оказываются единичные сигналы. На выходе этого вентиля формируется логический ноль. Других изменений выходных сигналов элементов делителя в момент t6 не будет, а все выходные сигналы элементов совпадают с аналогичными сигналами в исходный момент (до подачи импульсов по шине 1 тактовых импульсов). Это означает, что далее работа делителя будет полностью повторять рассмотренную выше.

Рассмотрим теперь, могут ли существовать в данном делителе запрещенные комбинации. Выше было показано, что в отсутствии импульсов на шине 1 тактовых импульсов полностью определены выходные сигналы вентилей 4, 5, 7, 8, 9, 11, 13 и 14 и инвертора 15. При этом на выходах вентилей 4, 7, 9, 11, 13, 14 и инвертора 15 оказываются единичные сигналы, а на выходах вентилей 5 и 8 сигналы логического нуля. Это означает, что на всех входах триггера 16 первого разряда оказываются единичные сигналы (с выходов вентилей 4, 9 и 13). В триггере 16 возможно либо единичное, либо нулевое содержимое. Выше предполагалось, что в исходный момент в триггере 16 нулевое содержимое, то есть логический ноль на выходе вентиля И-НЕ 18 и логическая единица на выходе вентиля И-НЕ 17. Предложим теперь, что в исходный момент в триггере 16 не нулевое, а единичное содержимое, т. е. логический ноль на выходе вентиля 17 и логическая единица на выходе вентиля 18. При этом на всех входах триггера 20 третьего разряда оказываются единичные сигналы (с выходов вентилей 11, 13 и 18). Это означает, что в триггере 20 может быть как нулевое, так и единичное содержимое. Предложим сначала, что в триггере 20 нулевое содержимое, т. е. логический ноль на выходе вентиля 22 и логическая единица на выходе вентиля 21. Тогда на всех трех входах вентиля 19 второго разряда оказываются единичные сигналы (с выходов вентилей 9, 18 и 21). На выходе вентиля 19 формируется логический ноль, который устанавливает логическую единицу на выходе вентиля 12. Таким образом определены все выходные сигналы элементов делителя. Они полностью совпадают с сигналами в промежутке времени между t2 и t3, то есть мы получили нормальное цикловое разрешенное состояние выходных сигналов элементов. Если же в триггере 20 присутствует не нулевое, а единичное содержимое (логическая единица на выходе вентиля 22 и логический ноль на выходе вентиля 21), то логический ноль на выходе вентиля 21 вызывает появление сигнала логической единицы на выходе вентиля 19. На обоих входах вентиля 12 оказываются логические единицы (с выходов вентилей 11 и 19) и на его выходе формируется сигнал логического нуля. Таким образом опять определены все выходные сигналы элементов делителя. Они полностью совпадают с сигналами в промежутке времени между t4 и t5, т. е. мы получили нормальное цикловое разрешенное состояние выходных сигналов элементов. Все это означает, что в делителе возможно существование только разрешенных цикловых состояний и никакие запрещенные режимы работы появиться в принципе не могут.

Таким образом полностью рассмотрена работа делителя как в режиме деления частоты импульсов на пять, так и в режиме деления частоты на три. Рассмотрение показало, что в обоих режимах деления ни в каких элементах не может оказаться запрещенных состояний. Кроме того, формирование выходных сигналов элементов делителя происходит не более чем с задержкой, равной времени срабатывания четырех логических элементов (т.е. налицо повышение быстродействия по сравнению с прототипом). Выходные сигналы составных элементов делителя очень удобны для использования: среди них есть сигнал близкий к меандру (на выходе вентиля 22) и совпадающий с меандром при поступлении входного меандра по шине 1 тактовых импульсов. И в режиме деления частоты на пять, и в режиме деления частоты на три на выходе вентиля 5 образуются сигналы, имеющие форму, обеспечивающую формирование двух пар перепадов за период. Это создает потенциальную возможность получения частот, близких к 2,5 и 1,5 без введения каких-либо дополнительных элементов. Кроме того, заявляемый делитель несколько проще прототипа: если прототип содержит пятнадцать составных элементов с общим числом входов равным 41, то заявляемый делитель частоты импульсов тоже содержит пятнадцать составных элементов, но всего с 40 входами. Таким образом, заявляемый делитель имеет лучшие характеристики и более высокую надежность работы, чем прототип.

Преимущества заявляемого делителя частоты импульсов подтвердили проведенные на предприятии сравнительные исследования функционирования заявляемого делителя и делителя, выполненного по схеме прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834549A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| Устройство для получения разности двух импульсных последовательностей | 1990 |

|

SU1798904A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2025895C1 |

| Устройство формирования серии импульсов | 1989 |

|

SU1829108A1 |

| СЕЛЕКТОР ИНФОРМАЦИОННЫХ ИМПУЛЬСОВ | 1990 |

|

RU2042266C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ БЫСТРОМЕНЯЮЩЕГОСЯ ПРОЦЕССА | 1990 |

|

RU2007756C1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2042261C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С НОСИТЕЛЯ МАГНИТНОЙ ЗАПИСИ | 1992 |

|

RU2018174C1 |

| СПОСОБ ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2047224C1 |

Использование: в автоматике и вычислительной технике, а именно в устройствах, где необходимо деление частоты последовательности импульсов на пять, а также изменение коэффициента деления с пяти на три. Сущность изобретения: делитель частоты импульсов содержит два триггера, вентиль и три разряда, каждый из которых состоит из триггера и вентиля, выходы которых соединены с первыми единичными входами триггеров соответствующих разрядов, инвертор. 3 ил.

ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ, содержащий два триггера, вентиль и три разряда, каждый из которых состоит из триггера и вентиля, выходы которых соединены с первыми единичными входами триггеров соответствующих разрядов, первый вход вентиля первого разряда подключен к выходу вентиля второго разряда, первый вход которого соединен с инверсным выходом триггера третьего разряда, первый единичный вход которого подключен к нулевому входу триггера первого разряда, первый единичный вход которого соединен с первым единичным входом первого триггера и с первым входом вентиля, второй вход которого подключен к прямому выходу первого триггера, первый нулевой вход которого соединен с инверсным выходом второго триггера, нулевой вход которого подключен к второму входу вентиля первого разряда и к входной шине тактовых импульсов, а единичный вход к выходу вентиля, третий вход которого соединен с вторым единичным входом первого триггера, с первым входом вентиля третьего разряда и с инверсным выходом триггера второго разряда, первый нулевой вход которого подключен к второму входу вентиля третьего разряда, отличающийся тем, что в него введен инвертор, вход которого соединен с прямым выходом второго триггера, а выход подключен к третьему входу вентиля третьего разряда и к второму нулевому входу триггера второго разряда, инверсный выход которого соединен с вторым единичным входом триггера третьего разряда, прямой выход которого подключен к четвертому входу вентиля третьего разряда, выход которого соединен с третьим входом вентиля первого разряда, а второй вход с вторым входом вентиля первого разряда, четвертый вход которого подключен к первому входу, а выход к второму входу вентиля второго разряда, третий вход которого соединен с нулевым входом триггера третьего разряда и с прямым выходом триггера первого разряда, второй единичный вход которого подключен к инверсному выходу первого триггера, второй нулевой вход которого соединен с шиной управления.

| Делитель частоты импульсов | 1988 |

|

SU1653152A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-08-09—Публикация

1993-02-16—Подача