Изобретение относится к радиотехнике и может быть использовано для умножения частоты в аппаратах воспроизведения магнитной записи, а также в качестве измерительного прибора, следящего за изменением входной частоты в различных радиотехнических устройствах.

Известен цифровой умножитель частоты [1] , содержащий формирователь импульсов, блок управления, три вентиля, два делителя частоты, счетный триггер, два счетчика, два регистра памяти, три блока переноса, элемент И, элемент ИЛИ, параллельный сумматор, триггер задержки и генератор импульсов эталонной частоты с их функциональными связями.

Данный умножитель характеризуется недостаточно высокой точностью и низкой помехозащищенностью, а также он неконтролепригоден.

Известен также умножитель частоты следования импульсов [2], содержащий генератор импульсов, делитель частоты, два счетчика импульсов, три элемента ИЛИ, два элемента задержки, регистр, формирователь импульсов, входную и выходную шины, блок управления, триггер и три элемента И с их функциональными связями.

Данный умножитель повышает точность работы за счет снижения количества сбойных ситуаций, но не устраняет их совсем, а также обладает малой контролепригодностью и помехозащищенностью.

Наиболее близким по технической сущности к предлагаемому является умножитель частоты следования импульсов [3], содержащий два умножителя частоты, выполненные каждый из делителя частоты, фазового детектора, управляющего элемента и управляемого генератора с их связями, два делителя с переменным коэффициентом деления, два блока управления коэффициентом деления, два элемента И-НЕ, RS-триггер и коммутатор с их функциональными связями.

Данный умножитель расширяет частотный диапазон, но имеет недостаточные помехозащищенность и контролепригодность.

Задачей, на решение которой направлено изобретение, является повышение точности и контролепригодности, что в конечном итоге позволяет получить более высокий технический результат, а именно устранить недостоверные участки и оперативно ввести корректировки в результаты обработки.

Поставленная задача решается тем, что в умножитель частоты следования импульсов, содержащий первый и второй блоки умножения, коммутатор, первый и второй выходы которого подключены к первым входам первого и второго блоков умножения соответственно, а также входную и выходную шины, введены блок синхронизации, блок управления, первый и второй блоки анализа, счетчик импульсов, первый и второй индикаторы, элемент задержки, первый и второй элементы И, элемент И-НЕ, первый и второй элементы ИЛИ, элемент ИЛИ-НЕ, генератор импульсов, выход которого подключен к первым входам блока синхронизации и коммутатора, второй, третий и четвертый входы которого подключены к первому, второму и третьему выходам блока синхронизации соответственно, причем третий выход блока синхронизации подключен к входам элемента задержки и блока управления, первый выход которого подключен к второму входу блока синхронизации, а второй выход - к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, первый вход которого подключен к выходу элемента задержки и управляющему входу счетчика импульсов, выход которого подключен к первому входу второго элемента И, выход которого подключен к второму входу первого элемента ИЛИ, а второй вход - к счетному входу счетчика импульсов и выходу второго элемента ИЛИ, первый и второй входы которого подключены к первым выходам первого и второго блоков умножения соответственно, группа информационных выходов первого и второго блоков умножения подключена к группе информационных входов первого и второго блоков анализа соответственно, а вторые выходы первого и второго блоков умножения подключены к пеpвым входам первого и второго блоков анализа соответственно, первые выходы которых подключены к пятому и шестому входам коммутатора соответственно, первый выход которого подключен к второму входу второго блока умножения, второй выход - к второму входу первого блока умножения, третий выход - к третьим входам первого и второго блоков умножения и второму входу второго блока анализа, а четвертый выход - к четвертым входам первого и второго блоков умножения и второму входу первого блока анализа, второй выход которого подключен к первому входу элемента ИЛИ-НЕ, второй вход которого подключен к второму выходу второго блока анализа, первый выход которого подключен к первому входу элемента И-НЕ, второй вход которого подключен к первому выходу первого блока анализа, входы первого и второго индикаторов подключены к выходам элементов ИЛИ-НЕ и И-НЕ соответственно, входная шина подключена к третьему входу блока синхронизации, а выходная - к выходу первого элемента И.

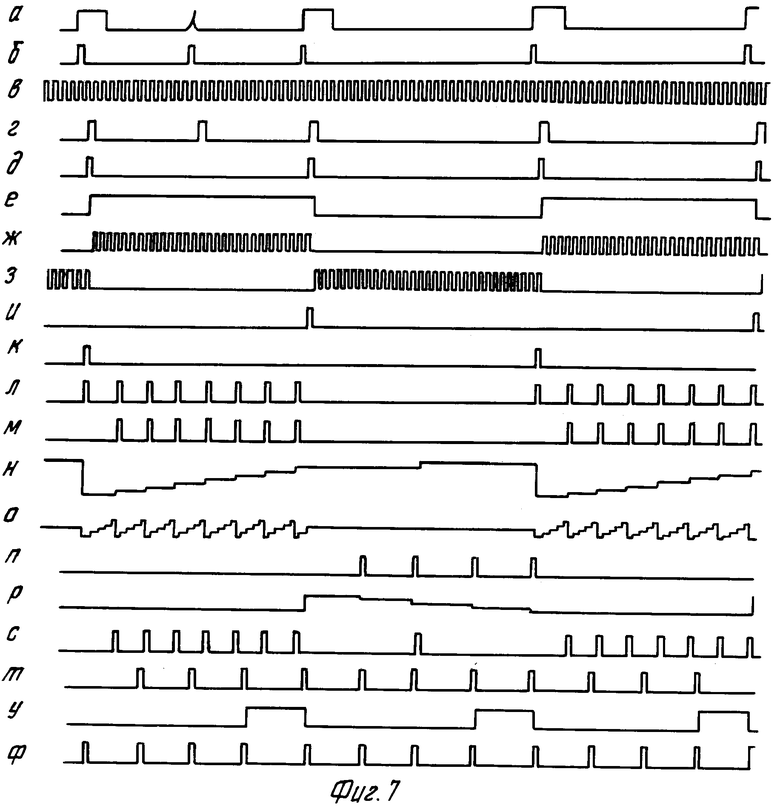

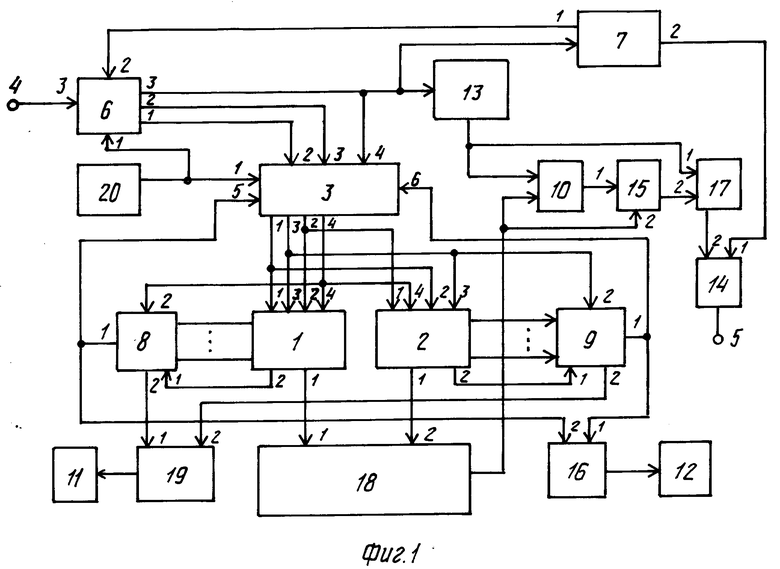

Сущность умножителя поясняется электрическими функциональными схемами (фиг.1-6) и временными диаграммами (фиг.7-9), иллюстрирующими его работу.

Умножитель (фиг. 1) содержит первый и второй блоки 1 и 2 умножения, коммутатор 3, первый и второй выходы которого подключены к первым входам и второго блоков 1 и 2 умножения соответственно, а также входную и выходную шины 4 и 5, блок 6 синхронизации, блок 7 управления, первый и второй блоки 8 и 9 анализа, счетчик 10 импульсов, первый и второй индикаторы 11 и 12, элемент 13 задержки, первый и второй элементы И 14 и 15, элемент И-НЕ 16, первый и второй элементы ИЛИ 17 и 18, элемент ИЛИ-НЕ 19, генератор 20 импульсов, выход которого подключен к первым входам блока 6 синхронизации и коммутатора 3. Второй, третий и четвертый входы последнего подключены к первому, второму и третьему выходам блока 6 синхронизации соответственно, третий выход блока 6 синхронизации подключен к входам элемента 13 задержки и блока 7 управления, первый выход которого подключен к второму входу блока 6 синхронизации, а второй выход - к первому входу первого элемента И 14. Второй вход элемента И 14 подключен к выходу первого элемента ИЛИ 17, первый вход которого подключен к выходу элемента 13 задержки и управляющему входу счетчика 10 импульсов. Выход счетчика 10 подключен к первому входу второго элемента И 15, выход которого подключен к второму входу первого элемента ИЛИ 17, а второй вход - к счетному входу счетчика 10 импульсов и выходу второго элемента ИЛИ 18, первый и второй входы которого подключены к первым выходам первого и второго блоков 1 и 2 умножения соответственно. Группа информационных выходов первого и второго блоков 1 и 2 умножения подключена к группе информационных входов первого и второго блоков 8 и 9 анализа соответственно, а вторые выходы первого и второго блоков 1 и 2 умножения подключены к первым входам первого и второго блоков 8 и 9 анализа соответственно, первые выходы которых подключены к пятому и шестому входам коммутатора 3 соответственно. Первый выход коммутатора 3 подключен к второму входу второго блока 2 умножения, второй выход - к второму входу первого блока 1 умножения, третий выход - к третьим входам первого и второго блоков 1 и 2 умножения и второму входу второго блока 9 анализа, а четвертый выход - к четвертым входам первого и второго блоков 1 и 2 умножения и второму входу первого блока 8 анализа, второй выход которого подключен к первому входу элемента ИЛИ-НЕ 19. Второй вход элемента ИЛИ-НЕ 19 подключен к второму выходу второго блока 9 анализа, первый выход которого подключен к первому входу элемента И-НЕ 16, второй вход которого подключен к первому выходу первого блока 8 анализа. Входы первого и второго индикаторов 11 и 12 подключены к выходам элементов ИЛИ-НЕ 19 и И-НЕ 16 соответственно. Входная шина 4 подключена к третьему входу блока 6 синхронизации, а выходная шина 5 - к выходу первого элемента И 14.

Каждый из блоков 1 (2) умножения (фиг.2) содержит первый, второй и третий счетчики 21, 22 и 23 импульсов, схему 24 сравнения, делитель 25 частоты, первый и второй элементы 26 и 27 задержки, первый, второй и третий элементы ИЛИ 28, 29 и 30. Первый вход первого элемента ИЛИ 28 подключен к четвертому входу блока 1 (2) умножения, а выход - к управляющему входу первого счетчика 21 импульсов, счетный вход которого подключен к второму входу блока 1 (2) умножения, а выход переполнения - к второму входу первого элемента ИЛИ 28 и первому входу второго элемента ИЛИ 29. Выход последнего подключен к счетному входу второго счетчика 22 импульсов, вход сброса которого подключен к первому входу первого элемента ИЛИ 28. Информационные выходы первого счетчика 21 импульсов подключены к первой группе информационных входов схемы 24 сравнения, вторая группа информационных входов которой подключена к информационным выходам третьего счетчика 23 импульсов. Управляющий вход счетчика 23 подключен к третьему входу блока 1 (2) умножения и входу первого элемента 26 задержки, выход которого подключен к первому входу третьего элемента ИЛИ 30. Второй вход элемента ИЛИ 30 подключен к счетному входу третьего счетчика 23 импульсов, выходу делителя 25 частоты и входу второго элемента 27 задержки, выход которого подключен к управляющему входу схемы 24 сравнения, выход которой подключен к второму входу второго элемента ИЛИ 29. Выход третьего элемента ИЛИ 30 подключен к управляющему входу делителя 25 частоты, информационные входы которого подключены к информационным выходам второго счетчика 22 импульсов и группе информационных выходов блока 1 (2) умножения, счетный вход - к первому входу блока 1 (2) умножения, а выход - к первому выходу блока 1 (2) умножения, второй выход которого подключен к входу переполнения второго счетчика 22 импульсов.

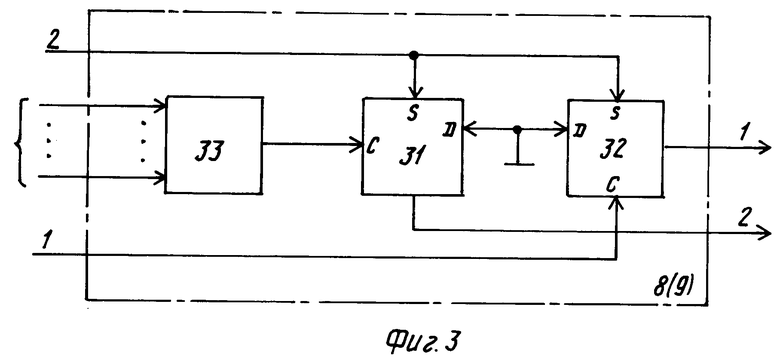

Каждый из блоков 8 (9) анализа (фиг.3) содержит первый и второй D-триггеры 31 и 32, дешифратор 33, группа информационных входов которого подключена к группе информационных входов блока 8 (9) анализа, а выход - к С-входу первого D-триггера 31, выход которого подключен к второму выходу блока 8 (9) анализа. С-вход второго D-триггера 32 подключен к первому входу блока 8 (9) анализа, первый выход которого подключен к выходу второго D-триггера 32, S-вход которого подключен к S-входу первого D-триггера 31 и второму входу блока 8 (9) анализа. D-входы первого и второго D-триггеров 31 и 32 подключены к нулевой шине.

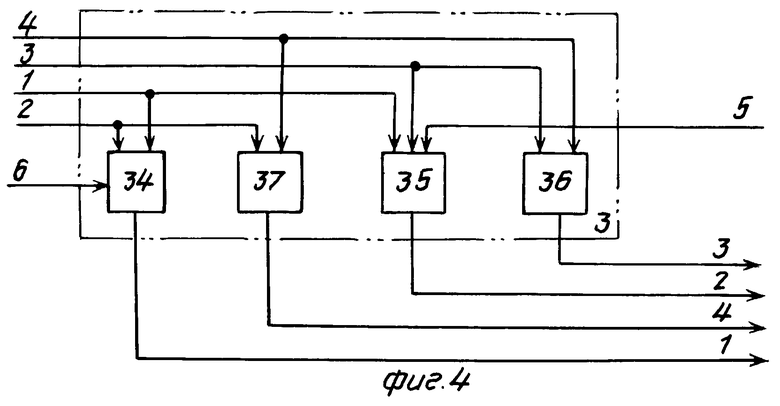

Коммутатор 3 (фиг.4) содержит первый, второй, третий и четвертый элементы И 34, 35, 36 и 37, выходы которых подключены соответственно к первому, второму, третьему и четвертому выходам коммутатора 3. Первый вход коммутатора подключен к первому входу первого элемента И 34 и первому входу второго элемента И 35, второй вход которого подключен к пятому входу коммутатора 3, а третий вход - к третьему входу коммутатора 3 и первому входу третьего элемента И 36. Второй вход элемента И 36 подключен к четвертому входу коммутатора 3 и первому входу четвертого элемента И 37, второй вход которого подключен к второму входу коммутатора 3 и второму входу первого элемента И 34, третий вход которого подключен к шестому входу коммутатора 3.

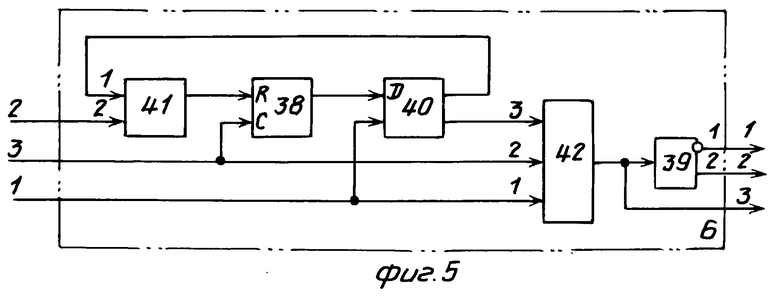

Блок 6 синхронизации (фиг.5) содержит первый и второй триггеры 38 и 39, регистр 40 сдвига, элемент ИЛИ 41, элемент И 42, первый вход которого подключен к первому входу блока 6 синхронизации и входу синхронизации регистра 40 сдвига, а второй вход - к третьему входу блока 6 синхронизации и С-входу первого триггера 38, R-вход триггера 38 подключен к выходу элемента ИЛИ 41, а выход - к информационному входу регистра 40 сдвига, первый выход которого подключен к первому входу элемента ИЛИ 41, второй вход которого подключен к второму входу блока 6 синхронизации. Второй выход регистра 40 сдвига подключен к третьему входу элемента И 42, выход которого подключен к С-входу второго триггера 39. Первый и второй выходы триггера 39 подключены соответственно к первому и второму выходам блока 6 синхронизации, третий выход которого подключен к выходу элемента И 42.

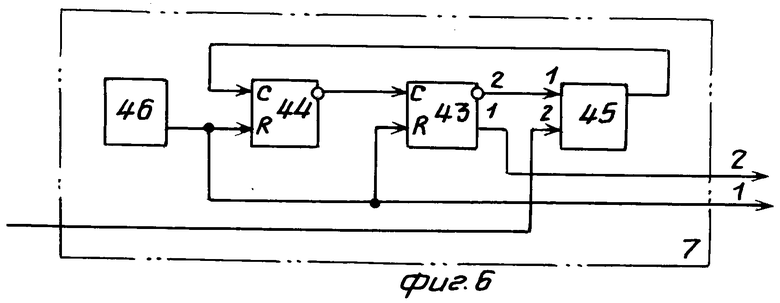

Блок 7 управления (фиг.6) содержит первый и второй триггеры 43 и 44, элемент И 45, элемент 46 начальной установки, выход которого подключен к R-входам первого и второго триггеров 43 и 44 и первому выходу блока 7 управления. Второй выход последнего подключен к первому выходу триггера 43, второй выход которого подключен к первому входу элемента И 45. Выход элемента И 45 подключен к С-входу триггера 44, выход которого подключен к С-входу триггера 43, а вход блока 7 управления подключен к второму входу элемента И 45.

Умножитель частоты следования импульсов работает следующим образом.

Входные импульсы (фиг.7а), период следования которых Твх, поступают с входной шины 4 на триггер 38, переводя его по переднему фронту в единичное состояние из исходного нулевого (фиг.7б). Первым импульсом с генератора 20 (фиг. 7в) единичное состояние переносится на первый выход регистра 40, и одновременно триггер 38 устанавливается в нулевое состояние. Таким образом, длительность импульсов на выходе регистра 40 (фиг.7г) равна периоду импульсов с генератора 20.

Для устранения коротких импульсных помех во входном сигнале используется элемент И 42, на выходе которого выделяются импульсы (фиг.7д) длительностью в полпериода сигнала с генератора 20, соответствующие истинным импульсам входного сигнала и синфазные с импульсами генератора 20.

За первый (после включения умножителя) период входного сигнала осуществляется автоматическая подготовка умножителя к работе. В этот период времени выходные импульсы умножителя не отражают достоверно требуемую зависимость Fвых = K ˙Fвх. Блокировку этих импульсов осуществляют элемент И 14 и блок 7.

Блок 7 управления работает следующим образом. При включении питания элемент 46 вырабатывает сигнал, который устанавливает триггеры 43 и 44, а также триггер 38 в нулевое состояние. Элемент И 14 закрыт. Первый после включения питания импульс с выхода элемента И 42 проходит через открытый элемент И 45 на счетный вход триггера 44 и перебрасывает его в противоположное (единичное) состояние. Следующий импульс с элемента И 42 опять перебрасывает триггер 44, по положительному фронту выходного сигнала которого перебрасывается в единичное состояние триггер 43, открывая элемент И 14 и закрывая элемент И 45. Следовательно, до окончания первого периода входного сигнала после включения в работу умножителя на его выходе не появляются импульсы, частота которых не отражает требуемой зависимости

Твых = Твх/К.

Импульсная последовательность с элемента И 42 преобразуется триггером 39 в прямую (фиг.7е) и инверсную стробирующие последовательности. В дальнейшем первый блок 1 умножения при положительных значениях прямой стробирующей последовательности измеряет входные периоды, при нулевых значениях идет их ускоренный пересчет, т.е. происходит умножение частоты импульсной последовательности. Второй блок 2 умножения работает аналогично при использовании инверсной стробирующей последовательности. Для работы блоков 1 и 2 на выходах элементов И 35, 34, 37, 36 формируются сигналы (фиг.7ж, з, и, к соответственно).

Рассмотрим работу первого блока 1 умножения. В первый входной период идет измерение периода: первый импульс (фиг.7к) поступает на установочные входы счетчиков 22 и 21 и записывает в них соответственно коды М - α + 1 и N-K, где М и N - емкости счетчиков 22 и 21; К - коэффициент умножения;

α =  ,

,  ...

... - целая часть;

- целая часть;

τ25 и τ30 - времена задержек делителя 25 частоты и элемента ИЛИ 30; То - период импульсов с генератора 20. На суммирующий вход счетчика 21 поступает пачка импульсов с генератора 20 (фиг.7ж), за счет обратной связи счетчика 21 через элемент ИЛИ 28 (фиг.7л) на суммирующий вход счетчика 22 поступает серия импульсов (фиг. 7м) с периодом То˙K. Таким образом, к концу первого входного периода в счетчике 22 записан (фиг.7н) код  , , а код δ остатка этого периода (0 ≅ δ < К) записан в счетчике 21 (фиг.7о). Вторым входным импульсом (фиг.7п) с элемента И 37 код счетчика 22 переносится в делитель 25, а счетчик 23 устанавливается в состояние N. Задержка сигнала в элементе 26 равна τ28 + τ 21 + + τ 29 + τ22, т.е. сумма времен задержек в элементах ИЛИ 28 и 29 и счетчиках 21 и 22. На вычитающий вход делителя 25 частоты поступает пачка импульсов (фиг.7з с элемента И 34. Когда делитель 25 частоты обнуляется, на его выходе появляется импульс умноженной частоты (фиг. 7п), который вновь записывает в делитель 25 частоты код счетчика 22 и задним фронтом вычитает из состояния счетчика 23 одну единицу (фиг.7р). Задержка элемента 27 немного больше времени задержки счетчика 23. Если коды счетчиков 21 и 23 равны, то в счетчик 22 добавляется одна единица (фиг.7с). Если, по-прежнему, код счетчика 21 меньше кода счетчика 23, то состояние счетчика 22 не изменяется, так как импульс с выхода элемента 27 не проходит через схему 24 и элемент ИЛИ 29. На выходе делителя 25 появляются импульсы умноженной частоты, причем после добавления единицы в счетчик 22 происходит корректировка временного положения этих импульсов. Так как коэффициент деления делителя 25 выбран кодом счетчика 22 и равен

, , а код δ остатка этого периода (0 ≅ δ < К) записан в счетчике 21 (фиг.7о). Вторым входным импульсом (фиг.7п) с элемента И 37 код счетчика 22 переносится в делитель 25, а счетчик 23 устанавливается в состояние N. Задержка сигнала в элементе 26 равна τ28 + τ 21 + + τ 29 + τ22, т.е. сумма времен задержек в элементах ИЛИ 28 и 29 и счетчиках 21 и 22. На вычитающий вход делителя 25 частоты поступает пачка импульсов (фиг.7з с элемента И 34. Когда делитель 25 частоты обнуляется, на его выходе появляется импульс умноженной частоты (фиг. 7п), который вновь записывает в делитель 25 частоты код счетчика 22 и задним фронтом вычитает из состояния счетчика 23 одну единицу (фиг.7р). Задержка элемента 27 немного больше времени задержки счетчика 23. Если коды счетчиков 21 и 23 равны, то в счетчик 22 добавляется одна единица (фиг.7с). Если, по-прежнему, код счетчика 21 меньше кода счетчика 23, то состояние счетчика 22 не изменяется, так как импульс с выхода элемента 27 не проходит через схему 24 и элемент ИЛИ 29. На выходе делителя 25 появляются импульсы умноженной частоты, причем после добавления единицы в счетчик 22 происходит корректировка временного положения этих импульсов. Так как коэффициент деления делителя 25 выбран кодом счетчика 22 и равен  , а в процессе умножения идет коррекция этого коэффициента, то на выходе делителя 25 получается зависимость Fвых = K ˙Fвх с точностью ±То/2.

, а в процессе умножения идет коррекция этого коэффициента, то на выходе делителя 25 получается зависимость Fвых = K ˙Fвх с точностью ±То/2.

Выходные сигналы с делителей 25 обоих блоков 1 и 2 умножения объединяются на элементе ИЛИ 18 (фиг.7т). Сбойные ситуации из-за совпадения импульсов входных и с генератора 20, в результате которых на выходе умножителя может появиться ложный импульс, принципиально устранены, так как все сигналы, поступающие на рабочую часть умножителя, синхронны и длительности сигналов установки нормируются периодом импульсов с генератора 20.

На установочный вход счетчика 10 поступает импульс, задержанный на время задержки одного блока 1 (2) умножения. В счетчик 10 записывается код L-K+1, где L - емкость счетчика 10. На суммирующий вход счетчика 10 поступают импульсы с элемента ИЛИ 18 - состояние счетчика 10 изменяется по заднему фронту этих импульсов. Выходной сигнал со счетчика 10 (фиг.7у) запрещает прохождение через элемент И 15 последнего импульса умноженной частоты, на место которого подставляется на элементе ИЛИ 17 синхронный входной импульс (фиг. 7ф). За счет этого при неодинаковых входных периодах устраняется ошибка, которая была бы, если последний импульс не успел сформироваться на выходе делителей 25 частоты, т.е. в случае (Твх)i+1 < (Твх)i. Кроме того, это позволяет производить умножение входной частоты с девиацией до ± 100/К (%).

Емкость счетчика 22 определяет минимальную частоту входного сигнала, а заданная точность умножения ограничивает сверху частоту входного сигнала.

Рассмотрим работу устройства в области минимальных входных частот.

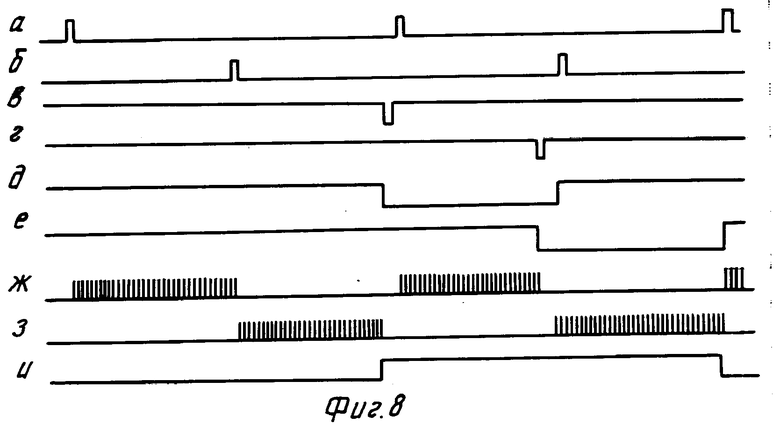

На четвертый и третий входы блока 1 умножения поступают разделенные коммутатором 3 отформированные входные импульсы (соответственно фиг.8а и фиг. 8б), а на второй и первый входы блока 1 - пачки импульсов с генератора 20 (соответственно фиг. 8ж и фиг.8з). Если входной период больше критического значения (Fвх < Fвх.мин), то на вторых выходах блоков 1 и 2 появляются импульсы переполнения со счетчика 22 (соответственно фиг.8в и фиг.8г). Эти импульсы и разделенные входные импульсы поступают на триггер 32, и на вторых выходах блоков 8 и 9 анализа формируются импульсы запрета (соответственно фиг.8д и фиг.8е), которые поступают на пятый и шестой входы коммутатора 3, запрещая прохождение импульсов высокой частоты с генератора 20 на счетчики 22. Таким образом, в них записано максимальное число, равное объему памяти счетчиков 22, а не начинается счет снова оставшихся импульсов в пачке. На выходе умножителя формируется минимально возможное значение умноженной частоты Fвых. Импульсы запрета с блоков 8 и 9 анализа суммируются элементом И-НЕ 16 (фиг.8и), индикатор 12 сигнализирует о выходе за границу частотного диапазона.

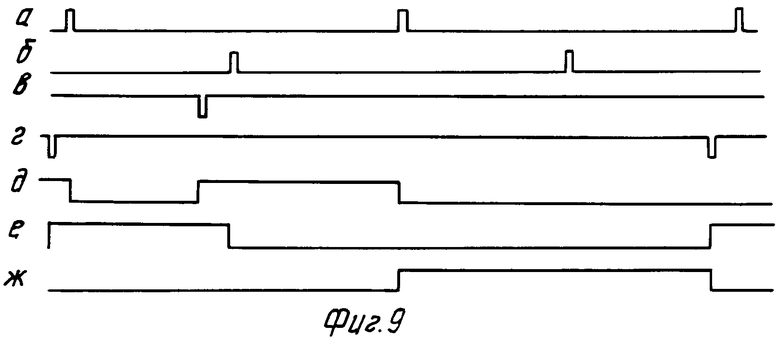

При работе в области максимальных входных частот на четвертый и третий входы блока 1 умножения поступают разделенные коммутатором 3 нормированные входные импульсы (соответственно фиг.9а и фиг.9б), они же поступают на первые входы блоков 8 и 9 анализа соответственно. Дешифратором 33 выбирается заданная точность умножения, и выходные импульсы с него у каждого блока 8 (фиг. 9в) и 9 (фиг.9г) анализа поступают на триггер 31. Если Fвх становится больше критического значения, то на выходе дешифратора 33 не формируются импульсы. Триггер 31 формирует контрольные импульсы на первом выходе блоков 8 (фиг.9д) и 9 (фиг.9е) анализа. Эти импульсы суммируются элементом ИЛИ-НЕ 19 (фиг.9ж), и индикатор 11 сигнализирует о понижении точности умножения.

Изобретение относится к импульсной технике и может быть использовано для умножения частоты в аппаратах воспроизведения магнитной записи, в измерительных приборах. Сущность изобретения: умножитель содержит два блока 1,2 умножения, коммутатор 3, блок 6 синхронизации, блок 7 управления, два блока 8,9 анализа, счетчик 10 импульсов, два 11,12 индикатора, элемент 13 задержки, два элемента И 14, 15, элемент И - НЕ 16, два элемента ИЛИ 17, 18, элемент ИЛИ - НЕ 19, генератор 20 импульсов, входную шину 4, выходную шину 5 с соответствующими связями. 5 з.п. ф-лы, 9 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1690171A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-12-30—Публикация

1992-06-03—Подача