Изобретение относится к измерительной технике, использующей регистраторы быстроменяющихся процессов.

Известно устройство для регистрации информации, в котором используется метод регистрации на электрохимическую бумагу с помощью набора электродов, которые выбираются дешифратором.

Недостатком вышеупомянутого устройства является то, что скорость регистрации входного сигнала напрямую связана со скоростью движения носителя информации, что определяет очень неэкономный расход носителя.

Наиболее близким по технической сущности и достигаемому результату к заявляемому устройству является устройство для регистрации и обработки быстроменяющихся процессов, содержащее переключатели, управляющий элемент, генератор синхроимпульсов, блок управления, два регистра кода входного сигнала, формирователь адреса строки, формирователь адреса электрода, дешифратор, блок выходных узлов (формирователей), блок электродов, транспортирующий механизм с носителем информации. В этом устройстве регистрация процесса производится перпендикулярно направлению движения носителя, т. е. поперек носителя. Поэтому, по сравнению с вышеописанным, в этом устройстве несколько увеличена экономичность расхода носителя, но недостаточно.

Техническим результатом изобретения является уменьшение расхода носителя путем временного уплотнения регистрируемой информации, а также возможность регистрации информации непрерывно без потери ее во время отображения на носителе.

Этот результат достигается за счет того, что в устройство для регистрации быстроменяющегося процесса, содержащее генератор тактовых импульсов, элемент управления, первый выход которого соединен с управляющими входами первого, второго и третьего элементов переключения, первая группа информационных входов первого из которых является информационным входом устройства, формирователь адреса электродов, выход переполнения которого соединен с информационным входом формирователя адреса строк, разрядные выходы формирователя адреса электродов соединены с входами дешифратора, выходы которого соединены через блок выходных узлов с входами блока электродов, два блока памяти, выходы которых соединены с информационными входами третьего элемента переключения, пятый элемент переключения, введены первый, второй и третий элементы И, шестой и седьмой элементы переключения, RS-триггер, два формирователя импульсов, формирователь адреса записи и делитель частоты, вход которого является входом синхронизации устройства, а выход соединен со входом формирователя адреса записи, выход переполнения которого соединен с S-входом RS-триггера, с обнуляющими входами формирователя адреса строки формирователя адреса электродов и со входом элемента управления, первый вход которого соединен с первым входом первого элемента И, а второй выход - с управляющими входами пятого, шестого и седьмого элементов переключения и с первым входом второго элемента И. Вход делителя частоты соединен со вторыми входами первого и второго элементов И и через первый формирователь импульсов подключен к первым инфорамционным входам четвертого и пятого элементов переключения, вторые информационные входы которых подключены к первому выходу второго формирователя импульсов, а выходы соединены со входами режима соответственно первого и второго блоков памяти, информационные входы которых подключены к выходам одноименных элементов И, входы первой группы информационных входов шестого элемента переключения объединены с одноименными входами первой группы информационных входов первого элемента переключения, входы вторых групп информационных входов первого и шестого элементов переключения подключены к разрядным выходам формирователя адреса строк, выход переполнения которого соединен с R-входом RS-триггера, выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход соединен с информационным входом формирователя адреса электродов и со входом второго формирователя импульсов, второй выход которого соединен со стробирующим входом третьего элемента переключения, выход которого соединен с информационным входом дешифратора, разрядные выходы формирователя адреса записи соединены со входами первых групп информационных входов второго и седьмого элементов переключения, входы групп информационных входов которых подключены к разрядным выходам формирователя адреса электродов, выходы второго и седьмого элементов переключения соединены со входами старших разрядов адреса соответственно первого и второго блоков памяти, входы младших разрядов адреса которых подключены к выходам первого и шестого элементов переключения соответственно.

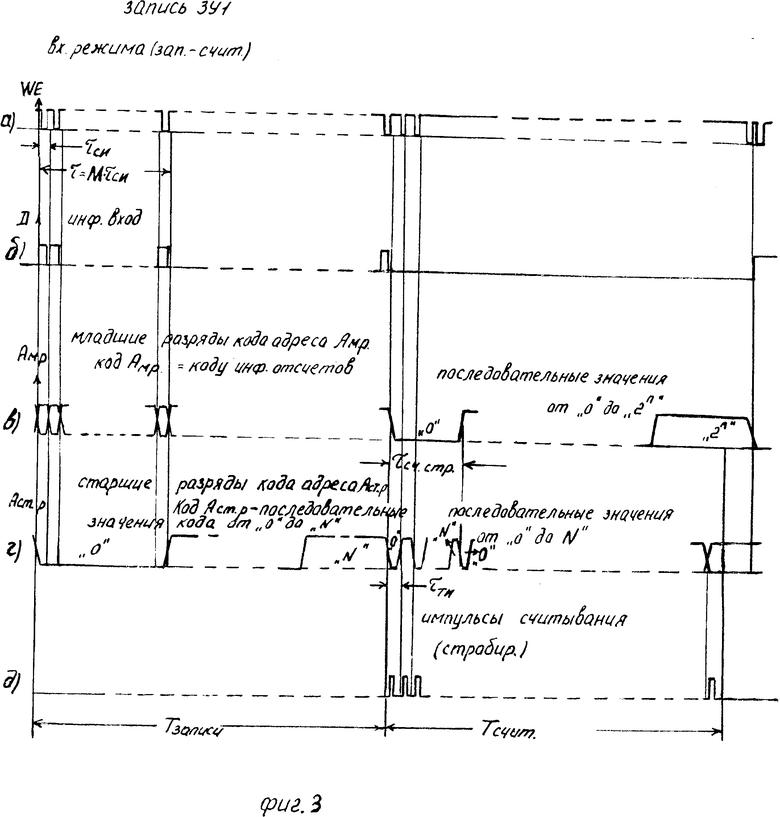

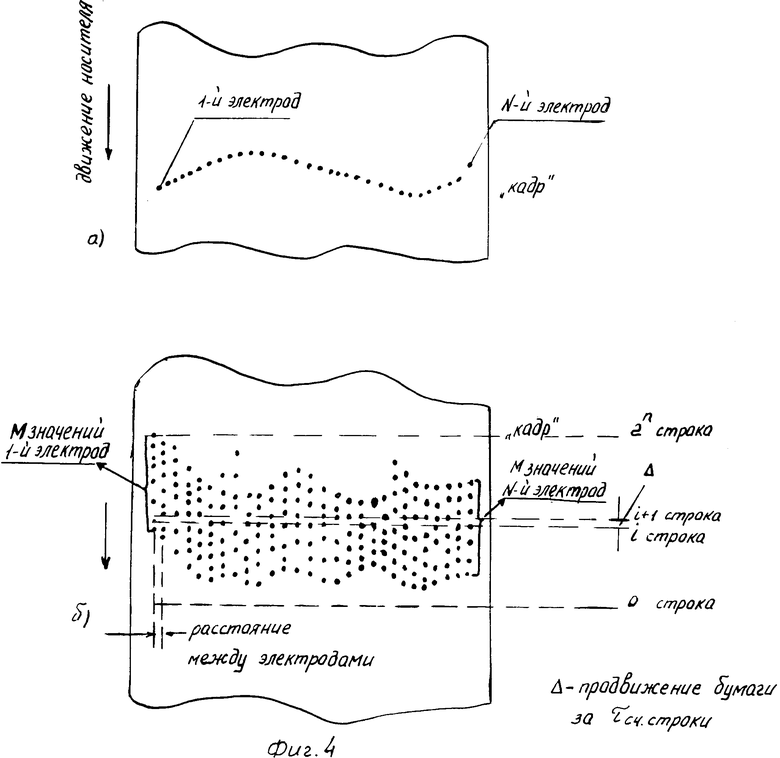

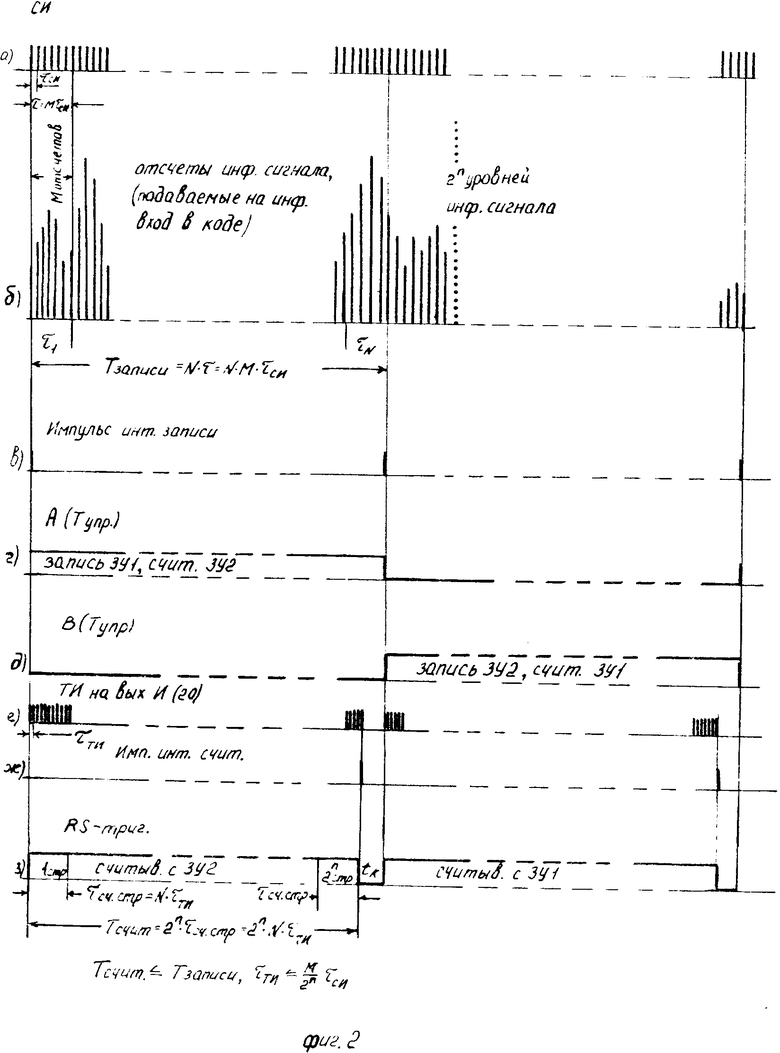

На фиг. 1 представлена функциональная схема устройства; на фиг. 2, 3 - временные диаграммы работы устройства; на фиг. 4 - вид изображения на носителе при регистрации.

Устройство содержит блоки 1, 2 памяти, элементы 3, 4 переключения, формирователь 5 адреса строк, элементы 6, 7 переключения, формирователь 8 адреса записи, формирователь 9 адреса электродов, дешифратор 10, элемент переключения 11, элемент 12 управления, RS-триггер 13, элементы И 14 и 15, делитель 16 частоты, формирователь 17, элементы 18 и 19 переключения, элемент И 20, формирователь 21 импульсов, генератор 22 тактовых импульсов, блок 23 выходных узлов, блок 24 электродов.

Устройство работает следующим образом.

Входной сигнал в виде n-разрядного параллельного кода поступает на вход устройства и далее на входы младших разрядов адреса первого блока памяти 1 или второго блока памяти 2. Переключение адресов осуществляется первым элементом переключения 3 для первого блока памяти 1 и шестым элементом переключения 4 для второго блока памяти 2 управляющим сигналом, снимаемым с прямого и инверсного плечей элемента управления 12, при этом, когда первый блок памяти 1 находится в режиме записи, второй блок памяти 2 находится в режиме считывания и наоборот. Режим записи информации осуществляется подачей на вход режима блоков памяти импульсов записи, которые формируются первым формирователем 17 импульсов из синхроимпульсов, сопровождающих код входного сигнала, и которые коммутируются элементами переключения 18 и 19. На информационный вход блока памяти, находящегося в режиме записи информации, подается сигнал логической единицы (синхроимпульсы) через схемы И 14, 15. Старшие разряды кода адреса в режиме записи информации поступают на блоки памяти 1, 2 через элементы переключения 6, 7 с формирователя 8 адреса записи. Формирователь 8 является двоичным счетчиком и запускается сигналом с частотой импульсов синхронизации, поделенной на коэффициент уплотнения М, определяемый делителем частоты 16. Количество кодовых комбинаций счетчика 8 должно быть равно количеству электродов регистрирующего блока 24.

Таким образом, при поступлении на вход устройства М значений входного сигнала и, следовательно, М синхроимпульсов СИ, расположенных на временном интервале τ (см. фиг. 2, а и б), производится запись "1" в ячейки блока памяти с одинаковыми старшими разрядами кода адреса и младшими разрядами кода адреса, соответствующими коду входного сигнала (интенсивности отсчетов). После поступления на вход устройства М˙N отсчетов, что соответствует временному интервалу Тзап (см. фиг. 2, б), на выходе счетчика 8 формируется импульс конца записи, меняющий состояние элемента управления (триггера) 12 и взводящий RS-триггер 13 (фиг. 2, в, г, д, е). Происходит смена режима блоков памяти. Положительный потенциал с выхода RS-триггера 13 через третью схему И 20 пропускает тактовые импульсы ТИ с выхода генератора 22 на входы второго формирователя импульсов 21 и формирователя 9 адреса электродов, выполненного в виде счетчика и формирующего код обращения к электродам и код старших разрядов адреса считывания, подаваемых на блоки памяти через элементы переключения 6. 7. Формирователь 9 адреса электродов отсчитывает N тактовых импульсов. Младшие разряды кода адреса считывания снимаются с формирователя 5 адреса строк, выполненного в виде двоичного счетчика с разрядностью n.

Таким образом осуществляется последовательный опрос блока 1 или 2 памяти, находящегося в режиме считывания. С частотой fти меняются старшие разряды кода адреса (N значений) и одновременно через дешифратор 10 производится обращение к N электродам, составляющим гребенку. Если из блоков 1, 2 памяти считывается "1", она проходит через элемент переключения 11, дешифратор 10, блок выходных узлов 23, и соответствующий электрод дает изображение точки на носителе. За один цикл формирователя 9 адреса электродов на носителе гребенкой электродов "рисуется" одна строка. Так как при этом младшие разряды кода адреса, снимаемые с формирователя 5 адреса строк, не меняются, а младшие разряды кода адреса при записи определялись кодом выходного сигнала, то каждая строка при изображении на носителе соответствует одному уровню интенсивности входного сигнала. Вертикальный столбик, "рисуемый" каждым электродом за интервал считывания Тсч, определяется старшими разрядами кода адреса блока памяти, потому что код электрода снимается с того же формирователя 9, что и старшие разряды кода адреса блока памяти в режиме считывания. А так как в режиме записи "1" заносилась в М ячеек блока памяти, имеющих один и тот же код старших разрядов, неотличающихся младшими разрядами кода адреса (они определялись кодом М отсчетов входного сигнала, расположенных во временном интервале τ), то следовательно, эти М отсчетов будут "сжаты" в одну вертикальную линию (см. фиг. 2, б, т. е. происходит сжатие во времени в М раз).

На фиг. 4, а показан вход изображения при регистрации в прототипе; на фиг. 4, б - в предлагаемом устройстве.

В предлагаемом устройстве за один интервал считывания регистрируется временной участок Тзаписи = M˙N˙τси входной информации, в прототипе Тзаписи = N˙τси. Это изображение составляет кадр, в котором уровни входного сигнала разворачиваются по вертикали за счет непрерывного движения носителя, а временные зоны τразворачиваются по горизонтали за счет расположения электродов в гребенке.

Время считывания "кадра", т. е. цикла считывания блока памяти, не должно превышать время цикла записи в блок памяти.

Тсч ≅Тзап (1)

Время записи Тзап = N τ= M˙N˙τси где τси- период СИ.

Время считывания Тсч = tстр ˙2n, где tстр - время считывания одной строки:

tстр = τти˙N, где τти- период ТИ,

2n - количество строк, равных количеству уровней входного сигнала.

Следовательно, Тсч = N˙2n˙τти .

Исходя из формулы (1),

τти< =

=  ,

,

fти> fси

fси

В конце интервала считывания Тсч сигналом переполнения с формирователя 5 адреса строк устанавливается в "0" RS-триггер и прекращается поступление ТИ на вход формирователя 9 адреса электродов. Считывание с блока памяти прекращается. Время tк обеспечивает отделение "кадров" друг от друга (фиг. 2з). Для привязки начала интервала считывания к концу интервала записи импульс конца записи с выхода формирователя 8 адреса записи обнуляет формирователь 9 адреса электродов и формирователь 5 адреса строк. Импульс записи блоков памяти формируется из синхроимпульсов первым формирователем 17 импульсов, обеспечивающим необходимые параметры импульсов, т. е. его временную задержку и длительность. Импульсы считывания, стробирующие выходной сигнал блока памяти, находящегося в режиме считывания формируются из тактовых импульсов вторым формирователем 21 импульсов и подаются на вход стробирования элемента переключения 11 (фиг. 2, а). Для обнуления блоков памяти второй формирователь 21 формирует импульс записи, следующий после импульса считывания и обнуляющий блок памяти, т. к. на информационном входе блока памяти в это время нулевой потенциал (фиг. 3а, б). Амплитуда и длительность импульсов, необходимых для регистрации сигнала электродами, обеспечивается блоком выходных узлов 23.

Таким образом, в предлагаемом устройстве так же, как и в прототипе, регистрация производится в виде кадров, содержащих информацию определенных временных интервалов и располагаемых поперек носителя. Кадры на носителе располагаются друг за другом. Но, если в прототипе кадр изображает временной участок входного процесса:

T = N˙τси, где τси- шаг дискретизации входного процесса, то в предлагаемом устройстве в кадре умещается временной участок входного процесса Т = M˙N˙τси , т. е. в М раз больше, где М - выбираемый коэффициент сжатия. Следовательно, в М раз будет экономнее расходоваться носитель.

Кроме того, такое компактное отображение информации во многих случаях удобнее, упрощает оценку информации.

(56) Авторское свидетельство СССР N 585507, кл. G 06 K 15/14, 1975.

Авторское свидетельство СССР N 492814, кл. G 06 F 15/46, 1974.

Использование: регистрация интенсивности быстроменяющихя процессов. Устройство содержит два блока памяти 1 и 2, семь элементов переключения 3, 4, 6, 7, 11, 18, 19, дешифратор 10, элемент управления 12, RS-триггер 13, три элемента И 14, 15, 20, два формирователя импульсов 17, 21, формирователь адреса строк 5, формирователь адреса записи 8, блок выходных узлов 23, блок электродов 24, генератор тактовых импульсов 22. Входной сигнал в виде двоичного кода заносится в блок памяти, объем которого обеспечивает запоминание информации определенного временного интервала. При этом интенсивность сигнала фиксируется в виде младших разрядов кода адреса запоминающих ячеек, в которые заносится сигнал логической единицы. Считывание с блока памяти на регистрирующие электроды осуществляется с временным сжатием информации, запись изображения производится поперек движения носителя. Непрерывная регистрация информации обеспечивается использованием двух поочередно меняющих режим записи - считывания блоков памяти. Предлагаемое устройство позволяет осуществить компактную, сжатую во времени регистрацию интенсивности быстроменяющихся процессов с малым расходом носителя информации. 4 ил.

УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ БЫСТРОМЕНЯЮЩЕГОСЯ ПРОЦЕССА, содержащее генератор тактовых импульсов, элемент управления, первый выход которого соединен с управляющими входами первого, второго, третьего и четвертого элементов переключения, первая группа информационных входов первого из которых является информационным входом устройства, формирователь адреса электродов, выход переполнения которого соединен с информационным входом формирователя адреса строк, разрядные выходы формирователя адреса электродов соединены с адресными входами дешифратора, выходы которого соединены через блок выходных узлов с входами блока электродов, два блока памяти, выходы которых соединены с информационными входами третьего элемента переключения, пятый элемент переключения, отличающееся тем, что в него введены первый, второй и третий элементы И, шестой и седьмой элементы переключения, RS-триггер, два формирователя импульсов, формирователь адреса записи и делитель частоты, вход которого является входом синхронизации устройства, а выход соединен со входом формирователя адреса записи, выход переполнения которого соединен с S-входом RS-триггера, с обнуляющими входами формирователя адреса электродов и формирователя адреса строк и с входом элемента управления, первый выход которого соединен с первым входом первого элемента И, а второй выход соединен с управляющими входами пятого, шестого и седьмого элементов переключения и с первым входом второго элемента И, вход делителя частоты соединен с вторыми входами первого и второго элементов И и через первый формирователь импульсов подключен к первым информационным входам четвертого и пятого элементов переключения, вторые ифнормационные входы которых подключены к первому выходу второго формирователя импульсов, а выходы соединены с входами режима соответственно первого и второго блоков памяти, информационные входы которых подключены к выходам одноименных элементов И, входы первой группы информационных входов шестого элемента переключения объединены с одноименными входами первой группы информационных входов первого элемента переключения, входы второй группы информационных входов первого и шестого элементов переключения подключены к разрядным выходам формирователя адреса строк, выход переполнения которого соединен с R-входом RS-триггера, выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход соединен с информационным входом формирователя адреса электродов и с входом второго формирователя импульсов, второй выход которого соединен со стробирующим входом третьего элемента переключения, выход которого соединен с информационным входом дешифратора, разрядные выходы формирователя адреса записи соединены с входами первых групп информационных входов второго и седьмого элементов переключения, входы вторых групп информационных входов которых подключены к разрядным выходам формирователя адреса электродов, выходы второго и седьмого элементов переключения соединены со входами старших разрядов адреса соответственно первого и второго блоков памяти, входы младших разрядов адреса которых подключены к выходам первого и шестого элементов переключения соответственно.

Авторы

Даты

1994-02-15—Публикация

1990-10-17—Подача