Изобретение относится к технике сбора и передачи цифровой информации и может быть использовано при сборе асинхронных потоков информации и формировании общего потока для передачи по синхронному каналу связи.

Известен способ синхронного сбора информации, при котором используется циклический опрос, заключающийся в периодическом поочередном опросе буферных регистров входных сообщений и формировании единого потока сообщений с частотой, равной сумме частот входных потоков (1).

Устройство для осуществления данного способа включает источники сигналов, буферные регистры сообщений по числу источников сигналов, коммутатор, синхpонизатор, блок формирования программ циклического опроса.

Недостатками данного способа и устройства для его осуществления, использующих циклический опрос и коммутацию сообщений, являются большая избыточность получаемой информации, поскольку частота опроса рассчитывается, исходя из максимальных частот выдачи информации источниками, и сложность обработки и декодирования получаемого потока на приемной стороне, в частности, при выборе массива данных конкретного пользователя. При этом также возникает трудность с поиском и извлечением необходимой для интерпретации и обработки этого массива служебной информации.

Данные недостатки устраняются (2). Первый недостаток преодолевается использованием средств и методов сокращения избыточности как в общем тракте, так и в трактах отдельных источников; второй недостаток, связанный с коммутацией сообщений, преодолевается за счет использования принципов пакетной передачи информации путем формирования в трактах отдельных источников, так называемых пакетов сигналов от этих источников. Пакеты представляют собой массивы данных объемом в несколько тысяч бит.

Однако использование в данном способе принципов сокращения избыточности в устройствах сбора информации приводит к неравномерности информационного потока на выходе этих устройств, к асинхронности следования сообщений или пакетов в тракте сжатой информации.

Известно множество способов сбора информации, в том числе пакетированный, от асинхронных источников в общий тракт. Способ сбора (3) заключается в направлении от центральной ЭВМ источникам информации программируемых циклических запросов, сборе ответных информационных массивов, отбраковке холостых массивов, формировании единого потока асинхронных массивов и его разравнивании. Устройство для его реализации содержит источники сигналов, блоки сжатия информации, буферные регистры, шину ответа, шину запроса, блок обработки информации, таймер, задающий генератор, процессор, счетчик адресов.

Недостатки данного способа и устройства заключаются в малом быстродействии, в большом объеме аппаратных средств, кроме этого требуется большой объем буферной памяти для разравнивания асинхронного потока пакетов.

Первые два недостатка устраняются (4). Это известный способ сбора информационных сообщений заключается в программном циклическом опросе входных регистров и формировании единого синхронного потока частотой, равной сумме частот входных потоков, в сокращении избыточности информации и формировании адресных информационных сообщений, формировании единого потока асинхронных сообщений, а также записи всего потока асинхронных сообщений в выходной блок буферной памяти и синхронном считывании информации из него с частотой следования выходных сообщений.

Устройство для реализации данного способа содержит источники информации, регистры памяти по числу входных трактов, циклический коммутатор, блок формирования программ опроса, состоящий из задающего генератора, таймера, счетчика, блока памяти и дешифратора; второй счетчик, второй блок памяти, третий счетчик, регистр памяти, формирователь сообщения, формирователь индивидуального адреса канала, блок сокращения избыточности.

Недостатки данного способа и устройства для его осуществления заключаются в следующем.

Во-первых, требуемая буферная память для разравнивания асинхронного потока велика (5). Через эту память проходит на выход весь информационный поток, приобретая большую временную задержку, что в ряде случаев недопустимо.

Во-вторых, информационные массивы передаются в выходной канал в порядке поступления, что исключает организацию приоритетного обслуживания источников.

Наиболее близким по технической сущности (прототипом) следует считать способ многоканальной передачи последовательности пакетов сигналов и устройство для его осуществления (6). Данный способ заключается в сборе, формировании существенных отчетов для каждого источника сигналов, преобразовании их в соответствующие асинхронные последовательности пакетов сигналов всех источников, объединении в групповую асинхронную последовательность пакетов с частотой следования, не меньшей суммы частот источников и выходного сигнала в канале передачи, в передаче в канал пакетов групповой асинхронной последовательности, частота следования которых соответствует частоте выходного сигнала в канале передачи, в задерживании части пакетов групповой асинхронной последовательности, частота которых превышает частоту выходного сигнала в канале передачи, и передачи ее в последующих циклах передачи, когда сумма частот источников сигналов меньше скорости выходного сигнала в канале передачи.

Устройство для осуществления данного способа содержит источники сигналов, блоки сокращения избыточности по числу источников, два блока буферных сдвоенных регистров, два циклических коммутатора, задающий генератор, таймер, пять счетчиков, три блока памяти, два переключателя, буферный регистр, ключ, три регистра, блок сравнения.

Недостатки данного способа и устройства для его осуществления заключаются в следующем.

Во-первых, при использовании этого способа и устройства для его реализации существует потенциальная возможность нарушения порядка следования во времени пакетов сигналов от тех канальных источников, ранее сформированные пакеты которых были задержаны для передачи в последующих циклах. Поясним это на следующем примере (6), фиг.1.

Пусть приоритет источников сигналов убывает слева направо, а интенсивность появления пакетов на первых выходах блоков 2 примерно одинакова. При функционировании устройства (6) пакеты сигналов наиболее приоритетных источников (их, согласно прототипу выбрано n/2 n общее число источников сигналов) будут беспрепятственно проходить в основной блок 14 памяти для передачи в синхронный канал. При этом число пакетов в кадре передачи выбрано равным n/2 (для нашего случая 2). Пакеты сигналов остальных источников (при наличии таковых у последних) будут накапливаться в буферном блоке памяти в общую очередь. Предположим, что первым в этой очереди стоит пакет от третьего слева источника, и при очередном цикле опроса, только в буферном регистре, соответствующем третьему каналу, содержится только что сформированный пакет, т.е. буферные регистры приоритетных источников пусты. Тогда по логике работы прототипа в этом цикле передачи в кадр передачи сначала войдет пакет из буферного регистра третьего канала, а затем первый, стоящий в очереди, из блока памяти, т. е. пакет того же канального источника, но сформированный несколько циклами раньше, т. е. предшествующий переданному первым. Таким образом, данные способ и устройство, его реализующее, не обеспечивают порядок следования во времени появления пакетов источников от неприоритетных источников. Это приводит к тому, что при передаче по синхронному каналу пакеты сигналов некоторых источников будут передаваться не в том порядке, в котором они были образованы на соответствующих выходах каналов. На приемном конце для восстановления очередности следования (по временному признаку, которым снабжен каждый пакет) необходимы будут дополнительные аппаратурные затраты (буферное ЗУ, блоки выделения номера пакетов и т.д.). Во избежание этих трудностей, а порой просто из-за невозможности (например, ограничение на вес бортовой аппаратуры ЛА) установки дополнительной аппаратуры, желательно избежать такого способа передачи и потребовать передачи пакетов от всех источников в порядке их возникновения во времени.

Во-вторых, использование в известном способе и устройстве для его реализации общего блока памяти для накопления, не прошедших в канал пакетов требует того, чтобы данный блок памяти обладал очень большой емкостью. В прототипе объем этого блока памяти определяется произведением максимального разностного потока между входным и выходным потоками на длительность сеанса связи.

Блок памяти с большим объемом требует для ввода-вывода информации наличие сложной схемы записи и считывания с многоразрядными счетчиками. Гораздо проще организация памяти такого же объема с помощью совокупности более мелких блоков. Кроме того блок памяти с большим объемом памяти менее надежен (8).

Целью изобретения является повышение достоверности передачи с учетом времени формирования информации за счет исключения возможности нарушения следования во времени пакетов любого канального источника.

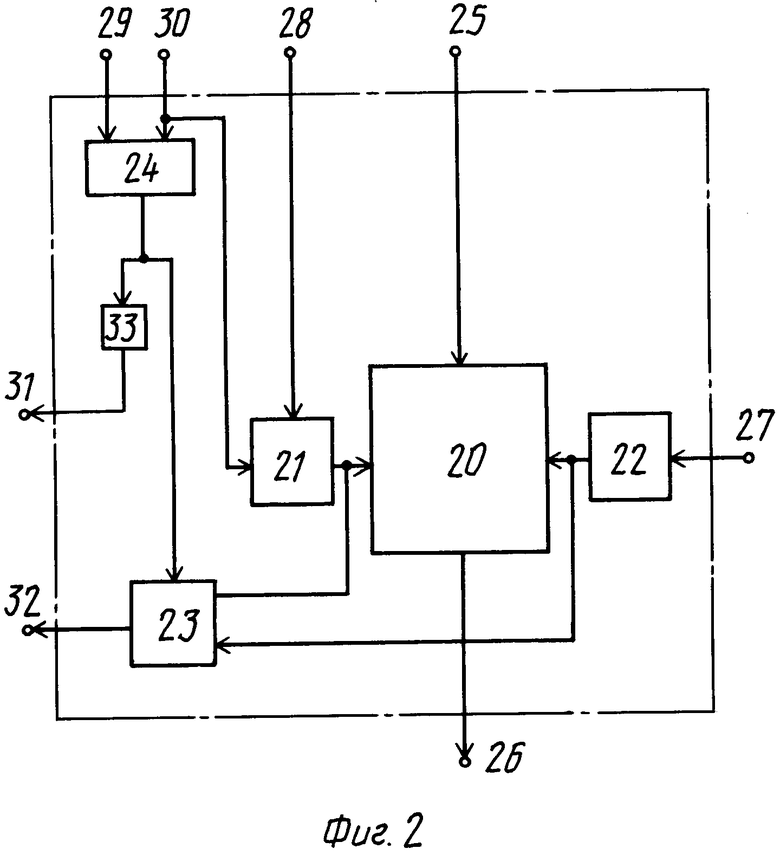

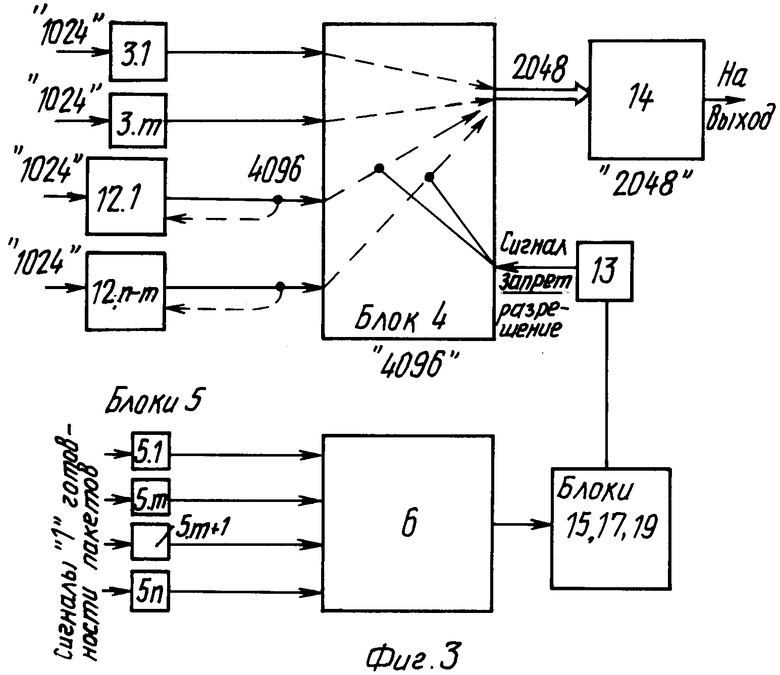

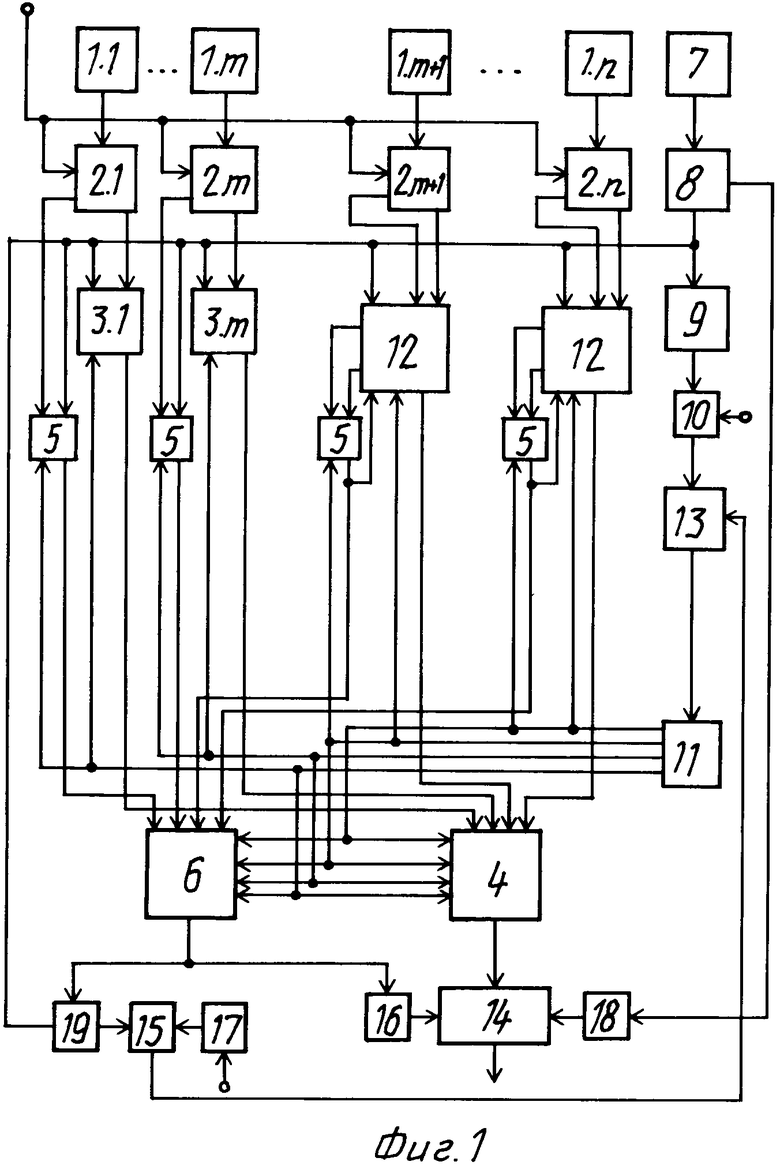

На фиг.1 приведена функциональная схема устройства; на фиг.2 выполнение блока канальной памяти; на фиг.3 структура опроса источников.

Устройство (фиг.1) содержит n источников 1.1-1.n цифровой информации, n блоков 2.1-2.n сокращений избыточности, m буферных регистров 3.1-3.m, где m число пакетов в цикле передачи в синхронный канал передачи, образующих первый блок регистров, первый циклический коммутатор 4, n буферных регистров 5.1-5. n, второй циклический коммутатор 6, задающий генератор 7, таймер 8, первый счетчик 9, первый блок памяти 10, дешифратор 11, m блоков канальной памяти 12-12. n, ключ 13, второй блок памяти 14, блок сравнения 15, третий счетчик 16 записи, регистр 17, второй счетчик 18 считывания, четвертый счетчик 19.

Устройство и работа блоков 1-11, 14-19 устройства аналогичны устройству и работе аналогичных соответствующих блоков прототипа.

Блок 12 канальной памяти содержит (фиг.2) элемент ИЛИ 24, элемент 33 задержки, счетчик 21 записи, счетчик 22 воспроизведения, блок 20 памяти, блок 23 сравнения, первый 30 и второй 29 входы элемента ИЛИ 24 образуют соответственно первый и второй синхровходы блока, выход элемента ИЛИ 24 соединен с управляющим входом блока 23 сравнения и входом элемента 33 задержки, выход которого является синхровыходом 31 блока, информационный вход блока 20 памяти является первым 25 информационным входом блока, вторым 28 информационным входом которого является установочный вход счетчика 21 записи, синхровход которого подключен к первому 30 синхровходу блока, первым информационным выходом 26 блока является информационный выход блока 20 памяти, вход записи которого подключен к выходу счетчика 21 записи и первому информационному входу блока 23 сравнения, выход которого является вторым информационным выходом 32 блока, входом считывания которого является установочный вход счетчика 22 воспроизведения, выход которого соединен с входом считывания блока 20 памяти и вторым информационным входом блока сравнения 23.

Устройство работает следующим образом.

Источники сигналов 1 опрашиваются с частотами опроса, формируемыми таймером 8 и выбранными, исходя из удовлетворения максимальных требований опроса каждого источника. Потоки выборок источников 1, представляющие собой потоки параллельных цифровых комбинаций постоянной длины, поступают на соответствующие входы блоков 2 сокращения избыточности, в которых формируются информационные пакеты сигналов. Функционирование блоков 2 полностью совпадает с функционированием аналогичных блоков прототипа. Так как частота слов (цифровых комбинаций), т.е. тактовая частота работы блока 2, выбрана вдвое выше частоты опроса источников, то выявление существенных выборок будет происходить уже в первой половине периодов опроса источников.

На выход блока 2 асинхронно поступают пакеты постоянного состава. Эти пакеты поступают на первые входы соответствующих буферных регистров 3.1-3.m, где m число пакетов в кадре передачи в асинхронный канал передачи и на первые входы блоков канальной памяти 12.m+1-12.n. Длина буферных регистров 3 и ячеек блоков 12 зависит от длительности пакетов. Одновременно с началом передачи из блоков 2 в регистры 3 и блоки 12 сформированных пакетов с другого выхода блоков 2 на первый вход соответствующих буферных регистров 5.1-5.m, либо на второй вход блоков канальной памяти 12.m+1-12.n поступает сигнал "1", который представляет собой сигнал готовности, т.е. информирует о том, что в соответствующем регистре 3 либо блоке 12 с начала очередности цикла опроса находится готовый пакет. Рассматриваемый сигнал готовности, проходя через блок 12, записывается в соответствующем ему буферном регистре 5 (он поступает на вход 28 блока 12 и выходит с выхода 32 на первый вход регистра 5). Таким образом, к началу следующего цикла работы всего устройства, т.е. цикла опроса первым 4 циклическим коммутатором буферных регистров 3.1-3.m и блоков канальной памяти 12.m+1-12.n и вторым циклическим коммутатором 6 буферных регистров 5.1-5.n, в регистрах 3.1-3.m и блоках 12.m+1-12.n пакеты, а в регистрах 5.1-5.n сигналы "1" могут либо находиться, либо отсутствовать, со случайным распределением этих событий. Работа устройства по записи пакетов и сигналов готовности синхронизируется задающим генератором 7, выходной сигнал которого формирует в таймере 8 сетку необходимых синхрочастот. На фиг. 1 показаны лишь основные связи задающего генератора 7 и таймера 8 с синхронизируемыми блоками. На этой фигуре не показана синхронизация блоков устройства по битам и параллельным словам и синхронизация источников цифровой информации 1 по частоте опроса, которая вдвое ниже частоты слов блоков 2. Работа устройства, в первую очередь коммутаторов 4.6 описывается с помощью соотнесения частоты следования пакетов и цикловой частоты, получаемой с выхода таймера 8.

Для того, чтобы программировать приоритетность опроса канальных источников, и соответственно узлов 3, 5, 12, в состав устройства введен первый блок памяти 10 программы опроса, в ячейках которого в требуемом порядке записана последовательность адресов узлов 3, 12, 5. Считывание этих адресов производится с помощью первого счетчика 9, который с частотой следования пакетов формирует последовательные адреса ячеек первого блока памяти 10, считываемые из которых цифровые комбинации, проходя ключ 13, после дешифрации в блоке 11 управляют ключами каналов циклических коммутаторов 4 и 6, а также сбросом регистров 3, 5 и опросом блока 12.

Для более четкого понимания прохождения информационных потоков по основным блокам устройства рассмотрим конкретный случай, который иллюстрируется на фиг.3. Пусть каждый поток одного из 4-х источников (фиг.1) имеет скорость передачи 1,024 мб/с. Суммарная скорость выходных потоков на входе первого циклического коммутатора 4 равна дискретной случайной величине в пределах от 0 до 4,096 мб/с. Пусть заданная выходная скорость в канале передачи равна 2,048 мб/с, следовательно, на входе блока 14 с выхода коммутатора 4 должны следовать пакеты со скоростью, равной 2,048 мб/с. Частота переключения коммутатора 4 выбирается не меньшей суммы максимальных частот входных и выходного потоков, т. е. по крайней мере 6,144 мб/с. Пусть (фиг.3) все источники имеют готовые пакеты для передачи. С началом очередного цикла опроса (передачи) первоначально опрашиваются высокоприоритетные (первый и второй) каналы, и пакеты сигналов беспрепятственно проходят через коммутатор 4 в блок памяти 14 для передачи. Параллельно ведется подсчет переданных пакетов в цикле с помощью блоков 6, 15, 17, 19, и при передаче порогового числа пакетов (в данном случае оно равно 2) вырабатывается сигнал, закрывающий ключ 13, что в свою очередь не позволяет опросить и передать пакеты в блок 14 от остальных источников коммутатора 4. При этом пакеты не опрошенных каналов накапливаются в порядке их поступления в соответствующих блоках канальной памяти 12.

Считывание пакетов сигналов из блоков канальной памяти 12 будет происходить всякий раз в последующих циклах по принципу "первым записан первым считан", когда после опроса приоритетных источников (первого и второго на фиг. 3) у них не окажется одного или более готовых пакетов для передачи. Функционирование коммутаторов 4 и 6 осуществляется следующим образом. Количество позиций в цикле опроса коммутаторов выбирается равным сумме максимального числа входных пакетов (4 для случая, рассматриваемого на фиг.1, n 4) и выходных пакетов (в данном случае m 2), при этом частота задающего генератора 7 всегда выбирается кратной выходной частоте.

Программа опроса регистров 3, в которых могут находиться текущие готовые входные пакеты, и блоков канальной памяти 12, в которых находятся пакеты, не прошедшие на выход в предшествующих циклах работы коммутаторов, а также текущие пакеты, причем пакеты, раньше записанные в блок 12, стоят раньше в очереди для передачи, составлена таким образом, чтобы вначале опрашивались высокоприоритетные источники (им соответствуют буферные регистры 3), а затем все остальные (им соответствуют блоки канальной памяти). Очередность опроса регистров 4 и блоков 12 определяется пользователем и записана в блоке 10.

В соответствии с готовностью входных пакетов в течение очередного цикла опроса на выходе первого циклического коммутатора 4 имеет место асинхронная последовательность готовых пакетов.

Одновременно с этой последовательностью на выходе второго циклического коммутатора 6 имеет место соответствующая асинхронная последовательность сигналов готовности "1". Последняя последовательность поступает на вход счетчика 16 для формирования очередного адреса записи соответствующего пакета в блок 14 и на счетный вход четвертого счетчика 19. Число, хранимое в счетчике 19, увеличивается при прохождении очередного пакета. В регистр 17 до начала работы введено число выходных пакетов в цикле передачи (в данном случае 2), исходя из заданной выходной скорости. После того, как число счета счетчика 19 сравняется с числом, хранимым регистре 17, на выходе блока сравнения 15 вырабатывается сигнал "1", закрывающий ключ 13, что в свою очередь прекращает выдачу адресов опроса в дешифратор 11, опрос и передача оставшихся пакетов сигналов от источников прекращается в данном цикле, так как число записанных пакетов в ходе данного цикла в блок 14 равно пороговому. В результате этого происходит накопление в порядке поступления пакетов во времени в блоках канальной памяти неприоритетных источников. С началом очередного цикла работы устройства счетчика 19 обнуляется синхросигналом от таймера 8. Первые пакеты каждого цикла (в данном случае их 2), число которых равно числу выходных пакетов, а также соответствует числу наиболее приоритетных источников, записываются во второй блок памяти 14, который служит для разравнивания выходного потока. Адреса записи формируются с помощью третьего счетчика 16, управляемого сигналами готовности пакетов с выхода коммутатора 6. Адреса считывания формируются с помощью счетчика 18 по соответствующим сигналам таймера 8.

Блок канальной памяти работает следующим образом.

На первый вход 25 блока 12 поступает текущий готовый пакет от блока 2, который заносится в блок памяти 20. Адреса записи формируются с помощью счетчика записи 21, управляемого сигналом готовности пакета, поступающим на второй вход 28 от второго выхода блока 2 и синхросигналом по первому синхровходу 30 от первого таймера 8. Адреса считывания формируются с помощью счетчика 22 по соответствующим сигналам циклического опроса, вырабатываемым дешифратором 11 и поступающим на вход 27 считавшимся блока 12. Синхросигнал, поступавший по входу 30 от таймера 8, служит для записи (при необходимости) нового пакета, проходя элемент ИЛИ 24 и элемент задержки 33, он поступает на синхровыход 31 блока 12 для подачи на синхровход соответствующего сдвоенного буферного регистра 5, хранящего информацию о наличии готового пакета для передачи у данного канала. Синхросигнал с выхода элемента ИЛИ 24 поступает на управляющий вход блока сравнения 23, который сравнивает ранее записанные значения счетчиков записи, числа, находящегося в счетчике 22 (это говорит о том, что в блоке 20 имеются пакеты для передачи ранее непередававшиеся) выдает сигнал готовности "1" на второй информационный выход 32, который поступает на первый вход соответствующего регистра 5 и устанавливает его в "1".

Выполнение операций способа с помощью описанного устройства не требует существенных пояснений. Емкость памяти блока 14 соответствует удвоенному количеству пакетов в цикле опроса-передачи, емкость блоков памяти канальной памяти не превышает произведения максимального потока пакетов данного канала на длительность сеанса связи.

Предлагаемый способ сбора информации обеспечивает согласование с синхронным выходным потоком асинхронных входных потоков, при этом исключается возможность нарушения порядка следования при передаче пакетов сигналов от неприоритетных источников, пакеты которых предварительно аккумулировались в соответствующих буферах каналов. Очевидно, что наибольшую вероятность (Р ≈ 1,0) непосредственного прохождения на выход (фиг.1) имеют пакеты первых по номеру опроса входных трактов, что позволяет организовать приоритетное обслуживание с прямым соответствием между номером опрашиваемого канала и его приоритетом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2007760C1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Устройство для сопряжения группы абонентов с каналом связи | 1990 |

|

SU1774342A1 |

| Способ автовыбора пакетной цифровой информации | 1984 |

|

SU1262737A1 |

| Многоканальный коммутатор | 1991 |

|

SU1780182A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство передачи и приема дискретной информации | 1989 |

|

SU1646066A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

Изобретение относится к технике сбора и передачи цифровой информации и может быть использовано при сборе асинхронных потоков и формирования общего потока для передачи по синхронному каналу связи. Цель изобретения повышение достоверности передачи с учетом времени формирования пакетов информации. Способ многоканальной передачи пакетов информации основан на формировании сигналов существенных отсчетов для каждого источника информации и преобразовании их в одноименные асинхронные последовательности пакетов информации, из которых формируют групповую асинхронную последовательность пакетов, частота следования импульсов в которой не меньше суммы частоты следования импульсов в одноименных асинхронных последовательностях пакетов информации источников информации и частоты передачи по каналу связи, и передают по каналу связи, далее задерживают асинхронные последовательности пакетов информации в порядке их формирования во времени для каждого источника информации, передачу групповой асинхронной последовательности пакетов информации осуществляют с приоритетных источников информации и в случае отсутствия какого-нибудь из них в цикле передаче в заданный момент времени осуществляют передачу сигналов других источников информации. Устройство, реализующее данный способ, содержит источник 1 информации, блоки 2 устранения избыточности и формирования пакетов, первый 3 и второй 5 блоки сдвоенных регистров, первый 4 и второй 6 циклические коммутаторы, задающий генератор 7, таймер 8, первый 9 и второй 18 счетчики, первый 10 и второй 14 блоки памяти, дешифратор 11, блоки 12 канальной памяти, ключ 13, блок 15 сравнения, счетчики записи 16 и воспроизведения 19, регистр 17. 2 с. и 1 з.п. ф-лы, 3 ил.

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М., Радиосвязь, 1988, с.415. | |||

Авторы

Даты

1995-09-10—Публикация

1992-06-24—Подача