Изобретение относится к передаче информации и может быть использовано при сокращении избыточности информации и формировании общего потока для передачи по каналу связи.

Известно устройство для сокращения избыточного информации (Л. I "Воздушно-космическая телеметрия", Воениздат, М. , 1968, с. 199-207, рис. 4.17), содержащее блок сравнения, блоки памяти, сумматор, счетчик, таймер, ключ, буферное запоминающее устройство, дешифратор, декодер и блок управления, при этом входы блока сравнения соединены с выходами первого и второго блоков памяти. Данное устройство обеспечивает преобразование входного потока информационных слов в поток существенных выборок, каждая из которых отличается от предшествующей более, чем на величину заранее установленного допуска. Устройство обеспечивает также накопление существенных выборок в буферном запоминающем устройстве и регулирование величины допуска в зависимости от степени заполнения буферного запоминающего устройства.

Недостатками данного устройства являются большой объем служебной адресно-временной информации, сопровождающей существенные выборки, сложная процедура определения амплитуды полученных выборок из-за необходимости учета динамики изменения допусков, неопределенность ситуации при длительном отсутствии существенных выборок (либо действительное отсутствие существенных выборок, либо отказ устройства).

Известно устройство для сокращения избыточности, содержащее блоки сравнения, блоки памяти, таймер, интегратор, блок задержки, ключи, элементы ИЛИ, вычислители приращений и элемент запрета, при этом входы первого блока сравнения соединены с выходами первого блока памяти и второго блока сравнения, а выход таймера подключен к входу первого ключа. Данное устройство обеспечивает сокращение избыточности информации по сложным алгоритмам при повышенной информативности.

Недостатками данного устройства являются большой объем служебной адресно-временной информации, усложненные критерии отбора существенных выборок, что сокращает поток выборок, но усложняет устройство, а это препятствует его использованию, на малогабаритных подвижных объектах. Кроме этого, не устранена неопределенность ситуации, связанной с длительным отсутствием существенных выборок.

Известно устройство для сокращения избыточности измерительной информации в состав адаптивной многоканальной системы передачи данных, содержащее первый регистр памяти, выход которого через блок сравнения подключен к выходу первого блока памяти, первый и второй адресные входы которого соединены с соответствующими входами второго блока памяти и с соответствующими выходами счетчика, первый выход таймера через преобразователь последовательного в параллельный код соединен с информационным входом устройства, второй выход соединен с синхровходом первого регистра памяти и словным входом преобразователя последовательно в параллельный вход, третий выход подключен к входу установки счетчика, а четвертый вход таймера соединен с синхровходами второго и третьего регистров памяти и словным входом преобразователя параллельного в последовательный вход, выход которого является информационным входом устройства, первый выход счетчика подключен к информационному входу третьего регистра памяти, первый и второй информационные входы второго блока памяти соединены соответственно с входами верхнего и нижнего значений допусков устройства, четвертый регистр памяти, и блок управления.

Данное устройство обеспечивает выделение существенных выборок и сокращение избыточности измерительной информации, при этом несколько сокращается объем служебной адресно-временной информации за счет группирования существенных выборок.

Данное устройство по назначению, достигаемому результату, технической сущности и совпадению с предлагаемым техническим решением по наибольшему количеству признаков выбрано прототипом.

Недостатками данного устройства являются: во-первых все еще большой объем служебной адресно-временной информации, вынужденное ограничение роста которого сокращает возможности повышения точности временной привязки существенных выборок, что ухудшает точность измерений, во-вторых неопределенность ситуации при длительном отсутствии существенных выборок, когда не ясно, произошел ли отказ устройства, либо действительно существенная выборка отсутствует, в-третьих, вытеснение некоторыми группами существенных выборок сжатой информации циклических опросов параллельно передаваемых других параметров, что приводит к потере информации.

Целью изобретения является повышение надежности и точности измерений.

Цель достигается тем, что в известное устройство для сокращения избыточности измерительной информации, содержащее блок сокращения избыточности, первые информационные входы которого соединены с соответствующими выходами преобразователя последовательного кода в параллельный, вход которого является входной шиной устройства, выходной шиной которого является выход преобразователя параллельного кода в последовательный, блок памяти, выходы которого соединены с соответствующими вторыми информационными входами блока сокращения избыточности, генератор синхросигналов, первый и второй выходы которого соединены соответственно с тактовым входом преобразователя последовательного кода в параллельный и словным входом преобразователя параллельного кода в последовательный, первый регистр и счетчик импульсов введены два дешифратора, элемент ИЛИ, триггер, инвертор, второй регистр, три ключа, выход первого из которых соединен со счетным входом счетчика импульсов, вход управления объединен с входом управления блока сокращения избыточности и подключен к выходу триггера, первый информационный вход которого объединен с входом обнуления счетчика импульсов и подключен к третьему выходу генератора синхросигналов, четвертый, пятый и шестой выходы которого соединены соответственно с информационным входом первого ключа, вторым информационным входом триггера и тактовым входом преобразователя параллельного кода в последовательный, первый информационный вход которого соединен с выходом первого регистра, а второй информационный вход подключен к выходу второго регистра и объединен с входом первого дешифратора, выход которого через инвертор соединен с входом управления второго ключа, информационный вход которого объединен с синхровходами блока сокращения избыточности и второго регистра, со словным входом преобразователя последовательного кода в параллельный и подключен к второму выходу генератора синхросигналов, а выход второго ключа соединен с синхровходом первого регистра и является выходом "флага" устройства, причем первый выход блока сокращения избыточности соединен с первым входом элемента ИЛИ, выход которого соединен с информационным входом второго регистра, а второй вход - с выходом третьего ключа, вход управления которого соединен с выходом второго дешифратора, входы которого объединены с соответствующими информационными входами первого регистра, соответствующими первыми адресными входами блока сокращения избыточности и подключены к выходам младших разрядов счетчика импульсов, выход старшего разряда которого соединен со вторым адресным входом блока сокращения избыточности и информационным входом третьего ключа, при этом вторые выходы блока сокращения избыточности соединены с информационными входами блока памяти.

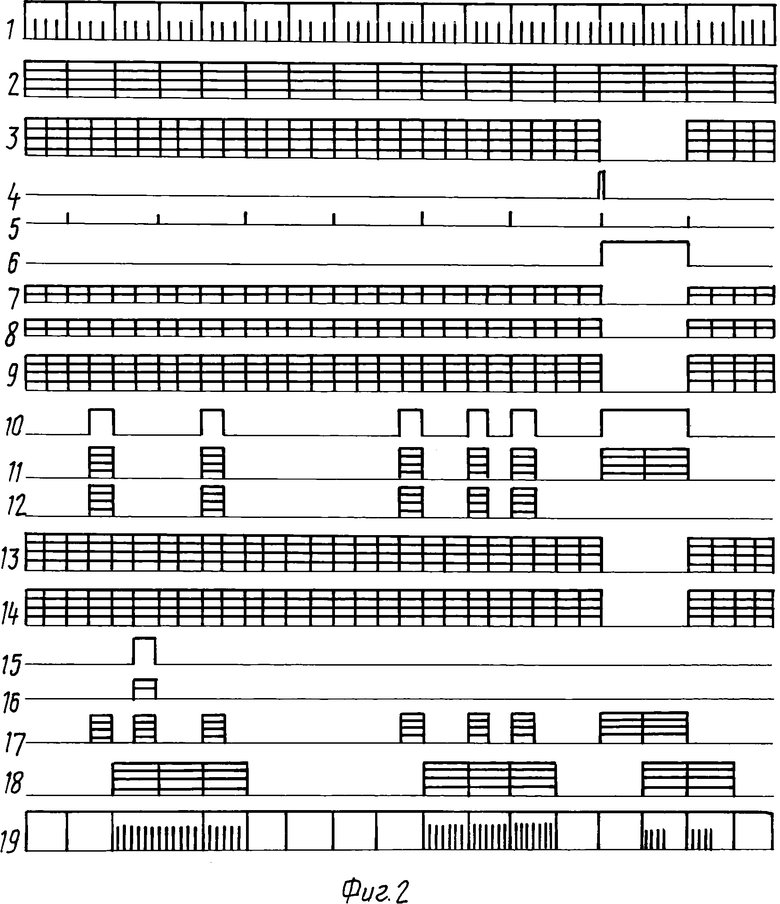

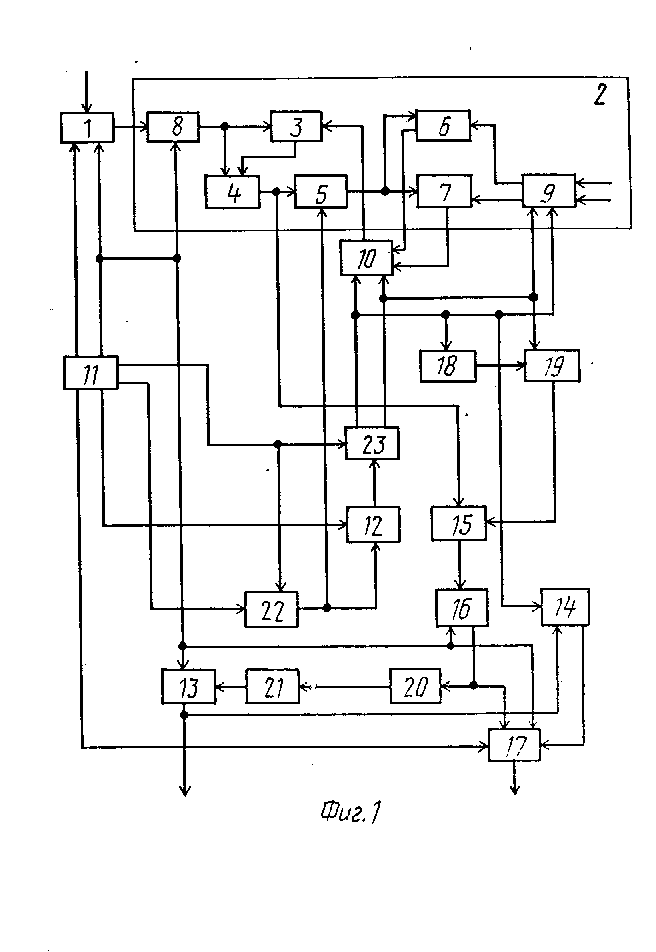

На фиг. 1 представлена схема устройства; а на фиг. 2 - временные диаграммы его работы.

Устройство содержит преобразователь 1 последовательного кода в параллельный, блок 2 сокращения избыточности, выполненный на блок 3 сравнения, ключах 4, 5, сумматорах 6 и 7, регистре 8, блоке памяти 9, блок памяти 10, генератор синхросигналов 11, ключи 12 и 13, регистр 14, элемент ИЛИ 15, регистр 16, преобразователь 17 параллельного кода в последовательный, дешифратор 18, ключ 19, дешифратор 20, инвертор 21, триггер 22, счетчик 23 импульсов.

Устройство работает следующим образом.

На информационный вход устройства поступает поток циклических выборок постоянной длины, соответствующий выходу многоканального циклического коммутатора (фиг. 2-1). После преобразования в параллельный код в преобразователе 1 параллельные циклические выборки запоминаются в регистре 8 памяти, обновляемом пословно (фиг. 2-2), и подаются на первый информационный вход блока 3 сравнения. На второй информационный вход блока 3 сравнения с выхода первого блока 10 памяти поступает сигнал о наличии существенной выборки (фиг. 2-10), вследствие чего открывается ключ 4 и входная текущая выборка поступает с удвоенной словной частотой поток эталонных сигналов, нечетные из которых представляют собой сумму значения предшествующей существенной выборки данного канала со значением верхнего допуска, а четные - сумму значения предшествующей существенной выборки этого же канала со значением нижнего допуска (фиг. 2-3). Эталонные сигналы, хранящиеся в блоке 10 памяти, формируются с помощью сумматоров 6, 7 и блока 11 памяти, в котором постоянно хранятся записанные в него через первый и второй информационные входы верхние и нижние значения допусков. Две группы эталонных сигналов в блоке 10 памяти хранятся соответственно в ячейках с нечетными и четными значениями адресов и считываются соответственно в первую и вторую половину каждого словного интервала. Формирование адресов считывания эталонных сигналов с выхода блока 10 памяти происходит следующим образом. С помощью частоты цикла работы устройства (третий выход генератора 11, фиг. 2-4) и кратной ей частоты цикла поступления выборок на вход устройства (пятый выход генератора 11 (фиг. 2-5), поступающих соответственно на второй и первый информационные входы триггера 22, формируется сигнал управления ключами 5 и 12 (фиг. 2-6), длительность которого соответствует длительности одного цикла входных выборок. Этот цикл (например, один из 16-256 циклов, совместно составляющих цикл работы устройства) представляет собой так называемый "теневой" цикл, в котором исходные циклические выборки не подвергаются операции сокращения избыточности, т. е. априорно считываются "существенными" и все проходят на выход устройства. Это преследует цель убедиться в том, что устройство работает нормально, а возможное отсутствие существенных выборок между выборками теневого цикла каждого цикла работы устройства свидетельствуют об их действительном отсутствии, во-вторых, с началом теневого цикла связана адресно-временная привязка каждой существенной выборки. При этом отличающийся адресно-временной код имеет каждая исходная циклическая выборка на протяжении всего цикла работы устройства. Например, при уплотнении во входном цикле выборок 256 каналов (8 разрядов) и при 256 циклах выборок в цикле работы устройства (8 разрядов) адресно-временной код каждой позиции, на которой размещена исходная циклическая выборка в цикле работы устройства, соответствует 16 разрядам, т. е. вдвое больше типичной длительности самой информационной части выборки (8 разрядов). Меры по сокращению выходной адресно-временной информации будут описаны ниже.

При открытии ключа 12 на его выход поступают счетные импульсы с выхода генератора 11, в соответствии с которыми после установки в начале каждого цикла работы устройства счетчик 23 производит и формирование адресов считывания информации из блоков 10 и 9 памяти (фиг. 2-7 - младшие разряды адреса, фиг. 2-8 - старшие разряды). Во время теневого цикла формируется адрес нулевой ячейки, в которой "хранятся" нулевое эталонное слово (фиг. 2-9). При сравнении с нулевым словом любой текущей выборки, поступающей на первый информационный вход блока сравнения 3, с выхода блока 3 обязательно поступает на выход этого ключа. Аналогичный сигнал вырабатывается и при сравнении эталонных сигналов с текущими выборками, если последние выходят за пределы допуска, т. е. превышает эталонный сигнал, соответствующий верхнему значению допуска, или будут ниже эталонного сигнала, соответствующего нижнему значению допуска (фиг. 2-11). С выхода первого ключа 4 поток существенных выбором и циклических выборок теневого цикла через элемент ИЛИ 15 поступают на информационный вход регистра 16. Через ключ 5 проходит только поток одних существенных выборок (фиг. 2-12), поскольку только для них на входы сумматоров 6 и 7 поступают сигналы о значениях допусков (фиг. 2-13 и 2-14 соответственно). На выходах этих сумматоров образуются эталонные сигналы, представляющие соответственно сумму текущей существенной выборки и значений верхнего и нижнего допусков. Синхронно с поступлением существенной выборки в регистр 16 в регистр 14 поступают младшие разряды адресно-временного кода, соответствующего положению данной существенной выборки на интервале цикла работы устройства. Для сокращения общего объема адресно-временной информации ее старшие разряды передаются в специально отведенном информационном канале. В исходном циклическом потока (фиг. 2-1) в этом канале передается нулевое слово. Код адреса выделенного канала дешифрируется с помощью дешифратора 20, формирующего управляющий сигнал открытия ключа 19 (фиг. 2-15). Соответствующие старшие разряды адреса, общие для всей группы младших разрядов, проходят через ключ 19 (фиг. 2-16), элемент ИЛИ 15 и совместно с существенными выборками и выборками теневого цикла записываются в регистр 16 (фиг. 2-17), считывание информации с выхода которого производится со словной частотой входного потока (фиг. 2-18). Сигнал считывания соответственного адресно-временного кода формируется с помощью первого дешифратора 18, выделяющего нулевые слова (т. е. слова, не являющиеся существенными выборками), инвертора 21 и ключа 13, пропускающего импульсы словной частоты только при наличии существенных выборок и наборок теневого цикла. Выходной сигнал ключа 13 является также выходом флага существенной выборки устройства. На информационный выход устройства поступают последовательно поток информационных выборок, представляющий собой совокупность поток существенных выборок, выборок теневых циклов и выборок информационных каналов с информацией старших разрядов адресно-временного кода (фиг. 2-19). При этом существенные выборки и выборка с адресно-временным кодом сопровождается пословной время-адресной информацией с ненулевым значением. (56) Авторское свидетельство СССР N 1462392, кл. G 08 C 19/28, 1987.

Авторское свидетельство СССР N 815935, кл. Н 04 J 6/00, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ МНОГОКАНАЛЬНОЙ ПЕРЕДАЧИ ПАКЕТОВ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043658C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С НОСИТЕЛЯ МАГНИТНОЙ ЗАПИСИ | 1992 |

|

RU2018174C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ БЫСТРОМЕНЯЮЩЕГОСЯ ПРОЦЕССА | 1990 |

|

RU2007756C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАКСИМАЛЬНОГО ЗНАЧЕНИЯ ИМПУЛЬСНОГО АНАЛОГОВОГО СИГНАЛА | 1993 |

|

RU2063048C1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2044405C1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2080608C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| КАРДИОМОНИТОР КВАНТИЛЬНЫЙ | 1994 |

|

RU2107455C1 |

Изобретение относится к технике передачи информации и может найти применение в измерительных системах для сокращения избыточности информации и формировании потока для передачи по каналу связи. Целью изобретения является повышение надежности и точности измерений. Цель изобретения достигается за счет того, что в известное устройство, содержащее преобразователь 1 последовательного кода в параллельный, блок 2 сокращения избыточности, блок 10 памяти, генератор 11 синхросигналов, регистр 16, счетчик 23 импульсов и преобразователь 17 параллельного кода в последовательный, введены два дешифратора 18 и 20, элемент ИЛИ 15, ключи 12, 13 и 19, триггер 22, инвертор 21 и регистры 14. 1 з. п. ф-лы, 2 ил.

Авторы

Даты

1994-02-15—Публикация

1990-05-14—Подача