Изобретение относится к электро- и радиосвязи и может использоваться в проводных, радио-, радиорелейных и космических линиях связи.

Известно устройство дня передачи и приема дискретных сообщений, содержащее на передающей стороне последовательно соединенные источник информации, канальный модулятор, передатчик, синх- роблок и генератор последовательностей, а на приемной стороне- последовательно соединенные приемник, канальный демодулятор и формирователь канальных символов и синхроблок; передающая и приемная стороны устройства соединены посредством линии связи.

Однако такое устройство не позволяет осуществить передачу дополнительной информации и имеет низкую помехоустойчивость связи.

Наиболее близким к заявляемому устройству является устройство для передачи и приема дискретных сообщений, включающее в себя на передней стороне последовательно соединенные источник информации, канальн.ый модулятор, передатчик, синхроблок, генератор последовательностей и коммутатор, и источник информации, выход которого соединен с управляющим входом коммутатора, первый выход синхроблока подключен к входу источника информации, а второй соединен с входом источника информации и синхровходом передатчика, а на приемной стороне - последовательно соединенные приемник, первые канальный демодулятор и формирователь символов, коммутатор,последовательно соединенные вторые канальный демодулятор и формирователь символов, последовательно соединенные первый накопитель, вычитающее устройство и третий формирователь символов, выход которого соединен с управляющим входом коммутатора, второй накопитель, последовательно соединенные синхроблок и формирователь синхроимпульсов, последовательно соединенный с формирователем символов первый регистр сдвига,и последовательно с вторым формирователем символов - второй регистр сдвига, причем тактовые входы обоих регистров объединены с тактовыми входами канальных демодуляторов, накопителей и соединены с выходов формирователя синхроимпульсов, выходы первого и второго регистров подключены к соответствующим сигнальным входом коммутатора, вход второго канального демодулятора подключен к ыыходу приемника, а его выход соединен с входом второго накопителя, выход которого подключен к р.торому сигнальному

входу вычитающего устройства, выход первого канального демодулятора подключен к входу первого накопителя, вход синхроблока подключен к синхровыходу приемника, а 5 его выход - к синхровходу вычитающего устройства; приемная и передающая стороны устройства соединены между собой посредством линии связи.

Однако такое устройство имеет низкую

10 помехоустойчивость связи.

Цель изобретения - повышение помехоустойчивости связи.

Для достижения поставленной цели в устройство для передачи и приема дискрет5 ных сообщений на передающей стороне введены последовательно соединенные регистр сдвига, сумматор по модулю два и ключ, причем вход регистра сдвига соединен с выходом источника информации, а его

0 выход - с информационным входом канального модулятора, выход ключа подключен к управляющему входу коммутатора, такто- вые-входы регистра сдвига и ключа соединены соответственно с первым и вторым

5 .выходами синхроблока, а на приемной стороне введены последовательно соединенные сумматор по модулю два и второй ключ, объединенные с регистром сдвига в блок обнаружения и исправления ошибок, при0 чем первая группа входов второго ключа соединена с инверсными выходами К первых разрядов регистра, вторая группа его входов объединен;) с К первыми информационными входами сумматора по модулю

5 два и с прямыми выходами К первых разрядов регистра, а его выходы соединены с установочными входами К первых разрядов регистра, вход регистра, его тактовыый вход, (К+1)-ый информационный вход сум0 матора по модулю два и его управляющий вход, и сигнальные входы второго ключа являются, соответственно, первым информационным,тактовым, вторым информационным, управляющим и сигналь5 ными входами блока обнаружения и исправления ошибок, а информационный выход регистра сдвига является выходом устройства, последовательнс соединенные первая линия задержки, первый блок выбора мини0 мума, первый ключ, ЗУ и дешифратор, последовательно соединенные вторая линия задержки и блок выбора минимума, и элемент задержки, причем выходы первого и второго канальных демодуляторов соедине5 ны соответственно с входами первой и второй линий задержки, выходы которых подключены соответственно к входам первого и второго формирователей символов, выходы второго блока выбора минимума соединены с второй группой входов первого

ключа, выходы первого и второго формирователей символов подключены к соответствующим сигнальным входам коммутатора, выход которого соединен с первым информационным входом блока обнаружения и исправления ошибок, выход элемента задержки подключен к управляющему входу блока обнаружения и исправления ошибок, сигнальные входы которого соединены с выходами дешифратора, а второй информационный вход объединен с управляющим входом первого ключа и подключен к выходу третьего формирователя символов, тактовые входы ЗУ, первых и вторых линий задержки и блоков выбора минимума элемента задержки и блока обнаружения и исправления ошибок подключены к выходу формирователя синхроимпульсов, вход элемента задержки соединен с выходом синхроблока.

Основными отличительными признаками предлагаемого устройства по сравнению с прототипом является наличие регистра сдвига, сумматора по модулю два и ключа с соответствующими связями на передающей стороне и двух линий задержки, блоков выбора минимума и ключей. ЗУ. дешифратора, сумматора по модулю два и элемента задержки с соответствующими связями - на приемной стороне.

Применение указанных блоков с соответствующими связями для повышения помехоустойчивости связи не является известным техническим решением. Таким образом, предложенное техническое решение удовлетворяет критерию существенных отличий.

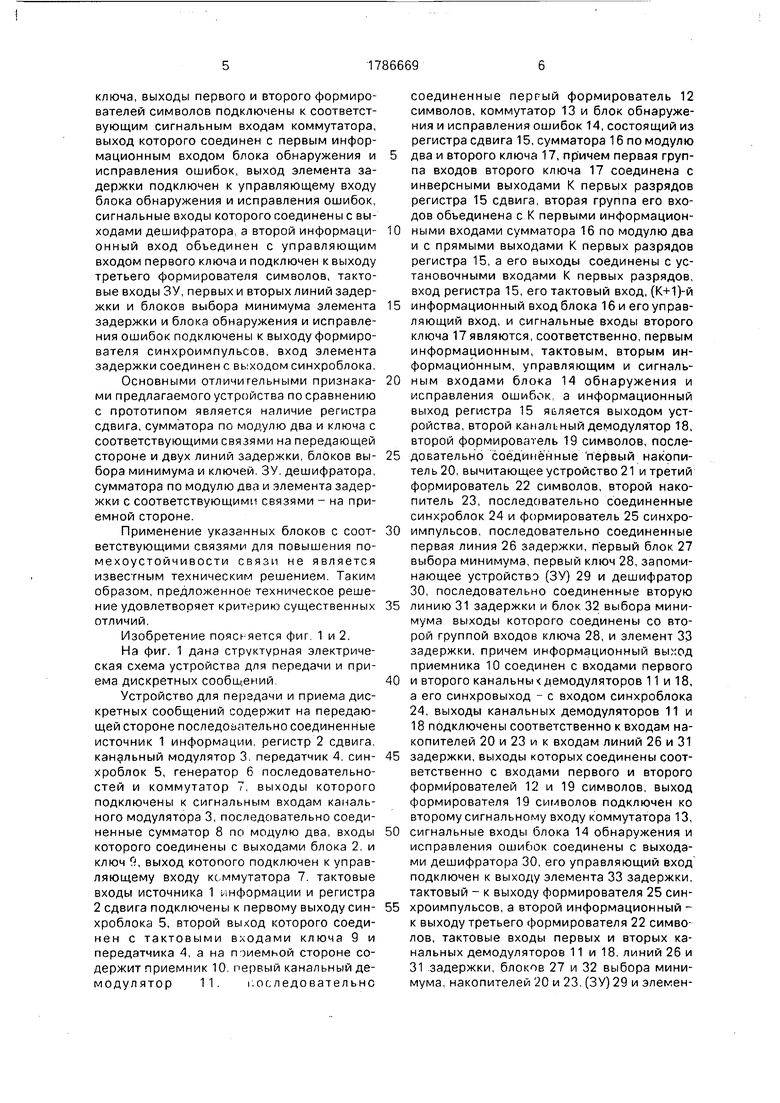

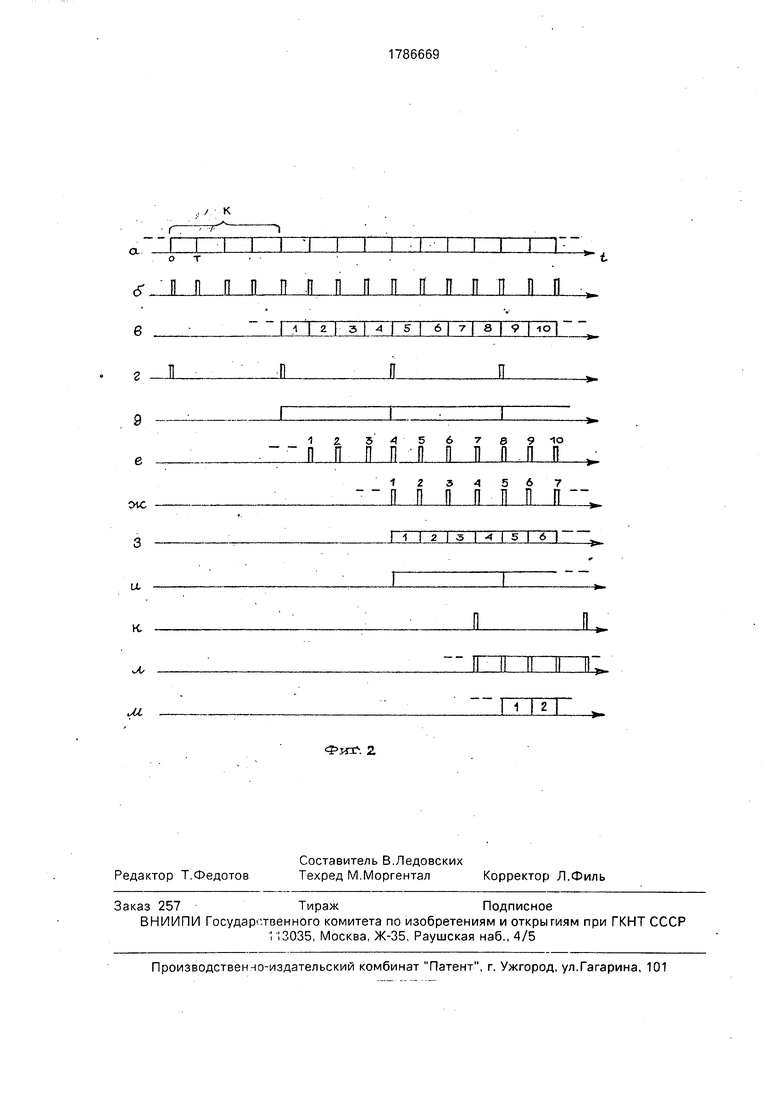

Изобретение поясняется фиг. 1 и 2.

На фиг. 1 дана структурная электрическая схема устройства для передачи и приема дискретных сообщений.

Устройство для передачи и приема дискретных сообщений содержит на передающей стороне последовательно соединенные источник 1 информации, регистр 2 сдвига, канальный модулятор 3. передатчик 4. син- хроблок 5, генератор 6 последовательностей и коммутатор 7, выходы которого подключены к сигнальным входам канального модулятора 3, последовательно соединенные сумматор 8 по модулю два, входы которого соединены с выходами блока 2. и ключ 5, выход котооого подключен к управляющему входу коммутатора 7. тактовые входы источника 1 информации и регистра 2 сдвига подключены к первому выходу синхроблока 5, второй выход которого соединен с тактовыми входами ключа 9 и передатчика 4, а на приемной стороне содержит приемник 10. первый канальный демодулятор 11. последовательно

соединенные перпый формирователь 12 символов, коммутатор 13 и блок обнаружения и исправления ошибок 14, состоящий из регистра сдвига 15, сумматора 1 б по модулю

два и второго ключа 17, причем первая группа входов второго ключа 17 соединена с инверсными выходами К первых разрядов регистра 15 сдвига, вторая группа его входов объединена с К первыми информацион0 ными входами сумматора 16 по модулю два и с прямыми выходами К первых разрядов регистра 15, а его выходы соединены с установочными входами К первых разрядов, вход регистра 15, его тактовый вход, (К+1)-й

5 информационный вход блока 16 и его управляющий вход, и сигнальные входы второго ключа 17 являются, соответственно, первым информационным, тактовым, вторым информационным, управляющим и сигналь0 ным входами блоха 14 обнаружения и исправления ошибок, а информационный выход регистра 15 является выходом устройства, второй канальный демодулятор 18, второй формирователь 19 символов, после5 довательно соединённые первый накопитель 20, вычитающее устройство 21 и третий формирователь 22 символов, второй накопитель 23, последовательно соединенные синхроблок 24 и формирователь 25 синхро0 импульсов, последовательно соединенные первая линия 26 задержки, первый блок 27 выбора минимума, первый ключ 28, запоминающее устройство (ЗУ) 29 и дешифратор 30, последовательно соединенные вторую

5 линию 31 задержки и блок 32 выбора минимума выходы которого соединены со второй группой входов ключа 28, и элемент 33 задержки, причем информационный выход приемника 10 соединен с входами первого

0 и второго канальны демодуляторов 11 и 18, а его синхровыход - с входом синхроблока 24, выходы канальных демодуляторов 11 и 18 подключены соответственно к входам накопителей 20 и 23 и к входам линий 26 и 31

5 задержки, выходы которых соединены соответственно с входами первого и второго формирователей 12 и 19 символов, выход формирователя 19 символов подключен ко второму сигнальному входу коммутатора 13,

0 сигнальные входы блока 14 обнаружения и исправления ошибок соединены с выходами дешифратора 30, его управляющий вход подключен к выходу элемента 33 задержки, тактовый - к выходу формирователя 25 син5 хроимпульсов, а второй информационный - к выходу третьего формирователя 22 символов, тактовые входы первых и вторых канальных демодуляторов 11 и 18, линий 26 и 31 задержки, блоков 27 и 32 выбора минимума, накопителей 20 и 23. (ЗУ) 29 и элемента 33 задержки подключены к выходу формирователя 25 синхроимпульсов, выход синхроблока 24 соединен с тактовым входом вычитающего устройства 21 и с входом элемента 33 задержки, выход третьего фор- мирователя 22 символов подключен куправ- ляющим входам коммутатора 13 и первого ключа 28; приемная и передающая стороны устройства соединены посредством линии связи 34.

Устройство для передачи и приема дискретных сообщений работает следующим образом.

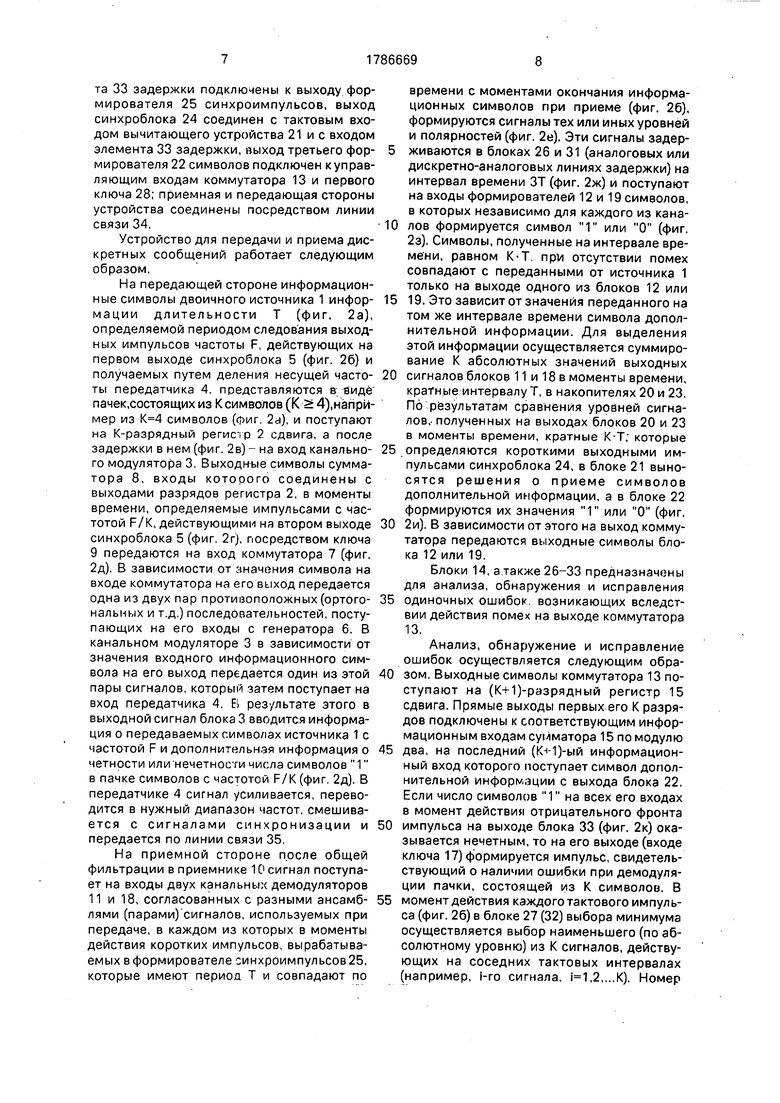

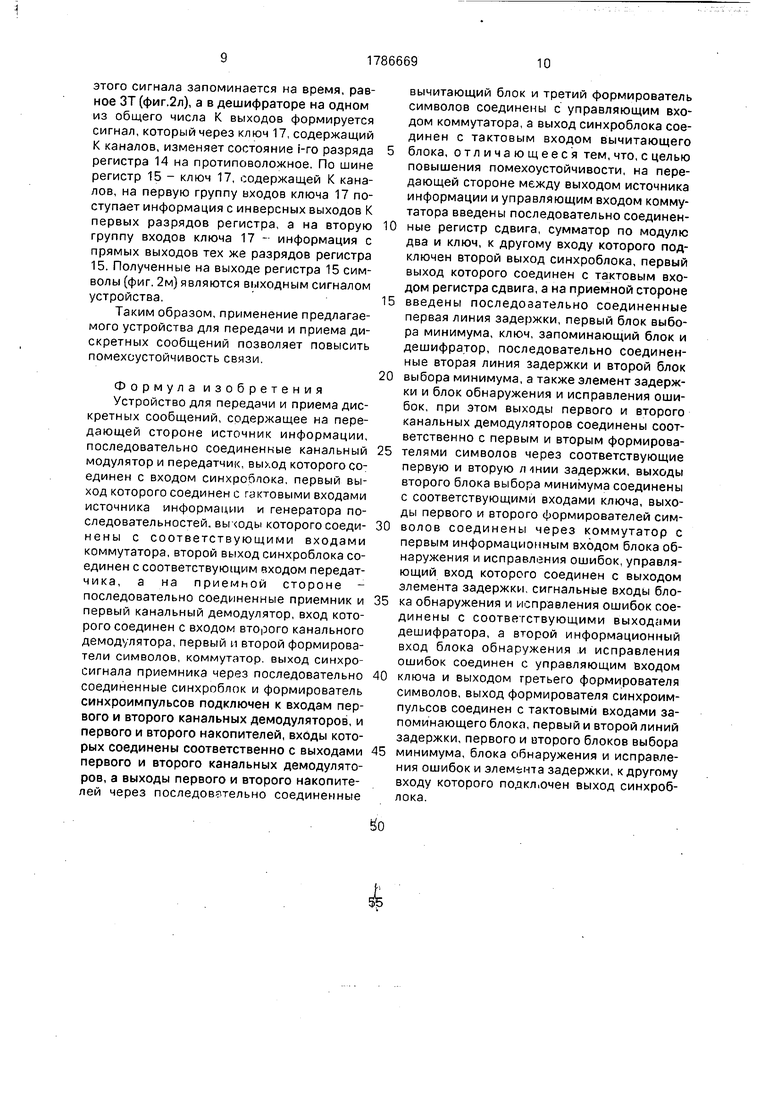

На передающей стороне информационные символы двоичного источника 1 инфор- мации длительности Т (фиг. 2а), определяемой периодом следования выходных импульсов частоты F, действующих на первом выходе синхроблока 5 (фиг. 26) и получаемых путем деления несущей часто- ты передатчика 4, представляются в виде пачек,состоящих из К символов (К .например из символов (фиг. 2а), и поступают на «-разрядный регистр 2 сдвига, а после задержки в нем (фиг. 2в) - на вход канально- го модулятора 3. Выходные символы сумматора 8, входы которого соединены с выходами разрядов регистра 2, в моменты времени, определяемые импульсами с частотой F/K, действующими на втором выходе синхроблока 5 (фиг. 2г), посредством ключа 9 передаются на вход коммутатора 7 (фиг. 2д). В зависимости от значения символа на входе коммутатора на его выход передается одна из двух пар противоположных (ортого- нальных и т.д.) последовательностей, поступающих на его входы с генератора 6. В канальном модуляторе 3 в зависимости от значения входного информационного символа на его выход передается один из этой пары сигналов, который затем поступает на вход передатчика 4. Ei результате этого в выходной сигнал блока 3 вводится информация о передаваемых символах источника 1 с частотой F и дополнительная информация о четности или нечетности числа символов 1 в пачке символов с частотой F/K (фиг. 2д). В передатчике 4 сигнал усиливается, переводится в нужный диапазон частот, смешивается с сигналами синхронизации и передается по линии связи 35,

На приемной стороне после общей фильтрации в приемнике 10 сигнал поступает на входы двух канальных демодуляторов 11 и 18, согласованных с разными ансамб- лями (парами) сигналов, используемых при передаче, в каждом из которых в моменты действия коротких импульсов, вырабатываемых в формирователе синхроимпульсов 25, которые имеют период Т и совпадают по

времени с моментами окончания информационных символов при приеме (фиг. 26), формируются сигналы тех или иных уровней и полярностей (фиг. 2е). Эти сигналы задерживаются в блоках 26 и 31 (аналоговых или дискретно-аналоговых линиях задержки) на интервал времени ЗТ (фиг. 2ж) и поступают на входы формирователей 12 и 19 символов, в которых независимо для каждого из каналов формируется символ 1 или О (фиг. 2з). Символы, полученные на интервале времени, равном К-Т. при отсутствии помех совпадают с переданными от источника 1 только на выходе одного из блоков 12 или 19. Это зависит от значения переданного на том же интервале времени символа дополнительной информации. Для выделения этой информации осуществляется суммирование К абсолютных значений выходных сигналов блоков 11 и 18 в моменты времени, кратные интервалу Т, в накопителях 20 и 23. По результатам сравнения уровней сигналов,- полученных на выходах блоков 20 и 23 в моменты времени, кратные К-Т; которые определяются короткими выходными импульсами синхроблока 24, в блоке 21 выносятся решения о приеме символов дополнительной информации, а в блоке 22 формируются их значения 1 или О (фиг. 2и). В зависимости от этого на выход коммутатора передаются выходные символы блока 12 или 19.

Блоки 14, а также 26-33 предназначены для анализа, обнаружения и исправления одиночных ошибок, возникающих вследст- вии действия помех на выходе коммутатора 13.

Анализ, обнаружение и исправление ошибок осуществляется следующим образом. Выходные символы коммутатора 13 поступают на (К+1)-разрядный регистр 15 сдвига. Прямые выходы первых его К разрядов подключены к соответствующим информационным входам сумматора 15 по модулю два, на последний (К-И)-ый информационный вход которого поступает символ дополнительной информации с выхода блока 22. Если число символов 1 на всех его входах в момент действия отрицательного фронта импульса на выходе блока 33 (фиг, 2к) оказывается нечетным, то на его выходе (входе ключа 17) формируется импульс, свидетельствующий о наличии ошибки при демодуляции пачки, состоящей из К символов. В момент действия каждого тактового импульса (фиг. 26) в блоке 27 (32) выбора минимума осуществляется выбор наименьшего (по абсолютному уровню) из К сигналов, действующих на соседних тактовых интервалах (например, i-ro сигнала, ,2,...К). Номер

этого сигнала запоминается на время, равное ЗТ(фиг.2л), а в дешифраторе на одном из общего числа К выходов формируется сигнал, который через ключ 17, содержащий К каналов, изменяет состояние i-ro разряда регистра 14 на протиповоложное. По шине регистр 15 - ключ 17, содержащей К каналов, на первую группу входов ключа 17 поступает информация с инверсных выходов К первых разрядов регистра, а на вторую группу входов ключа 17 - информация с прямых выходов тех же разрядов регистра 15. Полученные на выходе регистра 15 символы (фиг. 2м) являются выходным сигналом устройства.

Таким образом, применение предлагаемого устройства для передачи и приема дискретных сообщений позволяет повысить помехоустойчивость связи.

Формула изобретения Устройство для передачи и приема дискретных сообщений, содержащее на передающей стороне источник информации, последовательно соединенные канальный модулятор и передатчик, выход которого соединен с входом синхроблока, первый выход которого соединен с тактовыми входами источника информации и генератора последовательностей, выходы которого соединены с соответствующими входами коммутатора, второй выход синхроблока соединен с соответствующим входом передат- чика, а на приемной стороне последовательно соединенные приемник и первый канальный демодулятор, вход которого соединен с входом второго канального демодулятора, первый и второй формирователи символов, коммутатор, выход синхросигнала приемника через последовательно соединенные синхроблок и формирователь синхроимпульсов подключен к входам первого и второго канальных демодуляторов, и первого и второго накопителей, входы которых соединены соответственно с выходами первого и второго канальных демодуляторов, а выходы первого и второго накопителей через последовательно соединенные

вычитающий блок и третий формирователь символов соединены с управляющим входом коммутатора, а выход синхроблока соединен с тактовым входом вычитающего блока, отличающееся тем, что, с целью повышения помехоустойчивости, на передающей стороне между выходом источника информации и управляющим входом коммутатора введены последовательно соединенные регистр сдвига, сумматор по модулю два и ключ, к другому входу которого подключен второй выход синхроблока, первый выход которого соединен с тактовым входом регистра сдвига, а на приемной стороне

введены последовательно соединенные первая линия задержки, первый блок выбора минимума, ключ, запоминающий блок и дешифратор, последовательно соединенные вторая линия задержки и второй блок

выбора минимума, а также элемент задержки и блок обнаружения и исправления ошибок, при этом выходы первого и второго канальных демодуляторов соединены соответственно с первым и вторым формирователями символов через соответствующие первую и вторую л 1нии задержки, выходы второго блока выбора минимума соединены с соответствующими входами ключа, выходы первого и второго формирователей символов соединены через коммутатор с первым информационным входом блока обнаружения и исправления ошибок, управляющий вход которого соединен с выходом элемента задержки, сигнальные входы блока обнаружения и исправления ошибок соединены с соответствующими выходами дешифратора, а второй информационный вход блока обнаружения и исправления ошибок соединен с управляющим входом

ключа и выходом третьего формирователя символов, выход формирователя синхроимпульсов соединен с тактовыми входами запоминающего блока, первый и второй линий задержки, первого и второго блоков выбора

минимума, блока обнаружения и исправления ошибок и элемента задержки, к другому входу которого подключен выход синхроблока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретных сообщений | 1988 |

|

SU1573550A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| Многоканальная система связи | 1989 |

|

SU1622949A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2308163C2 |

| Устройство для приема дискретных сообщений | 1988 |

|

SU1559417A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2006 |

|

RU2316905C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396721C1 |

| Устройство для приема сигналов относительной фазовой телеграфии | 1989 |

|

SU1706051A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

Изобретение относится к технике связи и может использоваться для передачи дискретных сообщений в проводных, радио-, радиорелейных и космичэских линиях связи. Цель изобретения - повышение помехоустойчивости связи. Система для передачи и приема дискретных сообщений содержит на передающей стороне источник информации 1, регистр сдвига 2. канальный модулятор 3, передатчик . блок синхронизации 5, генератор 6 последовательности, коммутатор 7, сумматор 8 по модулю два, ключ 9, а на приемной стороне - приемник 10, демодулятор 11, формирователь 12 символов, коммутатор 13, блок обнаружения и исправления ошибок 14, в состав которого входят регистр сдвига 15, сумматор 16 по модулю два и ключ 17, канальный демодулятор 18, первый формирователь 19 символов, первый накопитель 20, вычитающий блок 21, второй формирователь 22 символов, второй накопитель 23, блок синхронизации 24, формирователь 25 синхооимпульсов, первая линия задержки 26. первый блок выбора минимума 27. ключ 28, запоминающий блок 29, дешифратор 30, вторая линия задержки 31, второй блок выбора минимума 32, элемент задержки 33. линия связи 34, 2 ил. ел С

I

а

о т

«г-JULJLJLJ1 JI. Д И II If II П IT Я II .

Гт a| 4 | 5 | 6 I 7 I a | 9 | 10

OtC

12 545670 9 40

о и n n ооii о . п о

1 234 567

- П -flОПИП П - у

ii ii ii n 1

Фиг. 2

П |2|5| T516T

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-01-07—Публикация

1990-01-25—Подача