Изобретение относится к вычислительной технике, а именно к устройствам синхронизации, и может быть использовано в системах синхронизации средств автоматики, вычислительной техники и телевидения.

Известен фазовый синхронизатор, содержащий генератор тактовых импульсов, блок элементов задержки, триггеры, элементы И, элемент ИЛИ, вход запуска, выход синхронизатора [1] который обеспечивает фиксированную величину временного сдвига начала выходной последовательности относительно переднего фронта запускающего импульса. Величина сдвига равна периоду следования выходных импульсов генератора с погрешностью, не превышающей максимальную задержку одного элемента задержки.

Однако данный синхронизатор выдает выходную последовательность тактовых импульсов только в интервале запускающего импульса. Это связано с тем, что вход запуска соединен с входами сброса в "0" триггеров, которые в отсутствие запускающего импульса удерживаются в нулевом состоянии и запрещают прохождение тактовых импульсов на выход синхронизатора. Вследствие этого при периодической подаче запускающего импульса выходная последовательность тактовых импульсов также периодическим прерывается на интервал времени, в течение которого отсутствует запускающий импульс. Кроме того, использование в качестве блока элементов задержки линий задержки или логических элементов снижает точность работы синхронизатора из-за разброса задержек отдельных элементов задержки. При изменении частоты генератора и неизменных параметрах схемы синхронизатора может нарушаться его работа вследствие невыполнения условия: задержка между сигналами с первого и последнего отводов блока элементов задержки должна быть не менее периода следования импульсов генератора.

Цель изобретения обеспечение непрерывности выходной последовательности фазового синхронизатора при периодической подаче запускающего импульса для исключения нарушения работы устройств, подключенных к выходу синхронизатора, а также повышение точности работы.

Для этого в фазовый синхронизатор, содержащий задающий генератор, n триггеров, дополнительно введены n-разрядный двоичный счетчик, двоичный дешифратор с n входами, мультиплексор m _→1, где m=2n, триггер запуска, причем выход задающего генератора соединен с S-входом триггера запуска и входом синхронизации двоичного счетчика, i-й выход которого соединен с i-м входом дешифратора и D-входом i-го триггера, где i=1,2.n, а j-й выход дешифратора соединен с j-м информационным входом мультиплексора (j=1,2.m), выход которого является выходом синхронизатора, i-й адресный вход мультиплексора подключен к прямому выходу i-го триггера, вход запуска синхронизатора подключен к входу синхронизации триггера запуска, D-вход которого соединен с шиной нулевого потенциала синхронизатора, а прямой выход подключен к входам синхронизации триггеров. Введение триггера запуска, вход синхронизации которого является входом запуска синхронизатора, а S-вход соединен с выходом задающего генератора, обеспечивает запуск синхронизатора по фронту запускающего импульса и исключает влияние длительности этого импульса на работу синхронизатора.

Введение двоичного счетчика, дешифратора и мультиплексора позволяет устранить влияние на формирование выходной последовательности параметров блока элементов задержки и необходимость их подбора. Стабильность выходной последовательности определяется параметрами задающего генератора. Кроме того, при изменении частоты задающего генератора в заявляемом изобретении при неизменной схеме устройства работоспособность устройства сохраняется, так как относительный сдвиг выходных последовательностей определяется частотой задающего генератора и разрядностью счетчика.

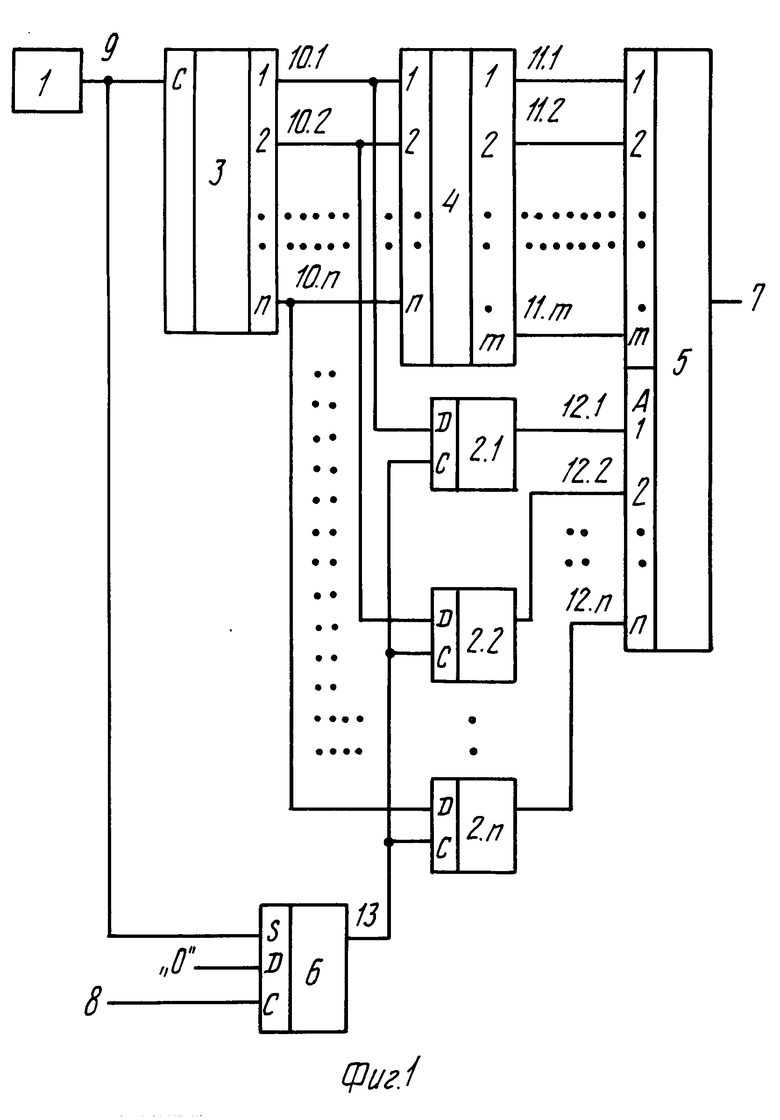

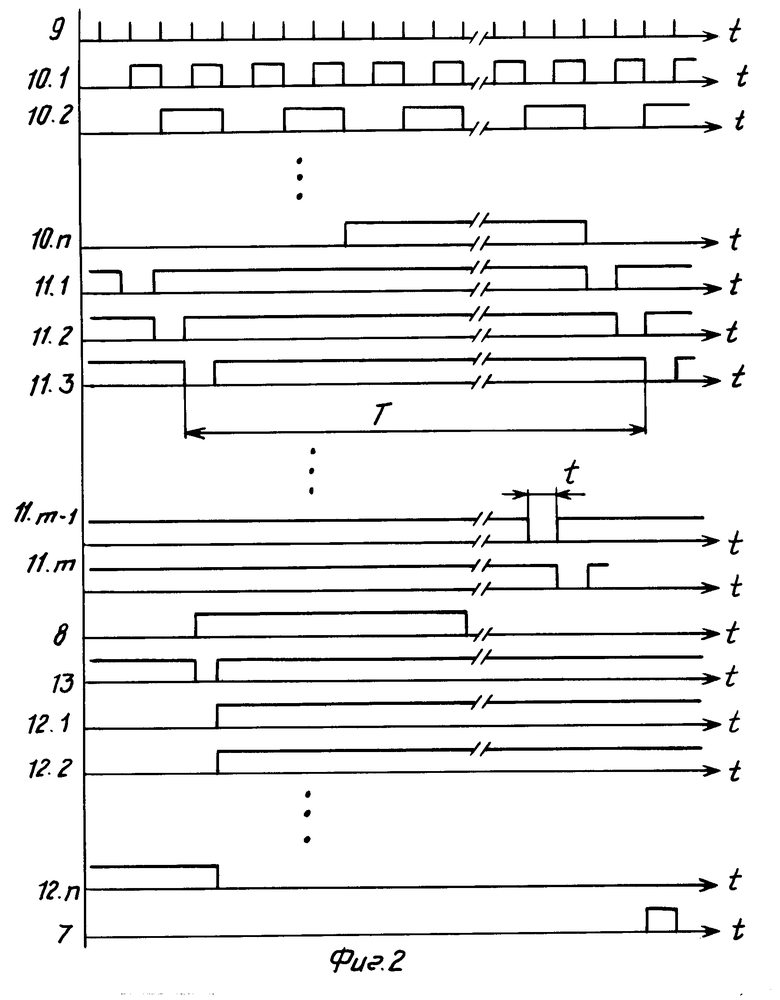

На фиг.1 представлена функциональная схема синхронизатора; на фиг.2 временные диаграммы работы синхронизатора.

Синхронизатор содержит задающий генератор 1, триггеры 2.1-2.n, двоичный счетчик 3, двоичный дешифратор 4, мультиплексор 5, триггер 6 запуска, выход 7 синхронизатора, вход 8 запуска синхронизатора, выходы 9 генератора, 10.1-10. n счетчика, выходы 11.1-11.m дешифратора, адресные входы 12.1-12.n мультиплексора, выход 13 триггера запуска.

Синхронизатор работает следующим образом.

После подачи на синхронизатор напряжения питания триггеры 2.1-2.n устанавливаются в произвольное состояние и на адресные входы 12.1-12.n мультиплексора поступает двоичный код, соответствующий этому состоянию триггеров и выбирающий один из входов мультиплексора 5. Импульсы с выхода 9 генератора 1 поступают на S-вход триггера 6 запуска и устанавливают его в единичное состояние. Счетчик 3 осуществляет циклический счет импульсов генератора 1. При этом двоичный код с выходов 10.1-10.n счетчика 3 преобразуется дешифратором 4 в сдвинутые относительно друг друга последовательности импульсов на его выходах 11.1-11. m. Одна из этих последовательностей выбирается мультиплексором 5 и передается на выход 7 синхронизатора. Импульсы на выходе 7 синхронизатора имеют период следования, равный Твых=Тзг˙2, а длительность равную t=Тзг, где Тзг период следования выходных импульсов генератора 1.

После прихода фронта запускающего импульса на вход 8 запуска синхронизатора триггер 6 запуска устанавливается в нулевое состояние, подготавливая запись информации в триггеры 2.1-2.n. Импульс с выхода 9, следующий первым за фронтом запускающего импульса, возвращает триггер 6 запуска в единичное состояние. При этом в триггеры 2.1-2.n заносится двоичный код с выходов 10.1-10. n счетчика, соответствующий адресу того информационного входа мультиплексора, импульсная последовательность на котором сдвинута относительно фронта запускающего импульса на величину времени Твых с погрешностью, не превышающей Тзг. Для положения фронта запускающего импульса на входе 8, показанного на фиг.2, нулевое состояние триггера 6 запуска устанавливается в интервале импульса на выходе 11.3 дешифратора 4. Двоичный код, соответствующий этому импульсу, заносится с выходов 10.1-10.n в триггеры по заднему фронту импульса на выходе 13 и поступает на адресные входы 12.1-12.n мультиплексора, разрешая прохождение импульсной последовательности с выхода 11.3 на выход 6 синхронизатора.

В качестве задающего генератора 1 импульсов может использоваться генератор с кварцевой стабилизацией частоты, собранный по любой схеме. В качестве триггеров 2.1-2.n и триггера 6 запуска могут использоваться D-триггеры К155ТМ2, К531ТМ, К555ТМ2, К1533ТМ2, двоичного счетчика 3 счетчики К1555ИЕ10, К1555ИЕ18, К1533ИЕ10, К1533ИЕ18, дешифратора 4 К555ИД7, КА1533ИД3, мультиплексора 5 К155КП1, К555КП5, К1533КП7.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1984 |

|

SU1217050A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1987 |

|

RU1612956C |

| Микропроцессор | 1986 |

|

SU1361572A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Устройство для измерения расстояния между центрами двух изображений точечного объекта | 1990 |

|

SU1788597A1 |

| Устройство для программного управления | 1987 |

|

SU1425607A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ЛИНЕЙНОГО ФОТОПРИЕМНИКА | 1987 |

|

SU1528306A1 |

| Устройство для определения положения проката | 1987 |

|

SU1634987A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Устройство обработки видеосигнала | 1989 |

|

SU1635284A1 |

Сущность изобретения: фазовый синхронизатор содержит задающий генератор, триггеры, двоичный счетчик, двоичный дешифратор, мультиплексор, триггер, вход, вход запуска, выход, выходы дешифратора, адресные входы мультиплексора, выход триггера запуска. 2 ил.

ФАЗОВЫЙ СИНХРОНИЗАТОР, содержащий задающий генератор, n триггеров, дополнительно введен n-разрядный двоичный счетчик, двоичный дешифратор с n входами мультиплексор m _→ 1, где m 2n, триггер запуска, причем выход задающего генератора соединен с S-входом триггера запуска и входом синхронизации двоичного счетчика, i-й выход которого соединен с i-м входом дешифратора и D-входом i-го триггера, где i 1, 2, n, а j-й выход дешифратора соединен с j-м информационным входом мультиплексора (j 1, 2, m), выход которого является выходом синхронизатора, i-й адресный вход мультиплексора соединен с прямым выходом i-го триггера, вход запуска синхронизатора подключен к входу синхронизации триггера запуска, D-вход которого соединен с шиной нулевого потенциала синхронизатора, а прямой выход подключен к входам синхронизации триггеров.

| Фазовый синхронизатор | 1987 |

|

SU1432751A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-09-20—Публикация

1993-06-01—Подача