и шины 1,2,13.1-13m и 14.1-14.k входного сигнала, обнуления, выходные кода грубого и точного отсчетов соответственно. В устройство введены |Шифраторы 10 и 11, представляющие ;собой электрически программируемые

1

Изобретение относится к цифровой измерительной технике и, в частности предназначено для использования в из мерительных оптико-электронных системах .

Цель изобретения - повышение быстродействия измерений путем уменьшения времени, затрачиваемого на получение кода точного отсчета.

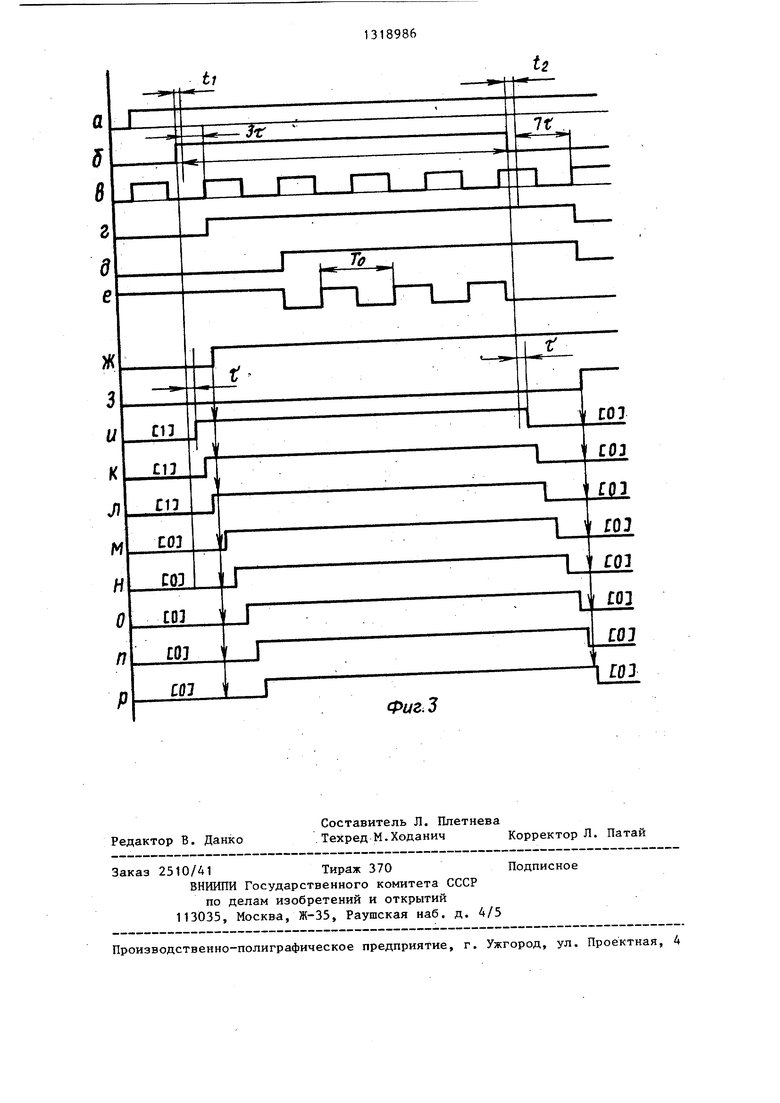

На фиг. 1 приведена структурная схема цифрового измерителя длительности одиночных импульсов; на фиг.2 структурная схема блока синхронизации; на фиг. 3 - временные диаграммы работы измерителя для .

Цифровой измеритель длительности одиночных импульсов содержит шину 1 входного сигнала, шину 2 обнуления, блок 3 синхронизации, генератор 4 счетных импульсов, блок 5 задержки с п-отводами, элемент 2И-ИЖ-НЕ 6, счетчик 7, первый 8 и второй 9 п- разрядные регистры, первый 1Q и второй 11 шифраторы, сумматор 12 выходные шины 13-13.т кода грубого отсчет (старших разрядов двоичного кода результата измерения), выходные шины 14.1-14.k кода точного отсчета (мпад ших разрядов двоичного кода результата измерения).

Блок 3 синхронизации содержит четыре D-триггера 15-18 с синхронными установочными R- и S-входами. Блок 3 синхронизации предназначен для привязки входного сигнала к счетным импульсам, что обеспечивает через элемент 2И-ИЛИ-НЕ 6 управление по счетному входу работой счетчика 7, который в результате этого просчитывает только число целых периодов счетных импульсов, а также для формирования сигналов режима записи в регистры 8

логические матрицы для реализации преобразования количества выходных сигналов высокого уровня с выходов блока 5 задержки в параллельные двоичные коды, и сумматор 12. 2 табл. 3 ил.

и 9 информации с отводов блока 5 задержки.

Причем шина 1 входного сигнала подключена к информационному входу

блока 3 синхронизации и входу блока 5 задержки, выходы Которого соединены с разрядными входами регистров 8 и 9, выходы которых подключены к входам шифраторов 10 и 11 соответственно,

выходы которых соединены с первой и второй группами входов соответственно сумматора 12, разрядные выходы сумм которого с 1-го по k-й являются выходными шинами .14.1-14.k

кода точного отсчета, а выход переноса в (k+1)-й разряд подключен к четвертому входу элемента 2И-ИЛИ- НЕ 6, первый и второй входы которого соединены соответственно с первым и вторым выходами блока 3 синхронизации, а третий вход элемента 2И-ИЛИ-НЕ - к выходу генератора 4, тактирующему входу блока 3 синхронизации и входам выбора режима регистров 8 и 9, входы синхронизации которых подключены соответственно к третьему и четвертому вькодам блока 3 синхронизации, входы установки нуля регистров 8 и 9 - к шине 2 обнуления, входу обнуления счетчика 7 и к входу установки исходного состояния блока 3, выход элемента 2И-ШШ-НЕ 6 - к счетному входу счетчика 7, выходы которого являются выходными шинами 13.1-13.га кода грубого отсчета.

Блок 5 задержки с п-отводами имеет общее время задержки на период следования счетных импульсов Т и время

задержки между отводами на длительность уточняющего дискрета f5 , где п - число отводов и, следовательно, число разрядов регистров 8 и 9.

3 13189864

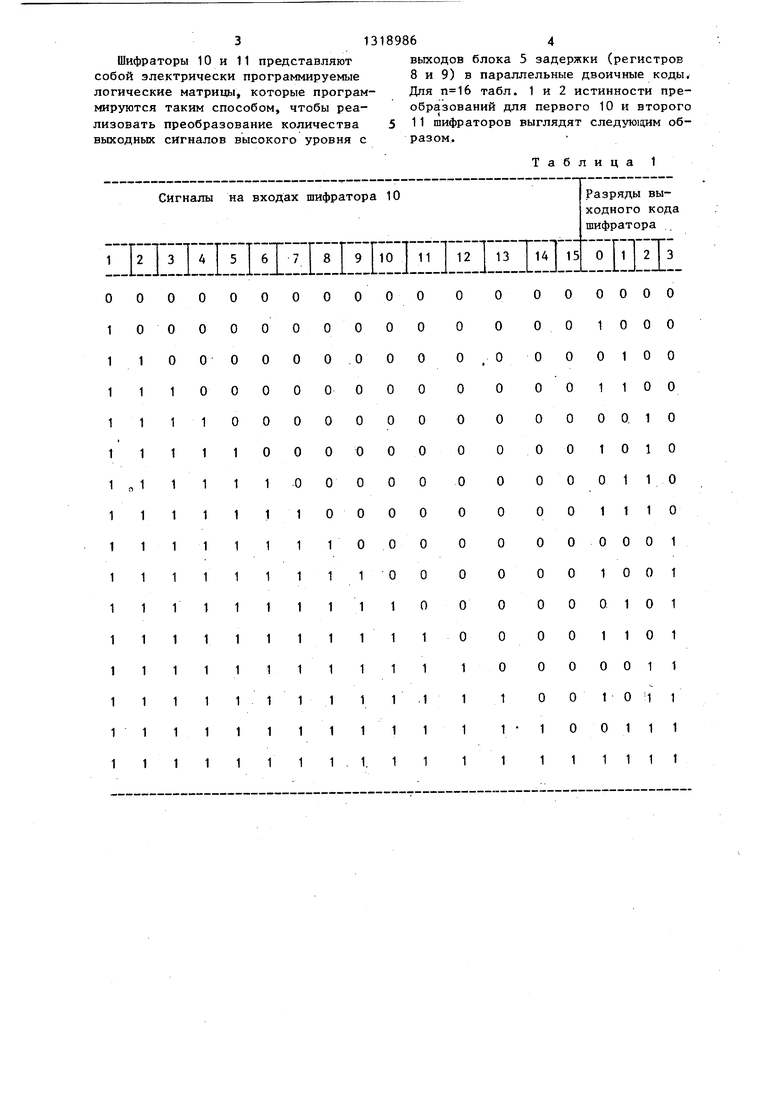

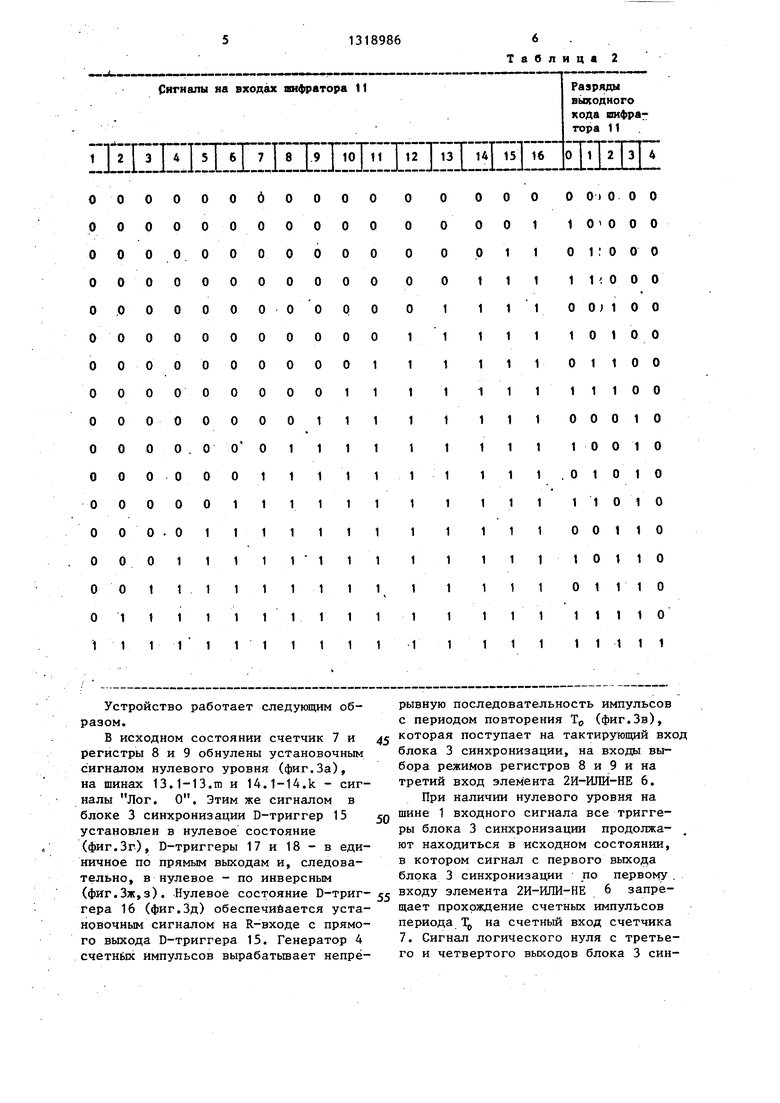

Шифраторы 10 и 11 представляютвыходов блока 5 задержки (регистров собой электрически программируемые8 и 9) в параллельные двоичные коды. логические матрицы, которые програм-Для табл. 1 и 2 истинности премируются таким способом, чтобы pea-образований для первого 10 и второго лизовать преобразование количества5 11 шифраторов выглядят следую1дим об- выходных сигналов высокого уровня сразом.

Таблица 1

Устройство работает следующим образом.

В исходном состоянии счетчик 7 и регистры 8 и 9 обнулены установочным сигналом нулевого уровня (фиг.За), на шинах 13,1-13.m и 14.1-14.k - сигналы Лог. О. Этим же сигналом в блоке 3 синхронизации D-триггер 15 установлен в нулевое состояние (фиг.Зг), D-триггеры 17 и 18 - в единичное по прямым выходам и, следовательно, в нулевое - по инверсным (фиг.3ж,з). Нулевое состояние D-триг- гера 16 (фиг.Зд) обеспечийается установочным сигналом на R-входе с прямого выхода D-триггера 15. Генератор 4 счетньк импульсов вырабатьшает непрёТаблица 2

рывную последовательность импульсов с периодом повторения Т (фиг.Зв),

которая поступает на тактирующий вход блока 3 синхронизации, на входы выбора режимов регистров 8 и 9 и на третий вход элемента 2И-ИЛИ-НЕ 6. При наличии нулевого уровня на шине 1 входного сигнала все триггеры блока 3 синхронизации продолжают находиться в исходном состоянии, в котором сигнал с первого выхода блока 3 синхронизации по первому .

входу элемента 2И-ИЛИ-НЕ 6 запрещает прохождение счетных импульсов периода 1 на счетный вход счетчика 7. Сигнал логического нуля с третьего и четвертого выходов блока 3 син

7 . 1 хронизации обеспечивает нахождение регистров 9 и 10 в состоянии хранени информации нулевого кода, записанного установочным импульсом (запись нового значения кодов не происходит, так как она возможна только по фронт сигнала на синхровходе регистра). Преобразование кода в шифраторах 10 и 11 и сложение в сумматоре 12 не- дают появления на выходе переноса сумматора 12 сигнала логической единицы, следовательно, нет прохождения на счетный вход счетчика 7 импульсов четвертого входа элемента 2И-ИЛИ-НЕ 6

При поступлении на шину 1 входног измеряемого импульса длительностью Т (фиг.36) последний поступает на информационный вход блока 3 синхронизации и на вход блока 5 задержки с п-отводами, где преобразуется в п сигналов (фиг. 3 и-р). Эти сигналы с задержкой Т относительно друг друга поступают с выходов блока 5 задержки с п-отводами на разрядные вхо ды регистров 8 и 9.

В блоке 3 синхронизации по фронту первого счетного импульса после поступления измеряемого сигнала D-триг гер 15 устанавливается в состояние логической единицы (фиг. Зг), снимая установочный сигнал с R-входа D-триг гера 16 и устанавливая D-триггер 18 по инверсному выходу в состояние логической единицы (третий выход блока 3 синхронизации). Сформированный таким образом фронт (фиг.Зж) поступает на синхровход первого регистра 8 и перезаписьшает на его выходы сигналы с отводов блока 5 за- держки. Шифратор 10 обеспечивает преобразование сигналов с отводов блока 5 задержки согласно табл. 1. Поскольку записи двоичного кода в регистр 9 не произошло, в сумматоре 12 происходит сложение числа с выхода шифратора 10 с О. На шинах 14.1-14.k присутствует двоичный код уточнения начала импульса.

Вторым сч етным импульсом в измеряемом интервале D-триггер 16 устанавливается в состояние логической единицы (фиг.Зд) и разрешает поступление счетных импульсов через элемен 2И-ИЛИ-НЕ 6 (фиг.Зе) на счетный вхо счетчика 7, которьй, работая по пере падам 1 - О, просчитьшает число

целых периодов Тд в измеряемом интервале Т,. Это число в двоичном

O

8986

у

30

35

40

45

50

8

коде присутствует на выходе счетчика 7.

После окончания сигнала измеряемой длительности фронтом первого счетного импульса в блоке 3 синхронизации D-триггер 15 устанавливается в нулевое состояние (фиг.2г), сигналом с прямого выхода D-триггера 15 по R-входу в нулевое состояние устанавливается D-триггер 16 (фиг.2д). В результате запрещается прохождение счетных импульсов через третий вход элемента 2И-ИЛИ-НЕ 6 на счетный вход счетчика 7. При установке D-триггера 15 в нулевое состояние с его инверсного выхода на синхровход D-триггера 17 поступает перепад , который формирует на инверсном выходе Dтриггера 17 перепад .Этот сигнал с четвертого выхода блока 3 синхронизации поступает на синхровход регистра 9 и, поскольку он существует в момент действия сигнала разрешения на входе выбора режима регистра 9, на выходы регистра 9 переписывается сигнал с отводов блока 5 задержки с п-отводами. Комбинация сигналов с выхода регистра 9 преобразуется согласно табл. 2 в шифраторе 11 в двоичный код. В сумматоре 12 происходит сложение этого кода с двоичным кодом, присутствующим на первой группе входов сумматора:. Результат сложения снимается с выходов сумматора 12, с разрядных выходов сумм которого (шины 14.1- 14.k) непосредственно снимается код уточнения.

Если при сложении кодов слагаемы : с выходов шифраторов 10 и 11 возникает единица переноса в (k+1)-й разряд, то соответствующий ее появлению перепад на выходе переноса сумматора 12, проходя через четвертый вход элемента 2И-ИЖ-НЕ, вызовет увеличение на единицу в младшем разряде числа на выходе счетчика 7, т.е. увеличение на единицу кода грубого отсчета.

Таким образом, через время Тр с момента среза входного сигнала процесс измере1гая заканчивается. В счетчике 7 записана длительность входного импульса в периодах счетных импульсов TQ, на сумматоре 12 - в уточняющих дискретах г.

При уточнении начала сигнала измеряемой длительности дробная часть

913

t уточняющего дискрета отбрасывается. Вследствие этого в реальной ситуации невозможно наличие сигналов высокого логического уровня на всех п-от- водах блока 5 задержки, и, следовательно, такая входная комбинация не содержится в таблице истинности шифратора 10, и число его выходов определяется из выражения log.n.

При уточнении конца измеряемого интервала дробная часть уточняющего дискрета округляется до целой добавлением tj. Следовательно, входная комбинация из одних логических единиц в таблице шифратора 11 не исключается и число его выходов определяется из выражения 1о§2П+1, т.е. на единицу больше числа выходов шифратора 10. Этот старший разряд соединяется с входом переноса в младший разряд сумматора 12. Общая погрешность измерения несовпадения начала и конца измеряемого интервала равна

d

Поскольку о t ТдИ о ,, то общая погрешность измерения длительности импульса не превышает уточняющего .дискрета Т..

Ф о

рмула изобретения

Цифровой измеритель длительнос ти одиночных импульсов, содержащий генератор счетных импульсов, блок задержки с п-отводами, блок синхронизации, элемент 2И-ИЛИ-НЕ, счетчик, первый и второй п-разрядные регистры, причем выходы .счетчика являются выходными шинами кода грубого отсчета, первый вход элемента 2И-ИЛИ-НЕ соединен с первым выходом блока синхро

610

низации, второй вход элемента 2И-ИЛИ-НЕ - с вторым выходом блока синхронизации, третий вход элемента 2И-ИЛИ-НЕ соединен с входами выбора

режима первого и второго п-разряд- ных регистров, тактирующим входом блока синхронизации и с выходом генератора счетных импульсов, а выход элемента 2И-Ш1И-НЕ подключен к счетному входу счетчика, вход обнуления которого соединен с входами установки нуля п-разрядных регистров, с шиной обнуления и со входом установки исходного состояния блока синхронизации, информационный вход которого подк.точен к шине входного сигнала, а третий и четвертый выходы - к синхровходам первого и второго п- разрядных регистров, соответственно, разрядные входы которых соединены с соответствукщими выходами блока задержки с п-отводами, отличающийся тем, что, с целью повышения быстродействия измерений, в него введены первый и второй шифраторы и сумматор, разрядные выходы которого являются выходными шинами кода точного отсчета, а выход переноса соединен с четвертым входом э.пе- мента 2И-ИЛИ-НЕ, первая и вторая группы входов сумматора подключены к выходам разрядов первого и второго шифраторов соответственно, вход переноса в младший разряд сумматора

соединен с выходом старшего разряда второго шифратора, входы первого и второго шифраторов соединены соответственно с выходами первого и второго п-разрядных регистров, вход блока

задерйски с п-отводами соединен с шиной входного сигнала.

Редактор В. Данко

Составитель Л. Плетнева .Техред М.Ходанич Корректор Л. Патай

Заказ 2510/41

Тираж 370Подписное

ВНИИГГИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ФигЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Цифровой измеритель длительности одиночных импульсов | 1983 |

|

SU1171444A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для обработки и регистрации сигналов | 1987 |

|

SU1458845A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Цифровой фазовращатель | 1986 |

|

SU1372593A1 |

| Генератор псевдослучайной последовательности | 1985 |

|

SU1305837A1 |

Изобретение может быть использовано в измерительных оптико-электронных системах. Цель изобретения - повьппение быстродействия устройства. Цифровой измеритель содержит блок 3 синхронизации, генератор 4 счетных импульсов, блок 5 задержки с п-от- водами, элемент 2И-ИЛИ-НЕ 6, счетчик 7, п-разрядные регистры 8 и 9 О./п с Ш О) /. 00 оо со 00 О)

| Цифровой измеритель длительности одиночных импульсов | 1983 |

|

SU1171444A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-21—Подача