4

00

to

ел

Изобретение относится к вычислительной технике, а именно к устройствам синхронизации, и может быть использовано в системах синхронизаци средств автоматики и вычислительной техники и в телевидении.

Цель изобретения - увеличение точности синхронизации по отношению к переднему фронту запускающего импульса.

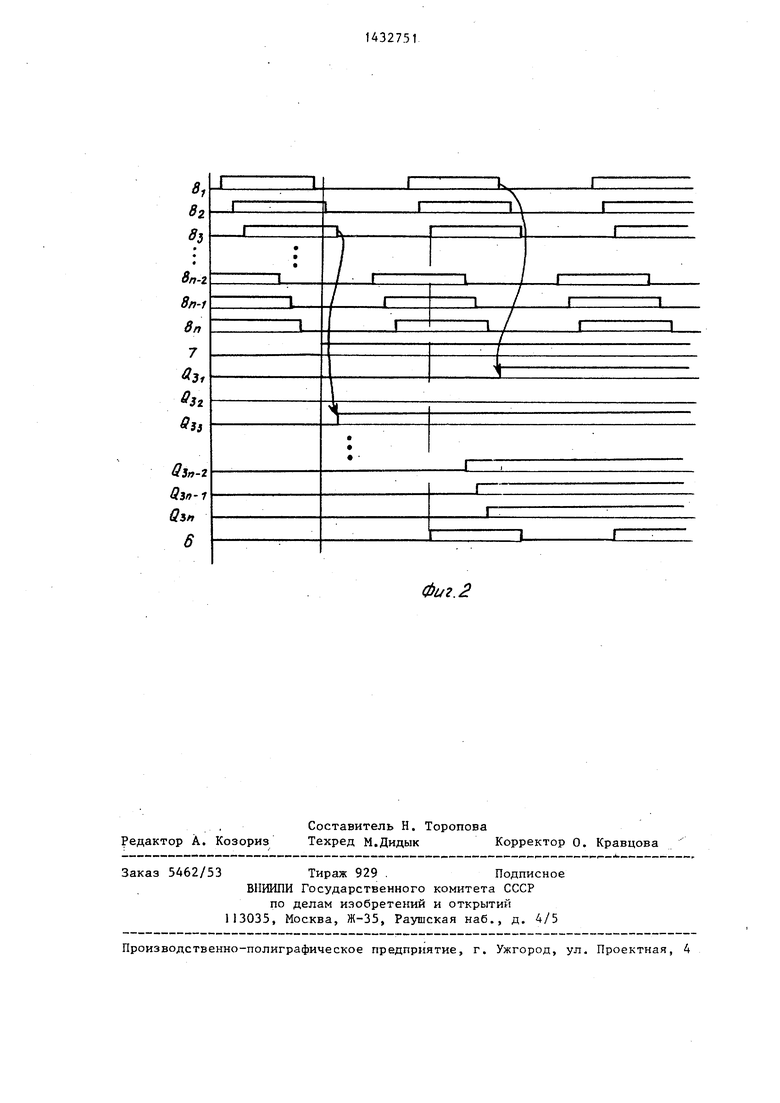

На фиг, 1 представлена функциональная схема синхронизатора; на фиг, 2 - временные диаграммы, поясняющие его работу.

Синхронизатор .содержит запускающий генератор 1, блок 2 элементов задержки, триггеры , элементы И , элемент ИЛИ 5, выход 6 синхронизатора, вход 7 запуска, выходы элементов задержки.

Синхронизатор работает следующим образом.

До прихода запускающего импульса по входу 7 запуска синхронизатора триггеры , установлены в О, и элементы И не пропускают на входы элемента ИЛИ 5 сигналы с выходов блока 2 элементов задержки. После прихода запускающего импульса по входу 7 триггеры 3,.,-3,-, устанавливаются в состояния, определяемые сигналами на входах I и К,.по задним фронтам (фронтам 1/0) выходов , импульсов поступающих на тактовые входы триггеров 3.,-Зп с вькодов бло- ка 2 элемент(Эв задержки. Для положени фронта запускающего импульса по вхо- ду 7 (фиг, 2), триггеры 3,,, 3 j-3 j, устанавливаются в 1 и сохраняют эт состояние на все время действия запускающего импульса по входу 7. Тригер 3 не устанавливается в 1, так как к моменту прихода на его тактовый вход импульсов входах I и К этого триггера присутствует комбинация О, О, в результате чего триггер З сохраняет свое состояние О. Это состояние поддерживается на протяжении действия запускающего импульса по входу 7. Таким образом, элемент И 4j пропускает на вход элемента ИЛИ 5 импульсную последовательность В2, которая через элемент ИЛИ 5 попадает на выход 6 уст- ройстда. Частота выходной последовательности равна частоте генератора 1 импульсов. Начало выходной последовательности импульсов сдвинуто по

0

5

0

5

0

35

40

45

50

5

времени относительно фронта запускающего импульса па величину, равную периоду следования импульсов генератора 1 с погрешностью, не превы- щающей максимальную задержку между сигналами с выходов блока 2 элементов задержки.

В качестве генератора 2 импульсов может быть использован кварцевый генератор импульсов, собранный по любой схеме. Б качестве блока 2 элементов задержки может быть использована любая линия задержки, обеспечивающая необходимую величину задержки между любыми соседними отводами. Например, в качестве отдельного элемента задержки может быть использован элемент И микросхемы 155ЛИ1, элемент ИЛИ микросхемы 155ЛП1 и т.п. Задержка между сигналами с первого и последнего отводов блока 2 должна быть не менее периода следования импульсов генератора 1. Фо. рмула изобретения

фазовый синхронизатор, содержащий задающий генератор, блок из п последовательно соединенных элементов задержки, п элементов И, п триггеров и элемент ИЛИ, причем выход задающего генератора соединен с входом первого элемента задержки, выходы блока элементов задержки с первого по п-й соединены с. первыми входами Соответствующих элементов И, вторые входы которых соединены соответственно с прямыми выходами триггеров, третий вход первого элемента И соединен с инверсным выходом п-го триггера, инверсный выход i-ro триггера, где i 1...(п-1), соединен с третьим входом (i+1)-ro элемента И, выходы элементов И соединены с входами элемента ИЛИ, выход .которого является выходом синхронизатора, отличающийся тем, что, с целью повышения точности синхронизации по отно- щению к переднему фронту запускающего импульса, выходы блока элементов задержки с первого по п-й соединены с синхровходами соответствующих триггеров, инверсный выход первого триггера соединен с 1-входом п-го триггера, инверсный выход j-ro триггера (.,.n) соединен с 1-входом (j-l)-ro триггера, вход запуска синхронизатора соединен с входами сброса в О триггеров, К-входы которых соединены с шиной нулевого потенциала синхронизатора.

Фк2.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации асинхронных сигналов | 1989 |

|

SU1755271A1 |

| ФАЗОВЫЙ СИНХРОНИЗАТОР | 1993 |

|

RU2044403C1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Преобразователь двоичного кода во временной интервал | 1986 |

|

SU1438003A1 |

| Распределитель импульсов | 1985 |

|

SU1298887A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Фазовый синхронизатор | 1990 |

|

SU1739491A1 |

Изобретение относится к вычислительной технике, а именно к устройствам синхронизации, и может быть использовано в системах синхронизации средств автоматики и вычислительной техники и в телевидении. Отличительной особенностью устройства является то, что оно обеспечивает строго фиксированную величину временного сдвига переднего фронта первого импульса вьфабатываемой на выходе последовательности относительно переднего фронта запускающего импульса. Целью изобретения является увеличение точности синхронизации по отношению к переднему фронту запускающего им- .пульса. У9тройство содержит задающий генератор 1, блок 2 элементов задержки, триггер 3, элементы И 4, элемент ИЛИ 5. Поставленная цель достигается за счет использования 1-К-триггеров, связи входа запуска с входами сброса в нуль триггеров и синхронизации триггеров сигналами с выхода элементов 2 задержки. 2 ил. с S ел

Авторы

Даты

1988-10-23—Публикация

1987-01-04—Подача