11

Изобретение относится к вычислительной технике и может быть использовано при построении микропроцессоров с микропрограммным управлением.

Целью изобретения является увеличение быстродействия.

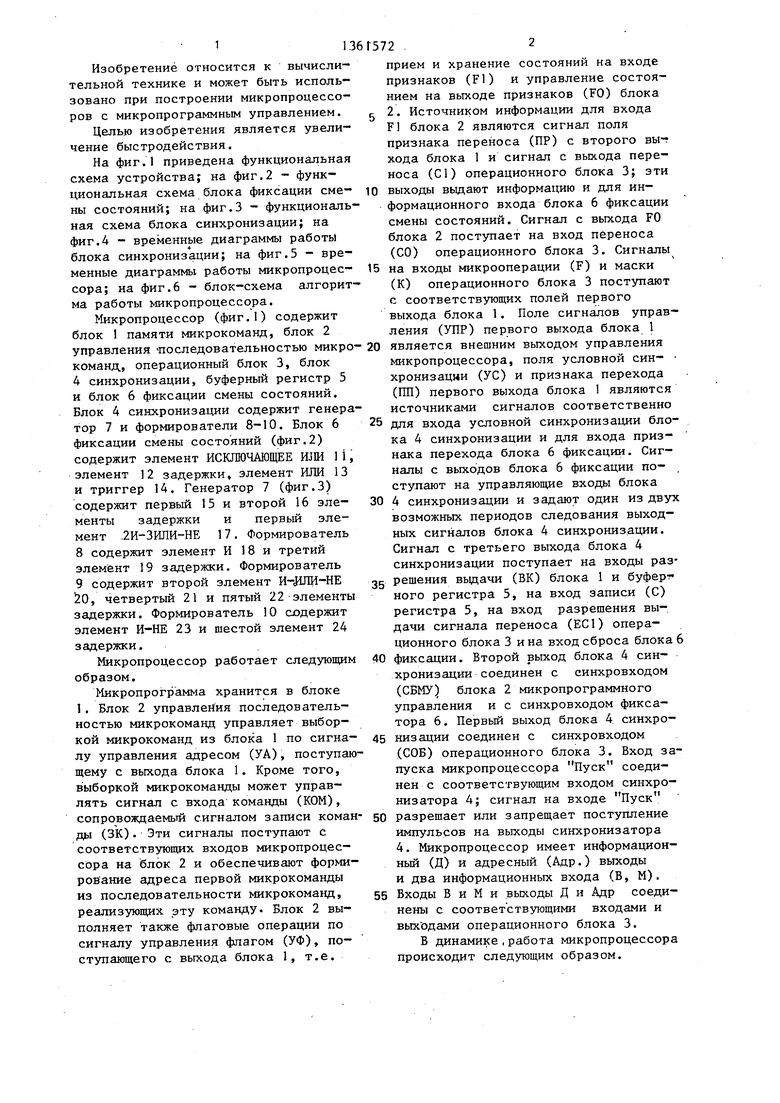

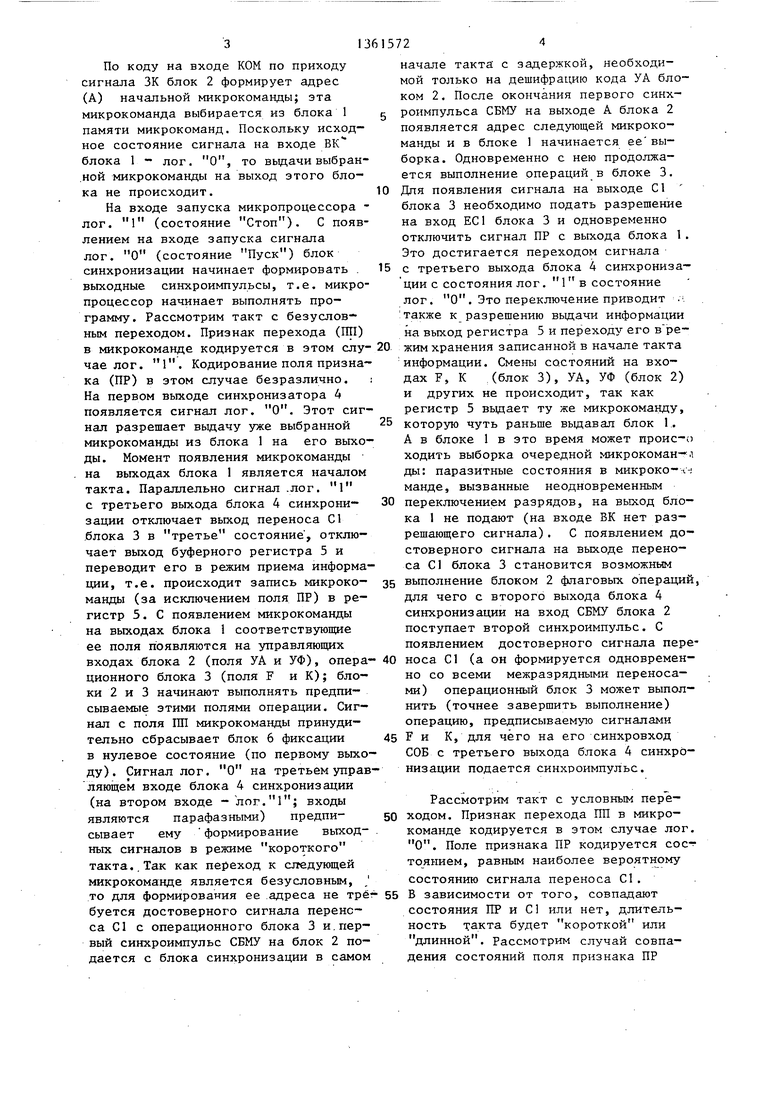

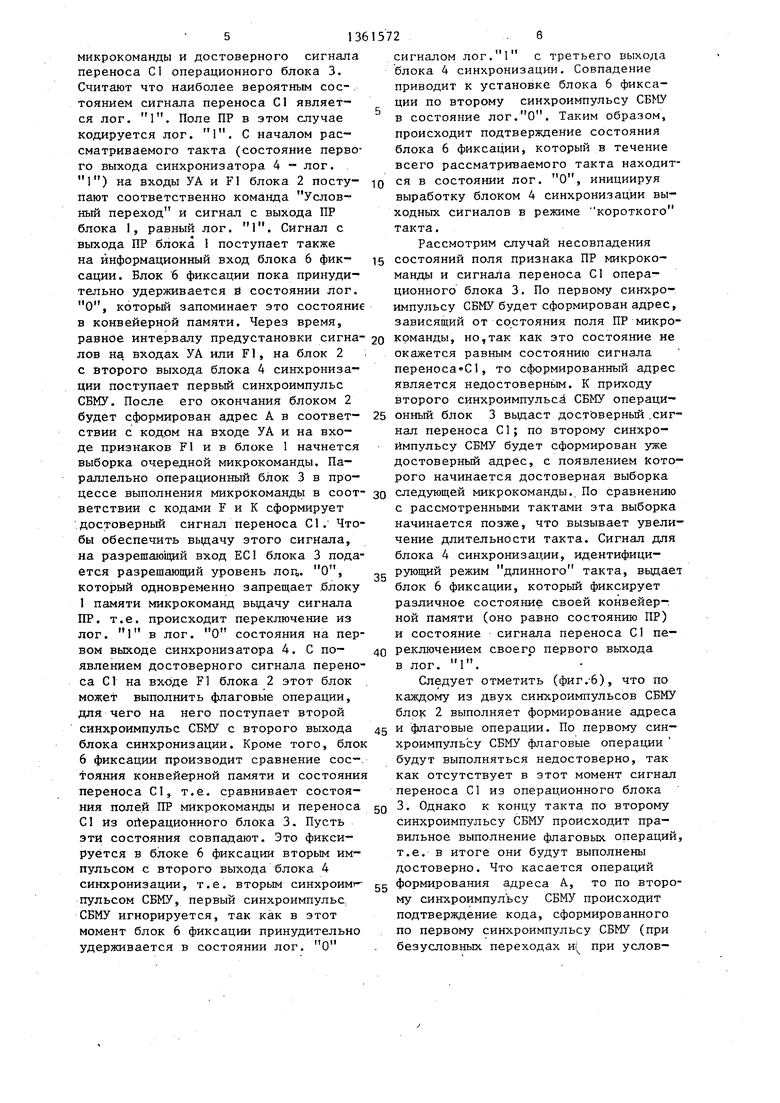

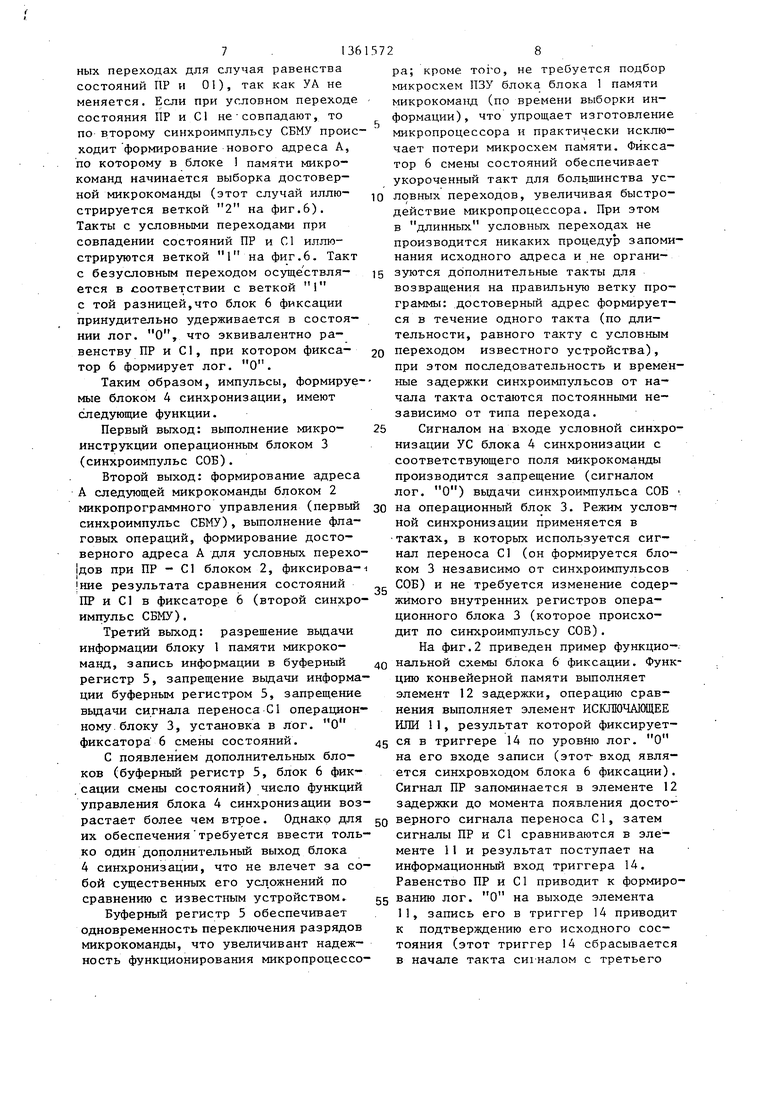

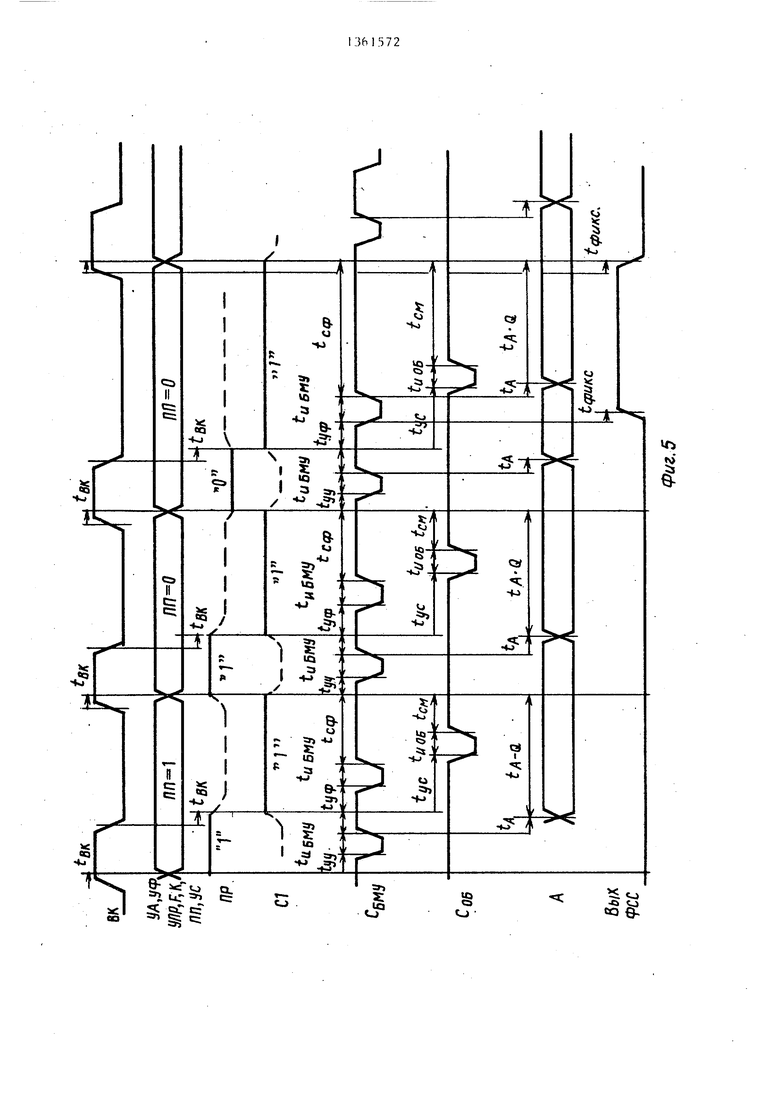

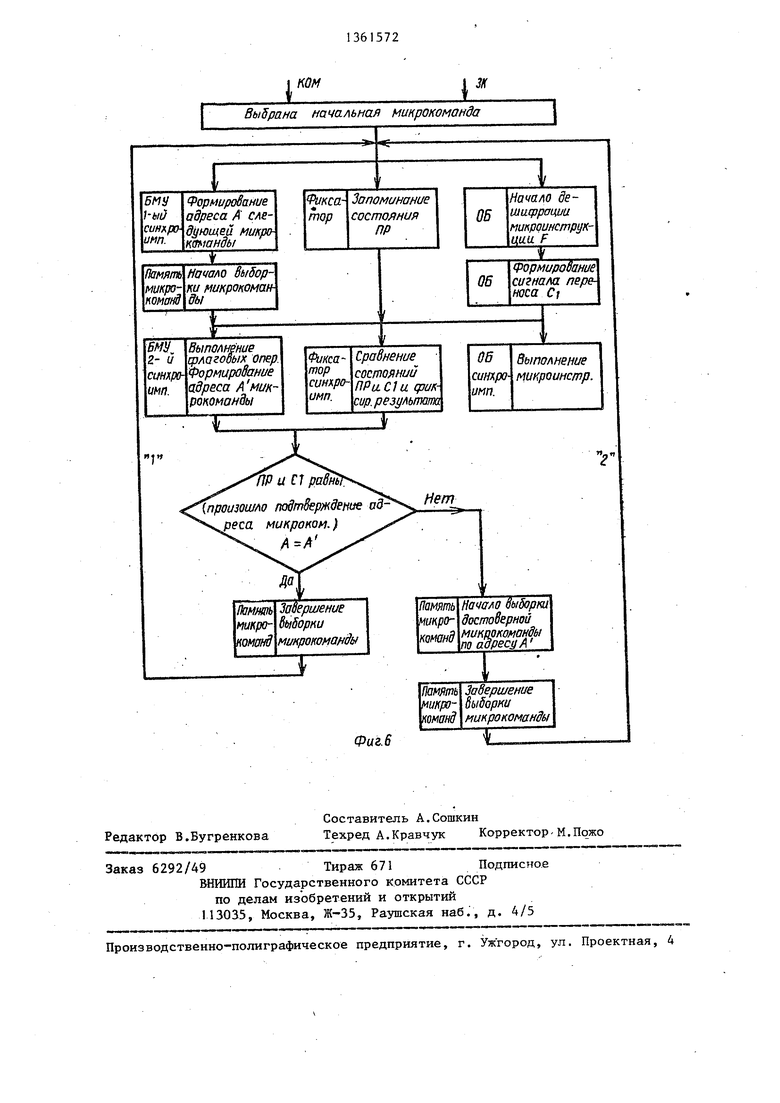

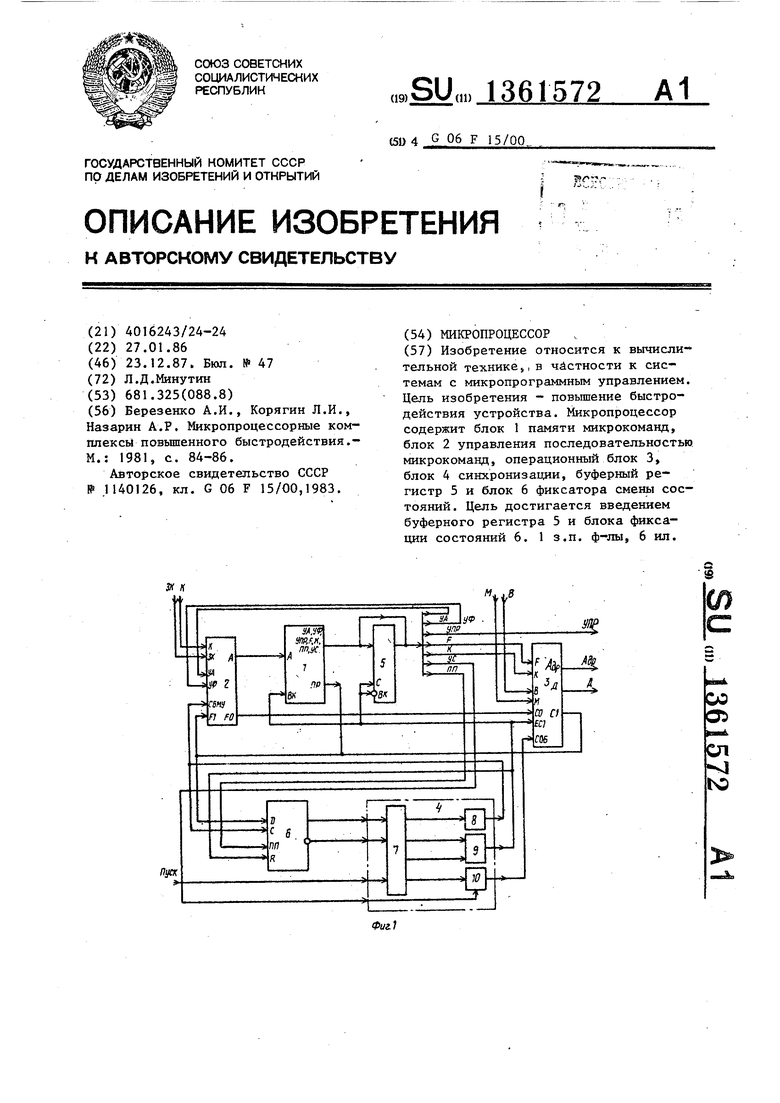

На фиг.1 приведена функциональная схема устройства на фиг.2 - функциональная схема блока фиксации сме- ны состояний; на фиг.З - функциональная схема блока синхронизации; на фиг.4 - временные диаграммы работь) блока синхронизации; на фиг.З - временные диаграммы работы микропроцес-

сора; на фиг.6 - блок-схема алгоритма работы микропроцессора.

Микропроцессор (фиг.1) содержит блок 1 памяти микрокоманд, блок 2

управления -последовательностью микро- 20 является внешним выходом управления

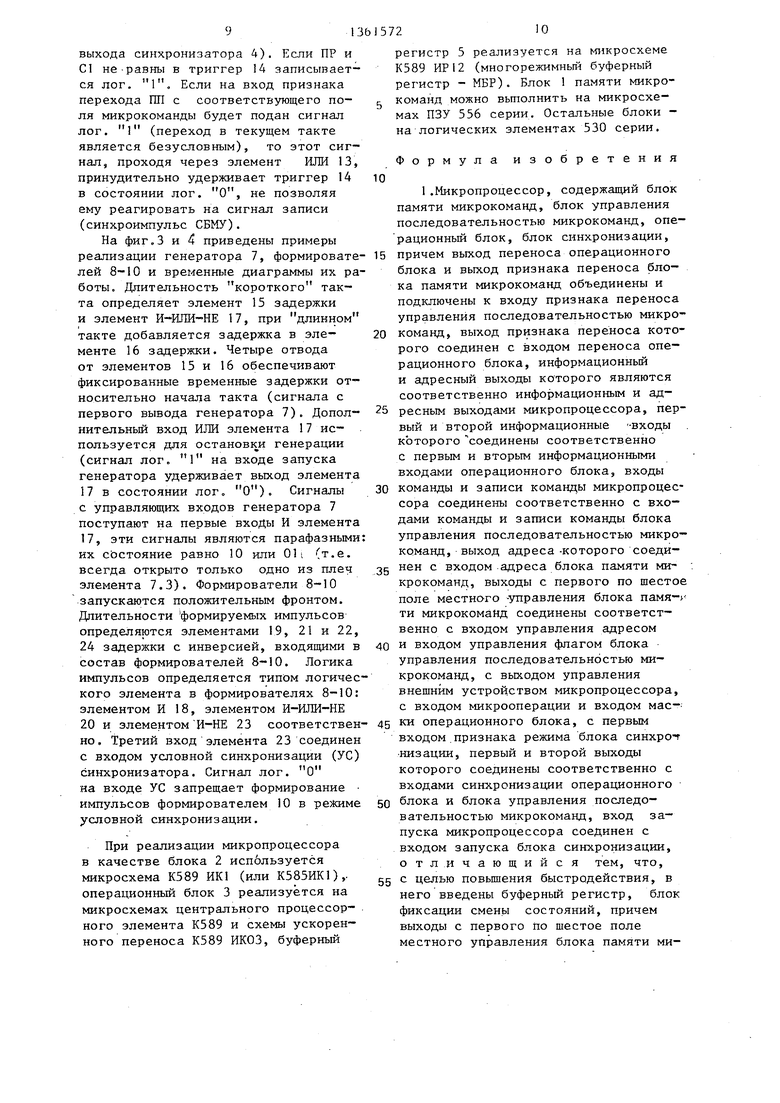

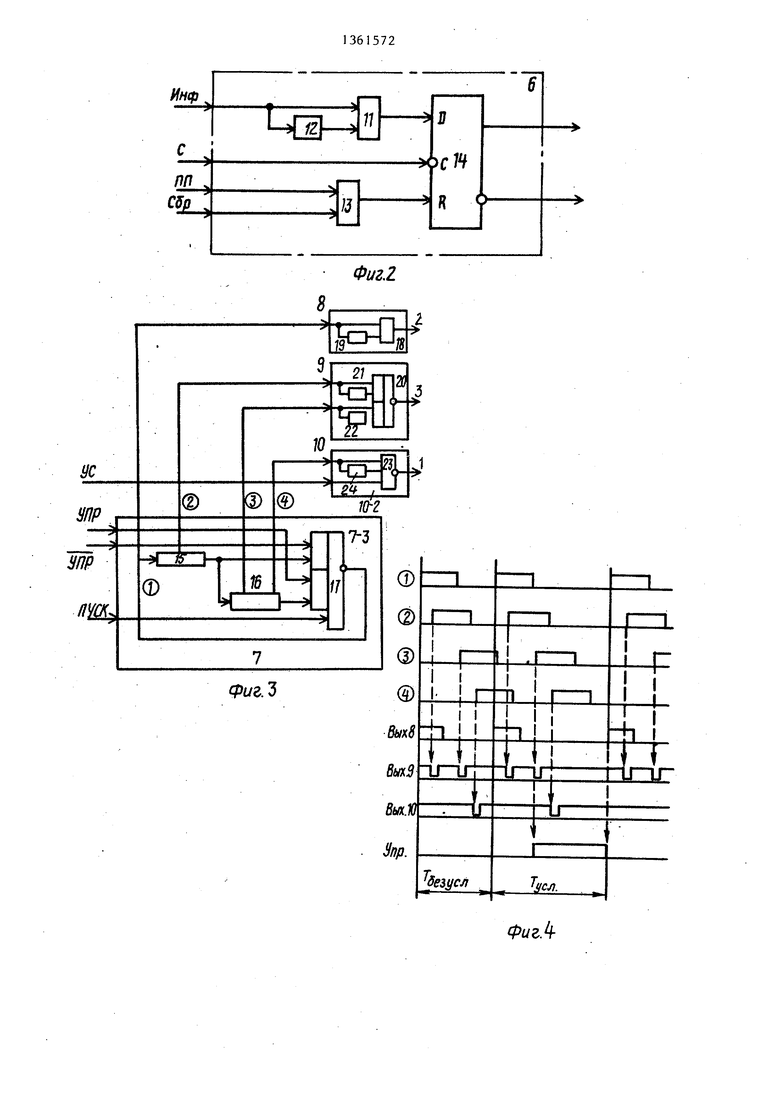

команд, операционный блок 3, блок 4 синхронизации, буферный регистр 5 и блок 6 фиксации смены состояний. Блок 4 синхронизации содержит генератор 7 и формирователи 8-10. Блок 6 фиксации смены состояний (фиг.2) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, элемент 12 задержки, элемент ИЛИ 13 и триггер 14. Генератор 7 (фиг.З) содержит первый 15 и второй 16 элементы задержки и первый элемент -2И-ЗШ1И-НЕ 17 . Формирователь

8содержит элемент И 18 и третий элемент 19 задержки. Формирователь

9содержит второй элемент И-ЛТЩ-НЕ 0, четвертый 21 и пятый 22 элементы задержки. Формирователь 10 содержит элемент И-НЕ 23 и шестой элемент 24 задержки.

Микропроцессор работает следующим образом.

Микропрограмма хранится в блоке . Блок 2 управления последовательностью микрокоманд управляет выборкой микрокоманд из блока 1 по сигналу управления адресом (УА), поступающему с выхода блока 1. Кроме того, выборкой микрокоманды может управлять сигнал с входа команды (КОМ), сопровождаемьтй сигналом записи команды (ЗК). Эти сигналы поступают с соответствующих входов микропроцессора на блок 2 и обеспечивают форми- ров ание адреса первой микрокоманды из последовательности микрокоманд, реализующих эту команду. Блок 2 выполняет также флаговые операции по сигналу управления флагом (УФ), поступающего с выхода блока 1, т.е.

прием и хранение состоянии на входе признаков (F1) и управление состоянием на выходе признаков (FO) блока 2. Источником информации для входа F1 блока 2 являются сигнал поля признака переноса (ПР) с второго выхода блока 1 и сигнал с выхода переноса (С1) операционного блока 3; эти выходы вьщают информацию и для информационного входа блока 6 фиксации смены состояний. Сигнал с выхода FO блока 2 поступает на вход переноса (СО) операционного блока 3. Сигналы на входы микрооперации (F) и маски (К) операционного блока 3 поступают с соответствующих полей первого выхода блока 1. Поле сигналов управления (УПР) первого выхода блока 1

микропроцессора, поля условной син- хронизации (УС) и признака перехода (ГШ) первого выхода блока 1 являются источниками сигналов соответственно

для входа условной синхронизации блока 4 синхронизации и для входа признака перехода блока 6 фиксации. Сигналы с выходов блока 6 фиксации поступают на управляющие входы блока

4 синхронизации и задают один из двух возможных периодов следования выходных сигналов блока 4 синхронизации. Сигнал с третьего выхода блока 4 синхронизации поступает на входы разрешения выдачи (ВК) блока 1 и буферт ного регистра 5, на вход записи (С) регистра 5, на вход разрешения выдачи сигнала переноса (ЕС1) операционного блока 3 и на вход сброса блока 6

фиксации. Второй выход блока 4 синхронизации соединен с синхровходом (СЕМУ) блока 2 микропрограммного управления и с синхровходом фиксатора 6. Первый выход блока 4 синхронизации соединен с синхровходом

(СОБ) операционного блока 3. Вход запуска микропроцессора Пуск соединен с соответствующим входом синхронизатора 4j сигнал на входе Пуск

разрещает или запрещает поступление импульсов на выходы синхронизатора 4. Микропроцессор имеет информационный (Д) и адресный (Адр.) выходы и два информационных входа (В, М).

Входы В и М и выходы Д и Адр соединены с соответствующими входами и вых одами операционного блока 3.

В динамике.работа микропроцессора происходит следующим образом.

По коду на входе КОМ по приходу сигнала ЗК блок 2 формирует адрес (А) начальной микрокоманды; эта микрокоманда выбирается из блока 1 памяти микрокоманд. Поскольку исход ное состояние сигнала на входе ВК блока 1 - лог. О, то вьщачи выбран- .ной микрокоманды на выход этого блока не происходит.

На входе запуска микропроцессора - лог. 1 (состояние Стоп). С появлением на входе запуска сигнала лог. О (состояние Пуск) блок синхронизации начинает формировать . выходные синхроимпульсы, т.е. микропроцессор начинает выполнять программу. Рассмотрим такт с безусловным переходом. Признак перехода (ПГ1) в микрокоманде кодируется в этом случае лог. 1. Кодирование поля признака (ПР) в этом случае безразлично. На первом выходе синхронизатора 4 появляется сигнал лог. О. Этот сигнал разрешает вьщачу уже выбранной микрокоманды из блока 1 на его выходы. Момент появления микрокоманды на выходах блока 1 является началом такта. Параллельно сигнал .лог. 1 с третьего выхода блока 4 синхрони- зации отключает выход переноса С1 .блока 3 в третье состояние , отключает выход буферного регистра 5 и переводит его в режим приема информации, т.е. происходит запись микроко- манды (за исключением поля ПР) в регистр 5. С появлением микрокоманды на выходах блока 1 соответствующие ее поля появляются на управляющих входах блока 2 (поля УА и УФ), опера- ционного блока 3 (поля F и К); блоки 2 и 3 начинают выполнять предписываемые этими полями операции. Сигнал с поля ПП микрокоманды принудительно сбрасывает блок 6 фиксации в нулевое состояние (по первому выходу). Сигнал лог. О на третьем управ ляющем входе блока 4 синхронизации (на втором входе - лог. входы являются парафазными) предпи- сывает ему формирование выходных сигналов в режиме короткого такта.,Так как переход к следующей микрокоманде является безусловным, , то для формирования ее адреса не трёг буется достоверного сигнала переноса С 1 с операционного блока 3 и,первый синхроимпульс СБМУ на блок 2 подается с блока синхронизации в самом

начале такта с задержкой, необходимой только на дешифрацию кода УА блоком 2. После окончания первого синхроимпульса СБМУ на выходе А блока 2 появляется адрес следующей микрокоманды и в блоке 1 начинается ее выборка. Одновременно с нею продолжается выполнение операций в блоке 3. Для появления сигнала на выходе С1 блока 3 необходимо подать разрешение на вход ЕС1 блока 3 и одновременно отключить сигнал ПР с выхода блока 1. Это достигается переходом сигнала с третьего выхода блока 4 синхронизации с состояния лог. состояние лог. О. Это переключение приводит . также к разрешению вьщачи информации на выход регистра 5 и переходу его в ре- жим хранения записанной в начале такта информации. Смены состояний на входах F, К (блок 3), УА, УФ (блок 2) и других не происходит, так как регистр 5 вьщает ту же микрокоманду, которую чуть раньше вьщавал блок 1. А в блоке 1 в это время может проис-о ходить выборка очередной микрокоманды: паразитные состояния в микpoкo-ч манде, вызванные неодновременным переключением разрядов, на выход блока 1 не подают (на входе ВК нет разрешающего сигнала). С появлением достоверного сигнала на выходе переноса С1 блока 3 становится возможным выполнение блоком 2 флаговых операций для чего с второго выхода блока 4 синхронизации на вход СБМУ блока 2 поступает второй синхроимпульс. С появлением достоверного сигнала переноса С1 (а он формируется одновременно со всеми межразрядными переносами) операционный блок 3 может выполнить (точнее завершить выполнение) операцию, предписываемую сигналами F и К, для чего на его синхровход СОБ с третьего выхода блока 4 синхронизации подается синхроимпульс.

Рассмотрим такт с условным перЪ- ходом. Признак перехода ПП в микрокоманде кодируется в этом случае лог О. Поле признака ПР кодируется состоянием, равным наиболее вероятному

состоянию сигнала переноса С1. Б зависимости от того, совпадают состояния ПР и С1 или нет, длительность такта будет короткой или длинной. Рассмотрим случай совпадения состояний поля признака ПР

513

микрокоманды и достоверного сигнала переноса С1 операционного блока 3. Считают что наиболее вероятным сое-. тоянием сигнала переноса С1 является лог. 1. Поле ПР в этом случае кодируется лог. 1. С началом рассматриваемого такта (состояние первого выхода синхронизатора 4 - лог. 1) на входы УА и F1 блока 2 поступают соответственно команда Услов ный переход и сигнал с выхода ПР блока I, равный лог. 1. Сигнал с выхода ПР блока 1 поступает также на информационный вход блока 6 фиксации. Блок 6 фиксации пока принудительно удерживается и состоянии лог. О, который запоминает это состояние в конвейерной памяти. Через время, равное интервалу предустановки сигналов на входах УА или F1, на блок 2 с второго выхода блока 4 синхронизации поступает первый синхроимпульс СБМУ. После его окончания блоком 2 будет сформирован адрес А в соответствии с кодом на входе УА и на входе признаков F1 и в блоке 1 начнется выборка очередной микрокоманды. Параллельно операционный блок 3 в процессе выполнения микрокоманды в соответствии с кодами F и К сформирует достоверный сигнал переноса С1. Чтобы обеспечить вьщачу этого сигнала, на разрешаю1щий вход ЕС1 блока 3 подается разрешающий уровень лол.. О, который одновременно запрещает блоку 1 памяти микрокоманд выдачу сигнала ПР, т.е. происходит переключение из лог. 1 в лог. О состояния на первом выходе синхронизатора 4. С появлением достоверного сигнала переноса С1 на входе F1 блока 2 этот блок может выполнить флаговые операции, для чего на него поступает второй синхроимпульс СБМУ с второго выхода блока синхронизации. Кроме того, блок 6 фиксации производит сравнение сое-, тояния конвейерной памяти и состояния переноса С1., т.е. сравнивает состояния полей ПР микрокоманды и переноса С1 из ойерационного блока 3. Пусть эти состояния совпадают. Это фиксируется в блоке 6 фиксации вторым импульсом с второго выхода блока 4 синхронизации, т.е. вторым синхроим - пульсом СБМУ, первый синхроимпульс. СБМУ игнорируется, так как в этот момент блок 6 фиксации принудительно удерживается в состоянии лог. О

2. б

сигналом лог. М с третьего выхода блока 4 синхронизации. Совпадение приводит к установке блока 6 фиксации по второму синхроимпульсу СБМУ

в состояние лог.О. Таким образом, происходит подтверждение состояния блока 6 фиксации, который в течение всего рассматриваемого такта находится в состоянии лог. О, инициируя выработку блоком 4 синхронизации выходных сигналов в режиме короткого такта.

Рассмотрим случай несовпадения

состояний поля признака ПР микрокоманды и сигнала переноса С1 операционного блока 3. По первому синхроимпульсу СБМУ будет сформирован адрес, зависящий от состояния поля ПР микрокоманды, но,так как это состояние не окажется равным состоянию сигнала переноса С1, то сформированный адрес является недостоверном. К приходу второго синхроимпульс СБМУ операционный блок 3 вьщаст достЬверный .сигнал переноса С1; по второму синхроимпульсу СБМУ будет сформирован уже достоверный адрес, с появлением Которого начинается достоверная выборка

следующей микрокоманды. По сравнению с рассмотренными тактами эта выборка начинается позже, что вызывает увеличение длительности такта. Сигнал для блока 4 синхронизации, идентифици-

рующий режим длинного такта, вьщает блок 6 фиксации, который фиксирует различное состояние своей конвейер-, ной памяти (оно равно состоянию ПР) и состояние сигнала переноса С1 переключением своего первого выхода в лог. 1.

Следует отметить (фиг.-б), что по каждому из двух синхроимпульсов СБМУ блок 2 выполняет формирование адреса

и флаговые операции. По первому синхроимпульсу СБМУ флаговые операции будут выполняться недостоверно, так как отсутствует в этот момент сигнал переноса С1 из операционного блока

3. Однако к концу такта по второму синхроимпульсу СБМУ происходит правильное выполнение флаговых операций, т.е. в итоге они: будут выполнены достоверно. Что касается операций

формирования адреса А, то по второму синхроимпульсу СБМУ происходит подтверждение кода, сформированного по первому синхроимпульсу СБМУ (при безусловных переходах и( при услов-

ных переходах для случая равенства состояний ПР и 01), так как УА не меняется. Если при условном переходе состояния ПР и С1 несовпадают, то по второму синхроимпульсу СБМУ происходит формирование нового адреса А, по которому в блоке 1 памяти микрокоманд начинается выборка достоверной микрокоманды (этот случай иллюстрируется веткой 2 на фиг.6). Такты с условными переходами при совпадении состояний ПР и С1 иллюстрируются веткой 1 на фиг.6. Такт с безусловным переходом осуще ствля- ется в соответствии с веткой 1 с той разницей,что блок 6 фиксации принудительно удерживается в состоянии лог. О, что эквивалентно равенству ПР и С1, при котором фиксатор 6 формирует лог. О.

Таким образом, импульсы, формируемые блоком 4 синхронизации, имеют следующие функции.

Первый выход: выполнение микроинструкции операционным блоком 3 (синхроимпульс СОБ).

Второй выход: формирование адреса А следующей микрокоманды блоком 2 микропрограммного управления (первый синхроимпульс СБМУ), выполнение флаговых операций, формирование достоверного адреса А для условных перехо 1дов при ПР - С1 блоком 2, фиксирова ние результата сравнения состояний ПР и С1 в фиксаторе 6 (второй синхроимпульс СБМУ).

Третий вьпюд: разрешение выдачи информации блоку 1 памяти микрокоманд, запись информации в буферный регистр 5, запрещение выдачи информации буферным регистром 5, запрещение вьщачи сигнала переноса С1 операционному, блоку 3, установка в лог. О фиксатора 6 смены состояний.

С появлением дополнительных блоков (буферньш регистр 5, блок 6 фик- .сации смены состояний) число функций управления блока 4 синхронизации возрастает более чем втрое. Однако для их обеспечения требуется ввести только один дополнительный выход блока 4 синхронизации, что не влечет за собой существенных его усложнений по сравнению с известным устройством.

Буферный регистр 5 обеспечивает одновременность переключения разрядов микрокоманды, что увеличивант надежность функционирования микропроцессора; кроме того, не требуется подбор микросхем ПЗУ блока блока 1 памяти микрокома1щ (по времени выборки информации), что упрощает изготовление микропроцессора и практически исключает потери микросхем памяти. Фиксатор 6 смены состояний обеспечивает укороченный такт для большинства ус-

0 ловных переходов, увеличивая быстродействие микропроцессора. При этом в длинных условных переходах не производится никаких процедур запоминания исходного адреса и не органи5 зуются дополнительные такты для

возвращения на правильную ветку программы: достоверный адрес формируется в течение одного такта (по длительности, равного такту с условным

0 переходом известного устройства), при этом последовательность и временные задержки синхроимпульсов от начала такта остаются постоянными независимо от типа перехода.

5 Сигналом на входе условной синхронизации УС блока 4 синхронизации с соответствующего поля микрокоманды производится запрещение (сигналом лог. О) вьщачи синхроимпульса СОБ

0 на операционный блок 3. Режим услов-т ной синхронизации применяется в тактах, в которых используется сигнал переноса С1 (он формируется блоком 3 независимо от синхроимпульсов

g СОБ) и не требуется изменение содержимого внутренних регистров операционного блока 3 (которое происходит по синхроимпульсу СОВ).

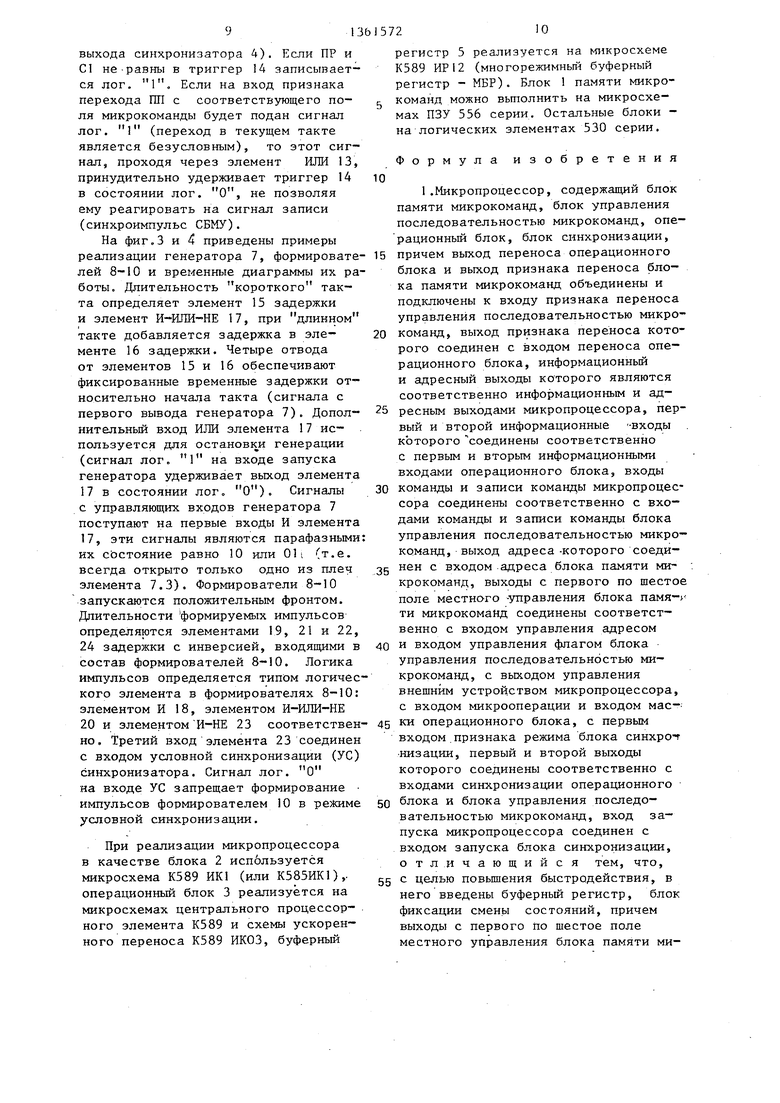

На фиг.2 приведен пример функцио-

0 нальной схемы блока 6 фиксации. Функцию конвейерной памяти выполняет элемент 12 задержки, операцию сравнения выполняет элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, результат которой фиксирует-

5 ся в триггере 14 по уровню лог. О на его входе записи (этот- вход является синхровходом блока 6 фиксации). Сигнал ПР запоминается в элементе 12 задержки до момента появления досто-0 верного сигнала переноса С1, затем сигналы ПР и С1 сравниваются в элементе 11 и результат поступает на информационный вход триггера 14. Равенство ПР и С1 приводит к формиро5 ванию лог. О на выходе элемента 11, запись его в триггер 14 приводит к подтверждению его исходного состояния (этот триггер 14 сбрасывается в начале такта сигналом с третьего

выхода синхронизатора 4). Если ПР и С1 не-равны в триггер 14 записывается лог. 1, Если на вход признака перехода ПП с соответствующего поля микрокоманды будет подан сигнал лог. 1 (переход в текущем такте является безусловным), то этот сигнал, проходя через элемент РШИ 13, принудительно удерживает триггер 14 в состоянии лог. О, не позволяя

1.Микропроцессор, содержащий блок памяти микрокоманд, блок управления последовательностью микрокоманд, операционный блок, блок синхронизации.

ему реагировать на сигнал записи

(синхроимпульс СБМУ).

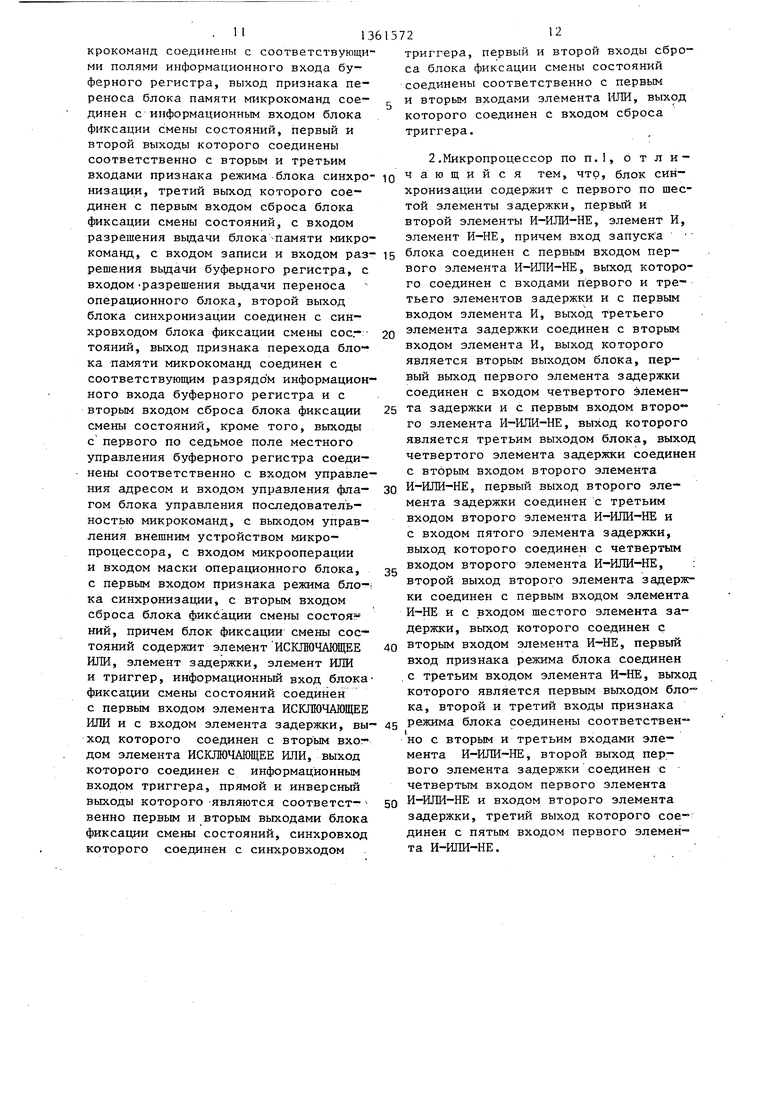

На фиг.З и приведены примеры

реализации генератора 7, формировате- 15 причем выход переноса операционного

лей 8-10 и временные диаграммы их ра- блока и выход признака переноса блока памяти микрокоманд объединены и подключены к входу признака переноса

боты. Длительность короткого

такта определяет элемент 15 задержки

и элемент И-ИЛИ-НЕ 17, при длинном такте добавляется задержка в элементе 16 задержки. Четыре отвода от элементов 15 и 16 обеспечивают фиксированные временные задержки относительно начала такта (сигнала с первого вывода генератора 7). Допол- нительньш вход ИЛИ элемента 17 ис- пользуется для остановки генерации (сигнал лог. 1 на входе запуска генератора удерживает выход элемента 17 в состоянии лог о О). Сигналы с управляющих входов генератора 7 поступают на первые входы И элемента 17, эти сигналы являются парафазными их состояние равно 10 или 01i (т.е. всегда открыто только одно из плеч элемента 7.3), Формирователи 8-10 запускаются положительным фронтом. Длительности формируемых импульсов определяются элементами 19, 21 и 22, 24 задержки с инверсией, входящими в состав формирователей 8-10. Логика импульсов определяется типом логического элемента в формирователях 8-10: элементом И 18, элементом И-ИЛИ-НЕ

20 и элементом И-НЕ 23 соответствен- 45 и операционного блока, с первым

но. Третий вход элемента 23 соединен с входом условной синхронизации (УС) синхронизатора. Сигнал лог. О на входе УС запрещает формирование импульсов формирователем 10 в режиме условной синхронизации.

При реализации микропроцессора в качестве блока 2 используется микросхема К589 ИК1 (или К585ИК1),. операционный блок 3 реализуется на микросхемах центрального процессорного элемента К589 и схемы ускоренного переноса К589 ИКОЗ, буферньш

регистр 5 реализуется на микросхеме К589 ИР 12 (многорежимньй буферный регистр - МБР). Блок 1 памяти микрокоманд можно выполнить на микросхемах ПЗУ 556 серии. Остальные блоки - на логических элементах 530 серии.

Формула изобретения

1.Микропроцессор, содержащий блок памяти микрокоманд, блок управления последовательностью микрокоманд, операционный блок, блок синхронизации.

управления последовательностью микро

команд, выход признака переноса которого соединен с входом переноса операционного блока, информационный и адресный выходы которого являются соответственно информационным и адресным выходами микропроцессора, первый и второй информационные -входы . которого соединены соответственно с первым и вторым информационными входами операционного блока, входы команды и записи команды микропроцессора соединены соответственно с входами команды и записи команды блока управления последовательностью микрокоманд, выход адреса -которого соединен с входом адреса блока памяти ми- ; крокоманд, выходы с первого по щестое поле местного -управления блока памя- ти микрокоманд соединены соответственно с входом управления адресом и входом управления флагом блока управления последовательностью микрокоманд, с выходом управления внешним устройством микропроцессора, с входом микрооперации и входом мае-

входом признака режима блока синхрот низации, первый и второй выходы которого соединены соответственно с входами синхронизации операционного

блока и блока управления последовательностью микрокоманд, вход запуска микропроцессора соединен с входом запуска блока синхронизации, отличающийся тем, что,

с целью повьшения быстродействия, в него введены буферный регистр, блок фиксации смены состояний, причем выходы с первого по шестое поле местного управления блока памяти ми

крокоманд соединены с соответствующими полями информационного входа буферного регистра, выход признака переноса блока памяти микрокоманд сое- динен с информационным входом блока фиксации смены состояний, первый и второй выходы которого соединены соответственно с вторым и третьим входами признака режима блока синхро низации, третий выход которого соединен с первым входом сброса блока фиксации смены состояний, с входом разрешения выдачи блока -памяти микрокоманд, с входом записи и входом разрешения вьщачи буферного регистра, с входом -разрешения выдачи переноса операционного блока, второй выход блока синхронизации соединен с синхро вход ом блока фиксации смены сое.-: тояний, выход признака перехода блока памяти микрокоманд соединен с соответствующим разрядо м информационного входа буферного регистра и с вторым входом сброса блока фиксации смены состояний, кроме того, выходы с первого по седьмое поле местного управления буферного регистра соединены соответственно с входом управления адресом и входом управления флагом блока управления последовательностью микрокоманд, с выходом управления внешним устройством микропроцессора, с входом микрооперации и входом маски операционного блока, с первым входом признака режима блока синхронизации, с вторым входом сброса блока фиксации смены состоя НИИ, причем блок фиксации смены состояний содержит элемент ИСКЛОЧАКШЩЕ ИЛИ, элемент задержки, элемент ИЛИ и триггер, информационный вход блока фиксации смены состояний соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом элемента задержки, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информацйонньм входом триггера, прямой и инверсный выходы которого ЯВЛЯЮТСЯ соответст- венно первым и вторым выходами блока фиксации смены состояний, синхровход которого соединен с синхровходом

триггера, первый и второй входы сброса блока фиксации смены состояний соединены соответственно с первым и вторым входами элемента liTM, выход которого соединен с входом сброса триггера,

2 .Микропроцессор поп.1, отли - чаюш;ийся тем, что, блок синхронизации содержит с первого по шестой элементы задержки, первый и второй элементы И-ИЛИ-НЕ, элемент И, элемент И-НЕ, причем вход запуск а блока соединен с первым входом первого элемента И-ИЛИ-НЕ, выход которого соединен с входами первого и третьего элементов задержки и с первым входом элемента И, выход третьего элемента задержки соединен с вторым входом элемента И, выход которого является вторым выходом блока, первый выход первого элемента задержки соединен с входом четвертого элемента задержки и с первым входом второ го элемента И-ИЛИ-НЕ, выход которого является третьим выходом блока, выход четвертого элемента задержки соединен с вторым входом второго элемента И-ИЛИ-НЕ, первый выход второго элемента задержки соединен с третьим входом второго элемента И-ИЛИ-НЕ и с входом пятого элемента задержки, выход которого соединен с четвертым входом второго элемента И-ИЛИ-НЕ, : второй выход второго элемента задержки соединен с первым входом элемента И-НЕ и с входом шестого элемента задержки, выход которого соединен с вторьм входом элемента И-НЕ, первый вход признака режима блока соединен .с третьим входом элемента И-НЕ, выход которого является первым выходом блока, второй и третий входы признака

режима блока соединены соответственI

но с вторым и третьим входами элемента И-ИЛИ-НЕ, второй выход первого элемента задержки соединен с четвертым входом первого элемента И-ИЛИ-НЕ и входом второго элемента задержки, третий выход которого сое- динен с пятым входом первого элемента И-ШШ-НЕ.

фиг. 5

Фиг2

ВЫХ.ТО Snp.

ФигЛ

ifi

MM

Редактор В.Бугренкова

Составитель А.Сошкин

Техред А.Кравчук Корректор-М.Пожо

Заказ 6292/49Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ЗК

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1983 |

|

SU1140126A1 |

| Микропроцессор | 1985 |

|

SU1336023A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропроцессор | 1985 |

|

SU1273939A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964641A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Система для управления технологическими процессами | 1987 |

|

SU1583920A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

Изобретение относится к вычислительной технике,, в частности к системам с микропрограммным управлением. Цель изобретения - повьшение быстродействия устройства. Микропроцессор содержит блок 1 памяти микрокоманд, блок 2 управления последовательностью микрокоманд, операционный блок 3, блок 4 синхронизации, буферный регистр 5 и блок 6 фиксатора смень состояний. Цель достигается введением буферного регистра 5 и блока фиксации состояний 6. 1 з.п. ф-лы, 6 ил. SK к «it cz

| Березенко А.И., Корягин Л.И., Назарин А.Р | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Микропроцессор | 1983 |

|

SU1140126A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-01-27—Подача