Изобретение относится к области вычислительной техники и предназначено для непрерывного отсчета астрономического времени (функция часов), для фиксации заранее заданного момента времени (функция компаратора), для измерения истекшего времени работы процессора (функция тай- мера процессора) и для формирования продвигающих импульсов с заданной частотой следования, предназначенных для продвижения интервального таймера, и может быть применено в ЭВМ любого класса, например в ЕС ЭВМ, а также в мультипроцессорных системах.

Цель изобретения - повышение полноты контроля устройства.

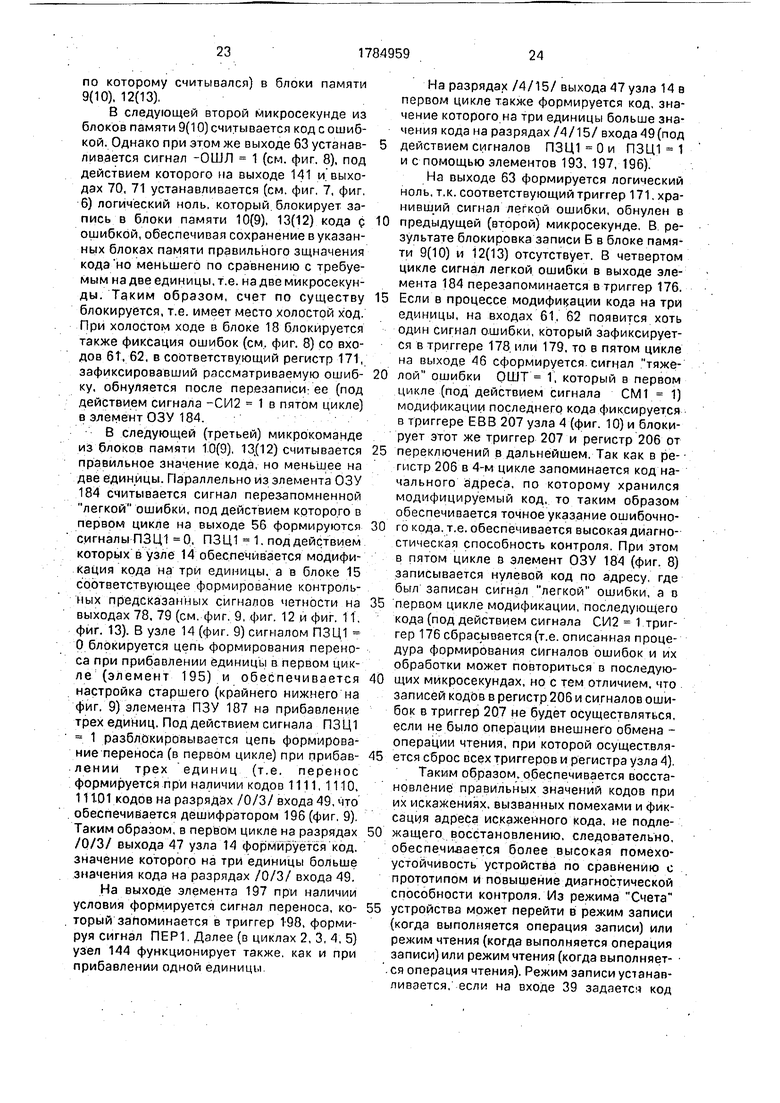

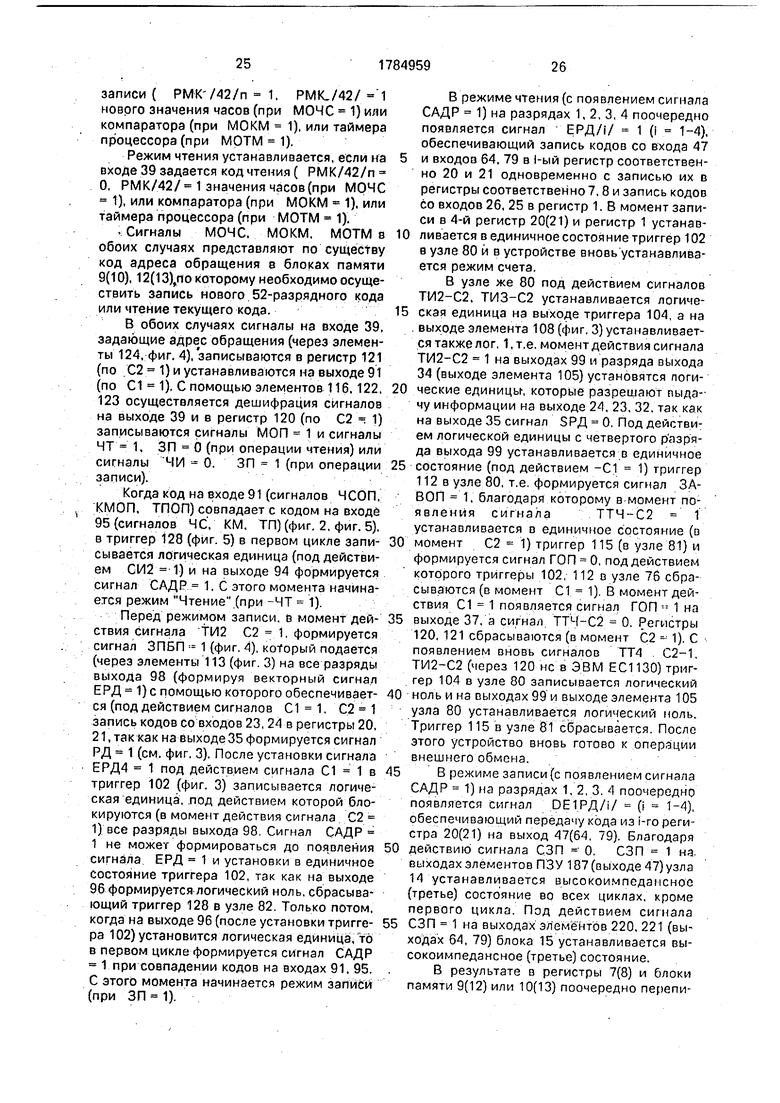

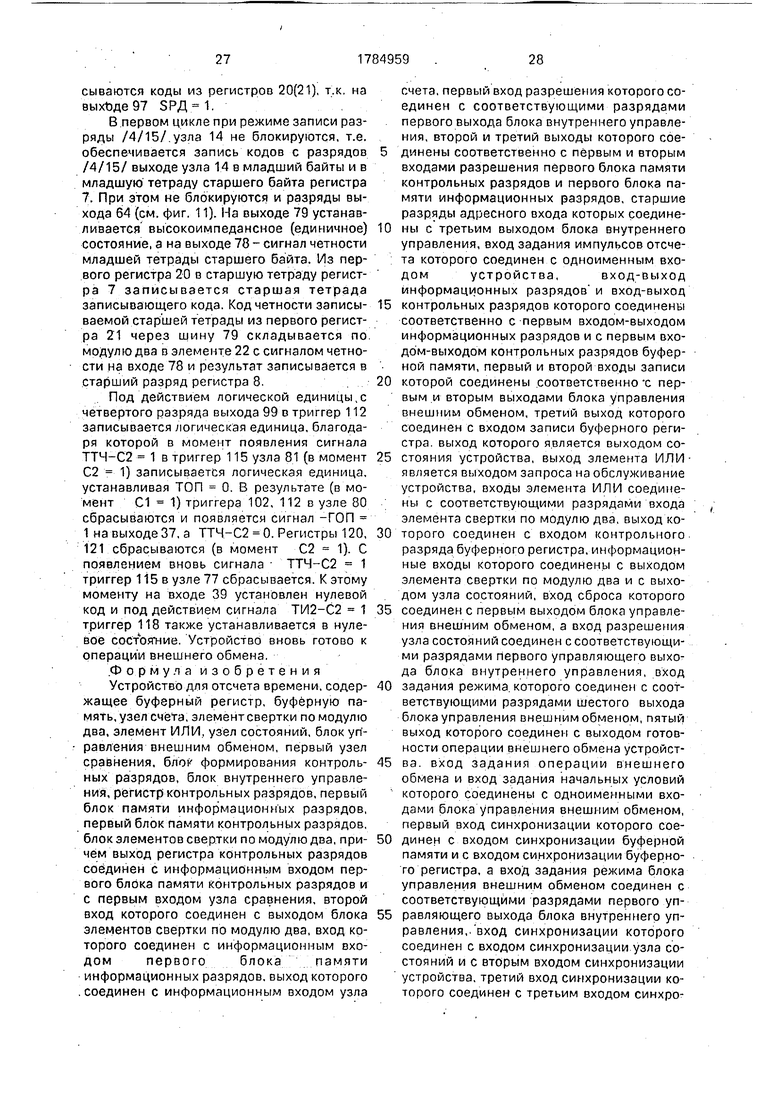

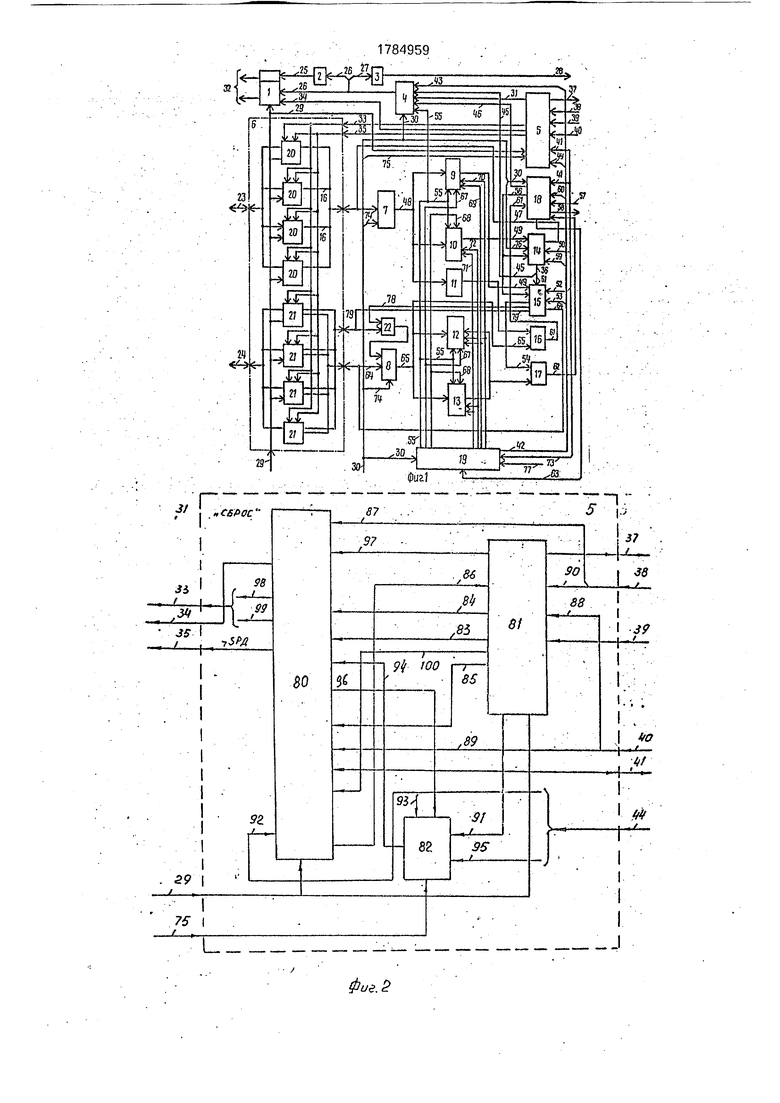

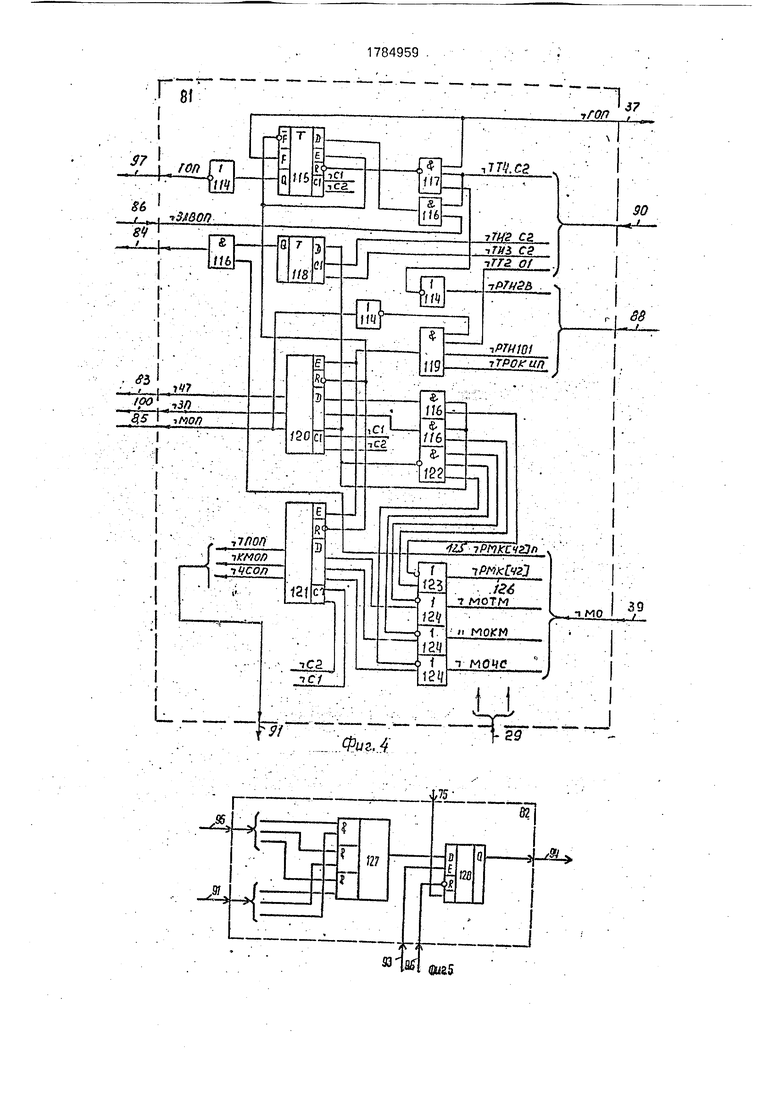

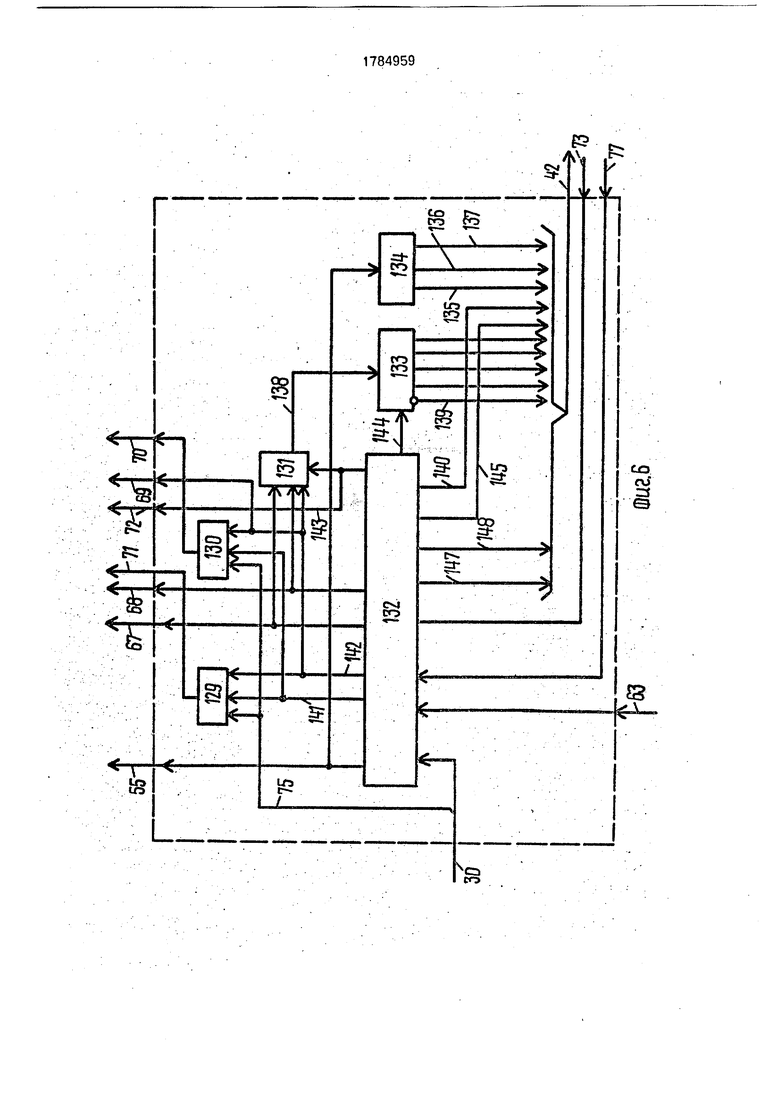

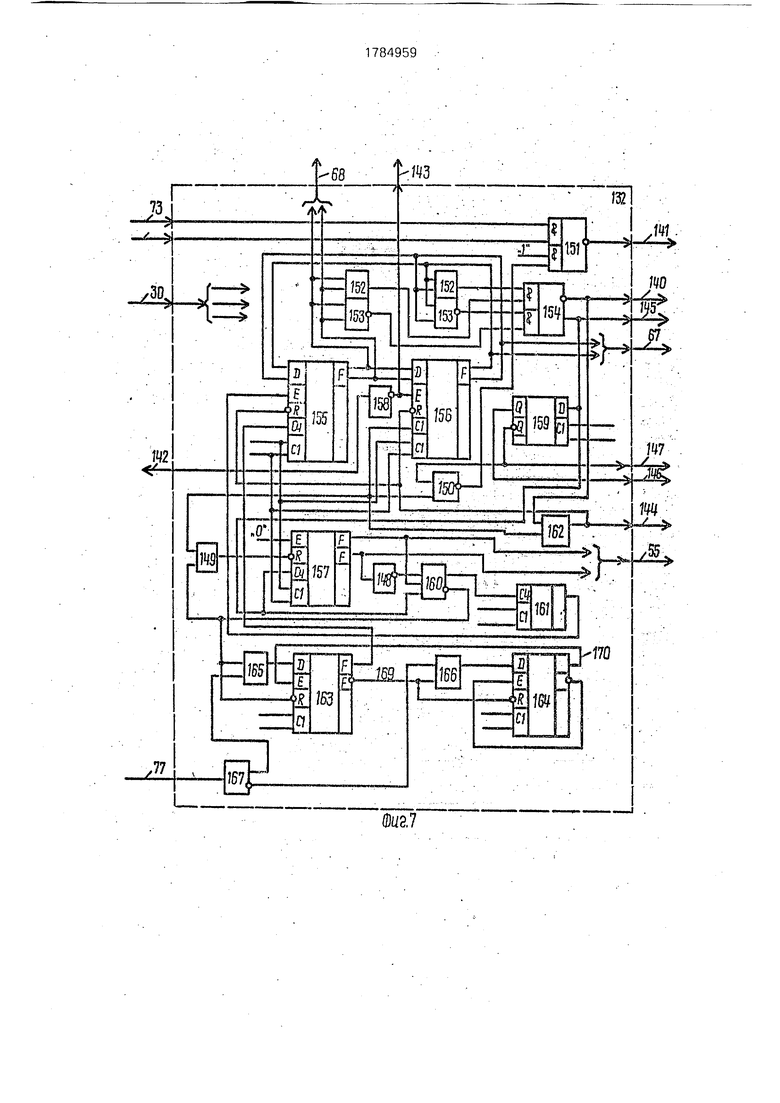

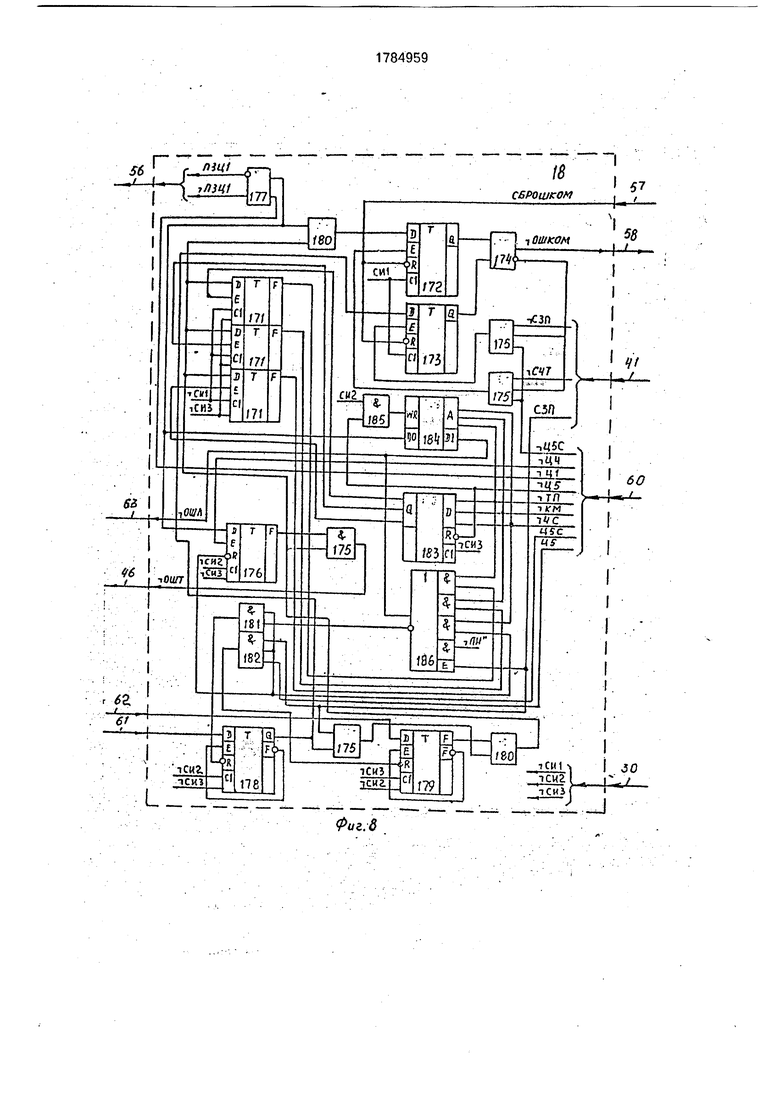

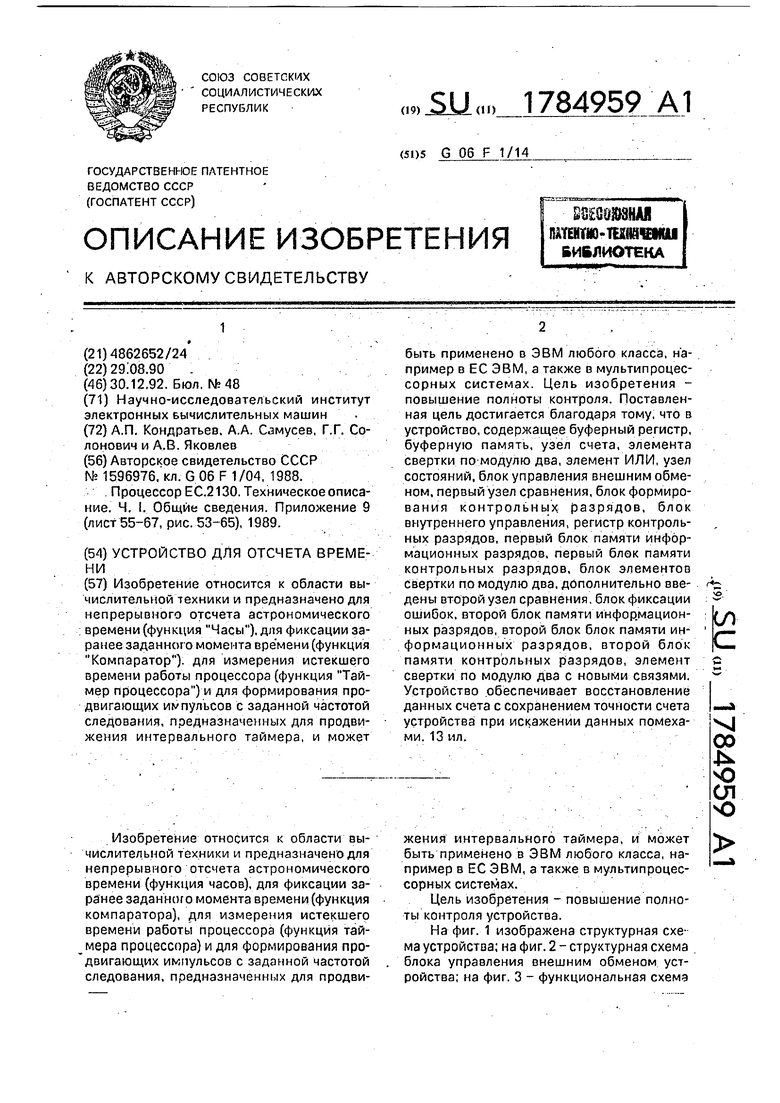

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема блока управления внешним обменом устройства; на фиг. 3 - функциональная схемэ

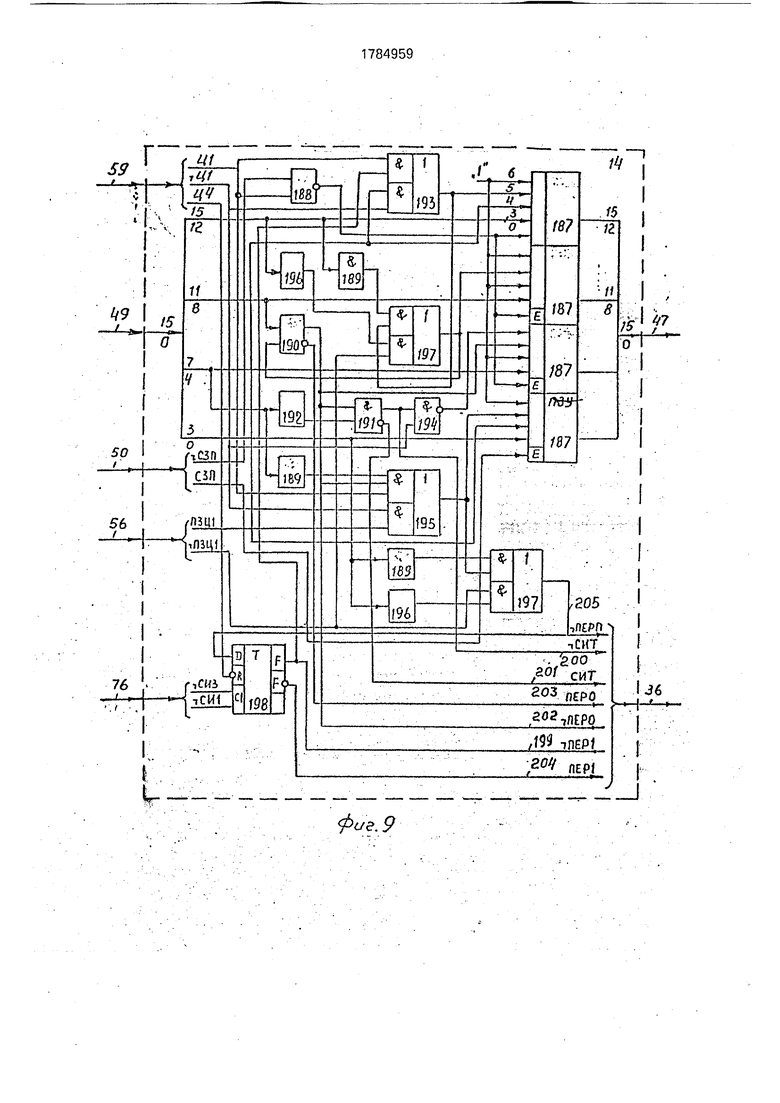

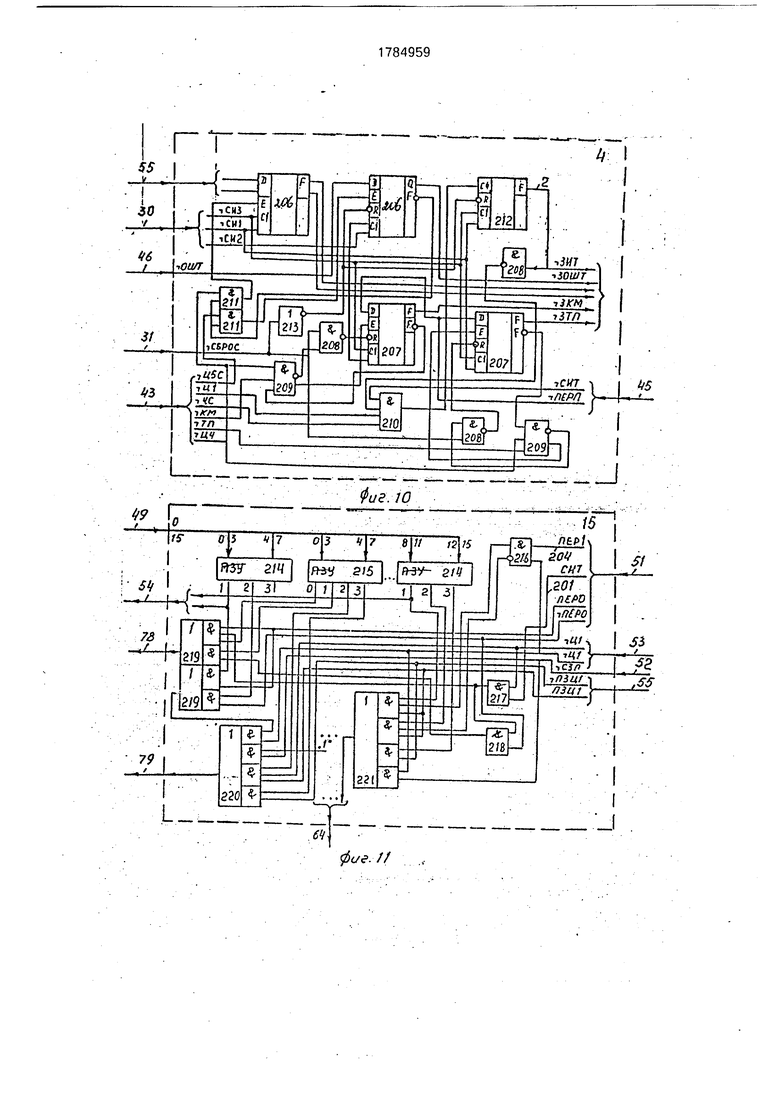

узла формирования управляющих сигналов, используемого в блоке управления внешним обменом; на фиг. 4 - функциональная схема узла фиксация входных и выходных управляющих сигналов, используемого в блоке управления внешним обменом; на фиг. 5 - функциональная схема узла сравнения, используемого в блоке управления внешним обменом; на фиг. 6 - структурная схема блока внутреннего управления уст- ройс тва; на фиг. 7 - функциональная схема узла формирования адресных сигналов, используемого в блоке внутреннего управления; на фиг. 8 - функциональная схема блока фиксации ошибок устройства; на фиг. 9 - функциональная схема узла счета устройства; на фиг. 10 - функциональная схема узла состояний устройства; на фиг, 11 - функциональная схема узла формирования контрольных сигналов; на фиг. 12. 13 - таблицы кодировки элементов 214, 215. ПЗУ. используемых в блоке формирования контрольных разрядов.

Устройство содержит буферный регистр 1, элемент свертки 2 по модулю два, элемент ИЛИ 3, узел 4 состояний устройства, блок 5 управления внешним обменом устройства, буферную память-6, регистр 7 информационных разрядов, регистр 8 контрольных разрядов, первый блок 9 памяти информационных разрядов, второй блок 10 памяти информационных разрядов, блок 11 элементов свертки по модулю два, первый блок 12 памяти контрольных разрядов, второй блок 13 памяти контрольных разрядов, узел 14 счета устройства, блок 15 формирования контрольных разрядов, соответствен- но первый и второй узлы сравнения 16, 17, блок 18 фиксации ошибок устройства, блок 19 внутреннего управления, буферные регистры 20 информационных разрядов и буферные регистры 21 контрольных разрядов в буферной памяти 6, элемент свертки по модулю два 22, первый вход/выход 23 информационных разрядов устройства буферной памяти б, первый вход/выход 24 контрольных разрядов устройства и буферной памяти б, вход 25 контрольного разряда регистра 1, выход элемента 2, вход 26 информационных разрядов регистра 1, выход узла 4, вход элемента 2, разряды 27 формирования запроса на обслуживание выхода 26, вход элемента 3, выход 28 элемента 3, выход запроса на обслуживание устройства, первый вход 29 синхронизации устройства и блока 5, вход синхронизации буферной памяти б. второй вход 30 синхронизации устройства, вход синхронизации блоков и узлов 4. 18, 19, первый выход 31 блока 5, выход 32 состояния устройства вместе с конкретным разрядом, первый управляющий вход 33 буферной памяти 6. управляющий вход 34 буферного регистра 1, четвертый выход 35 блока 5, выход 36 переноса узла 14, выход 37 готовности (завершения) операции внешнего обмена (ГОП) устройства, третий вход 38 синхронизации устройства, вход 39 задания операции внешнего обмена устройства, вход 40 зада0 ния начальных условий устройства, шестой выход 41 блока 5, первый управляющий выход 42 блока 19, управляющий вход 43 узла 4, соответствующие разряды выходы 42, управляющий вход 44 блока 5, вход 45 фикси5 руемых состояний узла 4, вход 46 фиксируемых ошибок узла 4, второй вход/выход 47 информационных разрядов памяти 6, выход 48 регистра 7, выход 49 блоков 9, 10, третий управляющий вход узла

0 14. вход 51 переносов блока 15, первый управляющий вход 52 блока 15, второй управляющий вход 53 блока 15, первый выход°54 контрольных разрядов блока 15, первый адресный выход 55 блока 19, второй выход 56

5 блока 18, вход 57 сброса ошибки команд обмена устройства, выход 58 ошибки команды обмена устройства, первый управляющий вход 59 узла 14, второй управляющий вход 60 блока 18, первый вход 61 фиксации

0 ошибок блока 18, второй вход 62 фиксации ошибок блока 18, четверый выход 63 блока 18, младшие разряды второго входа/выхода 64 контрольных разрядов буферной памяти б, выход 65 регистра 8, выход 66 блоков 12,

5 13, второй адресный выход 67 блока 19, третий адресный выход 68 блока 19, второй управляющий выход 69 блока 19, третий управляющий выход 70 блока 19. четвертый управляющий выход 71 блока 19, пятый уп0 равляющий выход 72 блока 19. управляющий вход 73 блока 19, вход 74 синхронизации регистров 7, 8, второй вход 75 синхронизации блока 5, вход 76 синхрс низации узла 14, вход 77 задающего генера5 тора импульсов отсчета устройства и блока 19 третий выход 78 контрольного разряда узла 15, четвертый выход 79 контрольного разряда 15.

Блок 5 управления внешним обменом

0 (фиг. 2) содержит узел 80 формирования управляющих сигналов, узел 81 фиксации входных и выходных управляющих сигналов, узел 82 сравнения, третий выход 83 узла 81. третий вход узла 80, четвертый вы5 ход 84 узла 81, четвертый вход узла 80, пятый выход 85 узла 81, пятый вход узла 80, первый выход 86 узла 76. вход завершения операции узла 77, (ЗАВОП 1, если операция внешнего обмена завершена), шестой вход 87 узла 80. вход 88 задания начальных уеловий узла 81, седьмой вход 89 узла 80, второй вход 90 синхронизации узла 81, выход 91 адресных сигналов узла 81, восьмой управляющий вход 92 узла ,80, первый управляющий вход 93 узла 82, девятый вход 94 узла 80, второй 95 информационный вход узла 82, второй выход 96 узла 80, первый выход 97 узла 81, первый вход узла 80, группа разрядов 98 выхода 33, группа разрядов 99 выхода 33, второй выход 100 узла 81. второй вход узла 76.

Узел 80 формирования управляющих сигналов (фиг. 3) содержит элемент И 101, триггер 102, элемент И-НЕ 103,триггер 104, элемент И-ИЛИ 105, элемент И-НЕ 106, элемент И-НЕ 107, элемент ЗИ-ИЛИ 108, элемент ИЛИ 109, элемент И в 110, элементы И 111. триггер 112, элементы 2И-ИЛИ 113, элементы НЕ 114.

Узел 81 содержит триггер 115, элементы И 116, элементы И-НЕ 117, триггер 118, элемент И 119, регистры 120, 121. элемент И-НЕ 122. элементы НЕ 123, 124 с парафаз- ными выходами, разряд 125 входа 39, соответствующий сигналу РМК/42/п 1 в тот момент когда на входах 23, 24 (фиг. 1) устанавливается информация для записи в память 6, разряд 126 входа 39, соответствующий сигналу РМК/42 1. в тот момент, когда микропрограмма задана операция внешнего обмена - запись данных через входы 23, 24 в память 6 и далее через регистры 7, 8 в блоки 9, 10, 12, 13.

Узел сравнения 82 содержит элемент ЗИ-ИЛИ 127, триггер 128 Блок внутреннего управления 19 содержит элементы И 129, 130, коммутатор 131, узел 1-32 формирования адресных сигналов, соответственно первый и второй дешифраторы 133, 134, выходы 135, 136, 137 дешифратора 134, на которых формируются сигналы 40 1 (, ) при установке на входе 55 кода, соответствующего адресу хранения значения часов (компаратора, таймера процессора), информационный вход 138 дешифратора 133, на выходах которого формируются сигналы или или при установке соответствующего значения кода на входе 138, инверсный выход 139 дешифратора 133 относительно сигнала Ц1, 140-147 - соответственно первый - восьмой управляющие выходы узла 132.

Узел 132 содержит элемент НЕ 148, элемент И 149. элемент И-НЕ 150, элемент 2И-ИЛИ-НЕ 151, элементы И 152, элементы ИЛИ-НЕ 153, элемент 2И-ИЛИ-НЕ 154, счетчики 155, 156, 157, элемент НЕ 158, триггер 159, элемент И-НЕ 160, счетный триггер 161, элемент И 162 триггеры 163, 164, элементы И 165, 166, элемент НЕ 167 с

парафазными выходами, прямой выход 168 триггера 163, инверсный выход 169 триггера 163, выход 170 триггера 164.

Блок 18 содержит триггеры 171, 172, 5 173, элемент ИЛИ 174, элементы И 175, триггер 176, элемент И-НЕ 177, триггеры 178, 179, элементы ИЛИ 180, элемент И 181, элемент И 182, регистр 183, оперативное запоминающее устройство (ОЗУ) 184, эле0 мент И 185, элемент 4И-ИЛИ 186.

Узел 14 (фиг. 9) содержит постоянные запоминающие устройства (ПЗУ) 187, элемент И-НЕ 188, элементы И 189, элемент V1-HE 190, элемент И-НЕ 191, дешифратор

5 192 кода 1100 на разрядах /8/11/ входа 49, элемент 2И-ИЛИ 193, элементы И-НЕ 194, элемент 2И-ИЛИ 195, дешифраторы 196 кодов 1110, 1101, 1111, элементы 2И-НЕ 197, триггер 198, выход 199триггера 198, один из

0 разрядов выхода 36 (соответствует сигналу ПЕР1 - переносу в 1-й байт узла 14), разряд 200 выхода 36, соответствующий сигналу СИТ( СИТ 1 в первом цикле модификации интервального таймера, если на разрядах

5 /4/7/ входа 49 установлен код 1100 и установилась единица на прямом выходе элемента И 190), разряд 201 вывода 36, соответствующий сигналу СИТ (инверсии сигнала СИТ), разряд 202 выхода 36, соот0 ветствующий сигналу ПЕРО (инверсий сигнала ПЕРО), разряд 204 выхода 36, соответствующий сигналу ПЕР1 (инверсии сигнала - ПЕР1), разряд 205 выхода 36, соответствующий сигналу ПЕРП - переносу

5 из старшего байта узла 14.

Узел 4 (фиг. 10) содержит триггеры 206, 207, элементы И-НЕ 208, элементы И-НЕ 209, элементы И 210, 211, триггер 212, элемент НЕ 213.

0Блок 15 (фиг. 11) содержит элементы

ПЗУ 214, 215, элемент И-НЕ 216. элемент И 217, 218, элементы 2И-ИЛИ 219, элементы 4И-ИЛИ 220, 221.

На фиг. 1 в регистре 1 используется бук5 венное обозначение К, обозначающее контрольный разряд регистра 1.

На фиг. 2, фиг. 3 используются обозначения сигналов СБРОС (на выходе 31 блока 5 узла 80), ЕРД (на выходе 98 узла 80), ЗРД

0 (на выходе 3 блока 5 и узла 80). Знак - означает, что сигнал является активным для элементов ЭСЛ - технологии при его значении, равном логической единице. Использование для реализации конкретного примера

5 устройства элементов ЭСЛ - технологии не является необходимым. Возможно использование любой элементной базы для построения устройства.

Сигнал СБРОС принимает значение СБРОС 1 в момент записи байта состояния

с выхода 26 (фиг. 1) в регистр 1 одновременно с записью последних m биг информации со входа 47 в буферную память б. Состояние СБРОС 1 удерживается в течение действия импульсов синхронизации С2, С1, С2 (С1. С2-С1) на разрядах входа 29. Сигнал ЕРД - векторный (например, 4-х битовый) (см. фиг. 3). Биты сигнала - ЕРД /1/4/ (см. фиг. 3) принимают значение логической единицы на время наименьшее, чем время действия синхроимпульсов С2 - С1 поочередно, начиная с 1-го разряда и кончая 4-м разрядом выхода 98 (см. нумерацию разрядов выхода 98 на фиг, 3). Для конкретного случая, когда разрядность информации, пе- редаваемый через память 6, равна 52 бита, а разрядность входа 47 равна m 16 бит, обеспечивается соответствующая очередность адресации и записи (под действием сигналов ЕРД 1) одной из 4-х пар буфер- ных регистров 20, 21, начинал с крайних правых (верхних на фиг. 1) пар, разрядностью соответственно 4 и 1 и кончая крайними левыми (нижними на фиг. 1) парами в регистре 1 разрядностью соответственно 16, 12 и 7. Описанная очередность записи в регистры 20, 21 может осуществиться как со входов 47, 64, 79. так и со входов 23, 24 (в зависимости от конкретной реализации управления (блока 5)

В заявочных материалах описан частный случай реализации блока 5, при котором на входы 23, 24 подается сразу весь 52-разрядный код с контрольными разрядами группы разрядов, который записывается одновременно во все соответствующие регистры 20, 21 (см. логику узла 80). При этом в регистр 1 осуществляется запись кода со входов 25, 26 и на выходах 32 устанавливается высокоимпедансное (третье) состояние благодаря управлению сигналом ДЕЗРД О (см. фиг. 3), подаваемым через выход 34 вместе с сигналом ЕРД4 (с четвертого разряда выхода 79).

Сигнал ДЕ1РД также является много- разрядным (4 бита). Этот сигнал используется для передачи информации, записанной в буферной памяти 6, на выходы 23, 24 и выходы 47. 64, 79 путем отключения высокоим- педансного (третьего) состояния только одной пары регистров 20, 21 (для передачи информации на выходы 47, 64, 79 поочередно путем установки логической единицы на время действия синхросигнала СИЗ поочередно на разрядах выхода 99 начиная с пер- вого и кончая четвертым (см. нумерацию разрядов выхода 99 на фиг. 3). Для передачи информации из всех регистров 20, 21, а также из регистра 1 на выходы 23, 24, 32 логическая единица формируется сразу на всех

разрядах выхода 99 и на выходе элемента 105 узла 80 (см. логику работы узла 80 на фиг 3).

Направление передачи и записи информации в память 6 задается сигналом 5РД. При 5РД 1 обеспечивается передача в запись информации со входов 23, 24 в буферную память и передачи информации из регистров 20, 21 на выходы 47, 64, 79 При ЗРД 0 обеспечивается передачи и запись информации со входов 47, 64, 79 в соответствующие пары регистров 20, 21.

На фиг. 3-11 используются следующие буквенные обозначения сигналов:

С1, С2 - синхросигналы, периодически и поочередно формируемые на соответствующих разрядах входа 29,

СИ1, СИ2, СИЗ - синхросигналы, периодически и поочередно формируемые на соответствующих разрядах входа 30,

ТТ4-С2, ТИЗ-С2, ТИ2 С2, ТТ2-С1, ТТ5-С1 - синхросигналы центрального процессора (ЦП) электронной вычислительной машины ЕС 1130 (частный случай использования устройства),

РТИ26, РТИ1П1. ТРСК-ЦП, ПРМРД, ИНДРД, БЛК ШД-сигналы состояния ЦП ЭВМ ЕС 1130, которые влияют на функционирование устройства (частный случай использования устройства),

PMK/42/n, РМК/42/, МОТМ, МОКМ, М04С - сигналы, состояния которых определяют операцию внешнего обмена (-МО). При РМК/42/п 1, РМК/42/ 1 и единичном состоянии одного из сигналов М01М, МОКМ, МОЧС осуществляется операция внешнего обмена, в результате которой через буферную память 6 и регистры 7, 8 в блоки памяти 9, 10, 12, 13 по соответствующему адресу записывается новая информация, устанавливаемая на входах 23, 24 (операция записи), При РМК/42/п 0, РМК/42/ 0 единичном состоянии одного из сигналов М01М, МОКМ, МОЧС осуществляется операция внешнего обмена, в результате которой информация считывается из блоков памяти 9, 12 или 10, 13, записывается в буферную память 6 и передается на выходы 23, 24 (операция чтения) При этом информация с выходов 25, 26 записывается в регистр 1 и передается на выходы 32. При отсутствии операций внешнего обмена сигналы МОТМ, МОКМ. МОЧС находятся в нулевом состоянии. Адрес блоков памяти 9, 12 или 10, 13, по которому осуществляется запись новой информации или чтение по соответствующей операции внешнего обмена определяется логической единицей соответствующего сигнала: МОЧС - (часы), МОКМ Т (компаратор), М-ОТМ 1 (таймер процессора).

ГОП - сигнал готовности операции внешнего обмена ( ГОП 1) после завершения операции внешнего обмена и удерживается с момента окончания синхроимпульса ТТ4-С2 до момента окончания следующего синхроимпульса ТТЧ-Ч2),

-ГОП - инверсия сигнала ГОП,

-ЗП - сигнал, задающий (при ) режим записи в узле 80,

-ЧТ - сигнал, задающий (при ЧТ 1) режим чтения в узле 80,

-ЗПБП - сигнал, определяющий (при ЗПБП 1) момент записи новой (внешней) информации в буферную память при операции записи, поступающей по входам/выходам 23 и 24 устройства,

-МОП - сигнал, подтверждающий (при МОП 1), что в устройстве задана операция внешнего обмена,

-ЗАВОП - сигнал, формируемый ( ЗА- ВОП 1) после завершения операции внешнего обмена в устройстве (сигнал ГОП подтверждает не только завершение операции внешнего обмена, но и готовность устройства для новой операции внешнего обмена),

ЧСОП, КМОП, ТПОП - сигналы, соответствующие перед запомненным сигналам соответственно МОЧС, МОКМ, МОТМ,

ЦС, КМ ТП - сигналы дешифрации кода адреса, устанавливаемого на выходе 55, соответствующие адресу соответственно часов, компаратора, таймера процессора (значение сигналов, соответствующее логической единице, появляется периодически каждую микросекунду на время 5 ТЦ, где ТЦ - длительнорть одного рабочего цикла устройства, равная времени действия трех синхросигналов С1, С2, С1 ( С2, С1. С2)на входе 29, или синхросигналов СИ1, СИ2, СИЗ на входе 30,

Ц1, Ц2, ЦЗ. Ц4 сигналы дешифрации кода адреса чтения из блоков памяти 9, 13 или 10, 12, формируемого на выходах дешифратора 133 узла 19 (эти сигналы соответствуют 1-му, 2-му, 3-му и 4-му рабочим циклам устройства и появляются (равны логической единице) периодически три раза в одну микросекунду в момент действия синхросигнала СИ1 с интервалом 5ТЦ, длительностью равной 1-ТЦ,

Ц1, Ц5 - сигналы, представляющие собой инверсию сигналов Ц1, Ц5,

Ц5С, Ц5С - сигналы, соответствующие перезапомненным (смещенным) сигналам соответственно Ц5, Ц5 (т е сигналы лог. 1

и лог. 0), появляются с задержкой, начиная с действия синхросигнала - СИЗ),

СЗП - сигнал (лог 1), определяющий интервал времени, в течение которого осу- ществляется перезапись информации из буферной памяти б в блоки памяти 9 12 или 10, 13,

СЗП - сигнал, представляющий собой инверсию сигнала - СЗП, СЧТ - сигнал (лог. 1), определяющий

интервал времени, в течение которого осуществляется перезапись затребованной информации из блоков памяти 9, 12 или 10, 13 в буферную память 6,

САДР - сигнал сравнения адресов (логическая единица устанавливается в 1-м цикле в момент и на время совпадения адреса, установленного на выходе 55 и заданного на входе 39 и соответственно установленного на выходе 91,

Е1, Е2 -сигналы блокировки элементов памяти (например, ОЗУ типа 500РУ145) блоков памяти 9, 10, 12, 13 (при Е1 О, Е2 О на выходах блоков памяти 9, 10, 12, 13 устанавливается высокоимпедансное (третье) состояние благодаря подключению выходов 69, 72 к Е-входам элементов ОЗУ), Р1, Р2 - сигналы (лог. 1) записи в блоки памяти 9. 10, 12, 13 (выходы 70, 71 подключаются к входам элементов ОЗУ),

ГИ - сигналы генератора импульсов, генерируемые с периодичностью 1 мкс и скважностью, равной 2,

ОШЛ - сигнал легкой ошибки (т.е ошибки, которая будет исправляться),

ОШТ - сигнал (лог. 1) тяжелой ошибки (т.е. ошибки, которая не может быть исправленной),

ОШКОМ - сигнал (лог. 1) о шибки, воз- пикшей при выполнении операции внешнего обмена,

СБРОШКОМ - сигнал (лог, 0) сброса ошибок, возникших при выполнении операций внешнего обмена (формируется цент- ральным процессором),

ПЗЦ1 -сигнал, задающий режим прибавления тройки (вместо единицы) в узле счета 14,

ПЗЦ1 - сигнал, представляющий со- бой инверсию сигнала - ПЗЦ1,

СИТ- сигнал продвижения интервального таймера,

СИТ - сигнал, представляющий инверсию сигнала СИТ,

ПЕРП - сигнал (лог. 1) переполнения,

с помощью которого формируются запросы на обслуживание (прерывание) от компара- тора и таймера процессора,

ПЕРО - сигнал (лог. 1) переноса в нулевой байт(разряды /0/7/)узла 14,

ПЕР1 - сигнал (лог. 1) переноса в первый байт (разряды /8/15/узла 14, формируется в предыдущем цикле и запоминается в триггере 198 узла 14,

ЗОШТ, ЗИТ, ЗКМ, ЗТП-сигналы (лог. 1) запросов на обслуживание (прерывание) центральным процессором соответственно по тяжелой ошибке, от интервального таймера, компаратора, таймера процессора (указанные сигналы объединяются по ИЛИ элементам 3 (фиг. 1), обеспечивая формирование сигнала запроса на обслуживание на выходе 28.

Цифры около перечеркнутых жгутов в памяти 6 на фиг. 1 указывают количество разрядов для конкретного случая реализации устройства. Цифры около жгутов и отдельных выходов элементов и около входов и выходов элементов ПЗУ 187, 214 и элемента 215 указывают номера разрядов жгутов, входов и выходов элементов ПЗУ.

На фиг. 12, 13 представлены таблицы кодировки элементов ПЗУ соответственно 214 и 215, На разрядах /0/13/и /4/7/ адресных входов элементов ПЗУ могут устанавливаться 16 - тиричные коды 0, 1,2,3,4, 5, 6, 7. 8, 9, А, В, С, Д, Е (верхняя горизонтальная строка и крайний левый столбец таблиц на фиг. 12, 13)

В клетке таблиц, соответствующей пересечению строки и столбца таблиц, указывается 16-тиричный код, который формируется на разрядах /1/3/и /0/3/ выходов элементов ПЗУ при установках на разрядах адресных входов комбинации кодов, указанных в верхней и крайней левой частях (клетках) выбранных столбца и строки.

Буквой Е на элементах 2И-ИЛИ 113, ЗИ- ИЛИ 108 на фиг. 3, на элементе 41/1-ИЛИ на фиг. 8 обозначается вход блокировки (при установке логического нуля на этом входе на выходе указанных элементов устанавлива- ; ется логический ноль).

Буквой Е на триггерах в регистрах 102, 112, 115, 120, 121, 128. 163, 164, 171, 172, 173, 176, 178, 179, 206, 207, 212 обозначен вход разрешения (при лог. 1 на входе Е триггерах и регистрах разрешается запись новой информации под действием синхросигнала, подаваемого на синхровход, обозначаемый С1, а при лог. О на входе Е триггера и регистры устанавливаются в режимах хранения ранее записанной информации, если не предусмотрен режим Сброс).

Буквой R на указанных триггерах в регистрах, а также на триггере 198, регистре 183 и счетчиках 155. 156. 157 обозначается вход сброса (при лог. Она входе R указанные

триггеры, счетчики и регистры переходят в режим сброса и сбрасываются под действием синхросигнала, подаваемого на вход С1).

Буквой D обозначаются информационные входы всех триггеров, регистров и счетчиков.

Буквой Е на счетчиках 155, 156, 157 обозначается вход управления функцией

(при лог. О на входе Е счетчиков выполняемой функцией является счет логических единиц, устанавливаемых на счетном входе СЧ поддействием синхросигнала, подаваемого на вход С1 счетчиков, а при лог. 1 на

входе Е счетчиков 155, 156, устанавливается режим приема информации со входов D под действием синхросигнала, подаваемого на вход С1.

Буквой Q на триггерах обозначен выход

триггеров, на котором состояние изменяется под действием синхросигнала, подавав мого на вход С1. Буквой F на триггерах, регистрах и счетчиках обозначены выходы, состояние которых под действием синхросигнала, подаваемого на вход СГ, не изменяется, а изменяется только поддействием второго синхросигнала, подаваемого на вход синхронизации, не имеющий буквенного обозначения.

Буквой F обозначается выход сигнала, инверсного по отношению к сигналу на выходе f. He обозначенные выходы регистров 120. 121, счетного триггера 161 эквивалентны 0 - выходам. Не обозначенные выходы

регистра Т83, а также регистров 7, 8 эквивалентны Q-выходам. Выходы регистров 1, 20, 21 эквивалентны F-выходам.

Триггеры, регистры, счетчики могут быть построены с использованием микросхем КМ500ТТ2, KM500PG4. КМ500СТ2, КМ500ТТ.

Память б и регистр 1 могут быть постро- ены с использованием микросхем KM500PG3.

В качестве элементов ПЗУ могут быть использованы микросхемы 500РТ4 16.

Буквой Е на элементе ПЗУ 187 обозначается вход блокировки выходов (при лог. О на входе Е ПЗУ на всех разрядах выхода

ПЗУ устанавливается высокоимпедансное (третье) (для ЭСЛ-логики - логические единицы) состояние.

Регистр 1 предназначен для временного хранения кода состояния, формируемого

и хранимого в узле 4 вместе с контрольным разрядом, формируемым с помощью элемента 2 свертки по модулю два при выполнении операции внешнего обмена - Чтение данных, хранимых в блоках 9, 12

или 10, 13, и передачи их на выходы 23, 24 через буферную память б.

С помощью элемента ИЛИ 3 формируется запрос (сигнал на выходе 28) в ЦП на обслуживание устройства, которое всегда начинается с операции Чтение данных.

Узел 4 предназначен для фиксации состояний устройства, требующих обслуживания со стороны ЦП. Дополнительно фиксируется код адреса, формируемый на выходе 55 каждый раз в 4-м цикле при отсутствии тяжелой ошибки. При наличии тяжелой ошибки зафиксированный код адреса вместе с сигналом тяжелой ошибки хранится до операции внешнего обмена Чтение данных.

Блок 5 предназначен для управления внешним обменом устройства.

Буферная память б предназначена для временного хранения кода информации вместе с контрольными разрядами, передаваемыми при выполнении операций внешнего обмена как чтение данных - операция чтения, так и запись данных - операция записи. Буферная память 6 может быть по- строена на регистрах или иметь другую структуру.

В предложенном варианте буферной памяти б под действием синхросигнала - С1 (на входе 29) осуществляется запись инфор- мации в регистры 20, 21 при соответствующих управляющих сигналах на входах 33 и 35, а под действием синхросигнала С2 на входе 29 осуществляется передача записанной информации на выбранный выход.

Регистры 7 и 8 предназначены для временного хранения информации и соответствующих контрольных бит, записываемых в блоки памяти 9(10) и 12(13) для обеспечения одновременного действия информации из блоков памяти 10(9) и 13(12). Информация записывается и сразу передается на выходы регистров 7, 8 под действием синхросигнала СИЗ - 1, подаваемого на вход 74.

Блоки памяти 9(10) и 12(13) предназна- чены соответственно для хранения кодов значений часов, компаратора, таймера процессора, кодов формирования импульсов продвижения интервального таймера и соответствующих им контрольных кодов. Эти блоки памяти могут бы гь построены на микросхемах типа 500 РУ 145.

Блок 11 предназначен для формирования контрольных бит для байтов кодов, записанных в регистр 7, и может быть построен на микросхемах типа 500ИЕ160А.

Узел 14 предназначен для модификации (счета) значения часов, компаратора, тайме- ра процессора и кодов формирования импульсов интервального таймера.

При модификации значений кодов обеспечивается прибавление единицы - при отсутствии ошибки, или прибавление трех при наличии легкой ошибки, что управляется сигналами ПЗЦ1 и ПЗЦ11. соответствующей логикой функциональной схемы (фиг. 9), а также благодаря соответствующей кодировке элементов ПЗУ 187. При выполнении операции внешнего обмена типа Запись данных под управлением сигнала СЗП осуществляется блокировка (установка высоко- импедансного состояния) выхода 47,

На выходе 36 формируются необходимые сигналы переносов.

Элементы ПЗУ 187 кодируются следующим образом. При установке на разряде /0/3/ адресного входа элементов ПЗУ 187 двоичного кода а, а на разрядах 4, 5, 6 адресного входа - кодов 001 и 011, на разрядах /0/3/ выхода элементов ПЗУ 187 формируется код а+3. При формировании на разрядах 4, 5, 6 кодов 101 или 111 на разрядах /0/3/ выхода элемента ПЗУ 187 формируются коды соответственно а и а+1. При формировании на разрядах 4.5, 6 кодов 000. 010. 100, 110 на разрядах /0/3/ выхода ПЗУ 187 формируется код 0000.

Узел 14 может содержать элементы ПЗУ 187, закодированные описанным выше способом, элементы И 189, И-НЕ 188, 190, 191, 194. 2И-ИЛИ 193, 195, 197. дешифраторы 192.196, триггер 198. На выходе дешдифра- тора 192 устанавливается логическая единица при установке на входе (разряда /4/7/ кода 1100. На выходе дешифратора 196 устанавливается логическая единица при установке на входе кодов 1110, 1101, 1111. Триггер 198 предназначен для временного хранения значения сигнала переноса в по- следующий байт данных, код которого считывается в последующем цикле.

Дополнительно функционирование узла 14 будет пояснено при описании функционирования устройства.

Блок 15 предназначен для формирования (на выходе 54) контрольных бит (доу бит) соответственно для двух байтов, считываемых из блока 9 или 10, для последующего их сравнения в узле 17 (т.е. для контроля) с контрольными битами четности, считываемыми из блока 12 или 13, и для формирования (на выходах 64, 78, 79 предсказанных контрольных бит соответственно для двух байт информации, формируемой на выходе узла 14 и запоминаемой в регистре 7. Сформированные на выходах 64, 78, 79 контрольные биты записываются в регистр 8 одновременно с записью двух байт информации в регистр 7 и сравниваются в узле 16 с контрольными битами четности (сформированных в узле 11) для двух байт информации, записанной в регистр 7 При несравнении контрольных бит четности с битами четности на выходах 61, 62 формируются сигналы ошибок. Формирование контрольных битов четности, фиксируемых в регистре 8, осуществляется с учетом сигналов переносов на входе 51 и управляющих сигналов на входах 51,53, 56, а также в результате пребразования сигналов с помощью элемента 22.

Функциональная схема блока 15 изображена на фиг. 11 и может содержать элементы ПЗУ 214, 215, закодированных в соответствии с таблицами на фиг. 12, 13, элементов 2И-ИЛИ 219, 4И-ИЛИ 220, 221. И218, 217, НЕ 216.

Блок 18 предназначен для фиксации ошибок, формируемых на входах 61, 62 и интерпретации их как легких ошибок, подлежащих исправлению, или как тяжелых ошибок, не подлежащих исправлению. При возникновении легкой ошибки и ее исправлении на выходе 63 формируется сигнал лог. 1. При этом на выходе 56 формируется сигнал прибавления тройки ( ПЗЦ1 1. ). При возникновении тяжелой ошибки на выходе 46 формируется сигнал ОШТ 1.

При выполнении операций внешнего обмена сигналы ошибок фиксируются отдельно с формированием сигнала ошибки / ОШКОМ 1 на выходе 58, который необходим ЦП для формирования кода признака выполнения соответствующей команды или микрооперации в ЦП. Сброс сигналов ошибок, возникающих при выполнении операций внешнего обмена. также осуществляется автономно путем формирования (внешней системой) на входе 57 сигнала СБРОШКОМ 0 длительностью большей 1ТЦ.

Блок 19 предназначен для формирования кодов адресов и управляющих сигналов для блоков памяти 9, 10, 12, 13 (на выходах 55, 67, 68, 69, 70. 71, 72) и управляющих сигналов (на выходе 42) для всех остальных узлов и блоков устройства, соответствующих определенным комбинациям адресных кодов на выходах 55, 67, 68. Логика работы блока 19 однозначно определяется структурой схемой на фиг. 6 и функциональной схемой узла 132 формирования адресных сигналов, изображенной на фиг. 3. При установке на управляющих входах 69, 72 коммутатора 131 кода 01 на его выход 138 передается код со входа 68. а при установке кода 10 - на его выход 138 передается код со входа 67.

При установке на входе 144 логического нуля на выходах дешифратора 139 устанавливается логический ноль, кроме выхода с сигналом Ц1, на котором устанавливается

Ц1 1 (см. фиг. 6).

Устройство работает следующим образом.

Для приведения устройства в исходное состояние все элементы памяти обнуляют0 ся, т.е. выполняется процедура сброса На всех разрядах входа 40 постоянно устанавливаются следующие сигналы исходного состояния устройства ПРМРД 1. ИНДРД 1. БЛКШ - 0. РТИ2В 0. РТИПП1 - 1 и

5 ТРСК-Ц 1. На разрядах входа 39 устанавливается логический ноль. Затем на входе 38 начинают периодически поступать сигналы синхронизации от центрального процессора, которые в случае отсутствия операций

0 внешнего обмена не влияют на работу устройства.

На входе 77 сразу после включения формируются импульсы отсчета ГИ, которые, при отсутствии сигналов синхронизации ус5 тройства С1. С2 и СИ1, СИ2. СИЗ не влияют на состояние устройства, установленное после выполнения процедуры сброса

Затем на разрядах входа 29 периодиче0 ски поступают сигналы синхронизации С1, С2. а на входе 30 - синхросигналы СИ1, СИ2, СИЗ. т.е. включается синхронизации устройства. После включения синхронизации устройство считывается готовым к рабо5 те (выполнять свои функции). При этом если в момент включения синхронизации устройства сигнал ГИ 1,устройство не запустится т.к. (см. фиг. 7) триггер 163 заблокирован (на входе Е установлен лог. О, а на выходе

0 168 триггера 163 установлен логический ноль. Триггерже 164 не может переключаться в единичное состояние и разблокировать триггер 163, т.к. на входе триггера 164 установлен логический ноль. Только когда на

5 входе 77 установится логический ноль ( ГИ 0), в триггер 164 запишется логическая единица со входа R. которая разблокирует триггер 163, нулевое состояние которого подтверждается записью логического нуля,

0 со входа С1. Т.е. устройство по-прежнему не запускается, так как все триггеры и регистры находятся в нулевом состоянии, на выходе 145 удерживается логический ноль, сигналы , Ц2 0, ЦЗ О, Ц4 0.

5 Ц5 0, Ц1-1, , СЗП-1. СЧТ 0. СЗП 0, ЧС 0, КМ 0, ТП 0, WR1 О, WR2 0, E1 - 1. Е2 0, ЧСОП О, КМОП 0, ТПОП 0, САДР 0. СБРОС О ЗАВОП 0, ОЕ1РД 0. 5РД 0 ЕЗРД 0 РД О, ГОП-1 ЯП - п -г -

, МОГТ 0, ЗАВОП 0, J3L1JT 0, ОШЛ О, ОШЕОМ О, ПЗЦ1 1. ЦЗЦ1

0,ГОП 0 (значения не упомянутых сигналов могут быть произвольны. Только когда на входе 77 вновь появится логическая единица (ГИ 1), в триггер 163 записывается логическая единица, которая устанавливается на выходе 168 (фиг. 7) и разблокировы- вает счетчики 155, 1G6, 157, запуская тем самым работу устройства. Таким образом обеспечивается синхронизация начала отсчета времени в устройстве (отсчет начинается в начальный момент появления ГИ

1,а не с середины или с конца) и исключение ошибок управления.

С запуском работы устройства счетчик 157 и счетный триггер 161 (фиг. 7) смогут переключаться (считать) только при установке на счетном входе СЧ логической единицы. Это произойдет только тогда, когда на выходе счетчика 155 (156) установится нулевой (единичный) код, а на выходе счетчика 156 (155) - единичный (нулевой) код.

Так как в триггере 161 установлен логический ноль, то счетчик 155 будет выполнять функцию счета, а счетчик 156 - функцию приема информации со входа

С появлением логической единицы на выходе 144 в момент появления сигнала СИ 1 начинается первый цикл работы (рабочий цикл) устройства после его запуска. На выходе 55 будет удерживаться код адреса 00, на выходах 67 и 68 - код 00 и установятся сигналы -Ц1 1 и Ц1 0 При этом в узле 14 осуществится прибавление единицы к значению кода, /становленного на разрядах /0/3/ входа 49 (смотри фиг 9) К значению кода, установленного на разрядах /4/15/ входа 49, также прибавится единица Под действием синхросигнала СИЗ 1 в регистры 7 и 8 запишется информация с их входов. С появлением следующего синхросигнала - СИ1 1 на выходе 68 счетчика 155 установится код 01, в счетчик 156 запишется код 00, который установится на выходе 67 узла 132 Код со входа 68 передается на выход 138 в блоке внутреннего управления 19 и дешифрируется на дешифраторе 133 (фиг 6). в результате чего появится сигнал -Ц2 1 и восстановятся сигналы Ц1 1, Ц1 0, т е кончается первый цикл и начинается второй цикл работы устройства. При этом в предыдущем (1-ом) цикле в момент действия сигнала СИ2 2 не формируется сигнал WR2 1 (т.к. на выходе 141 установлен логический ноль), благодаря чему блокируется запись в блоки памяти 9 и 12. Под действием сигнала СИ1 1 во втором цикле осуществляется формирование сигнала переноса на выходе

199 регистра 198 в узле 14 (фиг. 9) Под действием сигнала СИЗ 1 в первом цикле в рргистр 7 осуществляется запись кода, считанного в первом цикле из блока 10 вме- сте с контрольными битами из блока 13, модифицированного в узле 14, и установленного на входе 47 В регистр 8 при этом осуществляется запись предсказанных бит четности для кода, записываемого в регистр

0 7. Код, считанный из блока 10, контролируется по четности с помощью блока 15 и узла 17, в код, записываемый в блок 9, контролируется по четности с помощью блоков 11,15 в узле 16.

5 В заявленном устройстве формирование импульсов продвижения интервального таймера ( СИТ) осуществляется при модификации значений часов в первом цикле ( Ц1 1) путем независимого (автономного)

0 счета в разрядах /4/15/ узла 14 при одновременном независимом счете в разрядах /0/3/ узла 14 (фиг 9). С помощью дешифратора 192 и элемента 191 узла 14 (фиг 9) осуществляется фиксация момента счета с

5 появлением (256х13)3328 импульса (в микросекундах, что приблизительно равно 1 /300 с) осуществляется формирование сигнала СИТ 1 и автоматическое формирование нулевого кода на разрядах /4/15/

0 выхода 47 узла 14 Для того/ггобы при этом обеспечить побайтный контроль по четности, модифицируемой узлом 14 информации, в узле 15 предусматривается независимое формирование предсказан5 ных сигналов четности отдельно для кода информации старшей тетрады (разряды /0/3/ (на выходе 70 узла 15) и для кода информации младшей тетрады (разряды /4/7/ (на выходе 78 узла 15) старшего байта

0 выхода 47 узла 14 С помощью элемента 22 свертки эти сигналы складываются по модулю два, в результате чего на выходе элемента 22 формируется и записывается в старший разряд регистра 8 предсказанный

5 сигнал четности для всего старшего байта информации в регистре 7. Описанное про: исходит только в 1-ом цикле работы устройства. В остальных циклах работы устройства на выходе 78 формируется нулевой код. а но

0 выходе 79 формируется предсказанный сигнал четности для всего старшего байта (см. фиг. 11 и кодировку элементов ПЗУ 214 и 215 на фиг. 12, 13). При выполнении операции внешнего обмена - записи нового значения

5 часов в 1-м цикле в разряды /4/15/ регистра 7 предотвращается запись нового кода, а осуществляется запись кода, считанного из . памяти 9 или 10 и модифицированного в узле 14. В разряды же /0/3/ регистра 7 осуществляется запись старшей тетрады

нового значения часов, При этом на шине 79 формируется сигнал четности этой тетрады (см. логику узла 15 на фиг. 11), который складывается по модулю два (в элементе 22) с сигналом четности на входе 78. В результате и в этом случае обеспечивается правильное формирование сигнала четности старшего байта информации в регистре 7 и, следовательно, достоверный и более полный контроль. На разрядах выхода 64 узла 15 формируются предсказанные сигналы четности для остальных (младших) байт информации, записываемой в регистр 7.

Для рассматриваемого конкретного случая построения устройства количество разрядов выхода-64 равно 1. При разрядности узла 14 и регистра 7, равной 24, количество разрядов выхода 64 будет равно 2. Возможность нескольких указанных вариантов обозначена многоточием на фиг. 11. Сигналы ошибок; которые могут появиться на входах 61, 62, накапливаются (фиксируются) в триггерах 178, 179 (фиг. 8) в течение всех циклов, пока на выходе 55 удерживается один и тот же код адреса, кроме первого цикла, в котором триггеры 178. 179 сбрасываются. Во втором цикле работы устройства из блоков 10,13 считывается код с контрольными битами по новому адресу (с учетом кода 01 на выходе 68), и этот считанный код сбрасывается аналогично коду, считанному в первом цикле. При этом, во втором цикле, в момент действия сигнала СИ1 1, формируется сигнал WR2 1 (т.к. на выходе 141, 143 установлена логическая единица), который осуществляет запись кодов, записанных в регистрах 7, 8. в блоки памяти 9. 12 соответственно, по адресу, переписанному из счетчика 155 в счетчик 156 и установленному на выходе 67 (при сохраненном коде адреса на выходе 55).

Под действием следующих двух сигналов СИ1 1 в устройстве устанавливаются поочередно третий и четвертый циклы, в которых устройство функционируют аналогично второму циклу только с тем отличием, что на выходе 67 поочередно формируются коды 10 (в третьем цикле) и 11 (в четвертом цикле) и соответствующим образом будут изменяться состояния сигналов ЦЗ, Ц4. Кроме этого, в 4-ом цикле всегда осуществляется запись в триггер 176 (фиг 8) сигнала с выхода элемента 184.

Сигналы -Ц5С и Ц5С повторяют сигналы соответственно Ц5 и Ц5 с задержкой на время между появлением сигналов СИ1 1и .

Под действием следующего сигнала СИ1 1 (после 4-го цикла) в счетчике 155 устанавливается нулевой код, а в счетчике

156 перезаписывается единичный код. В результате на выходе 140 устанавливается логический ноль (Ц5 0), а на выходе 145 - лог.1 ( Ц5 1), т.е устанавливается пятый

цикл. Под действием сигнала СМЗ 1 формируется сигнал Ц5С 1. На выходе 144 устанавливается логический ноль, блокирующий выходы дешифратора 133 (фиг. 6, фиг. 7). В. пятом цикле осуществляется запись

0 управляющих сигналов ТП. КМ. ЧС в регистр 183, запись сигнала ошибки (-ОШЛ) в элемент памяти 184 (под действием сигнала СИ2) (фиг. 8). В узле 14 осуществляется завершение сброса 1 триггера 198. В блоки

5 памяти 9 и 12 осуществляется запись (под действием - СИ2 1) кодов, записанных в регистрах 7 и 8. В узле 4 осуществляется запись в регистр 203 кода адреса со входа 55. При этом продолжается фиксация сигна0 лов ошибок в узле 18 со входов 61, 62.

Под действием следующего сигнала СИ1 1 (после 5-го цикла) на выходе 65 счетчика 157 устанавливается код 01 (прибавляется единица), счетчики 155, 156 сбра5 сываются в нулевое состояние (т.к. на R-входе счетчиков установлен логический ноль с выхода 144).

В результате этого после 5-го цикла работы снова появляются сигналы , Ц1

0 1, т.е. начинается первый цикл работы устройства по модификации нового 52-разрядного кода, начальный адрес которого уже определяется кодом 01 на выходе 55. При этом результаты контроля обработки

5 (модификации) предыдущего 52-разрядного кода (с кодом начального адреса на выходе 55 равным 00), зафиксированные в виде возможных ошибок в триггерах 178, 179 (фиг 8), перезаписываются в соответствующий

0 триггер 171 под действием сигнала СИ1 1. СИЗ 1 в рассматриваемом первом цикле. Выбор соответствующего триггера 171 осуществляется сигналами с выходов регистра 183 благодаря перезаписи в регистр

5 183 адресных сигналов ТП 0, КМ 0, ЧС 1 в предшествовавшем пятом цикле. В рассматриваемом первом цикле указанные сигналы будут иметь уже новые значения: ТП 0, Ш-1.-ЧС-0.

0 В первом цикле в триггер 207 узла 4 фиксируется сигнал тяжелой ошибки (ЗОШТ), возникшей при обработке предшествующего 52-разрядного кода.

В остальном и далее устройство функ5 ционирует так же. как это было описано выше, вплоть до первого цикла обработки нового третьего 52-разрядного кода, когда на выходе 55 установится код 10. Далее алгоритм функционирования устройства по обработке третьего 52-разрядного кода повторяется также, как и второго 52-разрядного кода. Следует заметить, что обработка второго и третьего 52-разрядных кодов отличается от обработки первого кода тем, что в пятом цикле работы (под давлением сигнала - Ц4) осуществляется фиксация сигналов ПЕРП в узле 4. Если ПЕРП 1. тона выходах триггеров 207 узла 4 устанавливаются логические единицы, которые через элемент 3 (фиг. 1) формируют логическую единицу на выходе 28 ( ЗКМ 1. ЗТП 1) - сигнал запроса на обслуживание устройства центральным процессором (ЦП). Это связано с тем, что значение первого 52-разрядного кода представляет часы, а значения второго и третьего кодов представляют компаратор и таймер процессора, которые (в соответствии с принципами работы ЕС ЭВМ) должны вызывать прерывания ЦП, что и осуществляется через формирование сигнала на выходе 28устройства.

В пятом цикле обработки таймера процессора на прямом выходе элемента 160 узла 132 (фиг. 7) формируется логическая единица, подаваемая на счетный вход триггера 161, который под действием сигналов СИЗ, СИ1 переключается. Под действием логического нуля на инверсном выходе элемента 160 в момент действия сигналов СИЗ 1, СИ1 1 осуществляется сброс триггера 163 и счетчика 157, а под действием логического нуля на выходе 144 осуществляется сброс счетчиков 155, 156 в узле 132. При этом в блоке 18 (фиг. 8) и узле 4 (фиг. 10) может осуществляться запись сигналов ошибок в триггере 172, 173, 171, 207 под действием сигнала СИ1 1.

Узел 132 по существу переходит в исходное состояние с тем отличием, что в счетном триггере 161 установлено единичное значение, а в триггерах и элементах памяти блока 18 и узла 4 сохраняются состояния, зафиксированные к рассматриваемому моменту. На выходе 142 устанавливается логическая единица, а на выходе 43 - логический ноль,

Новый запуск устройства осуществляется в следующей микросекунде (после последовательного появления ГИ 0, ГИ 1).

После запуска устройство функционирует, как было описано, с тем отличи м, что информация считывается из блоков памяти 9, 12, а записывается в блоки памяти 10, 13. Счетчик 156 будет работать в режиме счета, а счетчик 155 - в режиме приема информации, а на выход 138 коммутатора 131 будет передаваться код со входа 67. После обработки третьего кода счетный триггер 161 вновь переходит в нулевое состояние и далее после запуска в следующей микросекунде устройство будет функционировать как описано выше. При этом информация будет считываться из блоков памяти 10, 13 и запи- 5 сываться в блоки памяти 9, 12 и изменяются режимы функционирования счетчиков 155, 156 и коммутатора 131.

Таким образом, в каждую следующую микросекунду устройство функционирует

0 аналогично с тем отличием, что поочередно изменяются режимы записи или чтения блоков памяти 8, 12 или 10, 13 и режимы функционирования счетчиков 155, 156 в узле 132 (фиг. 7) и коммутатора 131 в блоке 19,

5 Описанный алгоритм функционирования устройства соответствует основному режиму функционирования - режиму счета, при котором каждую микросекунду последовательно из блоков памяти 10(9), 13(12)

0 считываются четыре 52-х разрядные коды вместе с побайтными контрольными разрядами (битами). К значению каждого кода с помощыоузла 14 прибавляется единица (если отсутствуют ошибки) или три единицы

5 (если имеет место легкая ошибка и она исправляется).

Новое значение каждого кода с выхода 47 через регистр 7 записывается вместе с контрольными битами в блоки памяти 9(10)

0 и 12(13). При этом с помощью блока 15 и узла 17 осуществляется контроль по четности кодов, считываемых из блоков 9(10) благодаря формированию побайтовых контрольных сигналов четности на выходе 54 для кодов,

5 считанных на вход 49, и сравнения их в узле 17 с сигналами четности, считанными из блоков 12(13) 11 и 15 и узла 16 осуществляется контроль по четности кодов, получаемых в результате счета (модификации) в узле

0 14 после записи их в регистр 7 благодаря формированию на выходах 78, 79, 64 контрольных предсказанных сигналов четности для кодов на выходе 47 сравнения их в узле 16 (после записи в регистр 8 одновременно

5 с записью в регистр 7 кода с выхода 47) с сигналами четности кодов на выходе 48, формируемых с помощью блока 11. При этом, если при модификации (счете) любого 52-разрядного кода, считываемого вместе с

0 контрольными разрядами из блоков памяти 10(9), 13(12)}на выходах 61. 62 впервые формируется хоть один сигнал ошибки (несравнения, то он фиксируется в блоке 18 как легкая ошибка (и фиксируется в один из

5 регистров 171 блока 18 (фиг, 8), При этом значение 52-разрядного кода с ошибкой после узла 14 в регистре 7 записывается вместе с вновь сформированными контрольными битами (по тому же адресу.

по которому считывался) в блоки памяти 9(10), 12(13),

В следующей второй микросекунде из блоков памяти 9(10) считывается код с ошибкой. Однако при этом же выходе 63 устанавливается сигнал -ОШЛ 1 (см. фиг. 8), под действием которого на выходе 141 и выходах 70, 71 устанавливается (см. фиг. 7, фиг. 6) логический ноль, который блокирует запись в блоки памяти 10(9), 13(12) кода с ошибкой, обеспечивал сохранение в указанных блоках памяти правильного зщначения кода но меньшего по сравнению с требуемым на две единицы, т.е. на две микросекунды. Таким образом, счет по существу блокируется, т.е. имеет место холостой ход. При холостом ходе в блоке 18 блокируется также фиксация ошибок (см. фиг. 8) со входов 6Т, 62, в соответствующий регистр 171, зафиксировавший рассматриваемую ошибку, обнуляется после перезаписи ее (под действием сигнала -СИ2 1 в пятом цикле) в элемент ОЗУ 184.

В следующей (третьей) микрокоманде из блоков памяти 10(9), 13(12) считывается правильное значение кода, но меньшее на две единицы. Параллельно из элемента ОЗУ 184 считывается сигнал перезапомненной легкой ошибки, под действием которого в первом цикле на выходе 56 формируются сигналы ПЗЦ1 0, ПЗЦ1 1. под действием которых в узле 14 обеспечивается модификация кода на три единицы, а в блоке 15 соответствующее формирование контрольных предсказанных сигналов четности на выходах 78, 79 (см. фиг. 9, фиг. 12 и фиг. 11, фиг. 13). В узле 14 (фиг. 9) сигналом ПЗЦ1 О блокируется цепь формирования переноса при прибавлении единицы в первом цикле (элемент 195) и обеспечивается настройка старшего (крайнего нижнего на фиг. 9) элемента ПЗУ 187 на прибавление трех единиц. Под действием сигнала ПЗЦ1 1 разблокировывается цепь формирование переноса (в первом цикле) при прибавлении трех единиц (т.е. перенос формируется при наличии кодов 1111, 1110, 11101 кодов на разрядах /0/3/ входа 49, что обеспечивается дешифратором 196 (фиг, 9). Таким образом, в первом цикле на разрядах /0/3/ выхода 47 узла 14 формируется код. значение которого на три единицы больше значения кода на разрядах /0/3/ входа 49.

На выходе элемента 197 при наличии условия формируется сигнал переноса, который запоминается в триггер 198, формируя сигнал ПЕР1, Далее (в циклах 2, 3, 4, 5) узел 144 функционирует также, как и при прибавлении одной единицы

На разрядах /4/15/ выхода 47 узла 14 в первом цикле также формируется код, значение которого на три единицы больше значения кода на разрядах /4/15/ входа 49 (под

действием сигналов ПЗЦ1 1 и с помощью элементов 193, 197, 196).

На выходе 63 формируется логический ноль, т.к. соответствующий триггер 171. хранивший сигнал легкой ошибки, обнулен в

0 предыдущей (второй) микросекунде, В результате блокировка записи Б в блоке памяти 9(10) и 12(13) отсутствует. В четвертом цикле сигнал легкой ошибки в выходе элемента 184 перезапоминается в триггер 176.

5 Если в процессе модификации кода на три единицы, на входах 61. 62 появится хоть один сигнал ошибки, который зафиксируется в триггере 178 или 179, то в пятом цикле на выходе 46 сформируется сигнал тяже0 лой ошибки ОШТ 1, который в первом цикле (под действием сигнала СМ1 1) модификации последнего кода фиксируется в триггере EBB 207 узла 4 (фиг. 10) и блокирует этот же триггер 207 и регистр 206 от

5 переключений в дальнейшем. Так как в регистр 206 в 4-м цикле запоминается код начального адреса, по которому хранился модифицируемый код, то таким образом обеспечивается точное указание ошибочно0 го кода. т.е. обеспечивается высокая диагностическая способность контроля. При этом в пятом цикле в элемент ОЗУ 184 (фиг. 8) записывается нулевой код по адресу, где был записан сигнал легкой ошибки, а в

5 первом цикле модификации, последующего кода (под действием сигнала СИ2 1 триггер 176 сбрасывается (т.е. описанная процедура формирования сигналов ошибок и их обработки может повториться в последую0 щих микросекундах, но с тем отличием, что записей кодов в регистр 206 и сигналов ошибок в триггер 207 не будет осуществляться, если не было операции внешнего обмена - операции чтения, при которой осуществля5 ется сброс всех триггеров и регистра узла 4). Таким образом, обеспечивается восстановление правильных значений кодов при их искажениях, вызванных помехами и фиксация адреса искаженного кода, не подле0 жащего восстановлению, следовательно, обеспечивается более высокая помехоустойчивость устройства по сравнению о прототипом и повышение диагностической способности контроля. Из режима Счета

5 устройства может перейти в режим записи (когда выполняется операция записи) или режим чтения (когда выполняется операция записи) или режим чтения (когда выполняется операция чтения). Режим записи устанавливается, если на входе 39 задается код

записи ( РМК-/42/П 1, РМК, нового значения часов (при МОЧС 1) или компаратора (при МОКМ 1), или таймера процессора (при МОТМ 1).

Режим чтения устанавливается, если на входе 39 задается код чтения ( PMK/42/n О, РМК/42/ 1 значения часов (при МОЧС 1), или компаратора (при МОКМ 1), или таймера процессора (при МОТМ 1).

. Сигналы МОЧС. МОКМ. МОТМ в обоих случаях представляют по существу код адреса обращения в блоках памяти 9(10), 12(13),по которому необходимо осуществить запись нового 52-разрядного кода или чтение текущего кода.

В обоих случаях сигналы на входе 39, задающие адрес обращения (через элементы 124. фиг. 4), записываются в регистр 121 (по С2 1) и устанавливаются на выходе 91 (по С1 1). С помощью элементов 116.122, 123 осуществляется дешифрация сигналов на выходе 39 и в регистр 120 (по С2 ; 1) записываются сигналы МОП 1 и сигналы ЧТ 1, ЗП 0 (при операции чтения) или сигналы ЧИ - 0. ЗП 1 (при операции записи).

Когда код на входе 91 (сигналов ЧСОП, КМОП, ТПОП) совпадает с кодом на входе

95(сигналов ЧС, КМ, ТП) (фиг. 2, фиг. 5), в триггер 128 (фиг. 5) в первом цикле записывается логическая единица (под действием СИ2 1) и на выходе 94 формируется сигнал САДР 1. С этого момента начинается режим Чтение (при -ЧТ 1).

Перед режимом записи, в момент действия сигнала ТИ2 С2 1, формируется сигнал ЗПБП 1 (фиг. 4), который подается (через элементы 113 (фиг. 3) на все разряды выхода 98 (формируя векторный сигнал ЕРД 1) с помощью которого обеспечивается (под действием сигналов С1 1. С2 1 запись кодов со входов 23, 24 в регистры 20, 21. так как на выходе 35 формируется сигнал РД 1 (см. фиг. 3). После установки сигнала ЕРД4 1 под действием сигнала С1 1 в триггер 102 (фиг. 3) записывается логическая единица, под действием которой блокируются (в момент действия сигнала С2 1) все разряды выхода 98 Сигнал САДР 1 не может формироваться до появления сигнала ЕРД 1 и установки в единичное состояние триггера 102, так как на выходе

96формируется логический ноль, сбрасывающий триггер 128 в узле 82. Только потом, когда на выходе 96 (после установки триггера 102) установится логическая единица, то в первом цикле формируется сигнал САДР 1 при совпадении кодов на входах 91, 95. С этого момента начинается режим записи (при ЗП 1).

В режиме чтения (с появлением сигнала САДР 1) на разрядах 1, 2, 3, 4 поочередно появляется сигнал ЕРД/i/ 1 (I 1-4), обеспечивающий запись кодов со входа 47 5 и входов 64, 79 в l-ый регистр соответственно 20 и 21 одновременно с записью их в регистры соответственно 7,8 и запись кодов со входов 26, 25 в регистр 1. В момент записи в 4-й регистр 20(21) и регистр 1 устанав0 ливается в единичное состояние триггер 102 в узле 80 и в устройстве вновь устанавливается режим счета.

В узле же 80 под действием сигналов ТИ2-С2. ТИЗ-С2 устанавливается логиче5 екая единица на выходе триггера 104, а на выходе элемента 108 (фиг. 3) устанавливается также лог. 1, т.е. момент действия сигнала ТИ2-С2 1 на выходах 99 и разряда выхода 34 (выходе элемента 105) установятся поги0 ческие единицы, которые разрешают пыда- чу информации на выходе 24, 23, 32. так как на выходе 35 сигнал 5РД 0. Под действием логической единицы с четвертого разряда выхода 99 устанавливается в единичное

5 состояние (под действием -С1 1) триггер 112 в узле 80, т.е. формируется сигнал ЗА- ВОП 1, благодаря которому в момент появления сигналаТТЧ-С2 1 устанавливается в единичное состояние (о

0 момент С2 1) триггер 115 (в узле 81) и формируется сигнал ГОП 0, под действием которого триггеры 102, 112 в узле 76 сбрасываются (о момент С1 1) В момент действия С1 1 появляется сигнал ГОП -- 1 на

5 выходе 37, а сигнал ТТЧ-С2 0. Регистры 120, 121 сбрасываются (в момент С2 - 1). С появлением вновь сигналов ТТ4 С2-1, ТИ2-С2 (через 120 не в ЭВМ ЕС1130) триггер 104 в узле 80 записывается логический

0 ноль и на выходах 99 и выходе элемента 105 узла 80 устанавливается логический ноль. Триггер 115 в узле 81 сбрасывается. После этого устройство вновь готово к операции внешнего обмена.

5 В режиме записи (с появлением сигнала САДР 1) на разрядах 1, 2, 3. 4 поочередно появляется сигнал ОЕ1РД/1/ (i 1-4), обеспечивающий передачу кода из i-ro регистра 20(21) на выход 47(64, 79). Благодаря

0 действию сигнала СЗП 0. СЗП 1 на выходах элементов ПЗУ 187 (выходе 47) узла 14 устанавливается высокои.мпедапсное (третье) состояние во всех циклах, кроме первого цикла. Под действием сигнала

5 СЗП 1 на выходах элементов 220. 221 (выходах 64, 79) блока 15 устанавливается вы- сокоимпедансное (третье) состояние.

В результате в регистры 7(8) и блоки памяти 9(12) или 10(13) поочередно переписываются коды из регистров 20(21), т.к. на выхЪде97 5РД 1.

В первом цикле при режиме записи разряды /4/15/ узла 14 не блокируются, т.е. обеспечивается запись кодов с разрядов /4/15/ выходе узла 14 в младший байты и в младшую тетраду старшего байта регистра 7. При этом не блокируются и разряды выхода 64 (см. фиг. 11). На выходе 79 устанавливается высокоимпедансное (единичное) состояние, а на выходе 78 - сигнал четности младшей тетрады старшего байта. Из первого регистра 20 в старшую тетраду регист- ра 7 записывается старшая тетрада записывающего кода. Код четности записываемой старшей тетрады из первого регистра 21 через шину 79 складывается по модулю два в элементе 22 с сигналом четности на входе 78 и результат записывается в старший разряд регистра 8

Под действием логической единицы четвертого разряда выхода 99 в триггер 112 записывается логическая единица, благодаря которой в момент появления сигнала ТТЧ-С2 1 в триггер 115 узла 81 (в момент С2 1) записывается логическая единица, устанавливая ТОП 0. В результате (в момент С1 1) триггера 102, 112 в узле 80 сбрасываются и появляется сигнал -ТОП 1 на выходе 37, а ТТЧ-С2 0. Регистры 120, 121 сбрасываются (в момент С2 1). С появлением вновь сигнала ТТЧ-С2 1 триггер 115 в узле 77 сбрасывается. К этому моменту на входе 39 установлен нулевой код и под действием сигнала ТИ2-С2 1 триггер 118 также устанавливается в нулевое состояние. Устройство вновь готово к операции внешнего обмена.

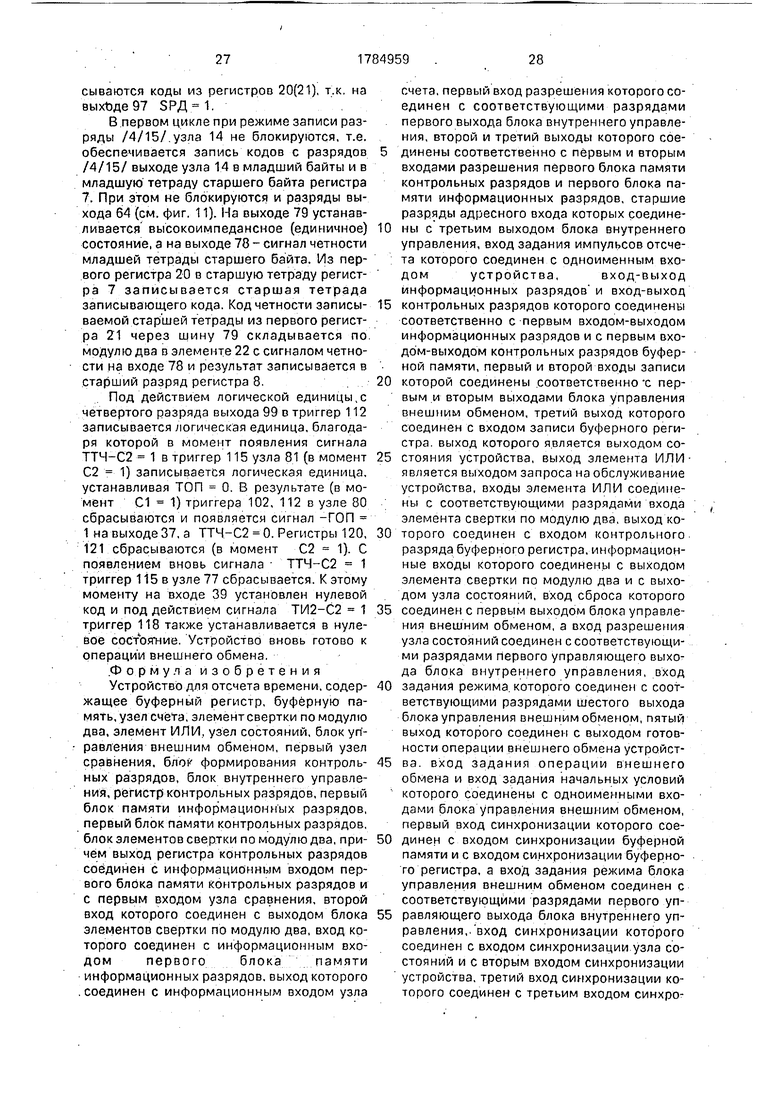

Формула изобретения

Устройство для отсчета времени, содержащее буферный регистр, буферную память, узел счета, элемент свертки по модулю два, элемент ИЛИ, узел состояний, блок управления внешним обменом, первый узел сравнения, блок формирования контрольных разрядов, блок внутреннего управления, регистр контрольных разрядов, первый блок памяти информационных разрядов, первый блок памяти контрольных разрядов, блок элементов свертки по модулю два, причем выход регистра контрольных разрядов соединен с информационным входом первого блока памяти контрольных разрядов и с первым входом узла сравнения, второй вход которого соединен с выходом блока элементов свертки по модулю два, вход которого соединен с информационным входом первого блока памяти информационных разрядов, выход которого соединен с информационным входом узла

счета, первый вход разрешения которого соединен с соответствующими разрядами первого выхода блока внутреннего управления, второй и третий выходы которого соединены соответственно с первым и вторым входами разрешения первого блока памяти контрольных разрядов и первого блока памяти информационных разрядов, старшие разряды адресного входа которых соедине0 ны с третьим выходом блока внутреннего управления, вход задания импульсов отсчета которого соединен с одноименным входомустройства,вход-выход информационных разрядов и вход-выход

5 контрольных разрядов которого соединены соответственно с первым входом-выходом информационных разрядов и с первым входом-выходом контрольных разрядов буферной памяти, первый и второй входы записи

0 которой соединены соответственно с первым и вторым выходами блока управления внешним обменом, третий выход которого соединен с входом записи буферного регистра выход которого является выходом со5 стояния устройства, выход элемента ИЛИ является выходом запроса на обслуживание устройства, входы элемента ИЛИ соединены с соответствующими разрядами входа элемента свертки по модулю два, выход ко0 торого соединен с входом контрольного разряда буферного регистра, информационные входы которого соединены с выходом элемента свертки по модулю два и с выходом узла состояний, вход сброса которого

5 соединен с первым выходом блока управления внешним обменом, а вход разрешения узла состояний соединен с соответствующими разрядами первого управляющего выхода блока внутреннего управления, вход

0 задания режима которого соединен с соответствующими разрядами шестого выхода блока управления внешним обменом, пятый выход которого соединен с выходом готовности операции внешнего обмена устройст5 ва вход задания операции внешнего обмена и вход задания начальных условий которого соединены с одноименными входами блока управления внешним обменом, первый вход синхронизации которого сое0 динен с входом синхронизации буферной памяти и с входом синхронизации буферного регистра, а вход задания режима блока управления внешним обменом соединен с соответствующими разрядами первого уп5 равляющего выхода блока внутреннего управления, вход синхронизации которого соединен с входом синхронизации узла состояний и с вторым входом синхронизации устройства, третий вход синхронизации которого соединен с третьим входом синхронизации блока управления внешним обменом, второй вход синхронизации которого и входы синхронизации узла счета и регистра контрольных разрядов соединены с соответствующими разрядами второго входа синхронизации устройства, отличающееся тем, что, с целью повышения полноты контроля, устройство содержит второй узел сравнения, блок фиксации ошибок, второй блок памяти информационных разрядов, второй блок памяти контрольных разрядов, регистр информационных разрядов, причем первый информационный вход блока фиксации ошибок соединен с выходом первого узла сравнения, первый вход которого сое- динен с информационным входом второго блока памяти контрольных разрядов, выход которого соединен с первым входом второго узла сравнения и с выходом первого блока памяти контрольных разрядов, младшие разряды адресного входа которого соединены с младшими разрядами адресного входа первого блока памяти информационных разрядов и с вторым адресным выходом блока внутреннего управления, третий ад- ресный выход которого соединен с младшими разрядами адресного входа второго блока памяти контрольных разрядов и с младшими разрядами адресного входа второго блока памяти информационных разря- дов, первый и второй входы разрешения которого соединены соответственно с первым и вторым входами разрешения второго блока памяти контрольных разрядов и с четверным и пятым выходами блока внутренне- го управления, вход ошибки которого соединен с первым выходов блока фиксации ошибок, второй вход фиксации ошибок которого соединен с выходом второго узла сравнения, второй вход которого соединен с первым выходом контрольных разрядов блока формирования контрольных разрядов, информационный вход которого соединен с выходом второго блока памяти информационных разрядов и с информаци- онпым входом узла счета, второй вход разрешения которого соединен с третьим входом разрешения блока формирования контрольных разрядов и с вторым выходом блока фиксации ошибок, третий выход кото- рого соединен с входом фиксируемых ошибок узла состояний, вход фиксации адреса которого соединен е первым адресным выходом блока внутреннего управления, а вход фиксации состояний узла состояний соединен с со- ответствующими разрядами выхода переносов узла счета, третий управляющий

вход которого соединен с соответствующими разрядами шестого выхода блока управления внешним обменом. а информационный выход узла счета соединен с вторым информационным входом-выходом буферной памяти и информационным входом регистра информационных разрядов, выход которого соединен с информационными входами второго блока памяти информационных разрядов и первого блока памяти информационных разрядов, а вход синхронизации регистра информационных разрядов соединен с входом синхронизации регистра контрольных разрядов, старший разряд информационного входа которого соединен с выходом элемента свертки по модулю два, первый вход которого соединен с третьим выходом контрольных разрядов блока формирования контрольных разрядов, четвертый выход контрольных разрядов которого соединен с вторым входом элемента свертки по модулю два и со старшим разрядом второго входа- выхода контрольных разрядов буферной памяти, младшие разряды второго входа-пыхода контрольных разрядов которой соединены с младшими разрядами информационного входа регистра контрольных разрядов и с вторым выходом контрольных разрядов блока формирования контрольных разрядов, первый оход разрешения которого соединен с соответствующими разрядами шес того выхода блока управления внешним обменом, второй вход разрешения блока формирования контрольных разрядов соединён с соответствующими разрядами первого управляющего выхода блока внутреннего управления, первый адресный выход которого соединен со старшими разрядами адресного входа второго блока памяти контрольных разрядов и со старшими разрядами адресного входа второго блока пямяти информационных разрядов, первый выход блока внутреннего управления соединен с вторым входом разрешения блока ошибок, вход сброса которого соединен с одноименным входом устройства, второй вход синхронизации которого соединен с входом синхронизации блока фиксации ошибок, четвертый выход которого является выходом ошибки команды обмена устройства, а первый вход разрешения блока фиксации ошибок соединен с шестым вы одом блока управления внешним обменом, оход переноса блока формирования контрольны разрядов соединен с соответствующими разрядами выхода переносов узла счета

$

а

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отсчета времени | 1990 |

|

SU1817085A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

Изобретение относится к области вычислительной техники и предназначено для непрерывного отсчета астрономического времени (функция Часы), для фиксации заранее заданного момента времени (функция Компаратор), для измерения истекшего времени работы процессора (функция Таймер процессора) и для формирования продвигающих ии/пульсов с заданной частотой следования, предназначенных для продвижения интервального таймера, и может быть применено в ЭВМ любого класса, например в ЕС ЭВМ, а также в мультипроцессорных системах. Цель изобретения - повышение полноты контроля. Поставленная цель достигается благодаря тому, что в устройство, содержащее буферный регистр, буферную память, узел счета, элемента свертки по модулю два, элемент ИЛИ, узел состояний, блок управления внешним обменом, первый узел сравнения, блок формиро- вания контрольных разрядов, блок внутреннего управления, регистр контрольных разрядов, первый блок памяти информационных разрядов, первый блок памяти контрольных разрядов, блок элементов свертки по модулю два. дополнительно введены второй узел сравнения, блок фиксации ошибок, второй блок памяти информационных разрядов, второй блок блок памяти информационных разрядов, второй блок памяти контрольных разрядов, элемент свертки по модулю два с новыми связями. Устройство обеспечивает восстановление данных счета с сохранением точности счета устройства при искажении данных помехами. 13 ил. НЈ 45 сл с VI 00 4 Ю СЛ О

v V

sy

к

s.

Фиг.д

29

L.

...fe...4

фие.9

.

фае. //

фие. /2

| Авторское свидетельство СССР № 1596976 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство радиостанций с быстродействующими аппаратами Юза и Бодо | 1922 |

|

SU2130A1 |

| Техническое описание | |||

| Ч | |||

| I | |||

| Общие сведения | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

Авторы

Даты

1992-12-30—Публикация

1990-08-29—Подача