Фж

Изобретение относится к области автс - матики и вычислительной техники и можег быть использовано для организации кот роля сдвигателей высокопроизводительны цифровых узлов.

Цель изобретения - расширение облг сти применения устройства.

На фиг.1 приведена функциональна) схема устройства; на фиг.2-4 - функцис нальные схемы узла формирования сигнг лов четности, формирователя сигнала четности группы и дешифратора типа СДВУ га соответственно.

Устройство (фиг.1) содержит узел 1 фор мирования сигналов четности, узел 2 сдвиг з контрольных разрядов, дешифратор 3 типа сдвига, дешифратор 4 нулевого кода, формирователь 5 дополнительного кода, формирователь 6 кода маски, элементы И 7-J1, элемент ИЛИ 10, вход 11 знака устройств;, информационный вход 12 устройства, груг- па 13 входов контрольных разрядов устройства, вход 14 задания величины сдвига устройства, вход 15 дешифратора 4 нулевс- го кода, младший разряд 16 входа 14 задг- ния величины сдвига устройства, вход 17 задания типа сдвига устройства, выхода 18-20 дешифратора 3 типа сдвига, вход 21 младшего контрольного разряда группы 13 устройства, вход 22 старшего контрольного разряда группы 13 устройства, входы 23, 24 коррекции четности узла 1 формирования сигналов четности, управляющий вход 25 формирователя 5 дополнительного кода, вход 26 дешифратора 4 нулевого кода, вхоц 27 задания величины сдвига узла 1 форм1 - рования сигналов четности, вход 28задану я величины сдвига узла 2 сдвига контрольных разрядов, выход 29 формирователя 6 кора маски, информационный вход 30 формирователя 6 кода маски, информационный вход 31 узла 2 сдвига контрольных разрядов, вн- ход 32 устройства.

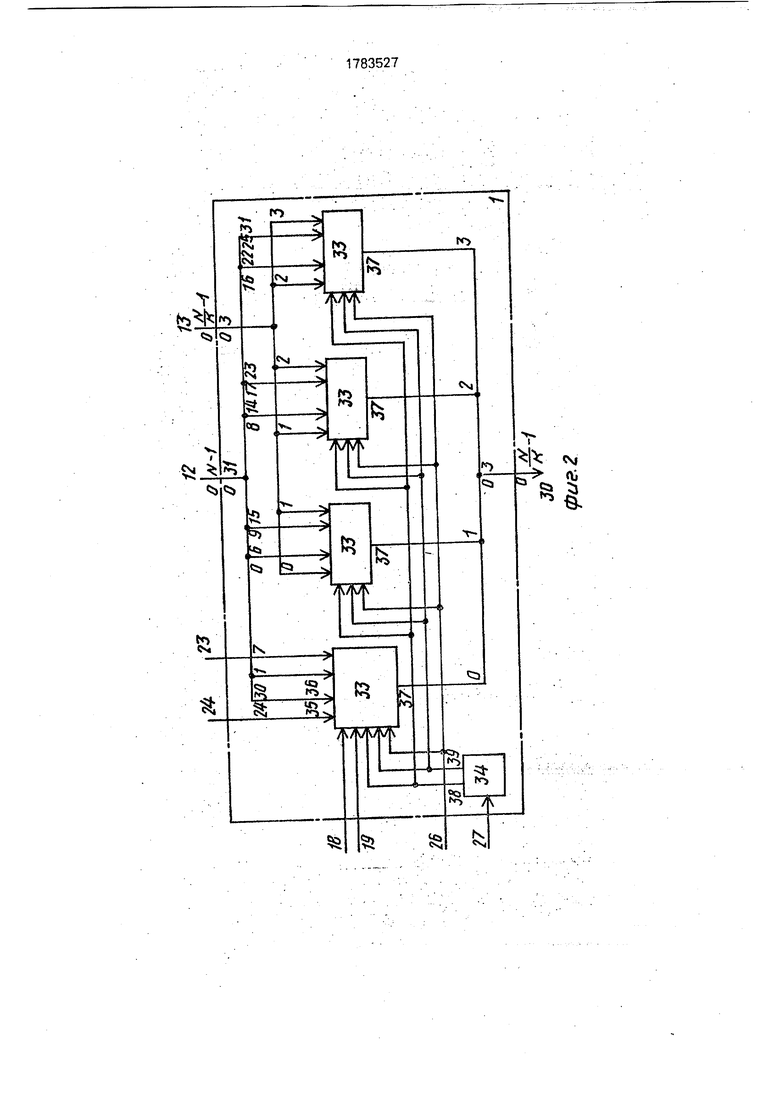

Узел формирования 1 сигналов четности на четыре байта, изображенный на фиг,2, содержит группу 33 формирователей сигнала четности и формирователя 34 кода маски, первый и второй информационные входы 35, 36 формирователя сигнала четности группы 33, соответственно выход 37 формирователя сигнала четности группы 33, входы 38,39 задания величины сдвига влево и вправо формирователя сигнала четности группы 33 соответственно.

Формироветель сигнала четности группы 33, изображенный на фиг.З, содержит узел 40 свертки по модулю два, группы 41, 42 элементов И, элемент И 43, узлы 44, 45 сложения по модулю два, группу элементов 46 ИЛИ.

Дешифратор 3 типа сдвига, изображенный на фиг.4, содержит элементы И 47, 48, элементы ИЛИ 49, 50, разряд 51 задания циклического сдвига, входа 17 устройства,

разряд 52 задания арифметического сдвига входа 17 устройства,

В формирователях группы 33 происходит следующее:

На выходе 37 формирователей группы

0 33 формируется сигнал четности байта сдвинутого кода, для которого сигналы сдвигаемого байта устанавливаются на входе 35, а вдвигаемого байта на входе 36. При этом на входе 23 устанавливается сигнал четности

5 для байта на входе 35 с учетом нулевого разряда, а на входе 24 устанавливается сигнал четности для байта на входе 36 с учетом крайнего правого (7-го) разряда или сигнал четности вдвинутых бит знака (для первого

0 крайнего левого узла группы 33). Например, сдвигаемый байт равен 11001101, а вдвигаемый байт равен 10001101. Например, рассмотрим сдвиг циклический вправо на . На входе 38 сформируется код маски

5 0000111, а на входе 39 - код маски 1111100. На входах 23.24 установятся сигналы четности соответственно 1 и 0, а на входах 35 и 36 будут установлены коды соответственно 1001101 и 1000110. На входе 26 установится

0 логич.1. На выходах групп элементов И 41 и 42 сформируются коды соответственно 0000101 и 10000100.,На входах группы элементов ИЛ И 46 установятся коды соответственно 000010 и 000100, в результате

5 поразрядной операции ИЛИ которых на выходе группы элементов ИЛИ 46 сформируется код 000110. На входе 48 установится код 1. В результате на выходе узла 44 сформируется код 0. На входе узла 45 установит0 ся код 1. В результате на выходе узла 45 сформируется код 1,

Сумма по модулю два сигналов кодов на различных входах элемента 40 ( Q0@000®091810091 1) даст код 1, сигнал

5 которого формируется на выходе 37, который равен сигналу четности байта сдвинутого кода, равного 10111001, если не произошла одиночная ошибка или неисправность в указанном байте.

0 Формирователь 34 кода маски предназначен для формирования кодов маски в соответствии с табл,1 и может быть построен на элементах ПЗУ или в виде логического шифратора.

5 Если величина сдвига (т) в пределах байта равна нулю, то на входах 38, 39, 26 формируются нулевые коды. В результате на выход 37 передается код со входа 23.

Узел 3 предназначен для формирования управляющих сигналов на выходах 18,19,20

в зависимости от типа сдвига, задаваемого кодом на входе 17 устройства, величины и четности количества битных сдвигов, задаваемых кодами на входе 26 узла 4 при m устанавл. лог.1, а при устанавл. лог.О) и на входе 16 (при четном кол. сдвигов устан. лог.О, а при нечетном количестве сдвигов устанавливается лог.1).

На входе 17 устройства в соответствии с типом сдвига могут устанавливаться еле- дующие коды на разрядах 51, 25, 52:

-000 - логический сдвиг вправо (ЛП);

-001 - арифметический сдвиг вправо (АП);

-01Х - логический сдвиг влево (ЛЛ);

-100 - циклический сдвиг вправо (ЦП);

-11Х - циклический сдвиг влево (ЦЛ),

Узел 3 реализует функцию определенную табл.2,

В качестве дешифратора 4 можно ис- пользовать элемент ИЛИ.

Узел 5 является известным формирователем дополнительного кода. При логическом нуле на входе 25 код со входа 14 транзитом передается на выход узла 5 (на разряды 26, 28). При логической единице на входе 25 на выходе узла 5 (разрядах 27, 28) формируется дополнительный код от кода на входе 14.

Формирователь 6 кода маски предназ- начен для формирования кода маски для маскирования соответствующих правых или левых разрядов циклически сдвинутого в узле 2 кода.

Формирователь 6 может быть построен на элементах ПЗУ, закодированных в соответствии с табл.3.

Узел 2 представляет собой узел циклических сдвигов вправо, построенный на мультиплексорах, например, типа К155КП7 и имеет структуры узла односторонних сдвигов, в котором одноименные разряды первого и второго информационных входов соединены между собой, вход блокировки

N

j-ro мультиплексора ,1, (тт-1)} при отсчете слева направо) соединен с j-ым разрядным выходом 29 узла 6 При логическом нуле на j-ом разряда выхода 29 на выходе j-ro мультиплексора и, следовательно, на J- ом разряде выхода 32 устройства устанавливается логический ноль.

Устройство работает следующим образом,

В исходном состоянии на входе 12 устройства устанавливается сдвигаемый код, на входах 13 группы устройства - код контрольных бит, значение каждого 1-го бита которого равно значению, сигнала четности 1-го байта сдвигаемого кода на входе 12 ус

5

10

15

20

25

0

5

0

5

0

5

тройства. На входе 17 устройства устанавливается код типа сдвига. На входе 14 устройства устанавливается код сдвига. При арифметическом сдвиге вправо на входе 11 устройства устанавливается код знака. На выходе 32 устройства формируется k-раз- рядный код предсказанных сигналов четности для сдвинутого кода.

Рассмотрим в качестве примера сдвиги кода 10111000111100001111000011110000 на величину m-HVI.8 5 + 2.8. Т.е. - код на младших разрядах входа 14 устройства, равный 101, а М 2 -код на старших разрядах входа 14 устройства равный 10. На выходе 13 устройства устанавливается код

0000.Последовательно рассмотрим все типы сдвига (см.табл.2).

При логическом сдвиге вправо (ЛП) на выходах 18, 19, 20 дешифратора 3 формируется код 100, На выходе 26 дешифратора 4 установится логическая единица. На старшем разряде 25 информационного входа формирователя 5 установится логический ноль. На управляющем входе узла 6 установится код 00. На входах 27, 28 установятся коды соответственно 101 и 10.

На выходе 29 узла 6 установится код 0011. На входе 24 узла 1 установится логический ноль, а на входе 11 знака устройства значение кода может быть произвольным. На вход 23 узла 1 осуществится передача сигнала четности со входа 22, равного 0, На входах 35 формирователей группы 33 сигналов четности с номерами О, 1, 2, 3 установятся коды соответственно 0111000, 1110000, 1110000, 1110000, а на входах 36 - коды соответственно 11110000, 1011100, 1111000, 1111000. На выходах 38 и 39 узлов группы 33 сформируются коды соответственно 0011111 и 1110000. На выходах групп элементов И 41 формирователей группы 33 сигналов четности с номерами 0, 1, 2 сформируются коды соответственно 0011000, 0010000, 0010000, 0010000, а на выходах элементов И группы 42 - коды соответственно 00000000, 1010000, 1110000, 1110000.

На выходах групп элементов ИЛИ 46 формирователей группы 33 сформируются коды соответственно 001100, 011000, 111000, 111000. На выходах узлов 44 всех формирователей формируется логический ноль. На выходе узлов 45 формирователей группы 33 сигналов четности с номерами О, 1,2,3 формируются коды, соответственно О,

1,1, 1. В результате на выходе 37 формиро- , вателей группы 33 сигналов четности с номерами 0, 1, 2, 3 формируются коды соответственно 0, 1,0, О а на входе 31 узла

2 - код 0100. В узле 2 осуществляется циклический сдвиг вправо на с формированием кода 0001, на который накладывается код маски 0011. В результате на выходе 32 устройства формируется код 0001, предсказанных сигналов четности для логически сдвинутого вправо кода, равного 00000000 ОШООООО 00000101 11000111.

При арифметическом сдвиге вправо (АП) устройство функционирует также как и при логическом сдвиге вправо, с тем отличием, что на входе 11 устройства устанавливается код знака, равный в рассматриваемом примере логической 1, т.к. нулевой разряд сдвигаемого кода равен 1, а на выходах 18, 19, 20 узла 3 формируется код 101 (см.табл.2 с учетом того, что на входе 18 установлена логическая единица - младший разряд кода 5 1001), В результате код (лог.1) со входа 11 устройства будет передан на вход 24 узла 1. В результате на выходе 37 первого формирователя группы 33 сформируется код 1. Т.е. на входе 31 узла 2 сформируется код 1100 и, следовательно, на выходе 32 устройства сформируется код 0011 предсказанных сигналов четности для арифметически сдвинутого вправо кода, равного 11111111, 11111111 11111101 11000111.

При циклическом сдвиге вправо (ЦП) устройство функционирует так же, как и при логическом сдвиге вправо, с тем отличием что на выходах 18,19,20 узла 3 формируется код 110, а на выходе 29 узла - код 11111111. В результате на вход 24 узла 1 передается код (лог.О) с разряда 21, а на выход группы элементов И 42 первого формирователя сигнала четности группы 33 - код 11100000. На входе группы элементов ИЛИ 46 формируется код 111100. На выходе узла 45 формируется код 1. В результате на выходе 37 первого узла группы 33 формируется код 1, на выходе 31 узла 1 - код 1100, а на выходе 32 устройства - код 0011 предсказанных сигналов четности для циклически сдвинутого вправо кода, равного 10000111100001111000010111000111.

При логическом сдвиге влево (Л Л) функционирование устройства различается от функционирования при логическом сдвиге вправо тем, что на входе 25 узла 5 устанавливается логическая единица, а на входах 27, 28 узлов 1, 2 формируется дополнительный ксгдбт кода на входе устройства 14, т.е. на входе 27 формируется код , а на входе 28 - код . На- выходе 29 узла 5 формируется код 1100, а на выходах 18, 19, 20 узла 3- код 010.

В результате на вход 24 узла 1 передается код (лог.О) с разряда входе 23 узла 1 формируется логический ноль. На

входах 38, 39 узлов группы 33 формируются коды соответственно 0000 111-и 1111100.

На выходе группы элементов И 41 формирователей группы.33 сигналов четности с

номерами 0, 1, 2, 3 сформируются коды соответственно 0000000, 0000000, 0000000, а на выходах группы элементов И 42 - коды 1111000, 1011100, 11110000, 1111000. На выходе узла 44 всех формирователей сигналов четности группы 33 формируется логический ноль. На выходе узла 45 формирователей группы 33 сигналов четности с номерами 0,1, 2,3 формируются коды соответственно 1, 1, 1, 1. На выходе группы

элементов ИЛИ 46 формирователей группы 33 сигналов четности с номерами 0, 1, 2, 3 сформируются коды, равные соответственно 111000, 011100, 111000, 111000. В результате на выходе 37 формирователей

группы 33 сигналов четности с номерами О, 1, 2, 3 сформируются коды равные соответственно О, О, О, О, а на входе 31 узла 2 формируются код 0000, который сдвигается циклическим вправо на величину

и затем маскируется кодом 1100. В результате на выходе 32 устройства сформируется код 0000 предсказанных сигналов четности для логически сдвинутого влево кода, рзвно- го 00011110000000000000000000000000.

При циклическом сдвиге влево (ЦЛ)уст- ройство функционирует также, как и при логическом сдвиге влево, с тем отличием, что на выходах 18,19,20 узла 3 формируется код 110, а на выходе 29 узла 6 код 11111111.

В результате на вход 23 узла 1 передается код (лог 0) с разряда 22, на выходе группы элементов И 41 формирователя сигналов четности первого узла группы 33 формируется код 0000000. На выходе группы элементов И ПИ 46 этого же формирователя сформируется код 000000. На выходе 37 первого формирователя сигналов четности группы 33 сформируется логический ноль, а на входе 31 узла 2 - код 0000. После циклического сдвига в узле 2 кода со входа 31 на выходе 32 устройства сформируется код 0000 предсказанных сигналов четности для циклически сдвинутого влево кода, равного 0001111000010111 0001111000011110.

В случае, если 0, то на входе 26 узла 4 устанавливается логический ноль, на входах 38, 39 узлов группы 33 формируются нулевые коды, на выходах 18, 19, 20 узла 3 формируется код 1x0, на выходах

узлов 45 и выходе группы элементов ИЛИ 46 всех формирователей группы 33 формируются нулевые коды. В результате сигналы четности с группы входов 13 транзитом передаются на вход 31 узла 2, что и требуется.

Таким образом, в устройстве обеспечивается формирование сигналов четности при всех типах сдвига (см.табл.2). Формула изобретения 1. Устройство для формирования сигналов четности при сдвигах двоичных кодов, содержащее узел формирования сигналов четности, узел сдвига контрольных разрядов, дешифратор нулевого кода, формирователь дополнительного кода и первый элемент И, причем информационный вход узла формирования сигналов четности является информационным входом устройства, группа входов контрольных разрядов узла формирования сигналов четности образует группу входов контрольных разрядов устройства, выход узла формирования сигналов четности соединен с информационным входом узла сдвига контрольных разрядов, выход которого является выходом устройства, выход первого элемента И соединен с первым входом коррекции четности узла формирования сигналов четности, вход блокировки сдвига которого соединен с выходом дешифратора нулевого кода, информационный вход формирователя дополнительного кода образует вход задания величины сдвига устройства, группа младших разрядов выхода формирователя дополнительного кода соединена с соответствующими разрядами входа задания величины сдвига узла формирования сигналов четности, группа младших разрядов входа задания величины сдвига устройства подключена к соответствующим разрядам входа дешифратора нулевого кода, отличающееся тем, что, с целью расширения области применения устройства, в него введены второй и третий элементы И, элемент ИЛИ, формирователь кода маски и дешифратор типа сдвига, причем первый, второй и третей выходы дешифратора типа сдвига соединены с первыми входами первого, второго и третьего элементов И соответственно, выходы второго и третьего элементов И соединены с соответствующими входами эпемента ИЛИ, выход которого соединен с вторым входом коррекции четности узла формирования сигналов четности, вторые входы первого и второго

элементов И подключены к первому и у МУ

входам контрольных разрядов группы устройства соответственно (N - число разрядов информационного входа, К - число разрядов в байте), второй вход третьего элемента И является входом знака устройства, первый и второй выходы дешифратора типа сдвига соединены соответственное первым и вторым разрядами входа задания типа

сдвига узла формирования сигналов четности, группа старших разрядов информационного входа дешифратора типа сдвига образуют вход задания типа сдвига устрой5 ства, первый и второй разряды информационного входа дешифратора типа сдвига подключены соответственно к выходу дешифратора нулевого кода и младшему разряду входа задания величины сдвига

0 устройства, третий, четвертый и пятый разряды информационного входа дешифратора типа сдвига образуют вход задания типа сдвига устройства, управляющий вход формирователя дополнительного кода подклю5 чен к разряду признака направления сдвига входа задания типа сдвига устройства, управляющий вход формирователя кода маски подключен к входу задания типа сдвига устройства, разряды информационного входа

0 формирователя кода маски подключены к группе старших разрядов входа задания величины сдвига устройства, группа старших разрядов выхода формирователя дополнительного кода подключена к группе входов

5 задания величины сдвига узла сдвига контрольных разрядов, вход задания типа сдвига которого соединен с выходом формирователя кода маски.

0 2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что узел формирования сигналов четности содержит йруппу из N/K формирователей сигнала четности и формирователь кода маски, причем информационный вход

5 формирователя кода маски является входом задания величины сдвига узла, каждый 1-й разряд первого информационного входа J- го формирователя сигнала четности

группы (1 I K-1, t j -Л соединен с

К(И) разрядом информационного входа узла, первый и второй входы контрольного разряда первого формирователя сигнала четности группы являются соответственно 5 первым и вторым входами коррекции четного разряда каждого р-го формирователя сигнала четности группы (2 р -) подключен

к р-1-му входу контрольных разрядов груп- 0 пы узла, второй вход контрольного разряда каждого р-го формирователя сигнала четности группы подключен к р-2-му входу контрольных разрядов группы узла, каждый i-й разряд второго информационного входа 5 первого формирователя сигнала четности группы подключен к i+N- К-1-му разряду информационного входа узла, каждый 1-й разряд второго информационного входа р- го формирователя сигнала четности группы соединен с К(р-2) разрядом информационного входа узла, входы блокировки сдвига формирователей сигнала сдвига группы подключены к входу блокировки сдвига узла, группы младших и старших разрядов выхода формирователя кода маски соединены соответственно с входами задания величины сдвига влево и вправо каждого формирователя сигнала четности группы, первый и второй разряды входа задания признака циклического сдвига первого формирователя сигнала, четности группы подключены соответственно к первому и второму разрядам входа задания типа сдвига узла.

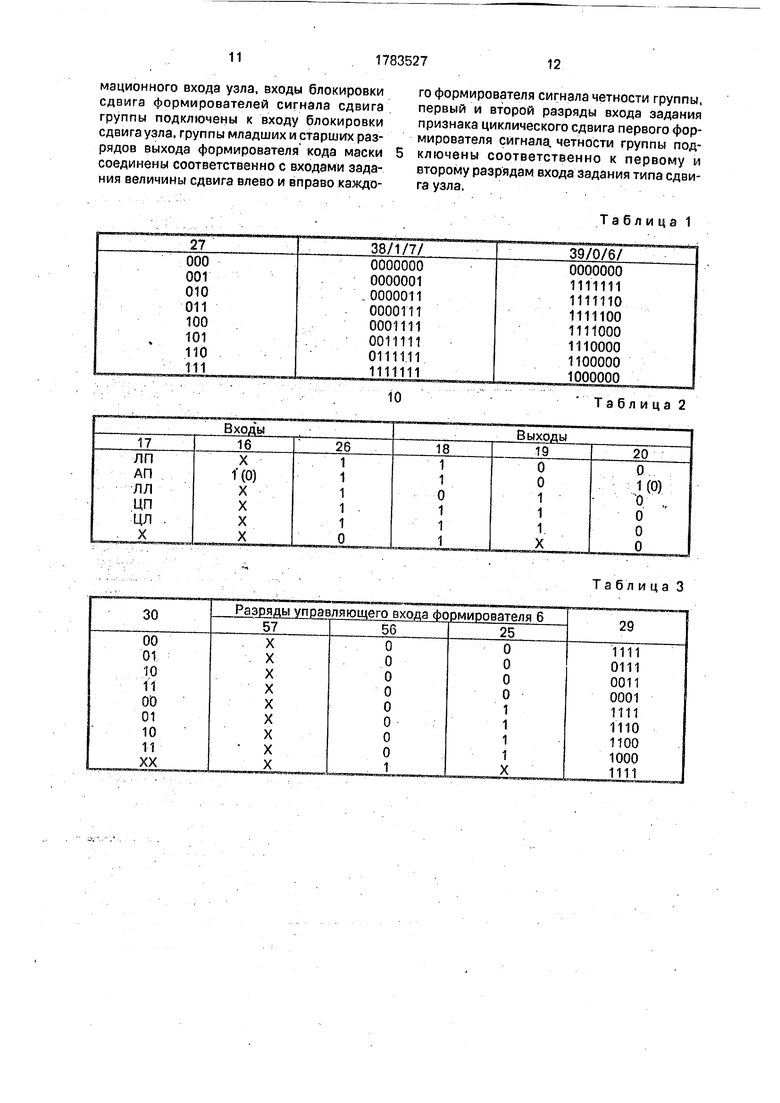

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

| Устройство для сдвига операндов | 1988 |

|

SU1633391A1 |

10

Таблица 2

Таблица 3

24

1783527

35 23

Авторы

Даты

1992-12-23—Публикация

1989-10-11—Подача