Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах обработки сигналов высокой производительности для вычисления двумерного дискретного преобразования Фурье.

Известно устройство для вычисления двумерного дискретного преобразования Фурье, содержащее Р вычислительных модулей, где Р порядок входной матрицы, и блок ввода [1]

Недостатками этого устройства являются большие аппаратурные затраты и невозможность вычисления двумерного дискретного преобразования Фурье для случая, когда размерность входной матрицы больше числа Р.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее три блока ввода, Р вычислительных модулей первого типа (Р порядок входной матрицы) и Р вычислительных модулей второго типа [2]

Недостатками данного устройства являются большие аппаратурные затраты и невозможность вычисления двумерного дискретного преобразования Фурье в случае, если размерность входной матрицы превышает число вычислительных модулей в устройстве.

Цель изобретения сокращение аппаратурных затрат.

Поставленная цель достигается тем, что устройство для вычисления двумерного дискретного преобразования Фурье содержит m вычислительных модулей 7, где m фиксированное число (m ≅ T, T размерность результирующей матрицы Y[I, T] ) n регистров 8, где n P(Q+I)-2m (P и Q размерности входной матрицы Х[P, Q] ), три группы триггеров 9 11, группу элементов ИЛИ 12, три элемента ИЛИ 13 15 и выход 16, причем первый 1 информационный вход устройства подключен к первым входам группы элементов ИЛИ 12, выход которого подключен к первому информационному входу первого вычислительного модуля 71, второй 2 информационный вход устройства подключен ко второму информационному входу первого вычислительного модуля 71, первый 3, второй 4 и третий 5 управляющие входы устройства подключены к первым входам соответственно первого 13, второго 14 и третьего 15 элементов ИЛИ, выходы которых подключены соответственно к первому, второму и третьему управляющим входам первого вычислительного модуля 71, первый и второй информационные выходы, первый, второй и третий управляющие выходы i-го вычислительного модуля 7 (i  ) подключены соответственно к первому и второму информационным входам, первому, второму и третьему управляющим входам (i+1)-го вычислительного модуля 7, первый информационный выход 7m-го вычислительного модуля подключен к информационному входу 8n-го регистра, информационный вход 8i-го регистра (i

) подключены соответственно к первому и второму информационным входам, первому, второму и третьему управляющим входам (i+1)-го вычислительного модуля 7, первый информационный выход 7m-го вычислительного модуля подключен к информационному входу 8n-го регистра, информационный вход 8i-го регистра (i  ) подключен к выходу 8i+1-го регистра, выход первого 81 регистра подключен ко вторым входам группы элементов ИЛИ 12, второй информационный выход 7m-го вычислительного модуля подключен к выходу 16 устройства, первый, второй и третий управляющие выходы 7m-го вычислительного модуля подключены к информационным входам n-х триггеров соответственно первой 9, второй 10 и третьей 11 групп, информационный вход i-го триггера (i

) подключен к выходу 8i+1-го регистра, выход первого 81 регистра подключен ко вторым входам группы элементов ИЛИ 12, второй информационный выход 7m-го вычислительного модуля подключен к выходу 16 устройства, первый, второй и третий управляющие выходы 7m-го вычислительного модуля подключены к информационным входам n-х триггеров соответственно первой 9, второй 10 и третьей 11 групп, информационный вход i-го триггера (i  ) j-й группы (j

) j-й группы (j  ) подключен к выходу (i+1)-го триггера j-й группы, выходы первых триггеров первой 9, второй 10 и третьей 11 групп подключены соответственно к вторым входам первого 13, второго 14 и третьего 15 элементов ИЛИ, тактовый вход 6 устройства подключен к синхровходам всех вычислительных модулей, регистров и триггеров, при этом каждый вычислительный модуль 7 содержит тринадцать групп элементов И 23-35, семь элементов И 36 42, шесть групп элементов ИЛИ 43-48, семь элементов ИЛИ 49 55, пять регистров 56-60, группу регистров 61, двенадцать триггеров 62 73, умножитель 74 и сумматор 75, причем первый 17 информационный вход вычислительного модуля подключен к информационному входу первого 56 регистра, выход которого подключен к первым входам первой 24, второй 27 и третьей 28 групп элементов И и информационному входу второго 57 регистра, выход которого подключен к первому 76 информационному выходу вычислительного модуля, второй 18 информационный вход которого подключен к информационному входу третьего 58 регистра, выход которого подключен к первым входам четвертой 23 и пятой 25 групп элементов И, вторые входы пятой 25 группы элементов И подключены к выходу первого 50 элемента И, а выход к первым входам третьей 44 группы элементов ИЛИ, выход которого подключен ко второму информационному выходу вычислительного модуля, выход четвертой 23 группы элементов И подключен к первым входам первой 43 группы элементов ИЛИ, вторые входы которой подключены к выходу первой 24 группы элементов И, а выход к информационному входу четвертого 59 регистра, синхровход которого подключен к выходу первого 36 элемента И, первый вход которого подключен к выходу второго 49 элемента ИЛИ, выход четвертого 59 регистра подключен к первому входу умножителя 74, выход которого подключен к первому входу сумматора 75, второй вход которого подключен к выходу второй 46 группы элементов ИЛИ, а выход к первым входам шестой 29, седьмой 32 и восьмой 26 групп элементов И, выход которой подключен ко вторым входам третьей 44 группы элементов ИЛИ, выход третьего 55 элемента ИЛИ подключен к первым входам девятой 34 группы элементов И, выходы девятой 34 и десятой 33 групп элементов И подключены соответственно к первому и второму входам четвертой 47 группы элементов ИЛИ, выход которой подключен ко второму входу умножителя 74, выход третьей 28 группы элементов И подключен к первым входам второй 46 группы элементов ИЛИ, вторые входы которой подключены к выходу одиннадцатой 31 группы элементов И, второй вход которой подключен к выходу четвертого 54 элемента ИЛИ, выход пятого 51 элемента ИЛИ подключен ко вторым входам второй 27 группы элементов И, выход которой подключен к первым входам пятой группы 45 элементов ИЛИ, вторые входы которой подключены к выходу элементов И шестой 29 группы, а выход к информационному входу первого регистра 571группы, выход 57i-го регистра группы (i

) подключен к выходу (i+1)-го триггера j-й группы, выходы первых триггеров первой 9, второй 10 и третьей 11 групп подключены соответственно к вторым входам первого 13, второго 14 и третьего 15 элементов ИЛИ, тактовый вход 6 устройства подключен к синхровходам всех вычислительных модулей, регистров и триггеров, при этом каждый вычислительный модуль 7 содержит тринадцать групп элементов И 23-35, семь элементов И 36 42, шесть групп элементов ИЛИ 43-48, семь элементов ИЛИ 49 55, пять регистров 56-60, группу регистров 61, двенадцать триггеров 62 73, умножитель 74 и сумматор 75, причем первый 17 информационный вход вычислительного модуля подключен к информационному входу первого 56 регистра, выход которого подключен к первым входам первой 24, второй 27 и третьей 28 групп элементов И и информационному входу второго 57 регистра, выход которого подключен к первому 76 информационному выходу вычислительного модуля, второй 18 информационный вход которого подключен к информационному входу третьего 58 регистра, выход которого подключен к первым входам четвертой 23 и пятой 25 групп элементов И, вторые входы пятой 25 группы элементов И подключены к выходу первого 50 элемента И, а выход к первым входам третьей 44 группы элементов ИЛИ, выход которого подключен ко второму информационному выходу вычислительного модуля, выход четвертой 23 группы элементов И подключен к первым входам первой 43 группы элементов ИЛИ, вторые входы которой подключены к выходу первой 24 группы элементов И, а выход к информационному входу четвертого 59 регистра, синхровход которого подключен к выходу первого 36 элемента И, первый вход которого подключен к выходу второго 49 элемента ИЛИ, выход четвертого 59 регистра подключен к первому входу умножителя 74, выход которого подключен к первому входу сумматора 75, второй вход которого подключен к выходу второй 46 группы элементов ИЛИ, а выход к первым входам шестой 29, седьмой 32 и восьмой 26 групп элементов И, выход которой подключен ко вторым входам третьей 44 группы элементов ИЛИ, выход третьего 55 элемента ИЛИ подключен к первым входам девятой 34 группы элементов И, выходы девятой 34 и десятой 33 групп элементов И подключены соответственно к первому и второму входам четвертой 47 группы элементов ИЛИ, выход которой подключен ко второму входу умножителя 74, выход третьей 28 группы элементов И подключен к первым входам второй 46 группы элементов ИЛИ, вторые входы которой подключены к выходу одиннадцатой 31 группы элементов И, второй вход которой подключен к выходу четвертого 54 элемента ИЛИ, выход пятого 51 элемента ИЛИ подключен ко вторым входам второй 27 группы элементов И, выход которой подключен к первым входам пятой группы 45 элементов ИЛИ, вторые входы которой подключены к выходу элементов И шестой 29 группы, а выход к информационному входу первого регистра 571группы, выход 57i-го регистра группы (i  ) подключен к информационному входу 57i+1-го регистра группы, выход 57Р-го регистра группы подключен к первым входам десятой 33, одиннадцатой 31, двенадцатой 35 и тринадцатой 30 групп элементов И, вторые входы группы И 30 подключены к выходу шестого 52 элемента ИЛИ, а выход к третьим входам пятой 45 группы элементов ИЛИ, выход седьмого 53 элемента ИЛИ подключен ко вторым входам элементов И седьмой 32 группы, выходы которых подключены к первым входам элементов ИЛИ шестой 48 группы, вторые входы которой подключены к выходам элементов И двенадцатой 35 группы, а выходы к информационному входу пятого 60 регистра, выход которого подключен ко вторым входам элементов И девятой 34 группы, первый 19 управляющий вход вычислительного модуля подключен к инверсным первым входам второго 37, третьего 38 и четвертого 39 элементов И, первым входам пятого 40, шестого 41 и седьмого 42 элементов И и информационному входу первого 68 триггера, выход которого подключен к информационному входу второго 69 триггера, выход которого подключен к первому 78 управляющему выходу вычислительного модуля, второй 20 управляющий вход которого подключен к инверсным вторым входам второго 37, четвертого 39, пятого 40 и шестого 41 элементов И, вторым входам третьего 38 и седьмого 42 элементов И и информационному входу третьего 70 триггера, выход которого подключен к информационному входу четвертого 71 триггера, выход которого подключен к второму 79 управляющему выходу вычислительного модуля, третий 21 управляющий вход которого подключен к инверсным третьим входам третьего 38, четвертого 39, шестого 41 и седьмого 42 элементов И, третьим входам второго 37 и пятого 40 элементов И и информационному входу пятого 72 триггера, выход которого подключен к информационному входу шестого 73 триггера, выход которого подключен к третьему 80 управляющему выходу вычислительного модуля, выходы элементов И со второго 37 по седьмой 42 подключены соответственно к информационным входам триггеров с седьмого 62 по двенадцатый 67, выход седьмого 62 триггера подключен к первым входам второго 49 и пятого 51 элементов ИЛИ и вторым входам элементов И четвертой 23 группы, выход восьмого 63 триггера подключен к первому входу первого 50 и второму входу пятого 51 элементов ИЛИ, выход девятого 64 триггера подключен ко вторым входам элементов И третьей 28, шестой 29 и десятой 33 групп, выход десятого 65 триггера подключен ко вторым входам элементов И первой 24 и двенадцатой 35 групп, второму входу второго 49 и первому входу шестого 52 элементов ИЛИ, выход одиннадцатого 66 триггера подключен к первым входам третьего 55, четвертого 54 и седьмого 53 элементов ИЛИ и вторым входам первого 50 и шестого 52 элементов ИЛИ, выход двенадцатого 67 триггера подключен к вторым входам восьмой 26 группы элементов И, вторым входам третьего 55, четвертого 54 и седьмого 53 элементов ИЛИ и третьему входу шестого 52 элемента ИЛИ, синхровход 22 вычислительного модуля подключен к синхровходам первого 56, второго 57, третьего 58 и пятого 50 регистров, регистров группы 61, триггеров 62-73 и второму входу первого 36 элемента И.

) подключен к информационному входу 57i+1-го регистра группы, выход 57Р-го регистра группы подключен к первым входам десятой 33, одиннадцатой 31, двенадцатой 35 и тринадцатой 30 групп элементов И, вторые входы группы И 30 подключены к выходу шестого 52 элемента ИЛИ, а выход к третьим входам пятой 45 группы элементов ИЛИ, выход седьмого 53 элемента ИЛИ подключен ко вторым входам элементов И седьмой 32 группы, выходы которых подключены к первым входам элементов ИЛИ шестой 48 группы, вторые входы которой подключены к выходам элементов И двенадцатой 35 группы, а выходы к информационному входу пятого 60 регистра, выход которого подключен ко вторым входам элементов И девятой 34 группы, первый 19 управляющий вход вычислительного модуля подключен к инверсным первым входам второго 37, третьего 38 и четвертого 39 элементов И, первым входам пятого 40, шестого 41 и седьмого 42 элементов И и информационному входу первого 68 триггера, выход которого подключен к информационному входу второго 69 триггера, выход которого подключен к первому 78 управляющему выходу вычислительного модуля, второй 20 управляющий вход которого подключен к инверсным вторым входам второго 37, четвертого 39, пятого 40 и шестого 41 элементов И, вторым входам третьего 38 и седьмого 42 элементов И и информационному входу третьего 70 триггера, выход которого подключен к информационному входу четвертого 71 триггера, выход которого подключен к второму 79 управляющему выходу вычислительного модуля, третий 21 управляющий вход которого подключен к инверсным третьим входам третьего 38, четвертого 39, шестого 41 и седьмого 42 элементов И, третьим входам второго 37 и пятого 40 элементов И и информационному входу пятого 72 триггера, выход которого подключен к информационному входу шестого 73 триггера, выход которого подключен к третьему 80 управляющему выходу вычислительного модуля, выходы элементов И со второго 37 по седьмой 42 подключены соответственно к информационным входам триггеров с седьмого 62 по двенадцатый 67, выход седьмого 62 триггера подключен к первым входам второго 49 и пятого 51 элементов ИЛИ и вторым входам элементов И четвертой 23 группы, выход восьмого 63 триггера подключен к первому входу первого 50 и второму входу пятого 51 элементов ИЛИ, выход девятого 64 триггера подключен ко вторым входам элементов И третьей 28, шестой 29 и десятой 33 групп, выход десятого 65 триггера подключен ко вторым входам элементов И первой 24 и двенадцатой 35 групп, второму входу второго 49 и первому входу шестого 52 элементов ИЛИ, выход одиннадцатого 66 триггера подключен к первым входам третьего 55, четвертого 54 и седьмого 53 элементов ИЛИ и вторым входам первого 50 и шестого 52 элементов ИЛИ, выход двенадцатого 67 триггера подключен к вторым входам восьмой 26 группы элементов И, вторым входам третьего 55, четвертого 54 и седьмого 53 элементов ИЛИ и третьему входу шестого 52 элемента ИЛИ, синхровход 22 вычислительного модуля подключен к синхровходам первого 56, второго 57, третьего 58 и пятого 50 регистров, регистров группы 61, триггеров 62-73 и второму входу первого 36 элемента И.

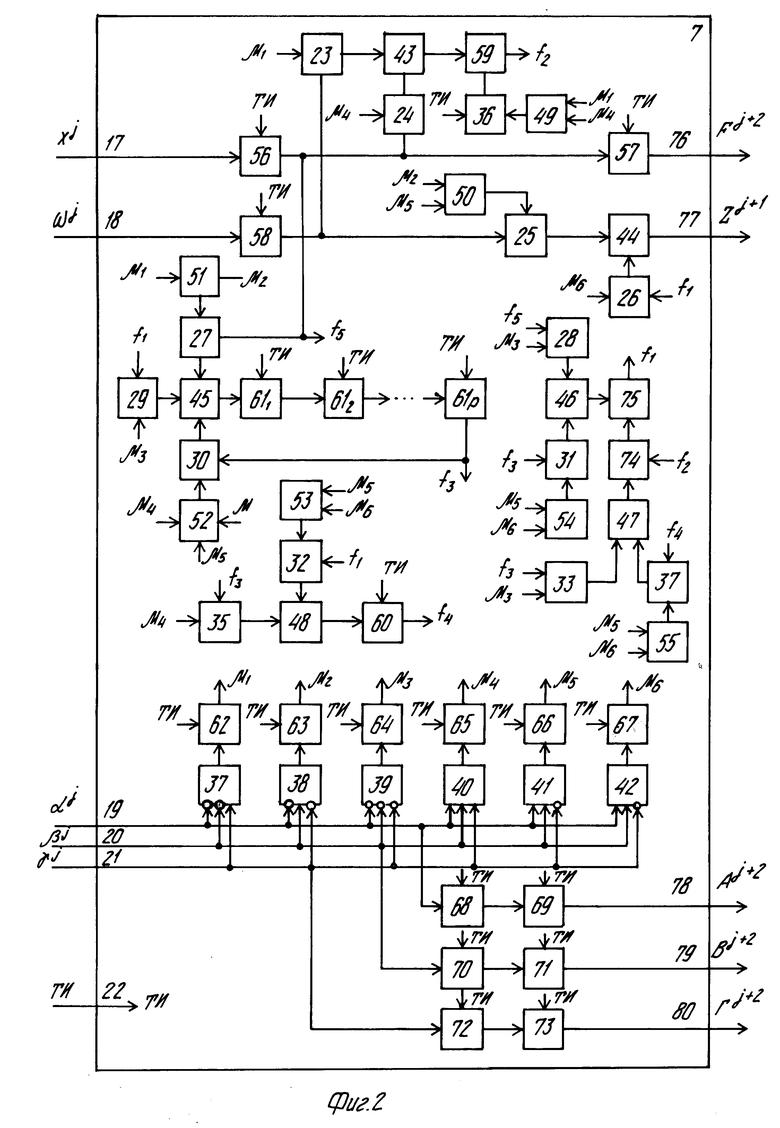

На фиг. 1 представлена структурная схема устройства для вычисления двумерного дискретного преобразования Фурье; на фиг. 2 структурная схема вычислительного модуля.

Устройство для вычисления двумерного дискретного преобразования Фурье (фиг. 1) содержит первый 1 и второй 2 информационные входы, первый 3, второй 4 и третий 5 управляющие входы, тактовый вход 6, вычислительные модули 7i (i  ), регистры 8i (i

), регистры 8i (i  ), первую 9i, вторую 10i и третью 11i (i

), первую 9i, вторую 10i и третью 11i (i  ) группы триггеров, группу элементов ИЛИ 12, элементы ИЛИ 13-15 и выход 16.

) группы триггеров, группу элементов ИЛИ 12, элементы ИЛИ 13-15 и выход 16.

Вычислительный модуль 7 (фиг. 2) содержит первый 17 и второй 18 информационные входы, первый 19, второй 20 и третий 21 управляющие входы, синхровход 22, группы элементов И 23 35, элементы И 36-42, группы элементов ИЛИ 43-48, элементы ИЛИ 49-55, первый 56, второй 57, третий 58, четвертый 59 и пятый 60 регистры, группы регистров 61i (i  ), триггеры 62-73, умножитель 74, сумматор 75, первый 76 и второй 77 информационные выходы, первый 78, второй 79 и третий 80 управляющие выходы.

), триггеры 62-73, умножитель 74, сумматор 75, первый 76 и второй 77 информационные выходы, первый 78, второй 79 и третий 80 управляющие выходы.

В основу работы устройства положен алгоритм вычисления двумерного дискретного преобразования Фурье в виде выражений:

Yij=

xpq·ω

xpq·ω , j

, j  ,

,

bjp= xpq·ω

xpq·ω , p

, p  ,

,

Yij= bjp·ω

bjp·ω

j  , p

, p  , q

, q  :

:

b(j,P,0) xPQ-1,

b(j,P,q) b(j,P,q-1) ˙ωTj + xpQ-1-q,

bjP b(j,p,Q-1);

i  , j

, j  , p

, p  :

:

Y(i,j,0) bjP-1;

Y(i,j,P) Y(i,j,P-1) ˙ωIi + bjP-1-P,

Yij Y(i,j,P-1).

Для случая, когда m фиксированное число (2 ≅m≅ T), значение Tm T/m целое число. Если Tm не целое число, то в качестве T берется m= T/m

T/m (

(  ближайшее сверху целое). При этом матрицуbjP} необходимо дополнить строками, а матрицу Yij} столбцами. Вектор (ωT0, ωT1,ωTT-1) дополняется до m=

ближайшее сверху целое). При этом матрицуbjP} необходимо дополнить строками, а матрицу Yij} столбцами. Вектор (ωT0, ωT1,ωTT-1) дополняется до m= T/m

T/m элементов нулями. Дополнительные столбцы матрицыYij} при выводе не принимаются во внимание.

элементов нулями. Дополнительные столбцы матрицыYij} при выводе не принимаются во внимание.

Вычислительный модуль 7 обладает возможностью реализации следующих функций:

Aj+2 αj

Bj+2 βj

Γj+2= γj где Aj+2, Bj+2 и Γj+2 значения управляющих сигналов соответственно на первой 78, втором 79 и третьем 80 управляющих выходах вычислительного модуля на (j+2)-м такте,

αj, βj и γj значения управляющих сигналов соответственно на первом 19, втором 20 и третьем 21 управляющих входах вычислительного модуля на j-м такте,

Fj+2 xj, где Fj+2 значение на первом 76 информационном выходе вычислительного модуля на (j+2)-м такте,

хj значение на первом 17 информационном входе вычислительного модуля на j-м такте,

Zj+1=

где

где

aj=

bj=

f

f ,

, и

и 1,

1,

f

f5j xj-1, где Zj+1 значение на втором 77 информационном входе вычислительного модуля на (j+1)-м такте,

ωj значение на втором 18 информационном входе вычислительного модуля

μ1j=(αj-1, βj-1, γj-1) (0, 0, 1),

μ2j=(αj-1, βj-1, γj-1) (0, 1, 0),

μ3j=(αj-1, βj-1, γj-1) (0, 0, 0),

μ4j=(αj-1, βj-1, γj-1) (1, 0, 1),

μ5j=(αj-1, βj-1, γj-1) (1, 0, 0),

μ6j=(αj-1, βj-1, γj-1) (1, 1, 0).

Рассмотрим работу устройства для случая I 2, T 6, P 3 и Q 3:

j  , p

, p  :

:

b(j,P,0) xP2,

q 1:

b(j,P,1) b(j,P,0)˙ωTj + xP1,

q 2:

b(j,P,2) b(j,P,1) ˙ωTj xP0,

bjP b(j,P,2);

i  , j

, j  :

:

Y(i,j,0) bj2,

P 1:

Y(i,j,1) Y(i,j,0) ˙ωIi + bj1,

P 2:

Y(i,j,2) Y(i,j,1) ˙ωIi + bj0,

Yij Y(i,j,2).

Входной и выходной потоки данных формируются на основании следующих выражений.

На вход подаются элементы х и ωIi в моменты времени:

t P -1 p + P(Q 1 q),

P -1 p + P(Q 1 q),

p  , q

, q  ,

,

t ωIi= P(I + Q i 1).

На вход 2 подаются элементы ωTδ+(γ-1)m в моменты времени

tωT ( γ- 1)P(Q + I) + δ,

0 ≅δ≅ m-1, 1≅γ≅ Tm.

На входы 3, 4 и 5 подается комбинация управляющих сигналов τip=(α,β,γ) i  p

p  представляемая матрицей вида:

представляемая матрицей вида:

τip=

в моменты времени

в моменты времени

t Pi + p

Pi + p

На выходе 16 формируются элементы Yi,δ+(γ-1)m в моменты времени

t

=γP(Q + I) + m + δ Pi 1, 0 ≅δ≅ m-1, 1≅γ≅ Tm.

=γP(Q + I) + m + δ Pi 1, 0 ≅δ≅ m-1, 1≅γ≅ Tm.

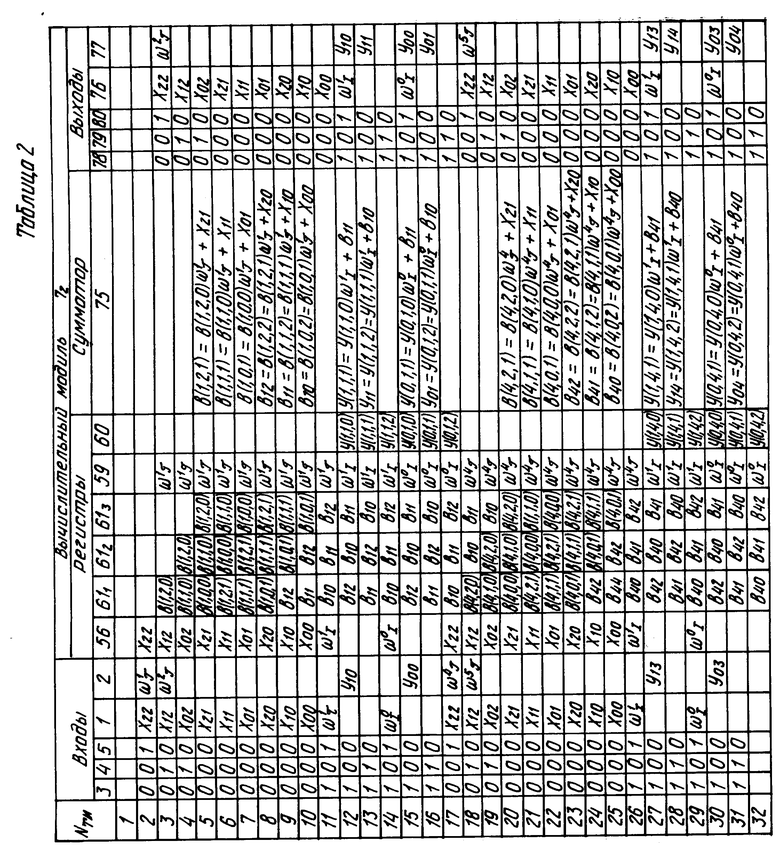

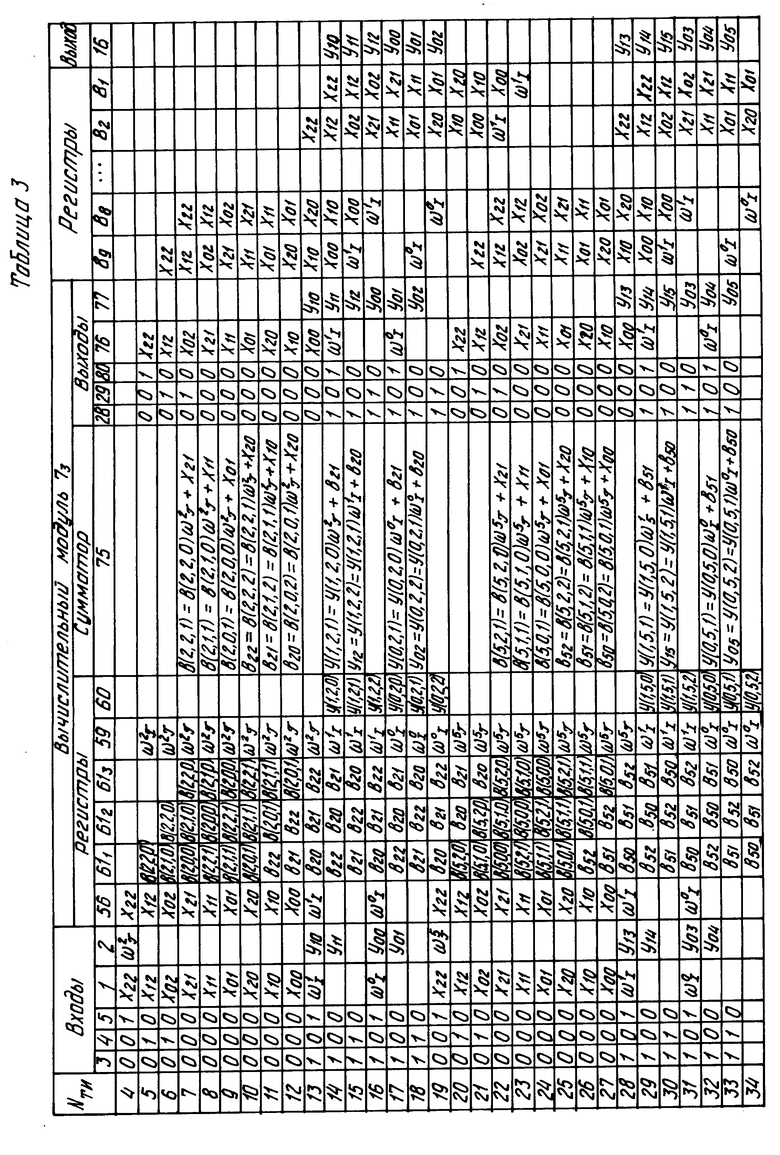

Для I 2, T 6, P 3 и Q 3 организация входного и выходного потоков данных, состояния регистров и результаты вычислений на выходе умножителя в вычислительных модулях 70, 71 и 72 приведены в табл, 1, 2 и 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1994 |

|

RU2116667C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ НАИМЕНЬШИХ КВАДРАТОВ | 1993 |

|

RU2049354C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРЕХМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1993 |

|

RU2069011C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024932C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЧЕТЫРЕХМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1993 |

|

RU2069010C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1991 |

|

RU2012049C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N X N)-МАТРИЦЫ | 1992 |

|

RU2012050C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024933C1 |

| УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ N X N МАТРИЦ | 1990 |

|

RU2037199C1 |

| Устройство для вычисления свертки | 1989 |

|

SU1679502A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах обработки сигналов высокой производительности для вычисления двумерного дискретного преобразования Фурье. Цель изобретения сокращение аппаратных затрат. Цель изобретения достигается тем, что устройство содержит m вычислительных модулей, m фиксированное число, m ≅ J (J - разномерность результирующей матрицы Y [I, J]), n регистров, где n P(Q + I) 2m (P и Q разномерность входной матрицы X [P, Q]), три группы триггеров 91-9n, 101-10n, 111-11n группу элементов ИЛИ 12 и три элемента ИЛИ 13, 14, 15, причем вычислительный модуль содержит тринадцать групп элементов И, семь элементов И, шесть групп элементов ИЛИ, семь элементов ИЛИ, пять регистров, группу регистров, двенадцать триггеров, умножитель и сумматор. 1 з. п. ф-лы, 2 ил. 3 табл.

) подключены соответственно к первому и второму информационным входам, первому, второму и третьему управляющим входам (i + 1)-го вычислительного модуля, отличающееся тем, что в него введены n регистров, где n P(Q + 1) 2m, P и Q - размерность входной матрицы X[P, Q] три группы по n триггеров, группа элементов ИЛИ и три элемента ИЛИ, причем первый информационный вход устройства подключен к первым входам элементов ИЛИ группы, выходы которых подключены к первому информационному входу первого вычислительного модуля, второй информационный вход устройства подключен к второму информационному входу первого вычислительного модуля, первый, второй и третий управляющие входы устройства подключены к первым входам соответственно первого, второго и третьего элементов ИЛИ, выходы которых подключены соответственно к первому, второму и третьему управляющим входам первого вычислительного модуля, первый информационный выход m-го вычислительного модуля подключен к информационному входу n-го регистра, информационный вход i-го регистра подключен к выходу (i + 1)-го регистра, выход первого регистра подключен к вторым входам элементов ИЛИ группы, второй информационный выход m-го вычислительного модуля подключен к выходу устройства, первый, второй и третий управляющие выходы m-го вычислительного модуля подключены к информационным входам n триггеров соответственно первой, второй и третьей групп, информационный вход k-го триггера

) подключены соответственно к первому и второму информационным входам, первому, второму и третьему управляющим входам (i + 1)-го вычислительного модуля, отличающееся тем, что в него введены n регистров, где n P(Q + 1) 2m, P и Q - размерность входной матрицы X[P, Q] три группы по n триггеров, группа элементов ИЛИ и три элемента ИЛИ, причем первый информационный вход устройства подключен к первым входам элементов ИЛИ группы, выходы которых подключены к первому информационному входу первого вычислительного модуля, второй информационный вход устройства подключен к второму информационному входу первого вычислительного модуля, первый, второй и третий управляющие входы устройства подключены к первым входам соответственно первого, второго и третьего элементов ИЛИ, выходы которых подключены соответственно к первому, второму и третьему управляющим входам первого вычислительного модуля, первый информационный выход m-го вычислительного модуля подключен к информационному входу n-го регистра, информационный вход i-го регистра подключен к выходу (i + 1)-го регистра, выход первого регистра подключен к вторым входам элементов ИЛИ группы, второй информационный выход m-го вычислительного модуля подключен к выходу устройства, первый, второй и третий управляющие выходы m-го вычислительного модуля подключены к информационным входам n триггеров соответственно первой, второй и третьей групп, информационный вход k-го триггера  подключен к выходу (k + 1)-го триггера j-й группы, выходы первых триггеров первой, второй и третьей групп подключены к вторым входам первого, второго и третьего элементов ИЛИ соответственно, тактовый вход устройства подключен к тактовым входам триггеров первой, второй и третьей групп и n регистров.

подключен к выходу (k + 1)-го триггера j-й группы, выходы первых триггеров первой, второй и третьей групп подключены к вторым входам первого, второго и третьего элементов ИЛИ соответственно, тактовый вход устройства подключен к тактовым входам триггеров первой, второй и третьей групп и n регистров. подключен к информационному входу (i + 1)-го регистра группы, выход P-го регистра группы подключен к первым входам элементов И десятой, одиннадцатой, двенадцатой и тринадцатой групп, вторые входы которых подключены к выходу шестого элемента ИЛИ, а выход к третьим входам элементов ИЛИ пятой группы, выход седьмого элемента ИЛИ подключен к вторым входам элементов И седьмой группы, выходы которых подключены к первым входам элементов ИЛИ шестой группы, вторые входы которых подключены к выходу элементов И двенадцатой группы, а выход к информационному входу пятого регистра, выход которого подключен к вторым входам элементов И девятой группы, первый управляющий вход вычислительного модуля подключен к инверсным первым входам второго, третьего и четвертого элементов И, первым входам пятого, шестого и седьмого элементов И и информационному входу первого триггера, выход которого подключен к информационному входу второго триггера, выход которого подключен к первому управляющему выходу вычислительного модуля, второй управляющий вход которого подключен к инверсным вторым входам второго, четвертого, пятого и шестого элементов И, вторым входам третьего и седьмого элементов И и информационному входу третьего триггера, выход которого подключен к информационному входу четвертого триггера, выход которого подключен к второму управляющему выходу вычислительного модуля, третий управляющий вход которого подключен к инверсным третьим входам третьего, четвертого, шестого и седьмого элементов И, третьим входам второго и пятого элементов И и информационному входу пятого триггера, выход которого подключен к информационному входу шестого триггера, выход которого подключен к третьему управляющему выходу вычислительного модуля, выходы с второго по седьмой элементов И подключены соответственно к информационным входам триггеров с седьмого по двенадцатый, выход седьмого триггера подключен к первым входам второго и пятого элементов ИЛИ и вторым входам элементов И четвертой группы, выход восьмого триггера подключен к первому входу первого и второму входу пятого элементов ИЛИ, выход девятого триггера подключен к вторым входам элементов И третьей, шестой и десятой групп, выход десятого триггера подключен к вторым входам элементов И первой и двенадцатой групп, второму входу второго и первому входу шестого элементов ИЛИ, выход одиннадцатого триггера подключен к первым входам третьего, четвертого и седьмого элементов ИЛИ и вторым входам первого и шестого элементов ИЛИ, выход двенадцатого триггера подключен к вторым входам элементов И восьмой группы, вторым входам третьего, четвертого и седьмого элементов ИЛИ и третьему входу шестого элемента ИЛИ, синхровход вычислительного модуля подключен к синхровходам первого, второго, третьего и пятого регистров, регистров группы, с первого по двенадцатый триггеров и второму входу первого элемента И.

подключен к информационному входу (i + 1)-го регистра группы, выход P-го регистра группы подключен к первым входам элементов И десятой, одиннадцатой, двенадцатой и тринадцатой групп, вторые входы которых подключены к выходу шестого элемента ИЛИ, а выход к третьим входам элементов ИЛИ пятой группы, выход седьмого элемента ИЛИ подключен к вторым входам элементов И седьмой группы, выходы которых подключены к первым входам элементов ИЛИ шестой группы, вторые входы которых подключены к выходу элементов И двенадцатой группы, а выход к информационному входу пятого регистра, выход которого подключен к вторым входам элементов И девятой группы, первый управляющий вход вычислительного модуля подключен к инверсным первым входам второго, третьего и четвертого элементов И, первым входам пятого, шестого и седьмого элементов И и информационному входу первого триггера, выход которого подключен к информационному входу второго триггера, выход которого подключен к первому управляющему выходу вычислительного модуля, второй управляющий вход которого подключен к инверсным вторым входам второго, четвертого, пятого и шестого элементов И, вторым входам третьего и седьмого элементов И и информационному входу третьего триггера, выход которого подключен к информационному входу четвертого триггера, выход которого подключен к второму управляющему выходу вычислительного модуля, третий управляющий вход которого подключен к инверсным третьим входам третьего, четвертого, шестого и седьмого элементов И, третьим входам второго и пятого элементов И и информационному входу пятого триггера, выход которого подключен к информационному входу шестого триггера, выход которого подключен к третьему управляющему выходу вычислительного модуля, выходы с второго по седьмой элементов И подключены соответственно к информационным входам триггеров с седьмого по двенадцатый, выход седьмого триггера подключен к первым входам второго и пятого элементов ИЛИ и вторым входам элементов И четвертой группы, выход восьмого триггера подключен к первому входу первого и второму входу пятого элементов ИЛИ, выход девятого триггера подключен к вторым входам элементов И третьей, шестой и десятой групп, выход десятого триггера подключен к вторым входам элементов И первой и двенадцатой групп, второму входу второго и первому входу шестого элементов ИЛИ, выход одиннадцатого триггера подключен к первым входам третьего, четвертого и седьмого элементов ИЛИ и вторым входам первого и шестого элементов ИЛИ, выход двенадцатого триггера подключен к вторым входам элементов И восьмой группы, вторым входам третьего, четвертого и седьмого элементов ИЛИ и третьему входу шестого элемента ИЛИ, синхровход вычислительного модуля подключен к синхровходам первого, второго, третьего и пятого регистров, регистров группы, с первого по двенадцатый триггеров и второму входу первого элемента И.

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1990 |

|

SU1751778A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип) | |||

Авторы

Даты

1995-11-27—Публикация

1994-03-15—Подача