Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных специализированных вычислительных системах для решения задачи наименьших квадратов.

Известно устройство для решения задачи наименьших квадратов путем решения системы линейных алгебраических уравнений, содержащее К х N вычислительных модулей, где К число уравнений, N число неизвестных [1]

Недостатками этого устройства являются большой объем оборудования и невозможность его реализации на основе сверхбольших интегральных схем за счет большого числа портов ввода и вывода.

Наиболее близким по технической сущности к предложенному является устройство, решающее задачу наименьших квадратов и содержащее N вычислительных модулей, где N число неизвестных системы линейных алгебраических уравнений [2]

Недостатком такого устройства является низкое быстродействие; время решения системы линейных алгебраических уравнений равно ((N + M)(K + N) + N 1) тактов, где К число уравнений, М число столбцов в правой части системы линейных алгебраических уравнений.

Предложенное для решения задачи наименьших квадратов содержит N вычислительных модулей, где N число неизвестных системы линейных алгебраических уравнений, причем информационный вход 1, первый 21, второй 22, третий 23 и четвертый 3 управляющие входы устройства подключены соответственно к информационному входу, первому, второму, третьему и четвертому управляющим входам первого вычислительного модуля 51, информационный выход, первый, второй, третий и четвертый управляющие выходы 5i-го вычислительного модуля (i  ) подключены соответственно к информационному входу, первому, второму, третьему и четвертому управляющим входам 5 i+1-го вычислительного модуля, информационный выход 5N-го вычислительного модуля подключен к выходу устройства, тактовый вход 4 которого подключен к тактовым входам всех вычислительных модулей, при этом вычислительный модуль содержит узел 13 вычисления величины из квадратного корня суммы квадратов двух чисел, узел 14 вычисления обратной величины числа, шесть умножителей 15 20, сумматор 21, вычитатель 22, два регистра 23 и 24, две группы регистров 25 и 26, блок управления 27, двадцать три группы элементов И 28 50, элемент И 51, девять групп элементов ИЛИ 52-60, четыре элемента ИЛИ 61 64, причем информационный вход 7 вычислительного модуля подключен к информационному входу первого 23 регистра, выход которого подключен к первым входам первого 15 и второго 16 умножителей, первой 29, второй 46 и третьей 49 групп элементов И и к первому входу узла 13 вычисления величины из квадратного корня суммы квадратов двух чисел, второй вход которого подключен к выходу второго 24 регистра, а выход к первым входам элементов И 31 четвертой группы, выход которых подключен к первым входам элементов ИЛИ 54 первой группы, вторые входы которых подключены к соответствующим выходам элементов И 30 пятой группы, а выходы к входу узла 14 вычисления обратной величины числа, выход которого подключен к первым входам элементов И шестой 33, седьмой 34, восьмой 37 и девятой 40 групп, выход второго регистра 24 подключен к первым входам второго 16, третьего 19 умножителей, элементов И пятой 30, десятой 48 и одиннадцатой 50 групп, первый, второй, третий и четвертый входы блока управления подключены соответственно к первому 8, второму 9, третьему 10 и четвертому 11 входам вычислительного модуля, а первый, второй, третий и четвертый выходы соответственно к первому 66, второму 67, третьему 68 и четвертому 69 управляющим выходам вычислительного модуля, прямой выход второго умножителя 16 подключен к первым входам элементов И 41 двенадцатой группы, а инверсный выход к первым входам элементов И 45 тринадцатой группы, выходы которых подключены к соответствующим первым входам элементов ИЛИ 58 второй группы, выходы которых подключены к информационному выходу 65 вычислительного модуля, выход первого элемента ИЛИ 63 подключен к вторым входам элементов И 37 восьмой группы, выходы которых подключены к второму входу первого умножителя 15, выход которого подключен к первым входам элементов И 36 четырнадцатой группы, выход первого регистра 251первой группы подключен к первым входам элементов И пятнадцатой 42 и шестнадцатой 32 групп, четвертого умножителя 18 и второму входу третьего умножителя 19, выход первого регистра 261 второй группы подключен к первым входам элементов И семнадцатой 38 и восемнадцатой 43 групп и второму входу пятого умножителя 20, выходы третьего 19 и пятого 20 умножителей подключены соответственно к первому и второму входам сумматора 21, выход которого подключен к первым входам элементов И 28 девятнадцатой группы, выходы элементов И седьмой 34 и шестнадцатой 32 групп подключены соответственно к первым и вторым входам элементов ИЛИ 53 третьей группы, выходы которых подключены к второму входу второго умножителя 16, выход второго элемента ИЛИ 62 подключен к вторым входам элементов И 30 пятой группы, выход элемента И 51 подключен к синхровходу второго регистра 24, выход третьего элемента ИЛИ 61 подключен к вторым входам элементов И 29 первой группы, выходы элементов И девятнадцатой 28, первой 29 и шестой 33 групп подключены соответственно к первым, вторым и третьим входам элементов ИЛИ 52 четвертой группы, выходы которых подключены к информационному входу второго регистра 24, вход установки в нуль которого подключен к пятому выходу блока управления 27, выходы элементов И семнадцатой 38, двадцатой 35 и четырнадцатой 36 групп подключены соответственно к первым, вторым и третьим входам элементов ИЛИ 55 пятой группы, выход которых подключен к информационному входу второго регистра 262 второй группы, выход 26i-го регистра второй группы (i

) подключены соответственно к информационному входу, первому, второму, третьему и четвертому управляющим входам 5 i+1-го вычислительного модуля, информационный выход 5N-го вычислительного модуля подключен к выходу устройства, тактовый вход 4 которого подключен к тактовым входам всех вычислительных модулей, при этом вычислительный модуль содержит узел 13 вычисления величины из квадратного корня суммы квадратов двух чисел, узел 14 вычисления обратной величины числа, шесть умножителей 15 20, сумматор 21, вычитатель 22, два регистра 23 и 24, две группы регистров 25 и 26, блок управления 27, двадцать три группы элементов И 28 50, элемент И 51, девять групп элементов ИЛИ 52-60, четыре элемента ИЛИ 61 64, причем информационный вход 7 вычислительного модуля подключен к информационному входу первого 23 регистра, выход которого подключен к первым входам первого 15 и второго 16 умножителей, первой 29, второй 46 и третьей 49 групп элементов И и к первому входу узла 13 вычисления величины из квадратного корня суммы квадратов двух чисел, второй вход которого подключен к выходу второго 24 регистра, а выход к первым входам элементов И 31 четвертой группы, выход которых подключен к первым входам элементов ИЛИ 54 первой группы, вторые входы которых подключены к соответствующим выходам элементов И 30 пятой группы, а выходы к входу узла 14 вычисления обратной величины числа, выход которого подключен к первым входам элементов И шестой 33, седьмой 34, восьмой 37 и девятой 40 групп, выход второго регистра 24 подключен к первым входам второго 16, третьего 19 умножителей, элементов И пятой 30, десятой 48 и одиннадцатой 50 групп, первый, второй, третий и четвертый входы блока управления подключены соответственно к первому 8, второму 9, третьему 10 и четвертому 11 входам вычислительного модуля, а первый, второй, третий и четвертый выходы соответственно к первому 66, второму 67, третьему 68 и четвертому 69 управляющим выходам вычислительного модуля, прямой выход второго умножителя 16 подключен к первым входам элементов И 41 двенадцатой группы, а инверсный выход к первым входам элементов И 45 тринадцатой группы, выходы которых подключены к соответствующим первым входам элементов ИЛИ 58 второй группы, выходы которых подключены к информационному выходу 65 вычислительного модуля, выход первого элемента ИЛИ 63 подключен к вторым входам элементов И 37 восьмой группы, выходы которых подключены к второму входу первого умножителя 15, выход которого подключен к первым входам элементов И 36 четырнадцатой группы, выход первого регистра 251первой группы подключен к первым входам элементов И пятнадцатой 42 и шестнадцатой 32 групп, четвертого умножителя 18 и второму входу третьего умножителя 19, выход первого регистра 261 второй группы подключен к первым входам элементов И семнадцатой 38 и восемнадцатой 43 групп и второму входу пятого умножителя 20, выходы третьего 19 и пятого 20 умножителей подключены соответственно к первому и второму входам сумматора 21, выход которого подключен к первым входам элементов И 28 девятнадцатой группы, выходы элементов И седьмой 34 и шестнадцатой 32 групп подключены соответственно к первым и вторым входам элементов ИЛИ 53 третьей группы, выходы которых подключены к второму входу второго умножителя 16, выход второго элемента ИЛИ 62 подключен к вторым входам элементов И 30 пятой группы, выход элемента И 51 подключен к синхровходу второго регистра 24, выход третьего элемента ИЛИ 61 подключен к вторым входам элементов И 29 первой группы, выходы элементов И девятнадцатой 28, первой 29 и шестой 33 групп подключены соответственно к первым, вторым и третьим входам элементов ИЛИ 52 четвертой группы, выходы которых подключены к информационному входу второго регистра 24, вход установки в нуль которого подключен к пятому выходу блока управления 27, выходы элементов И семнадцатой 38, двадцатой 35 и четырнадцатой 36 групп подключены соответственно к первым, вторым и третьим входам элементов ИЛИ 55 пятой группы, выход которых подключен к информационному входу второго регистра 262 второй группы, выход 26i-го регистра второй группы (i  ) подключен к информационному входу 26 i+1-го регистра, выход 26К+1-го регистра второй группы подключен к информационному входу первого регистра 261 второй группы, выход элементов И пятнадцатой 42, двадцать третьей 39, девятой 40 и двенадцатой 41 групп подключены соответственно к первым, вторым, третьим и четвертым входам шестой 56 группы элементов ИЛИ, выходы которых подключены к информационному входу второго регистра 252 первой группы, выход 25i-го регистра первой группы (i

) подключен к информационному входу 26 i+1-го регистра, выход 26К+1-го регистра второй группы подключен к информационному входу первого регистра 261 второй группы, выход элементов И пятнадцатой 42, двадцать третьей 39, девятой 40 и двенадцатой 41 групп подключены соответственно к первым, вторым, третьим и четвертым входам шестой 56 группы элементов ИЛИ, выходы которых подключены к информационному входу второго регистра 252 первой группы, выход 25i-го регистра первой группы (i  ) подключен к информационному входу 25 i+1-го регистра первой группы, выход 25К+1-го регистра первой группы подключен к информационному входу первого регистра 251 первой группы, выходы элементов И второй 46 и десятой 48 групп подключены соответственно к первым и вторым входам элементов ИЛИ 59 седьмой группы, выходы которых подключены к первому входу шестого умножителя 17, выходы элементов И восемнадцатой 43 и двадцать первой 44 групп подключены соответственно к первым и вторым входам восьмой 57 группы элементов ИЛИ, выходы которых подключены ко второму входу шестого умножителя 17, выходы элементов И третьей 49 и одиннадцатой 50 групп подключены соответственно к первым и вторым входам элементов ИЛИ 60 восьмой группы, выходы четвертого 18 и шестого 17 умножителей подключены соответственно к первому и второму входам вычитателя 22, выход которого подключен к первым входам элементов И 47 двадцать второй группы, выходы которых подключены к вторым входам элементов ИЛИ 58 второй группы, шестой выход блока управления 27 подключен к первым входам элементов И двадцатой 35 и двадцать третьей 39 групп и третьего элемента ИЛИ 61, седьмой выход блока управления 27 подключен к вторым входам элементов И четвертой 31, шестой 33, седьмой 34 и четырнадцатой 36 групп и первому входу пятого элемента ИЛИ 64, восьмой выход блока управления 27 подключен к вторым входам элементов И третьей 49, десятой 48, восемнадцатой 43 и девятнадцатой 28 групп, девятый выход блока управления 27 подключен к первым входам элемента И 51 и второго элемента ИЛИ 62, десятый выход блока управления 27 подключен к первому входу первого элемента ИЛИ 63 и вторым входам второго 62 и пятого 64 элементов ИЛИ, одиннадцатый выход блока управления 27 подключен к вторым входам элементов И 42 пятнадцатой группы, двенадцатый выход блока управления 27 подключен к вторым входам элементов И 38 семнадцатой группы, тринадцатый выход блока управления 27 подключен к вторым входам элементов И второй 46, одиннадцатой 50 и двадцать первой 44 групп и первого элемента ИЛИ, четырнадцатый выход блока управления 27 подключен ко второму входу третьего элемента ИЛИ 61, пятнадцатый выход блока управления 27 подключен к вторым входам элементов И 47 двадцать второй группы, шестнадцатый выход блока управления 27 подключен к вторым входам элементов И 40 девятой группы, семнадцатый выход блока управления 27 подключен к вторым входам элементов И 45 тринадцатой группы, единичный вход вычислительного модуля подключен к первым входам элементов И 44 двадцать первой группы и вторым входам элементов И 35 двадцатой группы, нулевой вход вычислительного модуля подключен к вторым входам элементов И 39 двадцать третьей группы, тактовый вход 12 вычислительного модуля подключен к синхровходам первого регистра, всех регистров первой 25 и второй 26 групп и шестому входу блока управления 27. Блок управления 27 содержит шесть триггеров 75 80, три группы триггеров 81 83, двенадцать элементов И 84 95, два элемента ИЛИ 96, 97, два элемента ИЛИ-НЕ 98, 99, три элемента НЕ 100 102, причем первый 70 вход блока управления подключен к входу первого элемента НЕ 100, первым входам четвертого 87 и пятого 88 элементов И и информационному входу первого триггера 811 первой группы, выход 81i-го триггера первой группы (i

) подключен к информационному входу 25 i+1-го регистра первой группы, выход 25К+1-го регистра первой группы подключен к информационному входу первого регистра 251 первой группы, выходы элементов И второй 46 и десятой 48 групп подключены соответственно к первым и вторым входам элементов ИЛИ 59 седьмой группы, выходы которых подключены к первому входу шестого умножителя 17, выходы элементов И восемнадцатой 43 и двадцать первой 44 групп подключены соответственно к первым и вторым входам восьмой 57 группы элементов ИЛИ, выходы которых подключены ко второму входу шестого умножителя 17, выходы элементов И третьей 49 и одиннадцатой 50 групп подключены соответственно к первым и вторым входам элементов ИЛИ 60 восьмой группы, выходы четвертого 18 и шестого 17 умножителей подключены соответственно к первому и второму входам вычитателя 22, выход которого подключен к первым входам элементов И 47 двадцать второй группы, выходы которых подключены к вторым входам элементов ИЛИ 58 второй группы, шестой выход блока управления 27 подключен к первым входам элементов И двадцатой 35 и двадцать третьей 39 групп и третьего элемента ИЛИ 61, седьмой выход блока управления 27 подключен к вторым входам элементов И четвертой 31, шестой 33, седьмой 34 и четырнадцатой 36 групп и первому входу пятого элемента ИЛИ 64, восьмой выход блока управления 27 подключен к вторым входам элементов И третьей 49, десятой 48, восемнадцатой 43 и девятнадцатой 28 групп, девятый выход блока управления 27 подключен к первым входам элемента И 51 и второго элемента ИЛИ 62, десятый выход блока управления 27 подключен к первому входу первого элемента ИЛИ 63 и вторым входам второго 62 и пятого 64 элементов ИЛИ, одиннадцатый выход блока управления 27 подключен к вторым входам элементов И 42 пятнадцатой группы, двенадцатый выход блока управления 27 подключен к вторым входам элементов И 38 семнадцатой группы, тринадцатый выход блока управления 27 подключен к вторым входам элементов И второй 46, одиннадцатой 50 и двадцать первой 44 групп и первого элемента ИЛИ, четырнадцатый выход блока управления 27 подключен ко второму входу третьего элемента ИЛИ 61, пятнадцатый выход блока управления 27 подключен к вторым входам элементов И 47 двадцать второй группы, шестнадцатый выход блока управления 27 подключен к вторым входам элементов И 40 девятой группы, семнадцатый выход блока управления 27 подключен к вторым входам элементов И 45 тринадцатой группы, единичный вход вычислительного модуля подключен к первым входам элементов И 44 двадцать первой группы и вторым входам элементов И 35 двадцатой группы, нулевой вход вычислительного модуля подключен к вторым входам элементов И 39 двадцать третьей группы, тактовый вход 12 вычислительного модуля подключен к синхровходам первого регистра, всех регистров первой 25 и второй 26 групп и шестому входу блока управления 27. Блок управления 27 содержит шесть триггеров 75 80, три группы триггеров 81 83, двенадцать элементов И 84 95, два элемента ИЛИ 96, 97, два элемента ИЛИ-НЕ 98, 99, три элемента НЕ 100 102, причем первый 70 вход блока управления подключен к входу первого элемента НЕ 100, первым входам четвертого 87 и пятого 88 элементов И и информационному входу первого триггера 811 первой группы, выход 81i-го триггера первой группы (i  ) подключен к информационному входу 81i+1-го триггера первой группы, выход 81К+3-го триггера первой группы подключен к первому 103 выходу блока управления, выход первого элемента НЕ 100 подключен к первым входам первого 84, второго 85 и третьего 86 элементов И, второй 71 вход блока управления подключен к входу второго элемента НЕ 101, вторым входам второго 85 и третьего 86 элементов И и информационному входу первого триггера 821 второй группы, выход 82i-го триггера второй группы (i

) подключен к информационному входу 81i+1-го триггера первой группы, выход 81К+3-го триггера первой группы подключен к первому 103 выходу блока управления, выход первого элемента НЕ 100 подключен к первым входам первого 84, второго 85 и третьего 86 элементов И, второй 71 вход блока управления подключен к входу второго элемента НЕ 101, вторым входам второго 85 и третьего 86 элементов И и информационному входу первого триггера 821 второй группы, выход 82i-го триггера второй группы (i  ) подключен к информационному входу 82i+1-го триггера второй группы, выход 82К+3-го триггера второй группы подключен к второму 104 выходу блока управления, выход второго элемента НЕ 101 подключен к вторым входам первого 84, четвертого 87 и пятого 88 элементов И, третий 72 вход блока управления подключен к входу третьего элемента НЕ 102, к третьим входам первого 84, третьего 86 и пятого 88 элементов И и информационному входу первого триггера 831 третьей группы, выход 83 i-го триггера третьей группы (i

) подключен к информационному входу 82i+1-го триггера второй группы, выход 82К+3-го триггера второй группы подключен к второму 104 выходу блока управления, выход второго элемента НЕ 101 подключен к вторым входам первого 84, четвертого 87 и пятого 88 элементов И, третий 72 вход блока управления подключен к входу третьего элемента НЕ 102, к третьим входам первого 84, третьего 86 и пятого 88 элементов И и информационному входу первого триггера 831 третьей группы, выход 83 i-го триггера третьей группы (i  ) подключен к информационному входу 83 i+1-го триггера третьей группы, выход 83 К+3-го триггера третьей группы подключен к третьему 105 выходу блока управления, выходы с первого по пятый элементов И 84 88 подключены к информационным входам соответственно с первого по пятый триггеров 76-80, выход первого элемента И 84 подключен к пятому 107 выходу блока управления, четвертый 73 вход которого подключен к первому входу шестого элемента И 94, второй вход которого подключен к выходу третьего элемента И 86, а выход к первому элементу ИЛИ 96, выход которого подключен к информационному входу шестого триггера 75, прямой выход которого подключен к первым входам одиннадцатого 92, двенадцатого 93 элементов И и четвертому 106 выходу блока управления, а инверсный выход к первым входам восьмого 89, девятого 90 и десятого 91 элементов И, выход пятого элемента И 88 подключен к первому входу седьмого элемента И 95, второй вход которого подключен к единичному входу блока управления, а выход к второму входу первого элемента ИЛИ 96, выход первого триггера 76 подключен к второму входу восьмого элемента И 89, первому входу второго элемента ИЛИ 97 и четырнадцатому 116 выходу блока управления, инверсный выход первого триггера 76 подключен к второму входу девятого элемента И 90, выход второго триггера 77 подключен к третьим входам восьмого 89 и девятого 90 элементов И и вторым входам одиннадцатого 92 элемента И, выход третьего 78 триггера подключен к вторым входам десятого 91, двенадцатого 93 элементов И и к пятнадцатому 117 выходу блока управления, выход четвертого 79 триггера подключен к первому входу первого элемента ИЛИ-НЕ 98 и шестнадцатому 118 выходу блока управления, выход пятого триггера 80 подключен к семнадцатому 119 выходу блока управления, выход восьмого элемента И 89 подключен к вторым входам элемента ИЛИ 97 и первого элемента ИЛИ-НЕ 98 и первому входу второго элемента ИЛИ-НЕ 99, выход девятого элемента И 90 подключен к третьим входам второго элемента ИЛИ 97 и первого элемента ИЛИ-НЕ 98 и второму входу второго элемента ИЛИ-НЕ 99, выход десятого элемента И 91 подключен к четвертому входу второго элемента ИЛИ 97, выход одиннадцатого элемента И 92 подключен к четвертому входу первого элемента ИЛИ-НЕ 98, выходы восьмого 89, девятого 90, десятого 91 элементов И, второго элемента ИЛИ 97, одиннадцатого элемента И 92, первого 98 и второго 99 элементов ИЛИ-НЕ и двенадцатого элемента И 93 подключены соответственно выходам с шестого по тринадцатый 108-115 блока управления, пятый вход 74 которого подключен к синхровходам всех триггеров блока управления.

) подключен к информационному входу 83 i+1-го триггера третьей группы, выход 83 К+3-го триггера третьей группы подключен к третьему 105 выходу блока управления, выходы с первого по пятый элементов И 84 88 подключены к информационным входам соответственно с первого по пятый триггеров 76-80, выход первого элемента И 84 подключен к пятому 107 выходу блока управления, четвертый 73 вход которого подключен к первому входу шестого элемента И 94, второй вход которого подключен к выходу третьего элемента И 86, а выход к первому элементу ИЛИ 96, выход которого подключен к информационному входу шестого триггера 75, прямой выход которого подключен к первым входам одиннадцатого 92, двенадцатого 93 элементов И и четвертому 106 выходу блока управления, а инверсный выход к первым входам восьмого 89, девятого 90 и десятого 91 элементов И, выход пятого элемента И 88 подключен к первому входу седьмого элемента И 95, второй вход которого подключен к единичному входу блока управления, а выход к второму входу первого элемента ИЛИ 96, выход первого триггера 76 подключен к второму входу восьмого элемента И 89, первому входу второго элемента ИЛИ 97 и четырнадцатому 116 выходу блока управления, инверсный выход первого триггера 76 подключен к второму входу девятого элемента И 90, выход второго триггера 77 подключен к третьим входам восьмого 89 и девятого 90 элементов И и вторым входам одиннадцатого 92 элемента И, выход третьего 78 триггера подключен к вторым входам десятого 91, двенадцатого 93 элементов И и к пятнадцатому 117 выходу блока управления, выход четвертого 79 триггера подключен к первому входу первого элемента ИЛИ-НЕ 98 и шестнадцатому 118 выходу блока управления, выход пятого триггера 80 подключен к семнадцатому 119 выходу блока управления, выход восьмого элемента И 89 подключен к вторым входам элемента ИЛИ 97 и первого элемента ИЛИ-НЕ 98 и первому входу второго элемента ИЛИ-НЕ 99, выход девятого элемента И 90 подключен к третьим входам второго элемента ИЛИ 97 и первого элемента ИЛИ-НЕ 98 и второму входу второго элемента ИЛИ-НЕ 99, выход десятого элемента И 91 подключен к четвертому входу второго элемента ИЛИ 97, выход одиннадцатого элемента И 92 подключен к четвертому входу первого элемента ИЛИ-НЕ 98, выходы восьмого 89, девятого 90, десятого 91 элементов И, второго элемента ИЛИ 97, одиннадцатого элемента И 92, первого 98 и второго 99 элементов ИЛИ-НЕ и двенадцатого элемента И 93 подключены соответственно выходам с шестого по тринадцатый 108-115 блока управления, пятый вход 74 которого подключен к синхровходам всех триггеров блока управления.

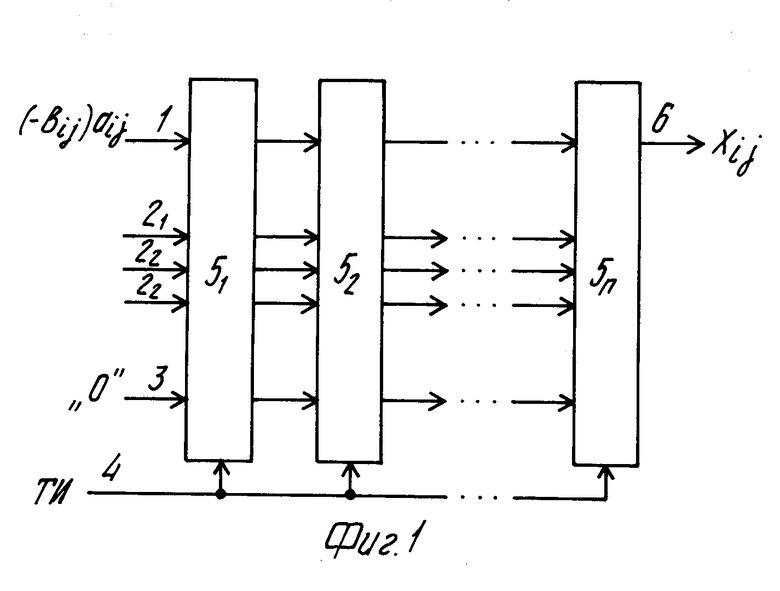

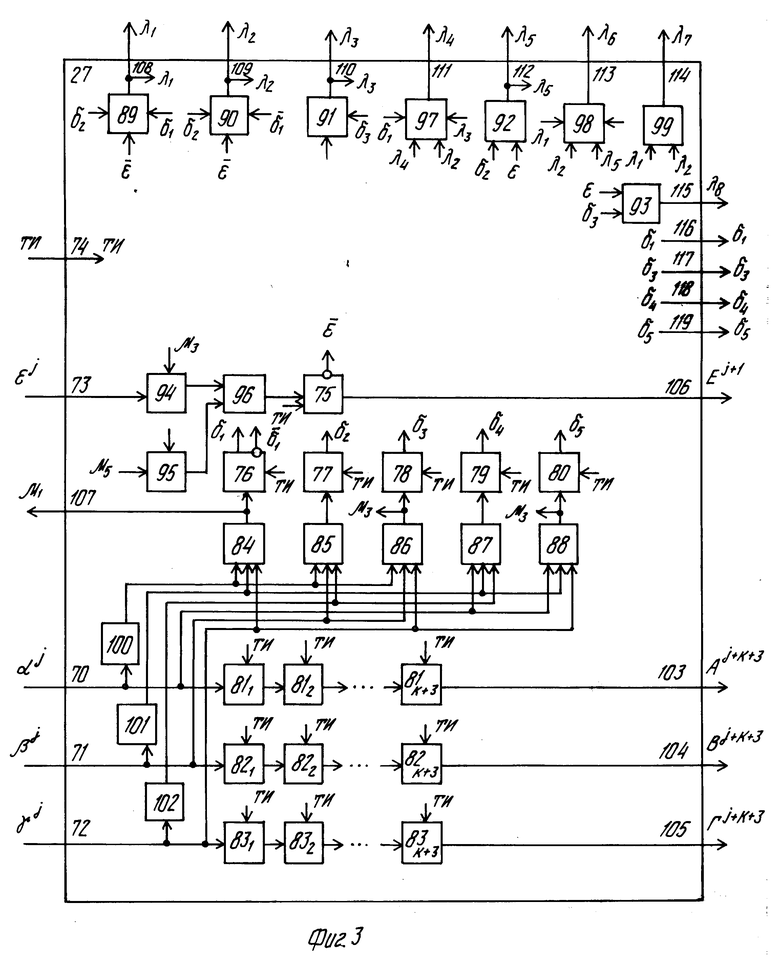

На фиг. 1 представлена структурная схема устройства для решения задачи наименьших квадратов; на фиг. 2 структурная схема вычислительного модуля; на фиг. 3 структурная схема блока управления.

Устройство для решения задачи наименьших квадратов (фиг. 1) содержит информационный вход 1; первый 21, второй 22, третий 23 и четвертый 3 управляющие входы, тактовый вход 4, вычислительные модули 5i(i  ) и выход 6.

) и выход 6.

Вычислительный модуль 5 (фиг. 2) содержит информационный вход 7, первый 8, второй 9, третий 10 и четвертый 11 управляющие входы, тактовый вход 12, узел 13 вычисления величины  , узел 14 вычисления обратной величины числа, первый 15, второй 16, третий 17, четвертый 18, пятый 19 и шестой 20 умножители, сумматор 21, вычитатель 22, первый 23 и второй 24 регистры, первую 25i и вторую 26i группы регистров (i

, узел 14 вычисления обратной величины числа, первый 15, второй 16, третий 17, четвертый 18, пятый 19 и шестой 20 умножители, сумматор 21, вычитатель 22, первый 23 и второй 24 регистры, первую 25i и вторую 26i группы регистров (i  ), блок управления 27, группы элементов И 28 50, элемент И 51, группы элементов ИЛИ 52 60, элементы ИЛИ 61 64; информационный выход 65, первый 66, второй 67, третий 68 и четвертый 69 управляющие выходы.

), блок управления 27, группы элементов И 28 50, элемент И 51, группы элементов ИЛИ 52 60, элементы ИЛИ 61 64; информационный выход 65, первый 66, второй 67, третий 68 и четвертый 69 управляющие выходы.

Блок управления 27 (фиг. 3) содержит первый 70, второй 71, третий 72, четвертый 73 и пятый 74 входы, триггеры 75-80, первую 81i, вторую 82i и третью 83i группы триггеров (i  ), элементы И 84 95, элементы ИЛИ 96, 97, элементы ИЛИ-НЕ 98, 99, элементы НЕ 100-102, с первого по семнадцатый выходы 103-119.

), элементы И 84 95, элементы ИЛИ 96, 97, элементы ИЛИ-НЕ 98, 99, элементы НЕ 100-102, с первого по семнадцатый выходы 103-119.

В основу работы устройства положено решение задачи наименьших квадратов, которое основано на QR-разложении матрицы: A QR, где Q ортогональная матрица, R

, R ∈

, R ∈  R1∈

R1∈  верхняя треугольная матрица, Q ∈

верхняя треугольная матрица, Q ∈  нулевая матрица.

нулевая матрица.

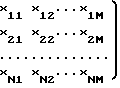

Задача наименьших квадратов осуществляется решением системы линейных алгебраических уравнений вида АХ В, где A ∈  , B ∈

, B ∈  , X ∈

, X ∈  , N ≅ K число уравнений К больше или равно числу неизвестных N, М число правых частей:

, N ≅ K число уравнений К больше или равно числу неизвестных N, М число правых частей:

(1) или

(1) или

Требуется найти матрицу Х, минимизирующую  A·X-B

A·X-B , где норма

, где норма  для любой матрицы S ∈

для любой матрицы S ∈  определяется так:

определяется так: S

S

S

S .

.

Если N K, то система уравнений АХ В с N неизвестными для каждой из М правых частей.

Если N K M, а В единичная матрица, то задача (1) сводится к вычислению обратной матрицы А-1. Матрица Х находится как произведение трех матриц:

Х R1-1 Q1T˙B, где Q1∈  первые N столбцов матрицы Q.

первые N столбцов матрицы Q.

Матрица Х определяется следующими рекуррентными соотношениями.

Для вычисления матриц R1 Q1T B и W Q1T(-В):

a(K i + 1, j, 0) aij, 1 ≅i≅ K, 1 ≅j≅ N;

a(K i + 1, N + j, 0) -bij, 1 ≅i≅ K, N + 1 ≅j≅ N + M;

K 1, 2, N:

r(k,j,k) a(k,j,k-1), j  ; если r(i 1, k, k) 0, то

; если r(i 1, k, k) 0, то

r(i, k, k) a(i, k, k-1),

S(i, k) 0,

c(i, k) 1; если r(i-1, k, k) ≠ 0, то

r(i,k,k)  ,

,

S(i, k) r(i-1, k, k)/r(i,k,k),

c(i,k) a(i, k, k-1)/r(i, k, k),

i  (если N=K, то K не берется равным N)

(если N=K, то K не берется равным N)

a(i, j, k) c(i, k) r(i-1, j, k) S(i, k) a(i, j, k-1),

r(i, j, k) S(i, k) r(i-1, j, k) + c(i, k) a(i, j, k 1),

i  (если N=K, то k ≠ N),

(если N=K, то k ≠ N),

j  ,

,

rkj(1) r(K, j, k), 1 ≅k≅ j ≅N;

ωkj= r(K, N+j, k), 1 ≅k≅ N, 1 ≅j≅ M.

Для вычисления матрицы U R1-1:

k 1, 2,N:

Ukk 1/rkk(1);

g(k,j,k) -Ukk·r , k ≠ N;

, k ≠ N;

Uik= g(i,k,k-1)/r , k ≠ 1;

, k ≠ 1;

g(i, j, k) g(i, j, k-1) Uik rkj(1),

i  , k ≠ 1,

, k ≠ 1,

j  , k ≠ N.

, k ≠ N.

Для вычисления матрицы Х -U W:

K 1, 2, N:

x(k,j,k) -Ukk·ωkj, j  ;

;

x(i, j, k) x(i, j, k-1) Uikωkj,

i  , k ≠ 1,

, k ≠ 1,

j  ,

,

xij x(i,j,М).

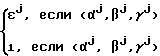

Вычислительный модуль 5 обладает возможностью реализации следующих функций:

Aj+k+3 αj

Bj+k+3 βj

Γj+k+3=γj где Аj+k+3, Bj+k+3 и Γj+k+3 значения соответственно на первом, втором и третьем управляющих выходах вычислительного модуля на (j+k+3)-м такте,

Ej+1=

где Еj+1 значение на четвертом управляющем выходе вычислительного модуля на (j+1)-м такте;

где Еj+1 значение на четвертом управляющем выходе вычислительного модуля на (j+1)-м такте;

αj, βj, γj и εj значения соответственно на первом, втором, третьем и четвертом управляющих входах вычислительного модуля на j-м такте,

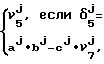

Fj+1=

где

где

aj=

bj=

cj=

ν = 1,

= 1,

ν

ν

ν

ν ,

,

ν

ν

ν и

и

ν9j=ν1j˙ν7j+ν2j˙ν8j

δ1j+1=μ1j=(αj, βj, γj)= (0, 0, 1),

δ2j+1=μ2j=(αj, βj, γj) (0, 1, 0),

δ3j+1=μ3j=(αj, βj, γj) (0, 1, 1),

δ4j+1=μ4j=(αj, βj, γj) (1, 0, 0),

δ5j+1=μ5j=(αj, βj, γj) (1, 0, 1),

λ ,

,

λ ,

,

λ ,

,

λ

λ5j δ2j˙εj

λ ,

,

λ ,

,

λ8j δ3j˙εj где аj значение на информационном входе вычислительного модуля на j-м такте;

Fj+1 значение на информационном выходе вычислительного модуля на (j+1)-м такте.

Организация входного и выходного потоков данных задается следующими выражениями.

На вход 1 подаются элементы матриц aij и (-bij) в моменты времени:

t = -i+j(K+1)-1, i

= -i+j(K+1)-1, i  , j

, j  ;

;

t = -i+(j+N)(K+1)-1, i

= -i+(j+N)(K+1)-1, i  , j

, j  .

.

На вход 3 постоянно подается нулевой сигнал.

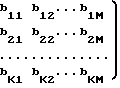

На входы 21, 22, 23 подаются значения управляющих сигналов τij=(α, β, γ) представляющих матрицу вида

τij=

в моменты времени

в моменты времени

t = j-1+(i-1)(K+1), i

= j-1+(i-1)(K+1), i  , j

, j  .

.

На выходе 6 формируются элементы хij в моменты времени

t = i+(j+N-1)(K+1)+N+K-2, i

= i+(j+N-1)(K+1)+N+K-2, i  , j

, j  .

.

Последний элемент ХNM формируется на ((N+M)(K+1)+2N-3)=М такте.

Рассмотрим работу устройства для решения системы линейных алгебраических уравнений при N 3, M 2 и K 3.

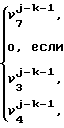

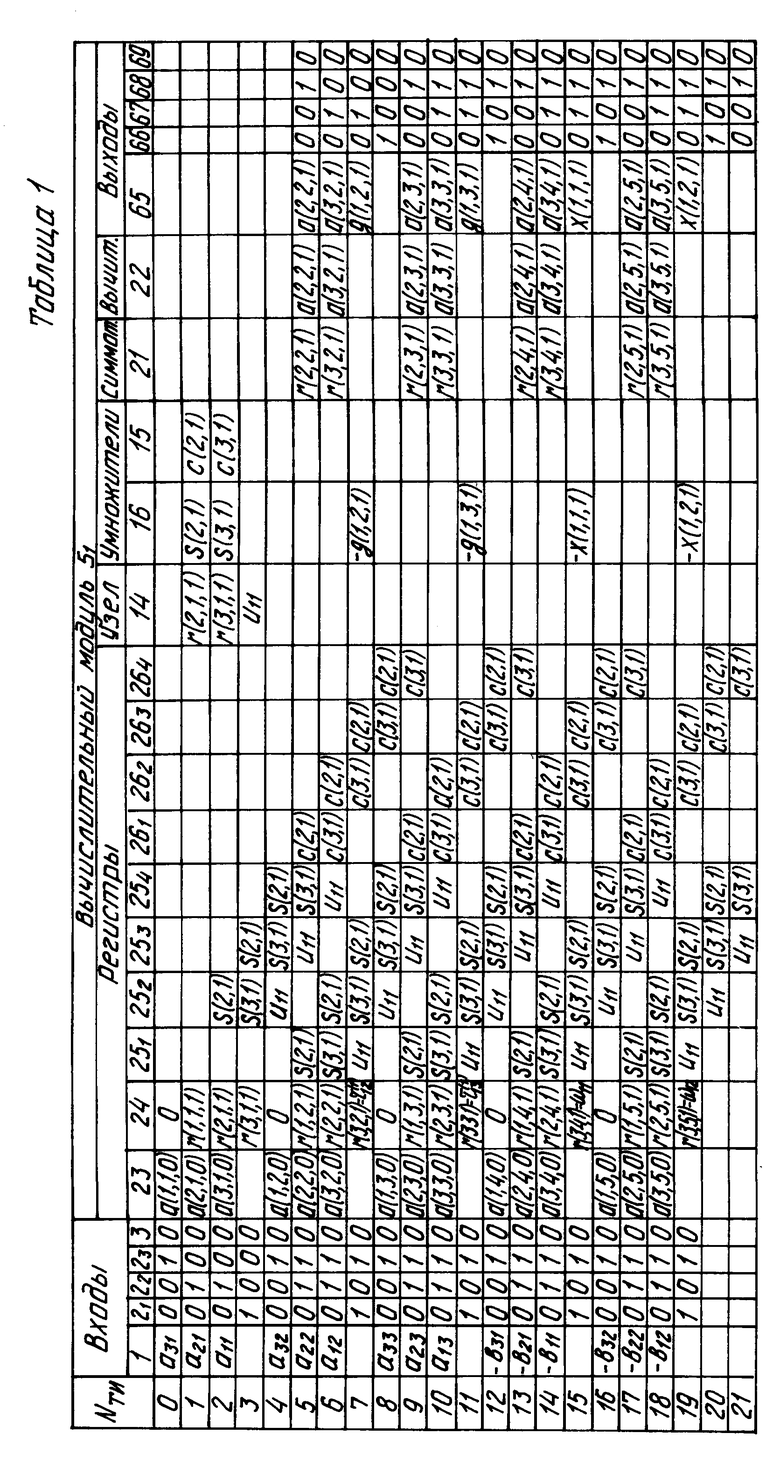

На вход 1 подаются элементы aij и (-bij), на входы 21, 22 и 23 соответствующие управляющие сигналы α, β, γ на вход 3 постоянно подается нулевой сигнал, с выхода 6 снимаются элементы хij. В табл. 1, 2 и 3 приведены значения на входах, состояние регистров, значение на выходе узла вычисления обратной величины числа, первом и втором умножителях, сумматора, вычитателе и выходах соответственно вычислительных модулей 51, 52 и 53.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЧЕТЫРЕХМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1993 |

|

RU2069010C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРЕХМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1993 |

|

RU2069011C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1994 |

|

RU2116667C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1994 |

|

RU2049351C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N X N)-МАТРИЦЫ | 1992 |

|

RU2012050C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024932C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1991 |

|

RU2012049C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦЫ НА ВЕКТОР | 1991 |

|

RU2011222C1 |

| УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ N X N МАТРИЦ | 1990 |

|

RU2037199C1 |

| Устройство для умножения матриц | 1990 |

|

SU1793446A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных специализированных вычислительных системах для решения задачи наименьших квадратов, обеспечивающей решение системы линейных алгебраических уравнений для случая, когда число уравнений больше числа неизвестных или нет уверенности в хорошей обусловленности матрицы. Решение задачи наименьших квадратов используется в задачах управления, связи и обработки сигналов (выравнивание, спектральный анализ, обработка речевых сигналов и т.д.). Устройство содержит N вычислительных модулей, где N число неизвестных системы линейных алгебраических уравнений, каждый вычислительный модуль содержит узел вычисления величины из квадратного корня суммы квадратов двух чисел, узел вычисления обратной величины числа, шесть умножителей, сумматор, вычитатель, два регистра, две группы регистров, блок управления, двадцать три группы элементов И, элемент И, девять групп элементов ИЛИ и четыре элемента ИЛИ. 1 з. п. ф-лы, 3 ил. 3 табл.

подключен к информационному входу (i + 1)-го регистра, выход (K + 1)-го регистра второй группы подключен к информационному входу первого регистра второй группы, выход элементов И пятнадцатой, двадцать третьей, девятой и двенадцатой групп подключены соответственно к первым, вторым, третьим и четвертым входам шестой группы элементов ИЛИ, выходы которых подключены к информационному входу второго регистра первой группы, выход i-го регистра первой группы

подключен к информационному входу (i + 1)-го регистра, выход (K + 1)-го регистра второй группы подключен к информационному входу первого регистра второй группы, выход элементов И пятнадцатой, двадцать третьей, девятой и двенадцатой групп подключены соответственно к первым, вторым, третьим и четвертым входам шестой группы элементов ИЛИ, выходы которых подключены к информационному входу второго регистра первой группы, выход i-го регистра первой группы  подключен к информационному входу (i + 1)-го регистра первой группы, выход (K + 1)-го регистра первой группы подключен к информационному входу первого регистра первой группы, выход элементов И второй и десятой групп подключены соответственно к первым и вторым входам элементов ИЛИ седьмой группы, выходы которых подключены к первому входу шестого умножителя, выходы элементов И восемнадцатой и двадцать первой групп подключены соответственно к первым и вторым входам восьмой группы элементов ИЛИ, выходы которых подключены к второму входу шестого умножителя, выходы элементов И третьей и одиннадцатой групп подключены соответственно к первым и вторым входам элементов ИЛИ девятой группы, выходы пятого и шестого умножителей подключены соответственно к первому и второму входам вычитателя, выход которого подключен к первым входам элементов И двадцать второй группы, выход которых подключен к вторым входам элементов ИЛИ второй группы, шестой выход блока управления подключен к первым входам элементов И двадцатой и двадцать третьей групп и третьего элемента ИЛИ, седьмой выход блока управления подключен к вторым входам элементов И четвертой, шестой, седьмой и четырнадцатой групп первого элемента ИЛИ и первому входу четвертого элемента ИЛИ, восьмой выход блока управления подключен к вторым входам элементов И третьей, десятой, восемнадцатой и девятнадцатой групп, девятый выход блока управления подключен к первым входам элемента И и второго элемента ИЛИ, десятый выход блока управления подключен к первому входу первого элемента ИЛИ и вторым входам второго и четвертого элементов ИЛИ, одиннадцатый выход блока управления подключен к вторым входам элементов И пятнадцатой группы, двенадцатый выход блока управления подключен к вторым входам элементов И семнадцатой группы, тринадцатый выход блока управления подключен к вторым входам элементов И второй, одиннадцатой и двадцать первой группы, четырнадцатый выход блока управления подключен к второму входу третьего элемента ИЛИ, пятнадцатый выход блока управления подключен к вторым входам элементов И двадцать второй группы, шестнадцатый выход блока управления подключен к вторым входам элементов И девятой группы, семнадцатый выход блока управления подключен к вторым входам элементов И тринадцатой и шестнадцатой групп, единичный вход вычислительного модуля подключен к первым входам элементов И двадцать первой группы и вторым входам элементов И двадцатой группы, нулевой вход вычислительного модуля подключен к вторым входам элементов И двадцать третьей группы, тактовый вход вычислительного модуля подключен к синхровходам первого регистра, всех регистров первой и второй групп и пятому входу блока управления.

подключен к информационному входу (i + 1)-го регистра первой группы, выход (K + 1)-го регистра первой группы подключен к информационному входу первого регистра первой группы, выход элементов И второй и десятой групп подключены соответственно к первым и вторым входам элементов ИЛИ седьмой группы, выходы которых подключены к первому входу шестого умножителя, выходы элементов И восемнадцатой и двадцать первой групп подключены соответственно к первым и вторым входам восьмой группы элементов ИЛИ, выходы которых подключены к второму входу шестого умножителя, выходы элементов И третьей и одиннадцатой групп подключены соответственно к первым и вторым входам элементов ИЛИ девятой группы, выходы пятого и шестого умножителей подключены соответственно к первому и второму входам вычитателя, выход которого подключен к первым входам элементов И двадцать второй группы, выход которых подключен к вторым входам элементов ИЛИ второй группы, шестой выход блока управления подключен к первым входам элементов И двадцатой и двадцать третьей групп и третьего элемента ИЛИ, седьмой выход блока управления подключен к вторым входам элементов И четвертой, шестой, седьмой и четырнадцатой групп первого элемента ИЛИ и первому входу четвертого элемента ИЛИ, восьмой выход блока управления подключен к вторым входам элементов И третьей, десятой, восемнадцатой и девятнадцатой групп, девятый выход блока управления подключен к первым входам элемента И и второго элемента ИЛИ, десятый выход блока управления подключен к первому входу первого элемента ИЛИ и вторым входам второго и четвертого элементов ИЛИ, одиннадцатый выход блока управления подключен к вторым входам элементов И пятнадцатой группы, двенадцатый выход блока управления подключен к вторым входам элементов И семнадцатой группы, тринадцатый выход блока управления подключен к вторым входам элементов И второй, одиннадцатой и двадцать первой группы, четырнадцатый выход блока управления подключен к второму входу третьего элемента ИЛИ, пятнадцатый выход блока управления подключен к вторым входам элементов И двадцать второй группы, шестнадцатый выход блока управления подключен к вторым входам элементов И девятой группы, семнадцатый выход блока управления подключен к вторым входам элементов И тринадцатой и шестнадцатой групп, единичный вход вычислительного модуля подключен к первым входам элементов И двадцать первой группы и вторым входам элементов И двадцатой группы, нулевой вход вычислительного модуля подключен к вторым входам элементов И двадцать третьей группы, тактовый вход вычислительного модуля подключен к синхровходам первого регистра, всех регистров первой и второй групп и пятому входу блока управления. подключен к информационному входу (i + 1)-го триггера первой группы, выход (K + 3)-го триггера первой группы подключен к первому выходу блока управления, выход первого элемента НЕ подключен к первым входам первого, второго и третьего элементов И, второй вход блока управления подключен к входу второго элемента НЕ, вторым входам второго и третьего элементов И и информационному входу первого триггера второй группы, выход i-го триггера второй группы

подключен к информационному входу (i + 1)-го триггера первой группы, выход (K + 3)-го триггера первой группы подключен к первому выходу блока управления, выход первого элемента НЕ подключен к первым входам первого, второго и третьего элементов И, второй вход блока управления подключен к входу второго элемента НЕ, вторым входам второго и третьего элементов И и информационному входу первого триггера второй группы, выход i-го триггера второй группы  подключен к информационному входу (i +1)-го триггера второй группы, выход (K + 3)-го триггера второй группы подключен к второму выходу блока управления, выход второго элемента НЕ подключен к вторым входам первого, четвертого и пятого элементов И, третий вход блока управления подключен к входу третьего элемента НЕ, третьим входам первого, третьего и пятого элементов И и информационному входу первого триггера третьей группы, выход i-го триггера третьей группы

подключен к информационному входу (i +1)-го триггера второй группы, выход (K + 3)-го триггера второй группы подключен к второму выходу блока управления, выход второго элемента НЕ подключен к вторым входам первого, четвертого и пятого элементов И, третий вход блока управления подключен к входу третьего элемента НЕ, третьим входам первого, третьего и пятого элементов И и информационному входу первого триггера третьей группы, выход i-го триггера третьей группы  подключен к информационному входу (i + 1)-го триггера третьей группы, выход (K + 3)-го триггера третьей группы подключен к третьему выходу блока управления, выход третьего элемента НЕ подключен к третьим входам второго и четвертого элементов И, выходы с первого по пятый элементов И подключены к информационным входам соответственно с первого по пятый триггеров, выход первого элемента И подключен к пятому выходу блока управления, четвертый вход которого подключен к первому входу шестого элемента И, второй вход которого подключен к выходу третьего элемента И, а выход к первому входу первого элемента ИЛИ, выход которого подключен к информационному входу шестого триггера, прямой выход которого подключен к первым входам одиннадцатого, двенадцатого элементов И и четвертому выходу блока управления, а инверсный выход к первым входам восьмого, девятого и десятого элементов И, выход пятого элемента И подключен к первому входу седьмого элемента И, второй вход которого подключен к единичному входу блока управления, а выход к второму входу первого элемента ИЛИ, прямой выход первого триггера подключен к второму входу восьмого элемента И, первому входу второго элемента ИЛИ и четвертому выходу блока управления, инверсный выход первого триггера подключен к второму входу девятого элемента И, выход второго триггера подключен к третьим входам восьмого и девятого элементов И и второму входу одиннадцатого элемента И, выход третьего триггера подключен к вторым входам десятого, двенадцатого элементов И и пятнадцатому выходу блока управления, выходы четвертого триггера подключен к первому входу первого элемента ИЛИ-НЕ и шестнадцатому выходу блока управления, выход пятого триггера подключен к семнадцатому выходу блока управления, выход восьмого элемента И подключен к вторым входам второго элемента ИЛИ и первого элемента ИЛИ-НЕ и первому входу второго элемента ИЛИ-НЕ, выход девятого элемента И подключен к третьим входам второго элемента ИЛИ и первого элемента ИЛИ-НЕ и второму входу второго элемента ИЛИ-НЕ, выход десятого элемента И подключен к четвертому входу второго элемента ИЛИ, выход одиннадцатого элемента И подключен к четвертому входу первого элемента ИЛИ-НЕ, выходы восьмого, девятого, десятого элементов И, второго элемента ИЛИ, одиннадцатого элемента И, первого и второго элементов ИЛИ-НЕ и двенадцатого элемента И подключены соответственно к шестому по тринадцатый выходам блока управления, пятый вход которого подключен к синхровходам всех триггеров блока управления.

подключен к информационному входу (i + 1)-го триггера третьей группы, выход (K + 3)-го триггера третьей группы подключен к третьему выходу блока управления, выход третьего элемента НЕ подключен к третьим входам второго и четвертого элементов И, выходы с первого по пятый элементов И подключены к информационным входам соответственно с первого по пятый триггеров, выход первого элемента И подключен к пятому выходу блока управления, четвертый вход которого подключен к первому входу шестого элемента И, второй вход которого подключен к выходу третьего элемента И, а выход к первому входу первого элемента ИЛИ, выход которого подключен к информационному входу шестого триггера, прямой выход которого подключен к первым входам одиннадцатого, двенадцатого элементов И и четвертому выходу блока управления, а инверсный выход к первым входам восьмого, девятого и десятого элементов И, выход пятого элемента И подключен к первому входу седьмого элемента И, второй вход которого подключен к единичному входу блока управления, а выход к второму входу первого элемента ИЛИ, прямой выход первого триггера подключен к второму входу восьмого элемента И, первому входу второго элемента ИЛИ и четвертому выходу блока управления, инверсный выход первого триггера подключен к второму входу девятого элемента И, выход второго триггера подключен к третьим входам восьмого и девятого элементов И и второму входу одиннадцатого элемента И, выход третьего триггера подключен к вторым входам десятого, двенадцатого элементов И и пятнадцатому выходу блока управления, выходы четвертого триггера подключен к первому входу первого элемента ИЛИ-НЕ и шестнадцатому выходу блока управления, выход пятого триггера подключен к семнадцатому выходу блока управления, выход восьмого элемента И подключен к вторым входам второго элемента ИЛИ и первого элемента ИЛИ-НЕ и первому входу второго элемента ИЛИ-НЕ, выход девятого элемента И подключен к третьим входам второго элемента ИЛИ и первого элемента ИЛИ-НЕ и второму входу второго элемента ИЛИ-НЕ, выход десятого элемента И подключен к четвертому входу второго элемента ИЛИ, выход одиннадцатого элемента И подключен к четвертому входу первого элемента ИЛИ-НЕ, выходы восьмого, девятого, десятого элементов И, второго элемента ИЛИ, одиннадцатого элемента И, первого и второго элементов ИЛИ-НЕ и двенадцатого элемента И подключены соответственно к шестому по тринадцатый выходам блока управления, пятый вход которого подключен к синхровходам всех триггеров блока управления.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| То же, fig | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-11-27—Публикация

1993-05-14—Подача