(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления свертки | 1988 |

|

SU1587539A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024933C1 |

| Устройство для умножения матрицы на вектор | 1990 |

|

SU1737463A1 |

| Устройство для вычисления двумерной свертки | 1988 |

|

SU1573460A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1721612A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N X N)-МАТРИЦЫ | 1992 |

|

RU2012050C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1994 |

|

RU2049351C1 |

| Устройство для вычисления собственных значений ( @ @ @ ) - матрицы | 1989 |

|

SU1721611A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1989 |

|

SU1644160A1 |

| Матричное устройство для вычисления свертки | 1986 |

|

SU1401477A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных специализированных вычислительных машинах и устройствах обработки сигналов для вычисления свертки (фильтрации с бесконечной импульсной характеристикой). Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство содержит матрицу lx max(Po, Pi) вычислительных модулей, где I - размерность выходного вектора YI (i - 0,1-1), Ро и Pi -соответственно размерности векторов ве- совых коэффициентов а) (I) 0, Ро-1) и n (I 3i, PI), причем каждый вычислительный модуль содержит семь регистров, умножитель, сумматор, два триггера, четыре группы элементов И и группу элементов ИЛИ. В основу работы устройства положена параллельно-поточная организация вычислений. 2 ил., 3 табл.

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных специализированных вычислительных машинах и устройствах обработки сигналов для вычисления свертки (фильтрации с бесконечной импульсной характеристикой).

Целью изобретения является сокращение аппаратурных затрат.

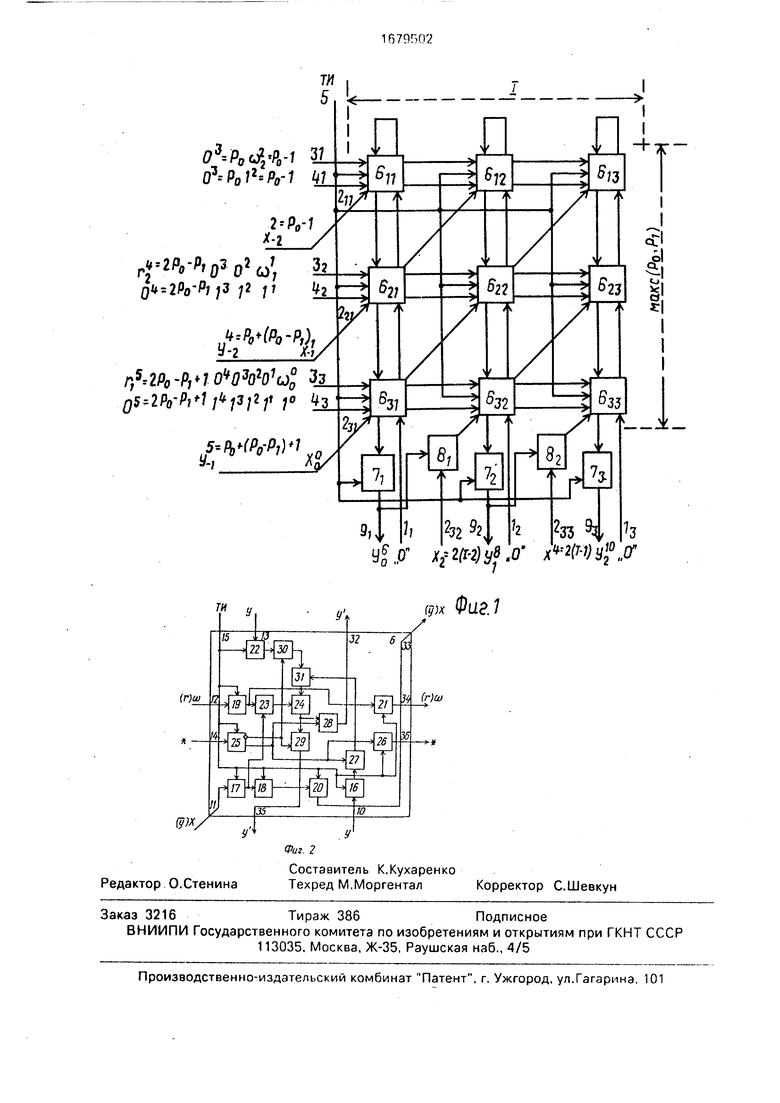

На фиг. 1 приведена структурная схема устройства для вычисления свертки (I 3, Р0 3, Pi 2); на фиг. 2-функциональная схема вычислительного модуля (I, Р0 и PI - соответственно размерности вектора выходных отсчетов V, векторов весовых коэффициентов а) и г).

Устройство для вычисления свертки содержит первую группу информационных входов 1, вторую группу информационных входов 2, третью группу информационных входов 3, настроечный вход 4| (I 1, max(Po, Pi), синхровход 5, вычислительные модули 6ij 0 1. О- регистры J7j 0 1,1) группы элементов ИЛИ 8j 0 1, I) и группу выходов 9,0 1.1).

Вычислительный модуль 6 содержит первый информационный вход 10 второй информационный вход 11, третий информационный вход 12, четвертый информационный вход 13, настроечный вход 14, синхровход 15, регистры 16 - 22 умножитель 23, сумматор 24, триггеры 25 и 2t группы элементов И 27 - 30, группу эле юнтов

О

VI ю ел о

го

ИЛИ 31, первый информационный выход32, второй информационный выход 33, третий информационный выход 34, четвертый информационный выход 35 и настроечный выход 36.

Свертка (фильтрация с бесконечной импульсной характеристикой) определяется формулой

ЈЬ-1Pi

Yi + 2 rpYf-p, ,1-1 (1) р 1

Разобьем задачу (1) на две подзадачи

УР Xi-p.(2)

р о

и

Р1

(3)

вычислении значений YI для I u.i-i, /.i

о. z,; z, шрхий,-z,p°- p-o; , YI(O Zi. Yi(p) Y, 1 + rpYi-p, Yi Y( рЛ

Y, Z,+Ј rp Y,-p

p 1

Представим подзадачи (2) и (3) в виде следующих рекуррентных соотносивший пои вычислении значений YI для I 0.1-1, Zi

ZI(PO -fl- p - q;

rpYi-p,Yi Y((

p 1, Pi, которые положены в основу работы устройства.

При описании работы устройства в обозначении Z™ индекс I в скобках указывает номер рекуррентного шага, а в обозначении Z1 индекс i без скобок - номер такта работы устройства.

Рассмотрим работу вычислительного модуля 6. Вычислительный модуль 6 работает в двух режимах. Первый режим работы задается единичным разрядом, котбрый подается на вход 14 и устанавливает триггер 25 в единичное состояние. При этом на входы 10, 11 и 12 подаются соответственно значения Y, X и о) , Значение Y записывается в регистр 16, с выхода которого через открытую группу элементов И 27 (с прямого выхода триггера 25 на первый вход группы элементов И 27 подается единичный сигнал), группу элементов ИЛИ 31 подается на вход сумматора 24. Значение X записывает- ся в регистр 17, с выхода которого подается на вход умножителя 23. Значение со записывается в регистр 19 и подается на вход умножителя 23, на выходе которого формируется значение .

На выходе сумматора 24 формируется значение Y1 Y + wX, которое через открытую группу элементов И 28 подается на выход 34 вычислительного модуля. Значение X подается на выход 33 с задержкой на два такта регистрами 18 и 20. Значение со подается на выход 34 с задержкой на один такт регистром 21. Настроечный сигнал задерживается также на один такт триггером 26.

5

5

0

0

5

5

0

0

5

Второй режим работы задается нулевым настроечным разрядом, который устанавливает триггер 25 в нулевое состояние. При этом группы элементов И 29 и 30 открываются, на входы 11, 12 и 13 подаются соответственно значения 9, г и Y, которые записываются соответственно в регистры 17, 19 и 22. На выходе умножителя 23 формируется значение rY, а на выходе сумматора 24 - значение Y1 Y + rY, которое подается через группу элементов И 29 на выход 35 вычислительного модуля. Значение Y задерживается на два такта регистрами 18 и 20, а значение г задерживается на один такт регистром 21.

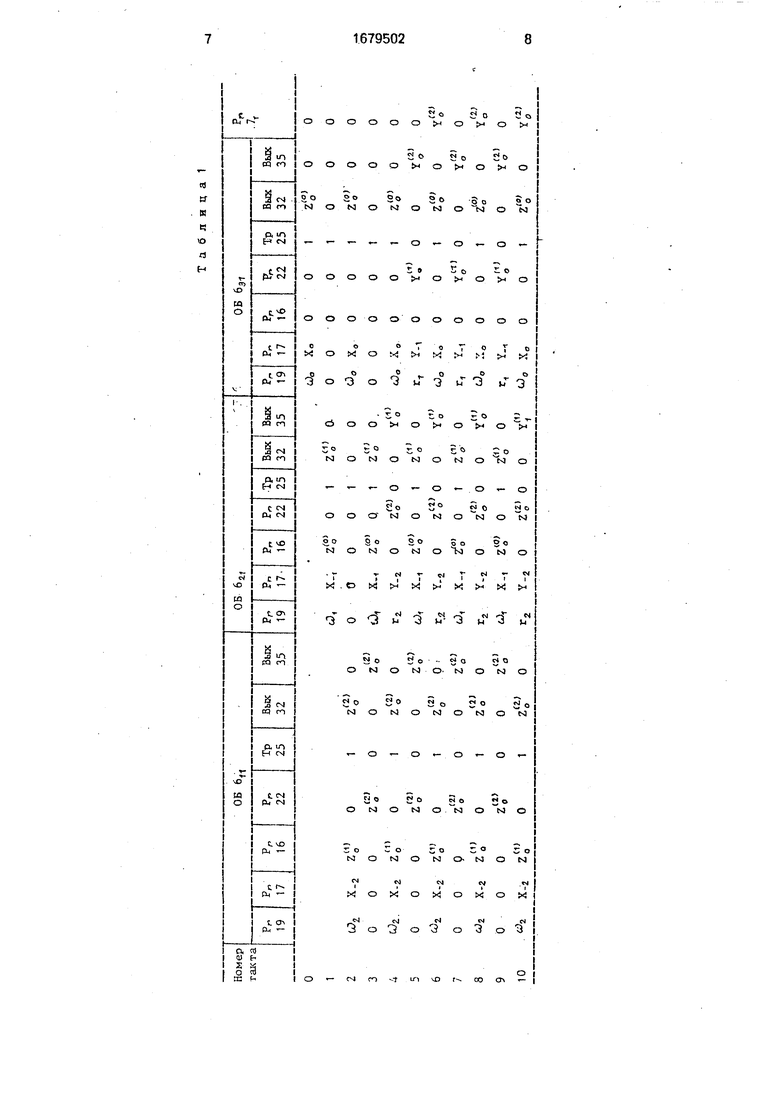

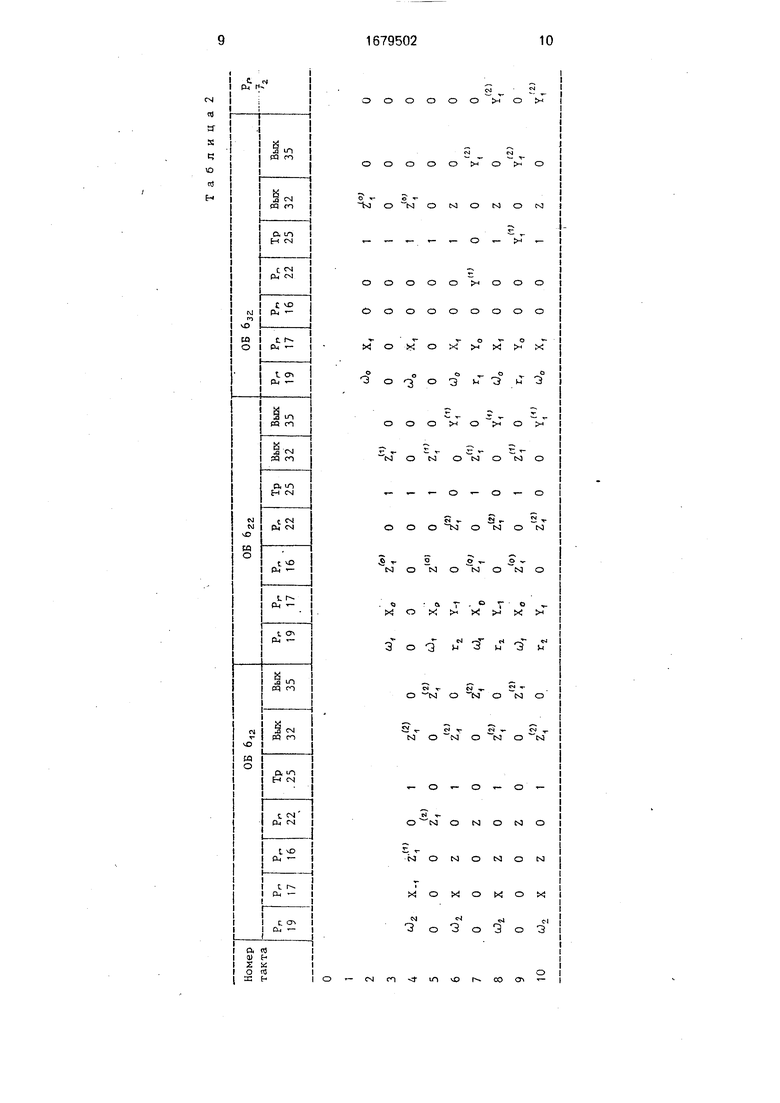

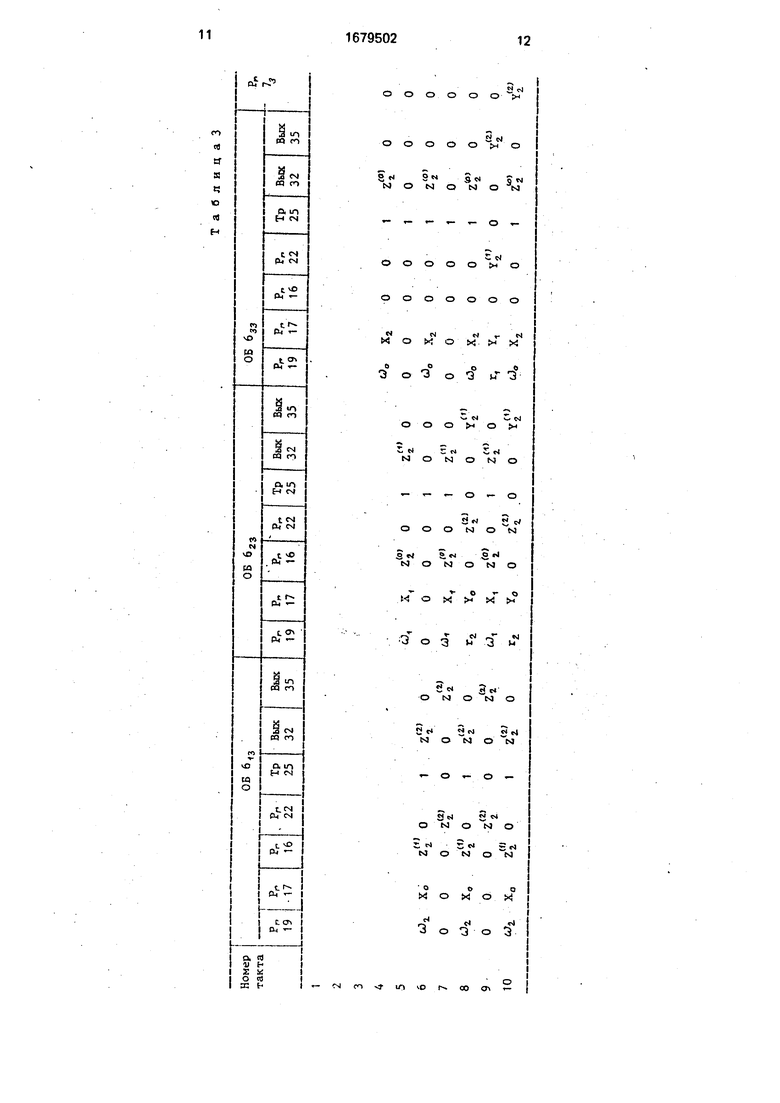

Рассмотрим работу устройства для I Ро 3 и Pi 2 (фиг. 1). Состояние регистров и триггеров вычислительных модулей устройства приведены в табл. 1, 2 и 3. Особенностью работы устройства является то, что только с элементами г подаются нулевые управляющие разряды. Кроме того, если Ро Pi, то на входы 3i, 32,..., ЗР0 - Pi подаются нулевые значения вместе с нулевыми настроечными разрядами соответственно в моменты времени Ро, Ро + 1,..., Ро + (Ро + Pi -1).

Если РО Pi, то на входы 3i. 323pi - РО

подаются нулевые значения с единичным настроечным разрядом в моменты времени

Ро. Ро+ 1Po + (Pi-Po-1). В данном случае

Ро 3, Pi 2 (Ро Pi), и на вход 31 подается на третьем такте (Ро 3) нулевое значение, а на вход 4i - нулевой разряд.

Рассмотрим формирование значения YO. На нулевом такте на вход 2з1 подается элемент Хо, на вход Зз - элемент Шо , а на вход 4з - единичный разряд. При этом в вычислительном модуле 6з1 формируется значение Zo Z(r + ufc X0. На первом такте на вход 221 подается элемент Х-ь на вход 32 - элемент , а на вход 42 - единичный разряд. В вычислительном модуле 621 формируется значение Zo + л X-i. На втором такте на вход 2ц подается элемент Х-2, на вход 3i - значение ok а на вход 4i - единичный разряд. В вычислительном модуле 6ц формируется значение Yo Zo Zo + ftfc X-2. которое с выхода 32 вычислительного модуля 6ц подается на вход 13 вычислительного модуля 6ц. На третьем такте на вход 3i. 4i и 2ц вычислительного модуля 6iГ подаются нулевые значения, при этом на выходе 35 формируется значение Yo . На четвертом такте на вход 32 подается значение п, на вход 42 - нулевой разряд, а на вход 221 - значение Y-2 . При этом в вычислительном модуле 621 формируется значение Yo + r2Y-2. На пятом такте на вход 2з1 подается значение Y-i, на вход Зз - значение п, на вход 4з - нулевой

разряд. При этом в вычислительном модуле 6з1 формируется значение Yo Yo® Ytr1 + nY-1, которое задерживается регистром 7i на один такт и подается на выход 91 устройства на шестом такте. Значения YI и Ya формируются аналогичным образом в соответствии с табл. 2 и 3 и выдаются соответственно на выходы 92 и 9з устройства.

Значение YI формируется на выходе 91 устройства на (2max(Po, PI) + 21)-м такте. Время вычисления всех значений YI (I О, И) устройством равно 2max(Po, Pi) + 21-1 тактов. Период ввода элементов в поточном режиме для вычисления свертки равен двум тактам (в табл. 1,2 и 3 приведены состояния регистров и триггеров в поточном режиме для вычисления свертки).

Формула изобретения Устройство для вычисления свертки, содержащее матрицу I x J вычислительных модулей и I регистров (J max(Po, Pi); I, Po и Pi - соответственно размерности вектора выходных отсчетов Y, векторов весовых коэффициентов ft) и г), причем 1-й информационный вход первой группы устройства (i f, 1) подключен к первому информационному входу (J. 1)--го вычислительного модуля матрицы, первый информационный вход Q, вычислительного модуля матрицы (| 1, J - 1) подключен к первому информационному выходу 0 + 1. вычислительного модуля матрицы, (к, 1)-й информационный вход второй группы устройства подключен к второму информационному входу (k,1)-rq вычислительного модуля матрицы (k 1, и);второй информационный выход (I, т)-тр вычисли,- те ль но го модуля матрицы (I 2, J, m 1,1-1) подключен к второму информационному входу (С-1, m+1)-ro вычислительного модуля матрицы, k-й информационный вход третьей группы устройства подключен к третьему информационному входу (k, 1)-го вычислительного модуля матрицы, третий информационный выход (k, вычислительного модуля матрицы подключен к третьему информационному входу (k, m+1)- го вычислительного модуля матрицы, синх- ровход устройства подключен к синхровходам всех вычислительных модуи

лей матрицы и всех регистров, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит 1-1 групп элементов ИЛИ, причем первый

5 информационный выход (1, i}-ro вычислительного модуля матрицы подключен к его четвертому информационному входу, четвертый информационный выход (j, i}-ro вычислительного модуля матрицы подключен

10 к четвертому информационному входу (J+1, }-го вычислительного модуля матрицы, четвертый информационный выход (J, l)-ro вычислительного модуля матрицы подключен к информационному входу 1-го регистра, вы15 ход которого подключен к i-му выходу группы устройства, выходы т-го регистра подключены к первым входам элементов ИЛИ m-й группы, вторые входы и выходы которых подключены соответственно к (J,

20 т+1)-м информационным входам второй группы устройства и к вторым информационным входам (J, т+1)-то вычислительного модуля матрицы, k-й настроечный вход устройства подключен к настроечному входу (k,

25 1)-го вычислительного модуля матрицы, настроечный выход (k, m)-ro вычислительного модуля матрицы подключен к настроечному входу (k, m+1}-ro вычислительного модуля матрицы, причем каждый вычислительный

30 модуль матрицы выполнен с возможностью реализации функции

br+3 br

с r+1 cr

d r+1 dr + crbr,e™H cf 0

a/r+1 ar + crbr, если d 1, где аг, Ьг, сг и dr - значения на первом, втором, третьем и четвертом информацион- 40 ных входах вычислительного модуля на г-м такте;

а/г, b r, с г и d r - значения на первом, втором, третьем и четвертом информационных выходах вычислительного модуля на г- 45 мтакте;

d и ft - значение на настроечных входе и выходе вычислительного модуля на г-м такте соответственно.

35

6

f1

Тр 25

02

О

CJ2

О

О

CJ2 о

Л

Х-2

о

Х-2

о

Х-2

о

Х-2

о

Х-2

)

. И)

7«D

7П) о

О 1

Zf2 ь о

Zf21

О

z(2J

L о

z(2

о

1 О 1 О 1 О

1 о 1

22

Тр 25

7f2

L a

О

-,(2) о

О

2)

О

Z. о

О

z z

-о

о z(Z)

i. о

z(i)

о

о

ZC2) о

О

)

о О

еЭ, О

iO,

г М г.2 Ji

Г2

Х- , О

Х-, Y-2 Х-, Y.s Х-, Y.2 Ч Х-, г, Y-2

„(0) 6 и

Z f О

О -

ео ел о ю

со

I

iт

DР

г | Zf

19 | -17

03-Pnd P0-i 3L

0 W2 T0

«

2 P0-J -2

-J ZVVoV,

2P0-P;;3 /2/7 1/2.

±1/

r lPo-Pi loWo1 Зз 05 2P0-/W/ ;3/27f ;o 3

(PfPi} 1

(г)а

№/

+Y

c

9fjT Xf2(1-2)yf.o W)y.ff

wx Фаг 7

(г)ш

| Кунг Х.Т | |||

| Вычисления на СБИС | |||

| Системы параллельной обработки | |||

| - М.: Мир, 1985, с | |||

| Телефонная трансляция с местной цепью для уничтожения обратного действия микрофона | 1924 |

|

SU348A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Устройство для вычисления свертки | 1988 |

|

SU1587539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

Авторы

Даты

1991-09-23—Публикация

1989-05-10—Подача