Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов.

Известны устройства, осуществляющие суммирование (и вычитание) нескольких чисел по модулю три. Недостатками их являются ограниченные функциональные возможности и невысокое быстродействие.

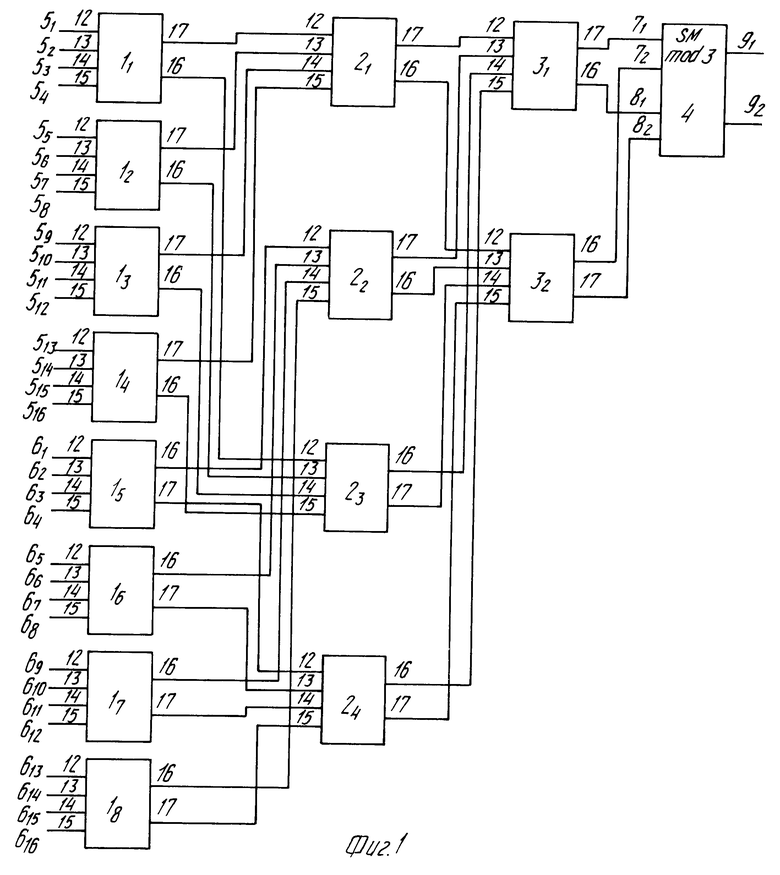

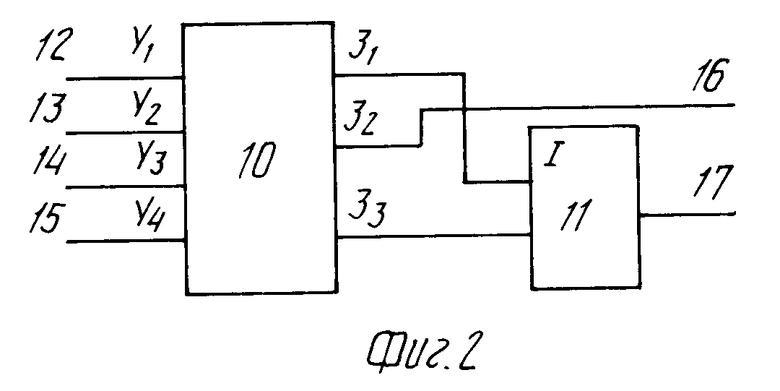

На фиг. 1 представлена функциональная схема устройства для сложения и вычитания шестнадцати чисел по модулю три; на фиг.2 функциональная схема логической ячейки.

Устройство для сложения и вычитания шестнадцати чисел по модулю три (см. фиг. 1) содержит три линейки логических ячеек, первая из которых содержит восемь логических ячеек 11.18, вторая четыре логических ячейки 21.24 и третья две логических ячейки 31 и 32, сумматор по модулю три 4, входы старших 51. 516 и младших 61.616 разрядов входных операндов, выходы старшего 91 и младшего 92 разрядов результата.

Логическая ячейка (см. фиг. 2) содержит четырехвходовый одноразрядный сумматор 10, элемент ИЛИ 11, четыре входа 12.15 и два выхода 16 и 17, причем выход 16 выход старшего разряда, а выход 17 выход младшего разряда.

В m-й ( (m=  )) логической ячейке первой линейки предложенного устройства j-й ( (j=

)) логической ячейке первой линейки предложенного устройства j-й ( (j= )) вход соединен с входом старшего разряда [(j+4(m-1)] -го операнда, младший разряд которого соединен с j-м входом (m+4)-й логической ячейки первой линейки. В первой логической ячейке второй линейки j-й вход соединен со вторым выходом j-й логической ячейки второй линейки, первый выход которой соединен с j-м входом третьей логической ячейки второй линейки. В второй логической ячейке второй линейки j-й вход соединен с первым выходом (j+4)-й логической ячейки первой линейки, второй выход которой соединен с j-м входом четвертой логической ячейки второй линейки.

)) вход соединен с входом старшего разряда [(j+4(m-1)] -го операнда, младший разряд которого соединен с j-м входом (m+4)-й логической ячейки первой линейки. В первой логической ячейке второй линейки j-й вход соединен со вторым выходом j-й логической ячейки второй линейки, первый выход которой соединен с j-м входом третьей логической ячейки второй линейки. В второй логической ячейке второй линейки j-й вход соединен с первым выходом (j+4)-й логической ячейки первой линейки, второй выход которой соединен с j-м входом четвертой логической ячейки второй линейки.

В первой логической ячейке третьей линейки r-й (r 1,2) вход соединен со вторым выходом r-й логической ячейки второй линейки, первый выход которой соединен с r-м входом второй логической ячейки третьей линейки, (r+2)-й вход которой соединен с вторым выходом (r+2)-й логической ячейки второй линейки, первый выход которой соединен с (r+2)-м входом первой логической ячейки третьей линейки, первый выход которой соединен с первым входом младшего разряда сумматора по модулю три, второй вход младшего разряда которого соединен с вторым выходом второй логической ячейки третьей линейки, первый выход которой соединен с вторым входом старшего разряда сумматора по модулю три, первый вход старшего разряда которого соединен с вторым выходом первой логической ячейки третьей линейки.

Входы 12-15 логической ячейки соединены соответственно с первым, вторым, третьим и четвертым входами четырехвходового одноразрядного сумматора 10, первый вход которого соединен с первым входом элемента ИЛИ 11, второй вход которого соединен с третьим выходом четырехвходового одноразрядного сумматора 10, второй выход которого соединен с первым выходом 16 логической ячейки, второй выход 17 которой соединен с выходом элемента ИЛИ 11.

Устройство для сложения и вычитания шестнадцати чисел по модулю три работает следующим образом.

На входы 51.516, 61.616 подаются полные операнды Хi 2х1i + х2i, где хji ∈0,1} j 1,2, i= и Хi ∈{0,1,2,3} Причем на входы 51.516 устройства подаются старшие разряды х1i, а на входы 61.616 младшие разряды х2i операндов.

и Хi ∈{0,1,2,3} Причем на входы 51.516 устройства подаются старшие разряды х1i, а на входы 61.616 младшие разряды х2i операндов.

На выходах 91 и 92 формируется двухразрядный двоичный код результата R 2r1 + r2 операций сложения и вычитания шестнадцати чисел по модулю три, ri ∈{ 0,1} i 1,2 и R ∈0,1,2} Причем на выходе 91 реализуется старший разряд r1, а на выходе 92 младший разряд r2 результата R.

Предлагаемое устройство реализует 216 операций сложения и вычитания вида:

R  X

X mod 3 (1)

mod 3 (1)

Выполняемая операция определяется путем соответствующей коммутации и старших и младших разрядов операндов на входах устройства, а именно: если i-й операнд Хi входит в уравнение (1) со знаком минус, то на входе устройства старший и младший разряд данного операнда меняются местами.

Укажем, что четырехвходовый одноразрядный сумматор 10, входящий в состав логической ячейки, работает следующим образом. На вход подаются одноразовые операнды Y1, Y2, Y3 и Y4, Yi ∈0,1} i= . На выходе формируется трехразрядный код результата S 22S1 + 2S2 + S3 суммы четырех одноразрядный чисел, Si ∈0,1} i 1,2 и S ∈0,1,2,3,4} Причем на первом выходе реализуется старший разряд S1, а на третьем выходе младший разряд S3 результата.

. На выходе формируется трехразрядный код результата S 22S1 + 2S2 + S3 суммы четырех одноразрядный чисел, Si ∈0,1} i 1,2 и S ∈0,1,2,3,4} Причем на первом выходе реализуется старший разряд S1, а на третьем выходе младший разряд S3 результата.

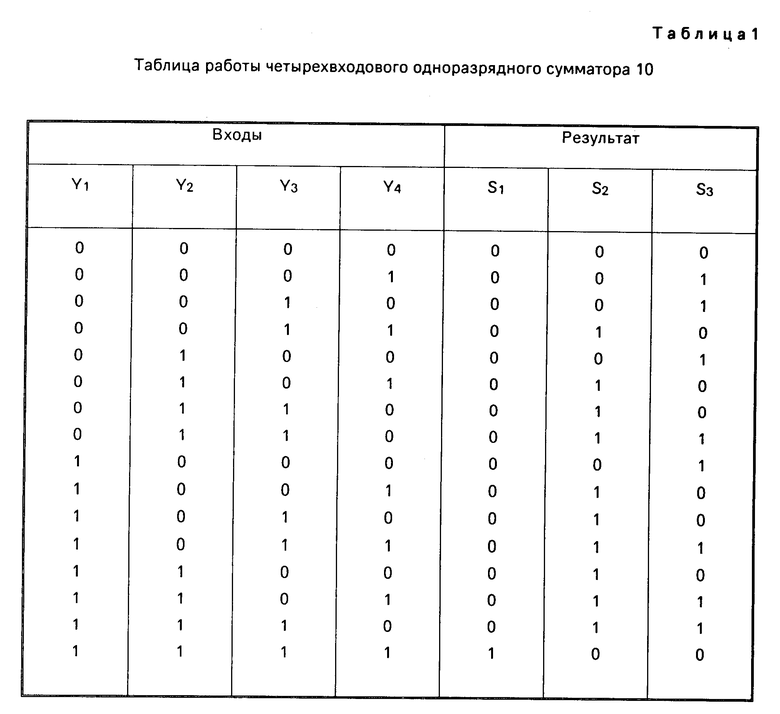

В качестве четырехвходового одноразрядного сумматора 10 может быть использован сумматор по авт.св. СССР N 1658145. Работа такого сумматора описывается в табл.1.

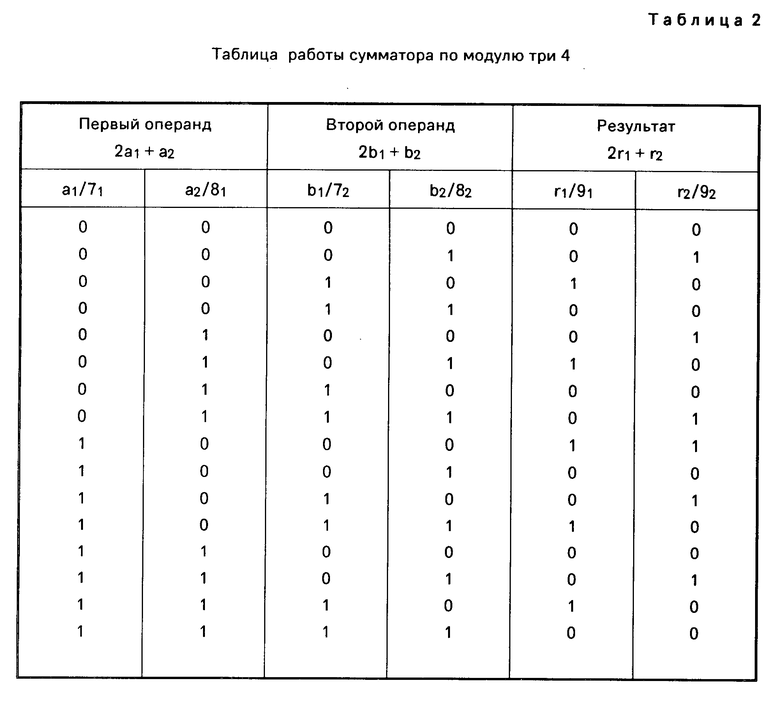

В качестве сумматора по модулю три 4, входящего в состав предложенного устройства, может быть использован сумматор, выполняющий сложение по модулю три двух полных операндов. Работа такого сумматора описывается в табл.2.

Устройство для сложения и вычитания шестнадцати чисел по модулю три построено с использованием следующего соотношения:

(2х1i + х2i) mod 3 (2х2i + х1i) mod 3, где i= .

.

Предлагаемое устройство выполняет 216 операций сложения/вычитания по модулю три над шестнадцатью двухразрядными операндами. По аналогии с ним может быть построено устройство для сложения и вычитания по модулю три произвольного числа операндов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018925C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018929C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ N ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2047897C1 |

| СУММАТОР ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018926C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2021630C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ТРИ | 1992 |

|

RU2045770C1 |

Изобретение относится к области вычислительной технике и микроэлектронике и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Устройство содержит сумматор по модулю три и четырнадцать логических ячеек, каждая из которых содержит четырехвходовый одноразрядный сумматор и элемент ИЛИ. Выполняемая операция определяется путем соответствующей коммутации старших и младших разрядов операндов на входах устройства. 2 ил. 2 табл.

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ШЕСТНАДЦАТИ ЧИСЕЛ ПО МОДУЛЮ ТРИ, отличающееся тем, что оно содержит три линейки логических ячеек,  из которых содержит li 24-i ячеек, j-й

из которых содержит li 24-i ячеек, j-й  логической ячейки первой линейки соединен с входом старшего разряда (j + 4(m - 1))-го операнда, если операнд положительный, или с входом младшего разряда этого операнда, если операнд отрицательный, j-й вход (m + 4)-й логической ячейки соединен с входом младшего разряда (j + 4 (m 1))-го операнда, если операнд положительный, или с входом старшего разряда этого операнда, если операнд отрицательный, j-й вход первой логической ячейки второй линейки соединен с вторым выходом j-й логической ячейки первой линейки, первый выход которой соединен с j-м входом третьей логической ячейки второй линейки, j-й вход второй логической ячейки второй линейки соединен с первым выходом (j + 4)-й ячейки первой линейки, второй выход которой соединен с j-м входом четвертой ячейки второй линейки, r-й

логической ячейки первой линейки соединен с входом старшего разряда (j + 4(m - 1))-го операнда, если операнд положительный, или с входом младшего разряда этого операнда, если операнд отрицательный, j-й вход (m + 4)-й логической ячейки соединен с входом младшего разряда (j + 4 (m 1))-го операнда, если операнд положительный, или с входом старшего разряда этого операнда, если операнд отрицательный, j-й вход первой логической ячейки второй линейки соединен с вторым выходом j-й логической ячейки первой линейки, первый выход которой соединен с j-м входом третьей логической ячейки второй линейки, j-й вход второй логической ячейки второй линейки соединен с первым выходом (j + 4)-й ячейки первой линейки, второй выход которой соединен с j-м входом четвертой ячейки второй линейки, r-й  вход первой логической ячейки третьей линейки соединен с вторым выходом r-й логической ячейки второй линейки, первый выход которой соединен с r-м входом второй логической ячейки третьей линейки, (r + 2)-й вход которой соединен с вторым выходом (r + 2)-й логической ячейки второй линейки, первый выход которой соединен с (r + 2)-м входом первой логической ячейки третьей линейки, первый выход которой соединен с первым входом младшего разряда сумматора по модулю три, второй вход младшего разряда которого соединен с вторым выходом второй логической ячейки третьей линейки, первый выход которой соединен с вторым входом старшего разряда сумматора по модулю три, первый вход старшего разряда которого соединен с вторым выходом первой логической ячейки третьей линейки, при этом логическая ячейка содержит четырехвходовый одноразрядный сумматор и элемент ИЛИ, первый вход которого соединен с первым выходом четырехвходового одноразрядного сумматора, второй выход которого соединен с первым выходом логической ячейки, второй выход которой соединен с выходом элемента ИЛИ, второй вход которого соединен с третьим выходом четырехвходового одноразрядного сумматора, j-й вход которого соединен с j-м входом логической ячейки, причем первый выход четырехвходового одноразрядного сумматора и первый выход логической ячейки - выходы их старших разрядов, а третий выход четырехвходового одноразрядного сумматора и второй выход логической ячейки выходы их младших разрядов.

вход первой логической ячейки третьей линейки соединен с вторым выходом r-й логической ячейки второй линейки, первый выход которой соединен с r-м входом второй логической ячейки третьей линейки, (r + 2)-й вход которой соединен с вторым выходом (r + 2)-й логической ячейки второй линейки, первый выход которой соединен с (r + 2)-м входом первой логической ячейки третьей линейки, первый выход которой соединен с первым входом младшего разряда сумматора по модулю три, второй вход младшего разряда которого соединен с вторым выходом второй логической ячейки третьей линейки, первый выход которой соединен с вторым входом старшего разряда сумматора по модулю три, первый вход старшего разряда которого соединен с вторым выходом первой логической ячейки третьей линейки, при этом логическая ячейка содержит четырехвходовый одноразрядный сумматор и элемент ИЛИ, первый вход которого соединен с первым выходом четырехвходового одноразрядного сумматора, второй выход которого соединен с первым выходом логической ячейки, второй выход которой соединен с выходом элемента ИЛИ, второй вход которого соединен с третьим выходом четырехвходового одноразрядного сумматора, j-й вход которого соединен с j-м входом логической ячейки, причем первый выход четырехвходового одноразрядного сумматора и первый выход логической ячейки - выходы их старших разрядов, а третий выход четырехвходового одноразрядного сумматора и второй выход логической ячейки выходы их младших разрядов.

| Барботажная ситчатая тарелка | 1955 |

|

SU118099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-12-20—Публикация

1992-04-29—Подача