Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов.

Известен сумматор по модулю три двух полных двухразрядных операндов, который содержит восемь элементов И, два элемента ИЛИ, два элемента ИЛИ-НЕ и два элемента сложения по модулю два [1].

Недостатком сумматора являются ограниченные функциональные возможности, так как он реализует только операцию сложения по фиксированному модулю, равному трем.

Наиболее близким техническим решением к предлагаемому является сумматор по модулю 2n-1, содержащий n элементов И, n элементов ИЛИ, n элементов ИЛИ-НЕ, n элементов РАВНОЗНАЧНОСТЬ и n элементов НЕРАВНОЗНАЧНОСТЬ [2].

Недостатком сумматора также являются ограниченные функциональные возможности, так как он не выполняет операций сложения и вычитания по модулю 2n-1 над тремя операндами.

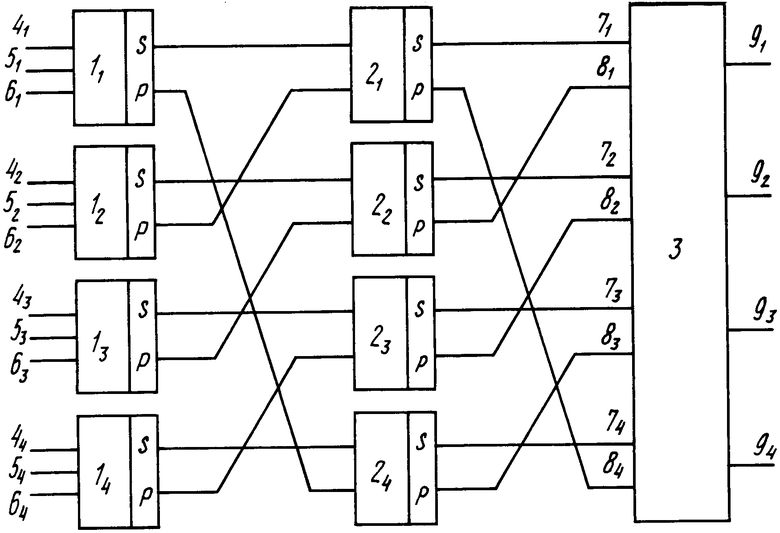

На чертеже в качестве примера представлена схема устройства для сложения и вычитания трех чисел по модулю 2n-1 при n = 4.

Устройство содержит n = 4 одноразрядных двоичных сумматоров 11...14, n = 4 полусумматоров 21...24, сумматор 3 по модулю 24 - 1 = 15, входы первого 41...44, второго 51...54 и третьего 61...64 операндов, причем входы 41, 51, 61 - входы старших, а входы 44, 54, 64 - входы младших разрядов операндов, выходы 91. ..94 результата, причем выход 91 - выход старшего, а выход 94 - выход младшего разряда результата.

В общем случае устройство для сложения и вычитания трех чисел по модулю 2n-1 содержит сумматор по модулю 2n-1, i-й (i =  выход которого соединен с i-м выходом устройства. В i-м одноразрядном двоичном сумматоре j-й (j = 1, 2, 3) вход соединен с входом i-го разряда j-го операнда. Выход суммы i-го одноразрядного двоичного сумматора соединен с первым входом i-го полусумматора, выход суммы которого соединен с входом i-го разряда первого операнда сумматора по модулю 2n-1. Выход переноса первого одноразрядного двоичного сумматора соединен с вторым входом n-го полусумматора, выход переноса (k+1)-го (k =

выход которого соединен с i-м выходом устройства. В i-м одноразрядном двоичном сумматоре j-й (j = 1, 2, 3) вход соединен с входом i-го разряда j-го операнда. Выход суммы i-го одноразрядного двоичного сумматора соединен с первым входом i-го полусумматора, выход суммы которого соединен с входом i-го разряда первого операнда сумматора по модулю 2n-1. Выход переноса первого одноразрядного двоичного сумматора соединен с вторым входом n-го полусумматора, выход переноса (k+1)-го (k =  одноразрядного двоичного сумматора - с вторым входом k-го полусумматора. Выход переноса первого полусумматора соединен с входом n-го разряда второго операнда сумматора по модулю 2n-1, выход переноса (k+1)-го полусумматора - с входом k-го разряда второго операнда сумматора по модулю 2n-1.

одноразрядного двоичного сумматора - с вторым входом k-го полусумматора. Выход переноса первого полусумматора соединен с входом n-го разряда второго операнда сумматора по модулю 2n-1, выход переноса (k+1)-го полусумматора - с входом k-го разряда второго операнда сумматора по модулю 2n-1.

При n = 4 входы первого одноразрядного двоичного сумматора 11соединены соответственно с входами 41, 51, 61, входы второго одноразрядного двоичного сумматора 12 - соответственно с входами 42, 52, 62, входы третьего одноразрядного двоичного сумматора 13 - соответственно с входами 43, 53, 63, входы четвертого одноразрядного двоичного сумматора 14 - соответственно с входами 44, 54, 64. Выход переноса первого одноразрядного двоичного сумматора 11 соединен с вторым входом четвертого полусумматора 24, первый вход которого соединен с выходом суммы четвертого одноразрядного двоичного сумматора 14. Выход переноса последнего соединен с вторым входом третьего полусумматора 23, первый вход которого соединен с выходом суммы третьего одноразрядного двоичного сумматора 13. Выход переноса сумматора 13 соединен с вторым входом второго полусумматора 22, первый вход которого соединен с выходом суммы второго одноразрядного двоичного сумматора 12. Выход переноса сумматора 12 соединен с вторым входом первого полусумматора 21, первый вход которого соединен с выходом суммы первого одноразрядного двоичного сумматора 11. Выход переноса первого полусумматора 21 соединен с входом 84 четвертого разряда второго операнда сумматора 3 по модулю пятнадцать, вход 74 четвертого разряда первого операнда которого соединен с выходом суммы четвертого полусумматора 24. Выход переноса полусумматора 24соединен с входом 83 третьего разряда второго операнда сумматора 3 по модулю пятнадцать, вход 73 третьего разряда первого операнда которого соединен с выходом суммы третьего полусумматора 23. Выход переноса полусумматора 23 соединен с входом 82 второго разряда второго операнда сумматора 3 по модулю пятнадцать, вход 72 второго разряда первого операнда которого соединен с выходом суммы второго полусумматора 22. Выход переноса полусумматора 22 соединен с входом 81 первого разряда второго операнда сумматора 3 по модулю пятнадцать, вход 71 первого разряда первого операнда которого соединен с выходом суммы первого полусумматора 21. Выходы первого, второго, третьего и четвертого разрядов сумматора 3 по модулю пятнадцать соединены с выходами первого 91, второго 92, третьего 93 и четвертого 94 разрядов результата соответственно.

Устройство для сложения и вычитания трех чисел по модулю 2n-1 при n = 4 работает следующим образом.

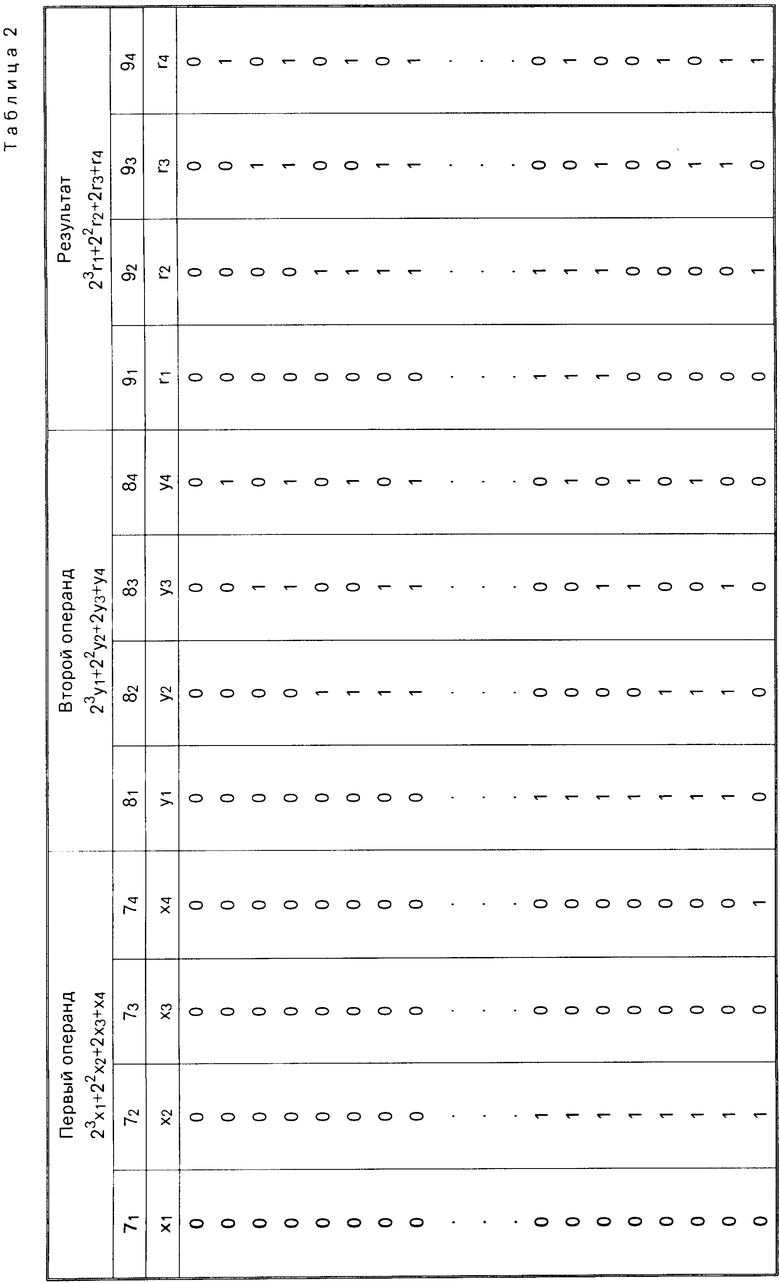

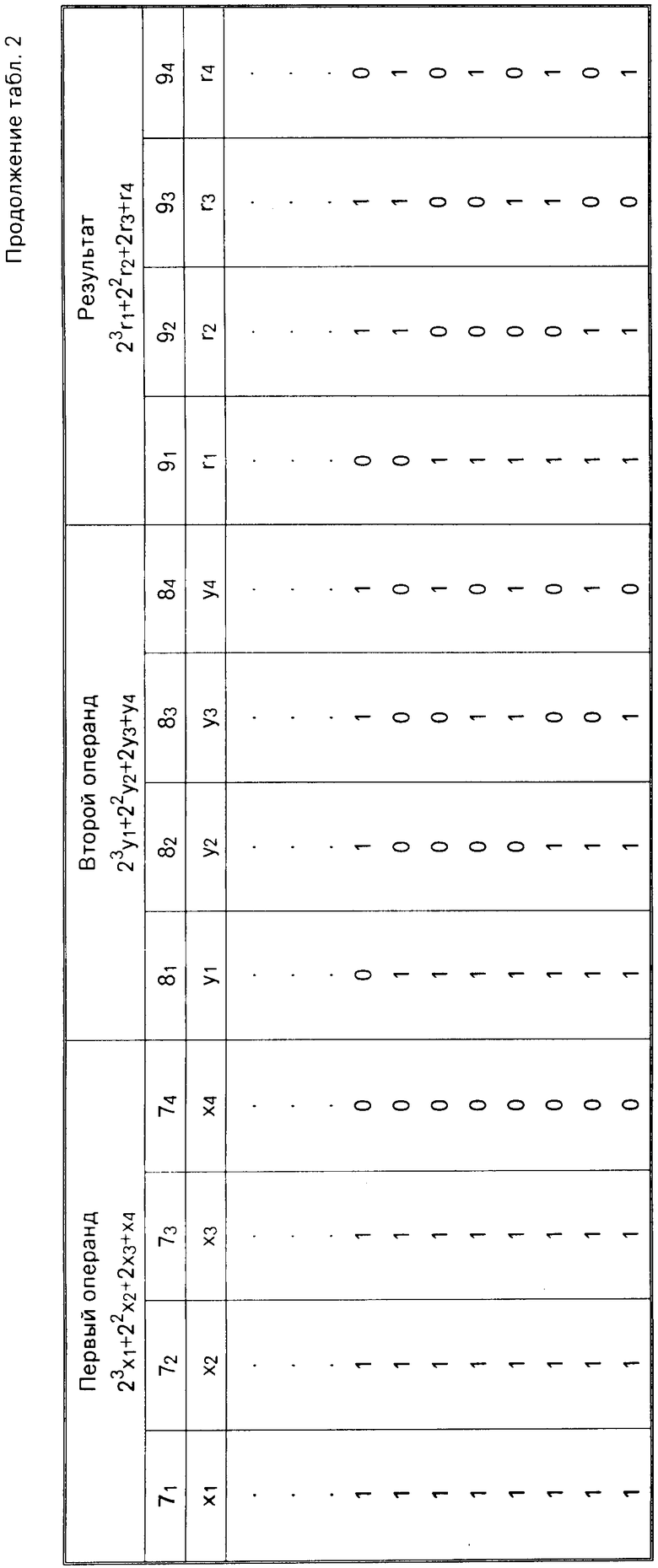

На входы 41...44, 51...54, 61...64 подаются соответственно четырехразрядные полные операнды Х = 23х1 + 22х2 + 2х3 + х3, Y = 23y1 + 22y2 + 2y3 + y4 и Z = 23z1 + 22z2 + 2z3 + z4, где xi ∈ {0,1}, yi∈ {0,1},zi ∈ {0,1}, i =  , X =

, X = , Y =

, Y =  и z =

и z =  .

.

На выходах 91...94 формируется четырехразрядный двоичный код результата R = =23r1 + 22r2 + 2r3 + r4 операций сложения и вычитания трех чисел X, Y и Z по модулю пятнадцать, ri ∈ {0,1}, i =  и R =

и R =  . Причем на выходе 91 реализуется старший разряд r1, а на выходе 94 - младший разряд r4 результата R.

. Причем на выходе 91 реализуется старший разряд r1, а на выходе 94 - младший разряд r4 результата R.

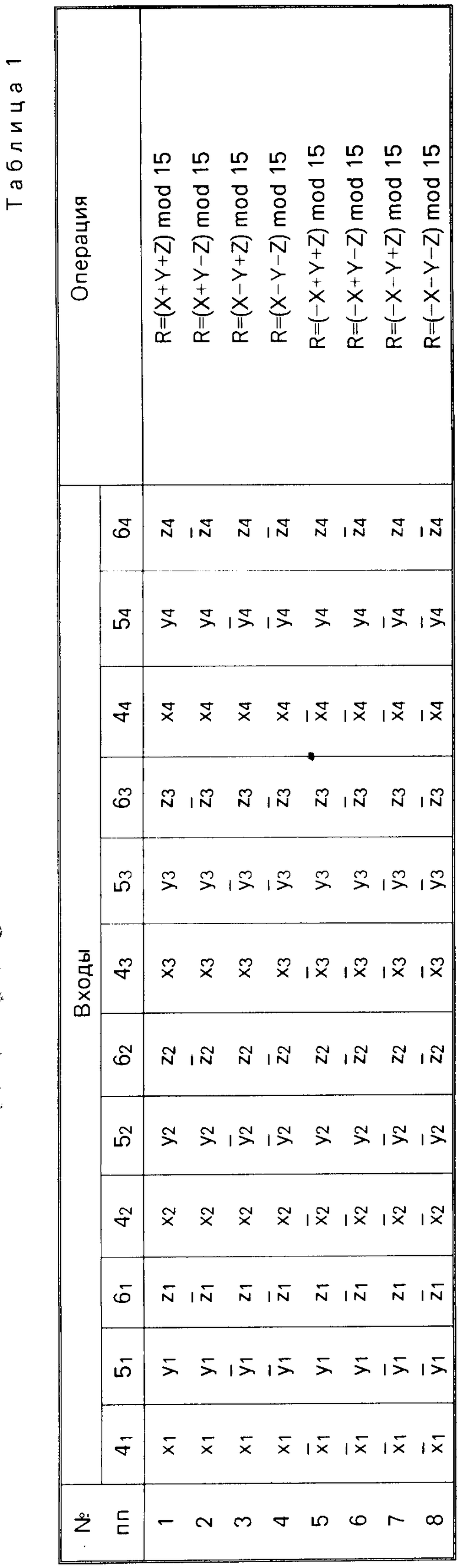

Предлагаемое устройство реализует восемь операций сложения и вычитания вида

R = ( ±X±Y±X) mod (2n-1)

Выполняемая операция определяется путем соответствующей коммутации прямых и обратных кодов операндов на входах устройства, как это указано в табл. 1 для n = 4.

Устройство для сложения и вычитания трех чисел по модулю 2n-1 построено с использованием следующего соотношения:

(-X) mod (2n-1) =  mod (2n-1) ,, где X =

mod (2n-1) ,, где X = 2n-ixi.

2n-ixi.

Отметим, что в качестве сумматора 3, входящего в состав заявляемого устройства, может быть использован сумматор, выполняющий сложение по модулю 2n-1 двух приведенных операндов, значения которых меньше значения модуля. Работа такого сумматора при n = 4 описывается табл.2.

Достоинством заявляемого устройства являются широкие функциональные возможности. Так, предлагаемое устройство выполняет восемь операций сложения-вычитания по модулю 2n-1 над тремя n-разрядными операндами. Известные устройства такими возможностями не обладают.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018929C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| СУММАТОР ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018926C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ШЕСТНАДЦАТИ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2050584C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ N ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2047897C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| МНОГОВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР | 1992 |

|

RU2047216C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ТРИ | 1992 |

|

RU2045770C1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано для построения средств аппаратурного контроля и цифровых устройств, работающих в системе остаточных классов. Устройство содержит сумматор двух чисел по модулю 2n-1 (n=2, 3, ...), n одноразрядных двоичных сумматоров и n полусумматоров. На его входы подаются n-разрядные полные операнды X, Y и Z. На выходах формируется n-разрядный двоичный код результата R = (± X ± Y ± Z) mod (2n-1). . Выполняемая операция определяется путем соответствующей коммутации прямых и обратных кодов операндов на входах устройства. 2 табл., 1 ил.

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2n-1(n = 2, 3, . ..), содержащее сумматор по модулю 2n - 1, i-й (i= ) выход которого соединен с i-м выходом устройства, отличающееся тем, что содержит n полусумматоров и n одноразрядных двоичных сумматоров, j-й (j = 1, 2, 3) вход i-го из которых соединен с входом i-го разряда j-го операнда, выход суммы i-го одноразрядного двоичного сумматора соединен с первым входом i-го полусумматора, выход суммы которого соединен с входом i-го разряда первого операнда сумматора по модулю 2n - 1, выход переноса первого одноразрядного двоичного сумматора соединен с вторым входом n-го полусумматора, выход переноса (k + 1)-го (k=

) выход которого соединен с i-м выходом устройства, отличающееся тем, что содержит n полусумматоров и n одноразрядных двоичных сумматоров, j-й (j = 1, 2, 3) вход i-го из которых соединен с входом i-го разряда j-го операнда, выход суммы i-го одноразрядного двоичного сумматора соединен с первым входом i-го полусумматора, выход суммы которого соединен с входом i-го разряда первого операнда сумматора по модулю 2n - 1, выход переноса первого одноразрядного двоичного сумматора соединен с вторым входом n-го полусумматора, выход переноса (k + 1)-го (k= ) одноразрядного двоичного сумматора соединен с вторым входом k-го полусумматора, выход переноса первого полусумматора соединен с входом n-го разряда второго операнда сумматора по модулю 2n - 1, выход переноса (k + 1)-го полусумматора соединен с входом k-го разряда второго операнда сумматора по модулю 2n - 1.

) одноразрядного двоичного сумматора соединен с вторым входом k-го полусумматора, выход переноса первого полусумматора соединен с входом n-го разряда второго операнда сумматора по модулю 2n - 1, выход переноса (k + 1)-го полусумматора соединен с входом k-го разряда второго операнда сумматора по модулю 2n - 1.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сумматор по модулю 2 @ -1 | 1984 |

|

SU1156063A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-08-30—Публикация

1992-03-25—Подача