Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении устройств, работающих в системе остаточных классов.

Известен сумматор по модулю 2n-1, который содержит в каждом разряде элементы И, ИЛИ, ИЛИ-НЕ, РАВНОЗНАЧНОСТЬ и НЕРАВНОЗНАЧНОСТЬ [1].

Недостатком сумматора является невозможность выполнения сложения по модулю 2n+1.

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является сумматор по модулю 2n+1 при n = 2 (сумматор по модулю пять), содержащий пятнадцать элементов И, восемь элементов ИЛИ, три элемента ИЛИ-НЕ, элемент И-НЕ и элемент ЗАПРЕТ [2].

Недостатком известного сумматора по модулю 2n+1 являются низкие функциональные возможности, так как он не выполняет сложение чисел по модулю 2n+1 при n > 2.

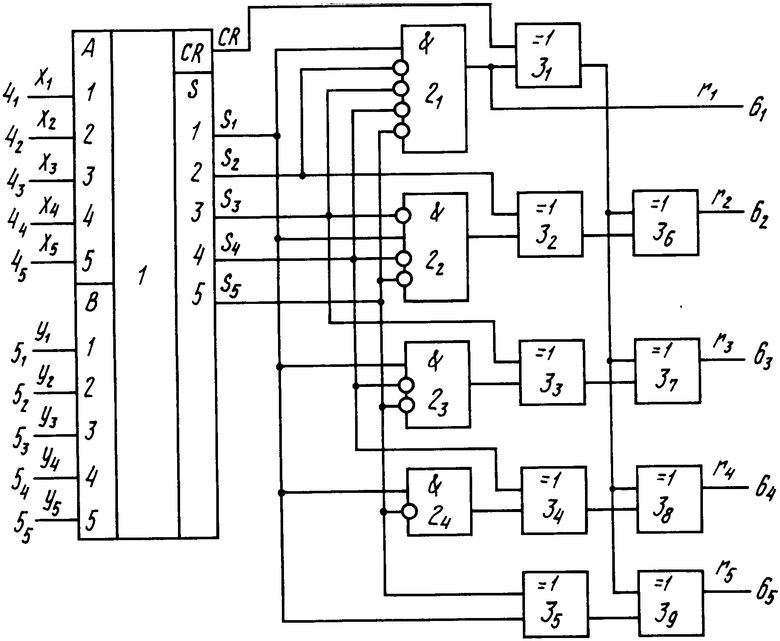

На чертеже представлена схема предлагаемого сумматора по модулю 2n+1 при n = 4.

При n = 4 сумматор по модулю 24 + 1 = =17 содержит пятиразрядный двоичный сумматор 1, n = 4 элементов ЗАПРЕТ 21...24, 2n+1 = 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 31. . .39, n = 5 входов первого операнда 41...45, n = 5 входов второго операнда 51...55, n = 5 выходов 61...65.

В общем случае сумматор по модулю 2n+1 содержит n элементов ЗАПРЕТ, 2n+1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и (n+1)-разрядный двоичный сумматор, i-й (i = 1, 2) вход j-го (j= разряда которого соединен с j-м разрядом i-го операнда. Выход переноса (n+1)-разрядного двоичного сумматора соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента ЗАПРЕТ и первым выходом сумматора по модулю 2n+1. Выход первого элемента ЗАПРЕТ соединен с первым входом (k+1)-го (k=

разряда которого соединен с j-м разрядом i-го операнда. Выход переноса (n+1)-разрядного двоичного сумматора соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента ЗАПРЕТ и первым выходом сумматора по модулю 2n+1. Выход первого элемента ЗАПРЕТ соединен с первым входом (k+1)-го (k=  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с (k+1)-м выходом сумматора по модулю 2n+1, а второй вход - с выходом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Первый вход (n + l + +1)-го (l=

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с (k+1)-м выходом сумматора по модулю 2n+1, а второй вход - с выходом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Первый вход (n + l + +1)-го (l= элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом (l+1)-го элемента ЗАПРЕТ. Выход первого разряда суммы (n+1)-разрядного двоичного сумматора соединен с прямым входом k-го элемента ЗАПРЕТ и первым входом (2n+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход (k+1)-го разряда суммы (n+1)-го разрядного двоичного сумматора соединен с вторым входом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и (k - s + 1)-м входом запрета (s=

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом (l+1)-го элемента ЗАПРЕТ. Выход первого разряда суммы (n+1)-разрядного двоичного сумматора соединен с прямым входом k-го элемента ЗАПРЕТ и первым входом (2n+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход (k+1)-го разряда суммы (n+1)-го разрядного двоичного сумматора соединен с вторым входом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и (k - s + 1)-м входом запрета (s= s-го элемента ЗАПРЕТ.

s-го элемента ЗАПРЕТ.

Сумматор по модулю 2n+1 работает следующим образом.

На входы (n+1)-разрядного двоичного сумматора поступают (n+1)-разрядные операнды X = 2nx1 + 2n-1x2 +...+xn+1 и Y = 2ny1 + 2n-1y2+...+Yn+1, значения которых принадлежат множеству {0, 1,...,2}, Xj ∈ {0, 1}, Yj ∈ {0, 1}, j =  . На выходе (n+1)-разрядного двоичного сумматора вычисляется сумма S = X + Y = 2n+1 CR + 2ns1 + 2n-1s2 +...+ sn+1. Причем CR ∈ {0, 1} - сигнал переноса и S ∈ {0, 1,...,2n+1}, sj∈ {0, 1},j=

. На выходе (n+1)-разрядного двоичного сумматора вычисляется сумма S = X + Y = 2n+1 CR + 2ns1 + 2n-1s2 +...+ sn+1. Причем CR ∈ {0, 1} - сигнал переноса и S ∈ {0, 1,...,2n+1}, sj∈ {0, 1},j= .

.

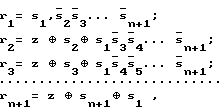

Двоичные разряды результата операции сложения по модулю 2n+1 входных операндов R = X + Y mod (2n+1) = 2nr1 + 2n-1r2 +...+ rn+1формируются комбинационной схемой из сигнала CR и Sj согласно следующим соотношениям: (1) где z = r1⊕ CR

(1) где z = r1⊕ CR

Так, при n = 4 на входы 41...45 и 51...55 пятиразрядного двоичного сумматора 1 поступают пятиразрядные операнды X = =16x1 + 8x2 + 4x3 + 2x4+ x5 и Y = 16y1 + 8y2 + +4y3 + 2y4 + y5 соответственно. При этом 0 ≅ Х ≅ 16, 0≅ Y≅16 xt ∈ {0, 1}, Yt ∈ {0, 1},t= . На выходе двоичного сумматора 1 вычисляется сумма S = X + Y = 32CR + 16s1 + + 8s2 + 4s3 + 2s4 + s5. Причем 0 ≅S ≅32, CR ∈ {0, 1}, st∈ {0, 1},t=

. На выходе двоичного сумматора 1 вычисляется сумма S = X + Y = 32CR + 16s1 + + 8s2 + 4s3 + 2s4 + s5. Причем 0 ≅S ≅32, CR ∈ {0, 1}, st∈ {0, 1},t= .

.

Как следует из соотношений (1), двоичные разряды результата операции сложения по модулю семнадцать R = X + Y mod 17= = 16r1 + 8r2 + 4r3 + 2r4 + r5 формируются комбинационной схемой из сигналов CR и stсогласно следующим соотношениям:

r1= s1, ;

;

r2= z ⊕ s2⊕ s ;

;

r3= z ⊕ s3⊕ s ;

;

r4=z ⊕ s4⊕ s ;

;

r5= z ⊕ s5⊕ s1, где z = r1⊕ CR.

Достоинством предлагаемого сумматора по модулю 2n+1 является высокое быстродействие и простая конструкция.

Быстродействие заявляемого сумматора по модулю 2n+1 не зависит от величины модуля и определяется выражением

T = tsм + 3t, где tsм - быстродействие (n+1)-разрядного двоичного сумматора;

t - задержка на вентиль.

Сигнал переноса CR в (n+1)-разрядном двоичном сумматоре может быть сформирован двухвходовым элементом И согласно соотношению CR = x1y1, поскольку X ≅2n и Y ≅ 2n. Кроме того, при использовании инверсного значения  первого разряда суммы (n+1)-разрядного двоичного сумматора элементы ЗАПРЕТ могут быть однозначно заменены элементами ИЛИ-НЕ без изменения связей в предлагаемом сумматоре по модулю 2n+1.

первого разряда суммы (n+1)-разрядного двоичного сумматора элементы ЗАПРЕТ могут быть однозначно заменены элементами ИЛИ-НЕ без изменения связей в предлагаемом сумматоре по модулю 2n+1.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018929C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018925C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ШЕСТНАДЦАТИ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2050584C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018923C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ N ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2047897C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ТРИ | 1992 |

|

RU2045770C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 1992 |

|

RU2018927C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2028660C1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении устройств, работающих в системе остаточных классов. Сумматор по модулю 2n+1 содержит (n+1)-разрядный двоичный сумматор, n элементов ЗАПРЕТ и 2n+1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. На его входы потупают (n+1)-разрядные приведенные операнды X и Y, значения которых принадлежат множеству { 0, 1 ..., 2n}. На выходах формируется (n+1)-разрядный двоичный код результата операции сложения по модулю 2n+1 входных операндов R = X + Y mod (2n+1).. Достоинством сумматора по модулю 2n+1 является высокое быстродействие и простая конструкция. 1 ил.

СУММАТОР ПО МОДУЛЮ 2n+1, содержащий первый элемент ЗАПРЕТ, отличающийся тем, что содержит элементы ЗАПРЕТ с второго по n-й, 2n + 1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и (n + 1)-разрядный двоичный сумматор, i-й (i = 1, 2) вход j-го (j= ) разряда которого соединен с j-м разрядом i-го операнда, выход переноса (n + 1)-разрядного двоичного сумматора соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента ЗАПРЕТ и первым выходом сумматора по модулю 2n + 1, а выход соединен с первым входом (k + 1)-го (k=

) разряда которого соединен с j-м разрядом i-го операнда, выход переноса (n + 1)-разрядного двоичного сумматора соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого элемента ЗАПРЕТ и первым выходом сумматора по модулю 2n + 1, а выход соединен с первым входом (k + 1)-го (k= ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с (k + 1)-м выходом сумматора по модулю 2n + 1, а второй вход соединен с выходом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход (n + l + 1)-го (l=

) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с (k + 1)-м выходом сумматора по модулю 2n + 1, а второй вход соединен с выходом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход (n + l + 1)-го (l= ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом (l + 1)-го элемента ЗАПРЕТ, выход первого разряда суммы (n + 1)-го разрядного двоичного сумматора соединен с прямым входом k-го элемента ЗАПРЕТ и первым входом (2n + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход (k + 1)-го разряда суммы (n + 1)-разрядного двоичного сумматора соединен с вторым входом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и (k - s + 1)-м входом запрета (s=

) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом (l + 1)-го элемента ЗАПРЕТ, выход первого разряда суммы (n + 1)-го разрядного двоичного сумматора соединен с прямым входом k-го элемента ЗАПРЕТ и первым входом (2n + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход (k + 1)-го разряда суммы (n + 1)-разрядного двоичного сумматора соединен с вторым входом (n + k + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и (k - s + 1)-м входом запрета (s= ) s-го элемента ЗАПРЕТ.

) s-го элемента ЗАПРЕТ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сумматор по модулю пять | 1988 |

|

SU1566342A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-08-30—Публикация

1992-03-26—Подача