Изобретение относится к автоматике и вычислительной технике и может быть использовано в корреляционно-экстремальных системах.

Известен цифровой коррелятор, содержащий N-разрядную (по числу каналов) цифровую линию задержки, первый и второй триггеры, первый элемент ИЛИ, а также в каждом канале блок умножения канальный счетчик, канальный элемент ИЛИ и канальный элемент И, преобразователь кода, первый и второй регистры, вычитающий счетчик, делитель частоты, ключ, переключатель, элемент И, второй элемент ИЛИ и блок управления, первый вход которого подключен к выходу первого элемента ИЛИ, первый выход блока управления соединен с управляющими входами регистров, установочные входы которого соединены с первым входом второго элемента ИЛИ, а также с первым входом первого триггера и подключены к второму выходу блока управления, третий выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом второго триггера и установочными входами вычитающего счетчика и делителя частоты, счетный вход которого объединен с информационным входом ключа и подключен к четвертому выходу блока управления, управляющий вход ключа объединен с вторыми входами триггеров и подключен к выходу делителя частоты, выход ключа соединен с управляющим входом N-разрядной цифровой линии задержки, вход которой соединен с выходом переключателя, первый информационный и управляющий входы которого соединены соответственно с выходами N-разрядной цифровой линии задержки и выходом первого триггера, второй информационный вход переключателя является первым входом устройства, информационные входы первого регистра соединены с соответствующими разрядными выходами вычитающего счетчика, счетный вход которого подключен к выходу элемента И, информационные входы второго регистра соединены с соответствующими выходами преобразователя кодов, входы которого соединены с соответствующими входами первого элемента ИЛИ и подключены к выходам соответствующих канальных счетчиков всех каналов, установленные входы которых объединены и подключены к выходу второго элемента ИЛИ, счетный вход канального счетчика каждого канала подключен к выходу канального элемента И своего канала, первый вход канального элемента И каждого канала подключен к выходу канального элемента ИЛИ своего канала, вторые входы канальных элементов И всех каналов и первый вход элемента И объединены и подключены к четвертому выходу блока управления, второй и третий входы которого являются соответственно вторым и третьим входами устройства, первые входы канальных элементов ИЛИ всех каналов и второй вход элемента И объединены и подключены к выходу второго триггера, второй вход канального элемента ИЛИ каждого канала подключен к выходу блока умножения своего канала, первые входы блоков умножения всех каналов объединены и являются четвертым входом устройства, а вторые входы блоков умножения всех каналов подключены к выходам соответствующих разрядов N-разрядной цифровой линии задержки [1]

Недостатками данного устройства являются заметная структурная неоднородность и, следовательно, сложность, существенно ограниченное быстродействие (за счет ограничений по вспомогательным операциям в межстрочных паузах), невозможность использования, например, в устройстве по авт.св. СССР N 649172 при реверсе скорости движения изображения.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее счетчик, одновибратор, инвертор, канальные счетчики с подключенными на их входы канальными элементами И, элементы задержки, элементы И и ИЛИ, цифровую линию задержки и подключенные к ней первые входы канальных блоков умножения и переключатель, который соединен с первым и вторым входами устройства, а третий вход подключен к вторым входам канальных блоков умножения, канальные шинные формирователи, дешифратор, компаратор и два регистра, выходы канальных блоков умножения через канальные элементы И подключены к входам канальных счетчиков, выходы последних подключены через канальные шинные формирователи к первым входам компаратора и первого регистра, выходы последнего подключены к вторым входам компаратора и входам второго регистра, выход первого элемента И подключен к цепям управления цифровой линии задержки и вторым входам канальных элементов И, а первый вход первого элемента И и инвертора подключены к пятому входу устройства, выход инвертора подключен через третий элемент И к счетному входу счетчика, выходы которого соединены с соответствующими входами дешифратора и через третий регистр с входами четвертого регистра, выход переполнения счетчика соединен через элемент ИЛИ с входами обнуления канальных счетчиков, а вход обнуления подключен к пятому входу устройства, выходы дешифратора соединены с входами управления шинных формирователей, второй вход устройства соединен с входами управления второго и четвертого регистров, а также с вторым входом элемента ИЛИ и через одновибратор и элемент задержки с входом обнуления первого регистра, выход "больше" компаратора через второй элемент И подключен к управляющим входам первого и третьего регистров, а вторые входы элементов И подключены к четвертому входу устройства [2]

Недостатком обоих корреляторов является невозможность обеспечить измерения при реверсе движения изображения, являющегося источником сигналов, обрабатываемых корреляторами, а также пониженную помехоустойчивость при анализе изображения, например, не имеющего осевой симметрии автокорреляционной функции (обладающего, к примеру, определенной периодичностью по одной из координат). Следовательно, недостатками прототипа можно считать ограниченные помехоустойчивость и функциональные возможности.

Целью изобретения является повышение помехоустойчивости и расширение функциональных возможностей.

Эта цель достигается тем, что линия задержки организована для хранения информации кадрового разложения из К строк, например, изображения, цифровой коррелятор дополнен 2m канальными процессорами, подключенными к отводам линии задержки в районе стыков j, (j + 1) и (K + 1 j) и (K j), j 1,2.m строк, выход первого элемента ИЛИ подключен через второй вновь введенный инвертор к третьему входу второго элемента И.

Предложенное техническое решение обладает существенными отличиями от известных, так как новая организация линии задержки для хранения информации кадрового разложения позволяет ввести дополнительные канальные процессоры и ограничивать поиск экстремума взаимно-корреляционной функции при любом направлении движения источника входной информации (например, изображения, считываемого телевизионной камерой). Кроме того, новый цифровой коррелятор является низкочастотным фильтром при кадровой организации анализируемого источника входной информации, что определяет его помехоустойчивость, например, при анализе изображений, ФВК которых не обладает осевой симметрией. При строчной организации (как в аналогах и прототипе) это свойство цифрового коррелятора в кадровом направлении организовать невозможно.

Таким образом, предложенный коррелятор обладает новизной и существенными отличиями, расширяющими область его применения. Например, на его основе может быть создана система, следящая за движущимся изображением. Отличительными качествами такой системы являются инвариантность к источнику входной информации и большой объем обрабатываемой информации, гарантирующий высокую точность, чувствительность и надежность работы.

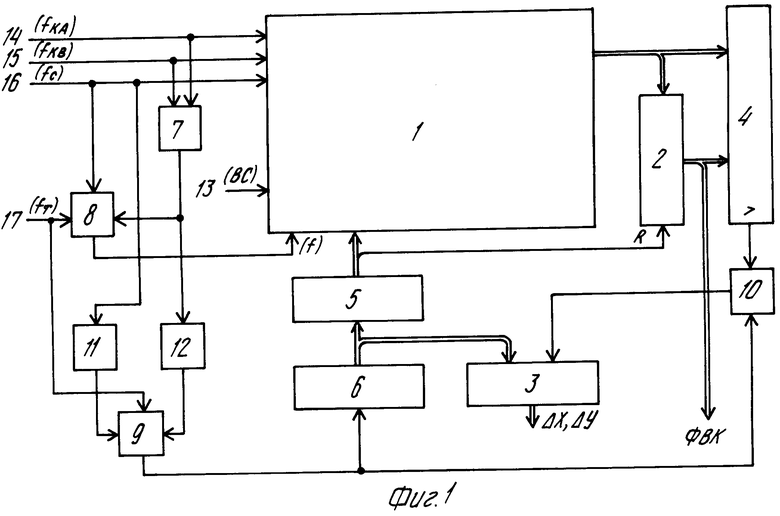

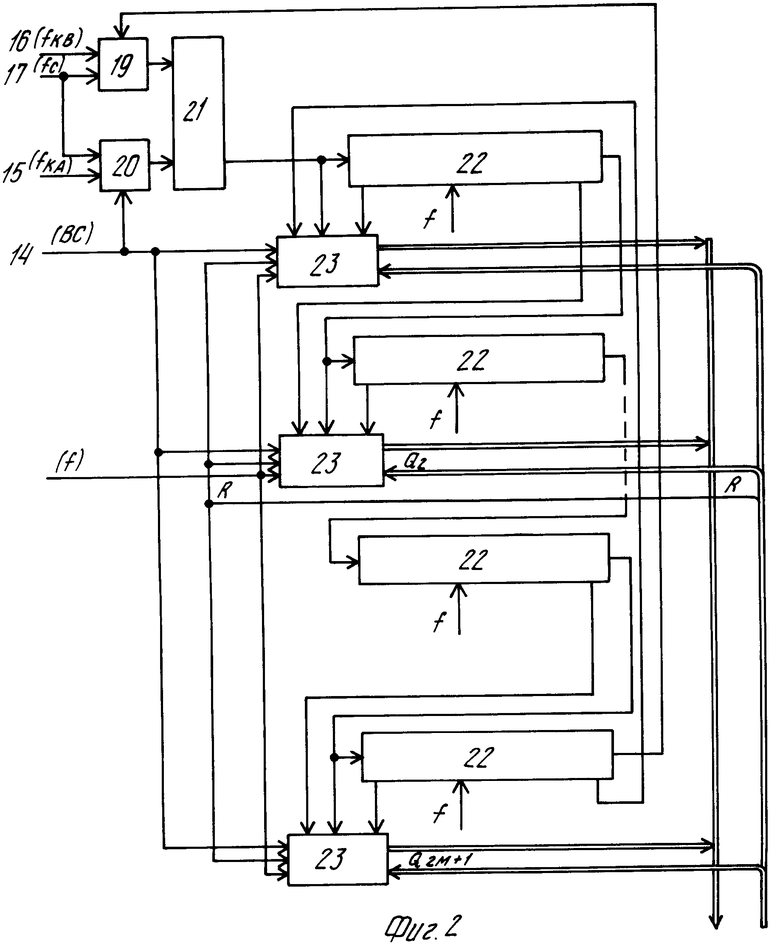

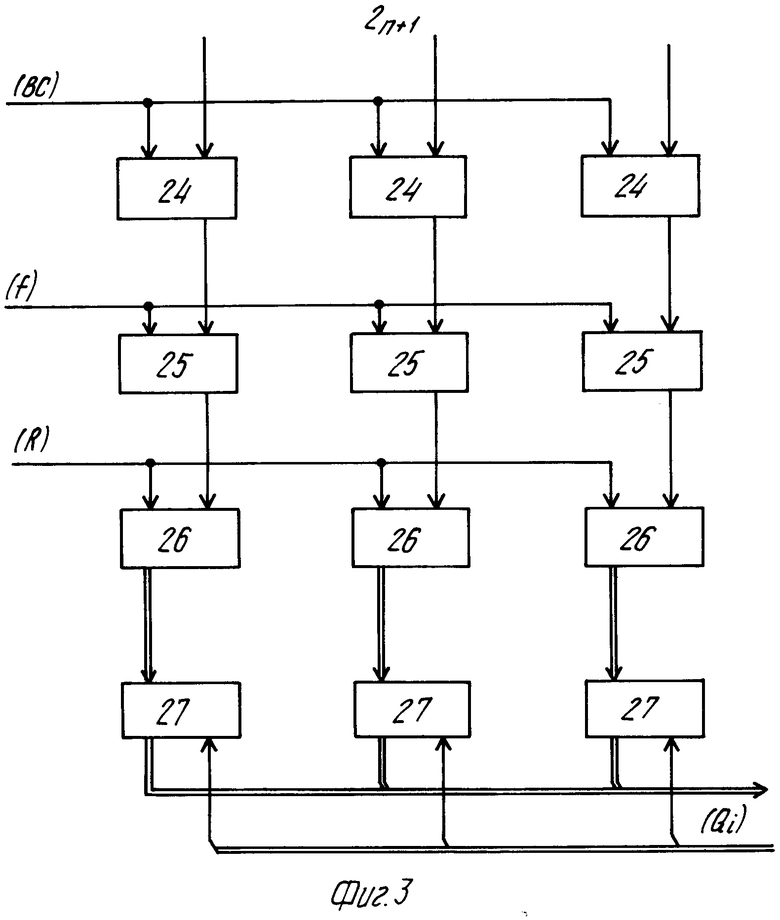

На фиг.1 изображена схема предлагаемого коррелятора; на фиг.2 схема его центрального процессора; на фиг.3 схема одного канала обработки информации.

Цифровой коррелятор состоит из центрального процессора 1, первого регистра 2, второго регистра 3, цифрового компаратора 4, дешифратора 5, счетчика 6, первого элемента ИЛИ 7, первого элемента И 8, второго элемента И 9, третьего элемента И 10, первого элемента НЕ 11, второго элемента НЕ 12.

На первый вход 13 подается последовательность информационных импульсов, поступающая, например, от видеоусилителя телевизионной передающей камеры, на второй вход 14 (fка) кадровый импульс для записи базовой последовательности импульсов, на третий вход 15 (fкв) кадровый импульс для записи текущей последовательности импульсов, на четвертый вход 16 (fc) строчные импульсы. Тактовые импульсы (fт) подаются на вход 17. На один из входов регистра 2 подаются импульсы сброса R, на выходах регистров 2 и 3 формируются коды Δx, Δy и ФВК соответственно. Первые являются мерой сдвига изображения по координатам х (в кадровом направлении), у (в строчном направлении) за промежуток времени между fка и fкв, вторые мерой экстремального значения ФВК, определяющее Δх и Δу.

Центральный процессор 1 (см. фиг.2) состоит из четвертого элемента И 19, пятого элемента И 20, второго элемента ИЛИ 21, блок задержки, например, из К регистров сдвига 22 по L разрядов и (2m + 1) и каналы 23 обработки информации, имеющие по (2n+1) входов, подключенных к соответствующим отводам регистров 22. Причем, К соответствует числу строк, а L числу пиксел строки, (2m+1) числу дискретов возможного сдвига изображения в кадровом направлении (x), a (2n+1) в строчном (у) направлениях (m и n дискретов от исходного положения).

Входная шина обслуживает каналы 23 импульсами сброса R в исходное состояние и сигналами запроса Q1,Q2m+1 выходной информации, выдаваемой каналами 23 в выходную шину данных.

Канал 23 обработки информации (см. фиг.3) состоит из 2n+1 каналов последовательно включенных блоков 24 умножения, элементов И 25, счетчиков 26 и блоков 27 ключей. Блоки 27 обеспечивают выдачу параллельных кодов состояний счетчиков 26 на выходную шину данных по сигналам запроса Qi, поступающим поочередно на каждый счетчик.

Сигнал f обеспечивает тактирование элементами И 25 поступающей информации от блока 24 умножения.

Коррелятор работает следующим образом.

Входной сигнал на рабочем ходе кадровой развертки (сигнал fка) через элементы И 20 и элементы ИЛИ 21 записывается в блок задержки с помощью тактовой последовательности f. Последняя формируется из тактовой последовательности fт, поступаемой на вход 17, с помощью элементов ИЛИ 7, И 8 только на время прямого хода fка, fкв и fc. Одновременно вычисляется в каналах 23 ФВК (точнее, на этом цикле измерения автокорреляционная функция). Последовательность импульсов телевизионного разложения кадра изображения сигналы перемножаются в блоке 24, результат тактируется элементами И 25 и суммируется в счетчике 26. По окончании в центральном счетчике 26 канала 23 вычисляется максимальное значение ФВК, что соответствует нулевому сдвигу последовательности информационных импульсов, поступающих на соответствующие входы канала 23. По остальным входам всех каналов вычисляются значения ФВК, соответствующие имеющимся сдвигам и значениям последовательности информационных импульсов, поступающим от блока задержки. Этот цикл измерения, при необходимости, может быть эталонным. На время обратного хода fка и fc (то же и при подаче fкв) с помощью элементов ИЛИ 7, НЕ 11, 12 и И 9 тактовая последовательность fт подается на счетчик 6 с заданным модулем счета, который формирует код для управления дешифратором 5. Последний выдает последовательность сигналов опроса Qiблоков 27, подключающих к выходной шине выходы счетчика 26, и их сигнал сброса R.

Последовательность кодов с выходной шины поступает на входы регистра 2 и компаратора 4, последний вырабатывает сигнал "больше" (>) в соответствии с кодами на его входах и через тактируемый элемент И 10 производит запись большего из поступивших кодов ФВК в регистр 2 и соответствующего ему номера канала одного из 2m+1 каналов 23 в регистр 3. Так осуществляется восхождение на этом периоде измерения к экстремальному значению ФВК и его положению в плоскости анализируемого изображения. Очевидно, это положение будет соответствовать Δх= Δу 0. Сброс регистра 2 в исходное осуществляется сигналом R от дешифратора 5.

На следующем цикле работы устройства через нужное число кадров подается сигнал fкв, который совместно с сигналом обеспечивает срабатывание элементов И 19 и ИЛИ 21 при поступлении последовательности информационных импульсов в блоке задержки. Дальше коррелятор работает по описанному выше циклу, обеспечивая вычисление и выдачу Δх и Δу при экстремальном значении ФВК на этом цикле измерения. Очевидно, экстремальное значение ФВК соответствует наибольшей идентичности изображений, считанных ТК за время действия сигналов fка и fкв.

Наличие отводов от блока задержки в кадровом (х) и строчном (у) направлениях от исходного положения позволяет определить максимальное значение ФВК при соответствующем сдвиге изображения. Таким образом, при сдвиге изображения справедливо Δх≠0; Δy≠0 vx= Δx/Δt; vy Δy/Δt; где Δ t r˙ fка-1 период измерения;

r число кадров между fка и fкв;

vx, vy средние скорости движения изображения за цикл измерения.

Следовательно, по сравнению с прототипом предложенный цифровой коррелятор обладает существенными преимуществами возможностью измерения при реверсе движения изображения и большей помехоустойчивостью, например, при отсутствии осевой симметрии ВФК анализируемого изображения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕЛЕВИЗИОННО-КОРРЕЛЯЦИОННЫЙ ДАЛЬНОМЕР | 1994 |

|

RU2086918C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2183382C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ ОБЪЕКТОВ | 1992 |

|

RU2065569C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ДВИЖЕНИЯ ОБЪЕКТОВ | 1994 |

|

RU2096927C1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Цифровой коррелятор | 1982 |

|

SU1045233A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ДВИЖЕНИЯ ПРОВОДОВ И КАБЕЛЕЙ | 1999 |

|

RU2170436C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2187884C1 |

Изобретение относится к устройствам автоматики и вычислительной техники и может быть использовано в корреляционных экстремальных системах типа телевизионно-корреляционных. Целью изобретения является расширение функциональных возможностей цифрового коррелятора, например, измерение кинематических параметров при реверсе движения источника входной информации. Эта цель достигается организацией линии задержки для хранения информации кадрового разложения, например, вводимого изображения, введением дополнительных канальных процессоров и нескольких логических элементов. Коррелятор содержит блок задержки, дешифратор, компаратор, счетчики, регистры, элементы И, ИЛИ, НЕ и каналы обработки информации, каждый из которых состоит из элемента И, счетчика, блока ключей и блока умножения. 3 ил.

ЦИФРОВОЙ КОРРЕЛЯТОР, содержащий блок задержки, дешифратор, компаратор, счетчик, два регистра, первый элемент ИЛИ, первый элемент НЕ, три элемента И и каналы обработки информации, каждый из которых состоит из элемента И, счетчика блока ключей и блока умножения, причем в каждом канале обработки информации выход блока умножения соединен с первым входом элемента И этого канала обработки информации, выход которого подключен к счетному входу счетчика своего канала обработки информации, выход которого соединен с информационным входом блока ключей своего канала обработки информации, выходы блоков ключей всех каналов обработки информации подключены к первому входу компаратора и информационному входу первого регистра, выход которого является выходом значения взаимно корреляционной функции коррелятора и соединен с вторым входом компаратора, выход "Больше" которого подключен к первому входу первого элемента И, выход которого соединен с синхровходом второго регистра, выход которого является выходом меры сдвига изображения по координатам коррелятора, информационный вход которого соединен с первыми входами блоков умножения, выход счетчика подключен к информационному входу второго регистра и входу дешифратора, выходы которого соединены с управляющими входами блоков ключей, выходы блока задержки подключены к вторым входам блоков умножения, выход первого элемента НЕ подключен к первому входу второго элемента И, выход которого соединен со счетным входом счетчика, тактовый вход коррелятора подключен к второму входу второго элемента И и первому входу третьего элемента И, выход которого соединен с вторыми входами элементов И всех каналов обработки информации, отличающийся тем, что в него введены второй элемент НЕ, два элемента И и второй элемент ИЛИ, выход которого соединен с вторым входом третьего элемента И и через второй элемент НЕ с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента И, вход задания строчных импульсов коррелятора соединен с входом первого элемента НЕ, третьим входом третьего элемента И и первыми входами четвертого и пятого элементов И, выходы которых подключены к входам первого элемента ИЛИ, выход которого соединен с входом блока задержки и вторым входом блока умножения соответствующего канала обработки информации, тактовый вход блока задержки подключен к тактовому входу коррелятора, вход обнуления которого соединен с обнуляющими входами счетчиков каналов обработки информации, синхровход первого регистра подключен к соответствующему выходу дешифратора, вход задания кадрового импульса для записи базовой последовательности импульсов коррелятора соединен с первым входом второго элемента ИЛИ и вторым входом четвертого элемента И, третий вход которого подключен к информационному входу коррелятора, вход задания кадрового импульса для записи текущей последовательности импульсов которого соединен с вторыми входами второго элемента ИЛИ и пятого элемента И, третий вход пятого элемента И подключен к соответствующему выходу блока задержки.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой коррелятор телевизионных сигналов | 1988 |

|

SU1553986A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-12-27—Публикация

1991-01-31—Подача