ключены к выходу второго триггера, второй вход канального влемента ИЛИ канедого канала подключен к выходу блока умножения своего канала, перв входы блоков умножения всех каналов объединены и являются четвертым входом устройства, а вторые входы блоков умножения всех каналов подключены .к выходам соответствующих разрядов N-разрядной цифровой линии задержки,

2. Устройство ПОП.1, о т л и

ч.ающе е с я тем, что блок упраления содержит первый одновибратор, вход которого, объединен с первым входом первого элемента ИЛИ и подключен к первому входу блока, выход одновибратора объединен с входом элемента задержки и подключен к перБому выходу блока, выход элемента 3 1держки соединен с первым входом irroporo эле;.к;1-1та ИЛИ, второй вход которого объединен с вТорым входом первого элемента ИЛИ и подключен к выходу второго одновибратора, вход

которого подключен к выходу первого триггера, нулевой вход которого объединен с установочным входом счетчика, третьим входом первого элемента ИЛИ и выходомтретьего элемента ИЛИ и подключен к второму выходу блока, выход второго элемента ИЛИ является третьим выходом блока, единичный вход первого триггера подключен к выходу счетчика, информационный, вход которого объединен с выходом элемента И и подключен к четвертому выходу блока, первый и второй входы элемента И соединены соответственно с выходом генератора тактовьох импульсов и выходом второго триггера, нулевой вход которого подключен к- выходу первого элемента ИЛИ первый и второй входы третьего элемента ИЛИ соединены соответственно с выходами третьего и четвертого, одновибраторов, вход третьего одновибратора и единичный вход второго триггера являются соответственно вторым и третьим входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1988 |

|

SU1566368A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1991 |

|

RU2051413C1 |

| Устройство распознавания изображений | 1989 |

|

SU1674153A1 |

| Устройство для определения составляющих вектора скорости движения изображения | 1983 |

|

SU1233190A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Цифровой коррелятор | 1990 |

|

SU1727133A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Цифровой коррелятор | 1984 |

|

SU1264200A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

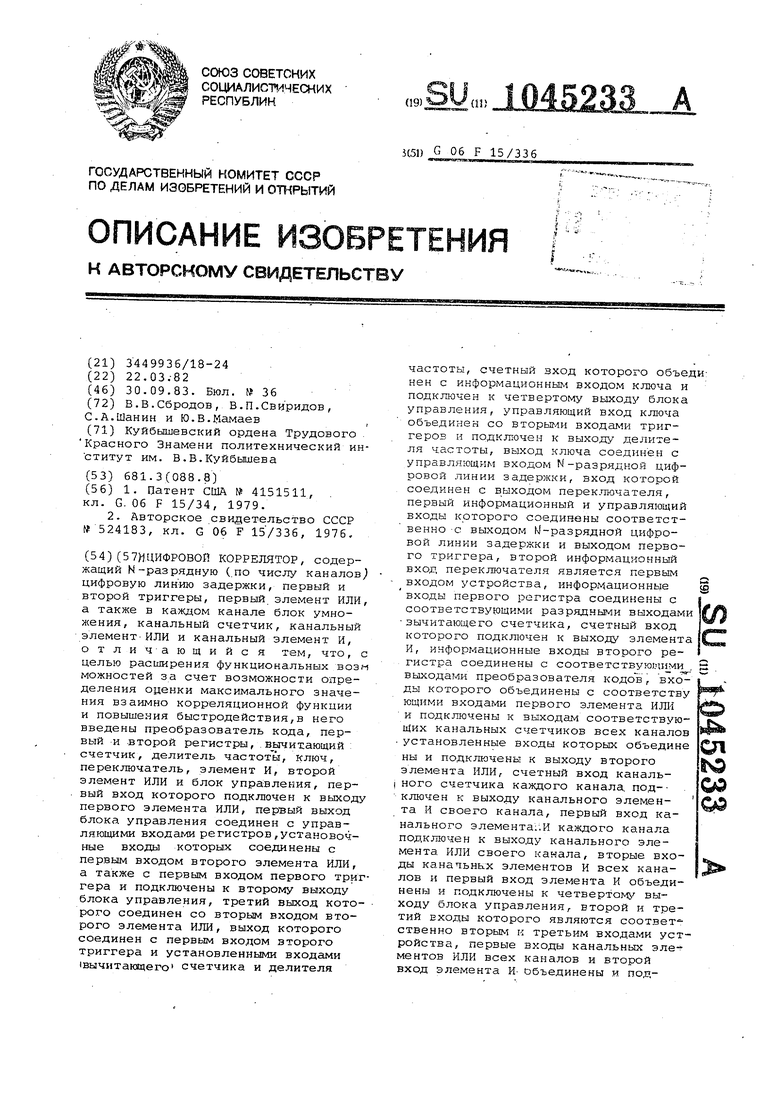

ЦИФРОВОП КОРРЕЛЯТОР, содержащий N-разрядную (.по числу каналов j цифровую линию задержки, первый и второй триггеры, первый элемент ИЛИ, а также в каждом канале блок умножения, канальный счетчик, канальный элемент-ИЛИ и канальный элемент И, отличающийс я тем, что, с целью расширения функциональных воэм можнОстей за счет возможности определения оценки максимального значения взаимно корреляционной функции и повышения быстродействия,в него введены преобразователь кода, первый и -второй регистры, . вьгчихающий : счетчик, делитель частоты, ключ, переключатель, элемент И, второй элемент ИЛИ и блок управления, первый вход которого подключен к выходу первого элемента ИЛИ, первый выход блока управления соединен с управляющими входами регистров,установочные входы которых соединены с первым входом второго элемента ИЛИ, а также с первым входом первого триггера и подключены к второму выходу блока управления, третий выход которого соединен со вторым входом второго элемента ИЛИ, выход которого соединен с первым входом второго триггера и установлеиньлми входами вычитающего счетчика и делителя частоты, счетный вход которого объеди: иен с информационным входом ключа и подключен к четвертому выходу блока управления, управляющий вход ключа объединен со вторыгли входами триггеров и подключен к выходу делителя частоты, выход ключа соединён с управляющим входом N-разрядной цифровой линии задержки, вход которой соединен с выходом переключателя, первый информационный и управляющий входы которого соединены соответственно с выходом М-разрядной цифровой линии задержки и выходом первого триггера, второй информационный вход переключателя является первым входом устройства, информационнь1е S входы первого регистра соединены с соответствующими разрядными выходами вычитающего счетчика, счетный вход которого подключен к выходу элемента И, информационные входы второго регистра соединены с соответствуюмими , выходами преобразователя кодов, входы которого объединены с соответству ющими входами первого элемента ИЛИ и подключены к выходам соответствующих канальных счетчиков всех каналов сд ьэ м установленные входы которых объедине ны и подключены к выходу второго элемента ИЛИ, счетный вход канальI ного счетчика каждого канала, под- ключен к выходу канального элемента И своего канала, первый вход канального элементами каждого канала подключен к выходу канального элемента ИЛИ своего канала, вторые входы каначьннх элементов И всех каналов и первый вход элемента И объединены и подключены к четвертомь выходу блока управления, второй н третий входы которого являются соответ ственно вторым и третьим входами устройства, первые входы канальных эле-t ментов ИЛИ всех каналов и второй вход элемента И- объединены и под

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в корреляционных экстремальных системах.

Известен цифровой коррелятор, содержагций два регистра сдвига, входы калуцого из которых подключены к выходам переключателей, первые входы переключателей являются входами устройства, а вторые входы подсоединены к выходам соответствующих регистров сдв.ига, которые одновременно подсоединены к двум входам схемы сравнения выход схемы сравнения соединен с входом счетчика, разрядные выходы которого соединены с информационными входами запоминающего устройства, выходы запоминающего устройства подключены к первым входам устройства сравнения, вторые входы которого подключены к выходам устройства фиксации, входы устройства фиксации и адресные входы запоминающего устройства соединены с выходами устройства адресации, выход хронизатора, выход устройства сравнения, управляющие входы переключателей, регистров сдвига, схемы сравнения, устройства адресации и запоминающего устройства подключены к устройству управления tl Недостатком данного устройства является малое быстродействие вследствие последовательной обработки информации в нем.

2

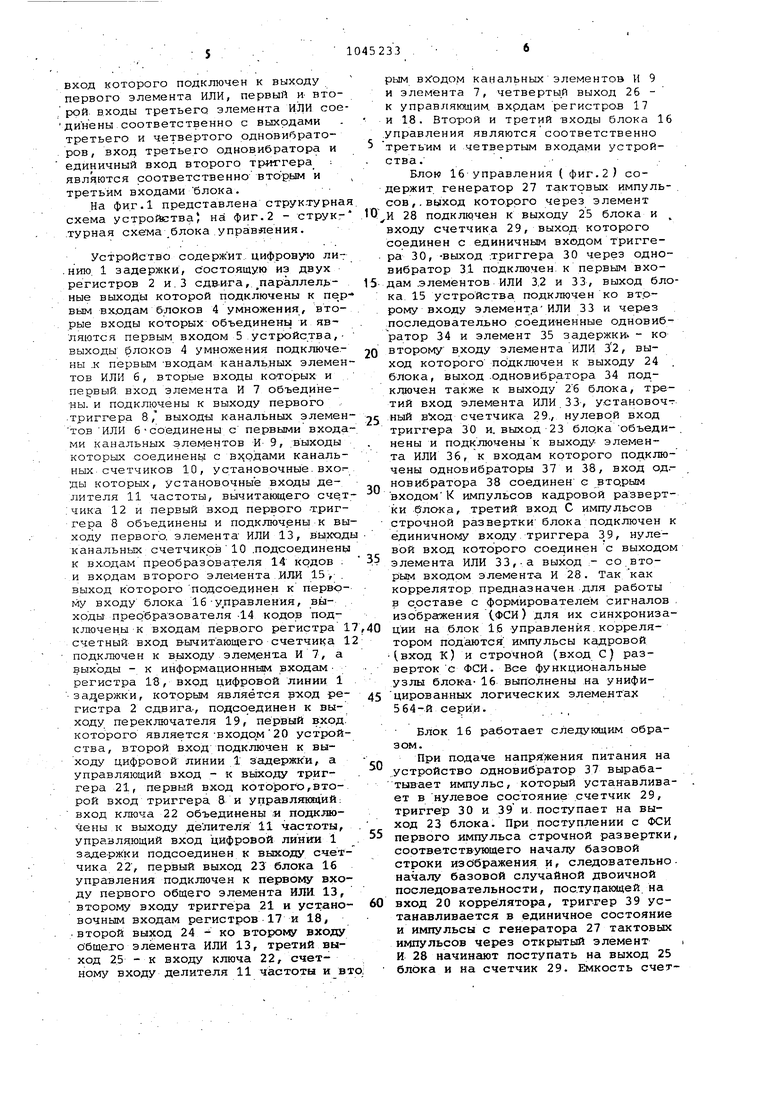

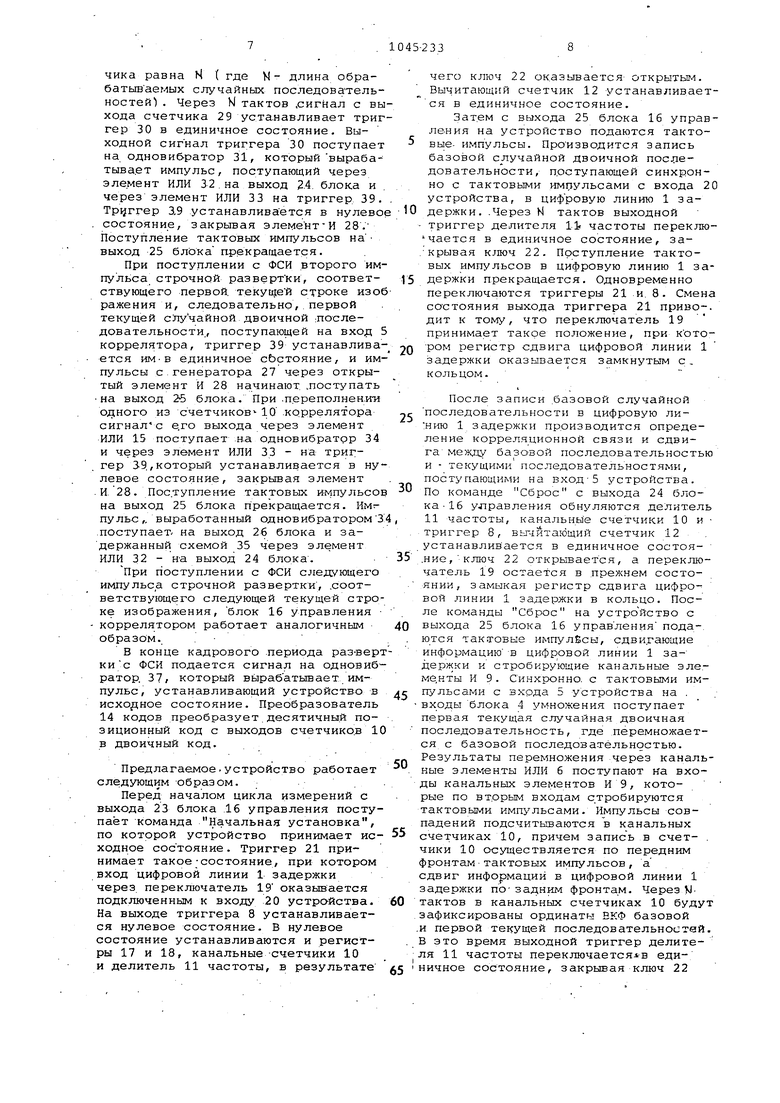

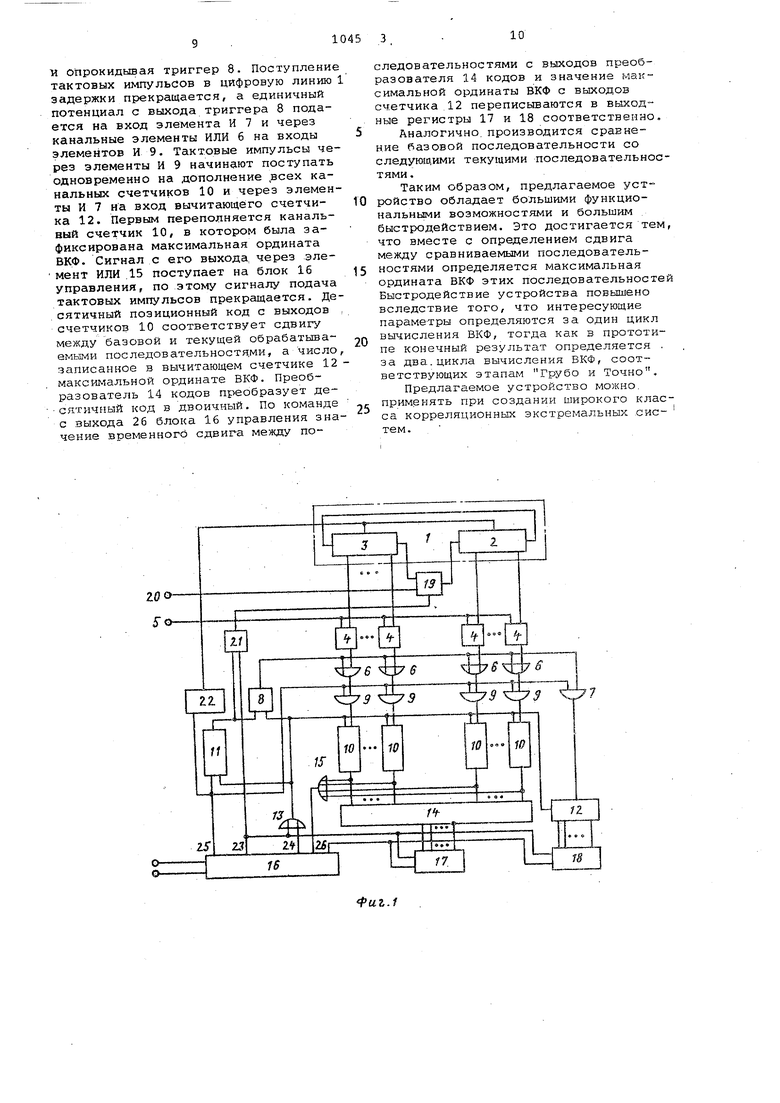

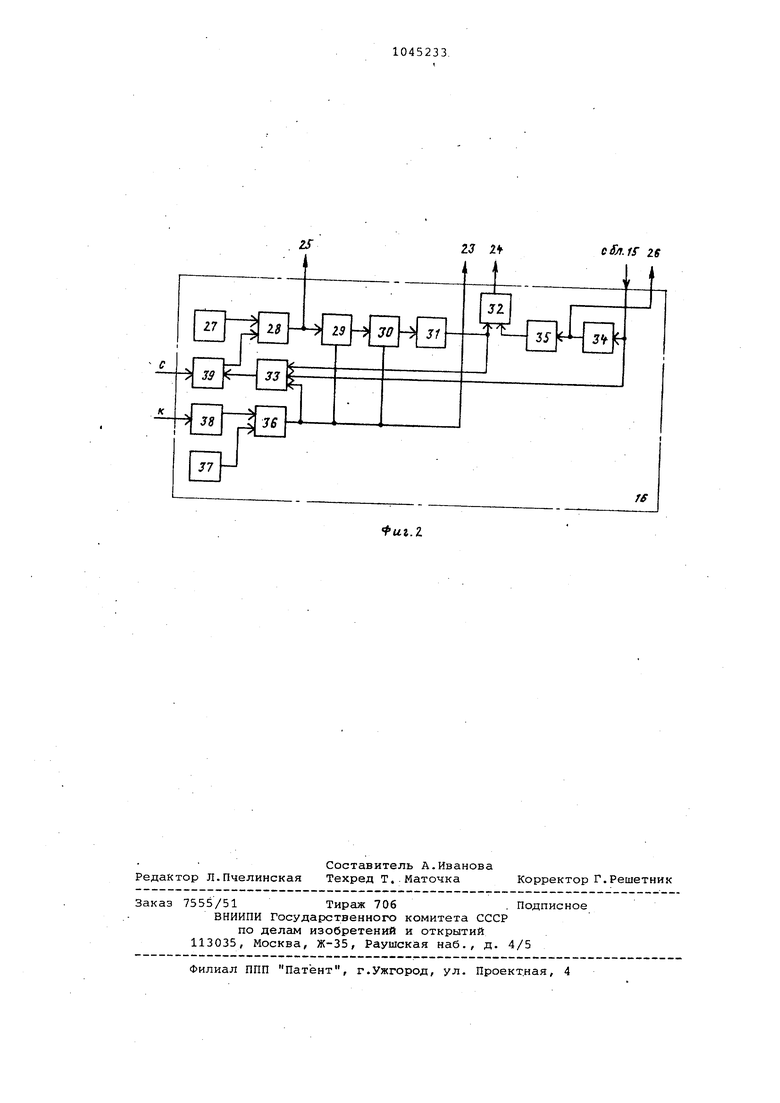

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее аналого-цифровой преобразователь (АЦП), выход которог подключен к входу цифровой линии задержки, параллельные выходы которой через вентили соединены с входами трехвходовых элементов ИЛИ, выходы трехвходовых элементов ИЛИ через преобразователи код - временной интервал подключены к первым входам блоков умножения, вторые входы которых подктаочены к выходу преобразователя напряжение-частота {UH4), к выходам блоков умножения подсоединены счетчики, выходы, которых соединены с входами дешифраторов переполнения, выходы дешифратора переполнения подключены к первым входагл канальных триггеров, к первым входам элементов И и входам многовходового элемента ИЛИ, выход которого подключен ко второму входу установочного триггера и установочным входам счетчиков, выходы канальных триггеров соединены с управляющими входами первой группы вентилей, вторыми входами элементов И и первыми входами двухвходовых элементов ИЛИ, вторые входы которых объединены и подключены к выхрду установочного триггера и выходы соединены с управляю,щими входами второй группы вентилей, 1 выходы элементов И соединены с вхо.дами индикаторов значений сдвига. первый вход установочного триггера, вторые входы канальных триггеров, управляющие входы АЦП, ПНЧ И цифровой линии задержки подключены к выходам блока управления 2. Однако известное устройство опре деляет только сдвиг между обрабатываемыми последовательностями, не определяя степень корреляционной связи между ними, что недостаточно, например, при построении корреляционных экстремальных систем и обусловливает низкие функциональные воз можности устройства, Кроме того, эт устройство имеет малое быстродейств вследствие двухэтапного режима рабо ты (грубо ,и точно) . Цель изобретения - расширение функциональных возможностей за счет возможности определения оценки максимального значения взаимно корреля ционной функции. Поставленная цель достигается те что в цифровой коррелятор, содержащий N-разрядную (по числу каналов) цифровую линию задержки, первый и второй триггеры, первый элемент ИЛИ а также в каждом канале блок умноже ния, канальный счетчик, канальный элемент ИЛИ. и канальный элемент И, введены преобразователь кода, первы и второй регистры, вычитающий счетчик, делитель частоты, ключ, переключатель, элемент И, второй элемент ИЛИ и блок управления, первый вход которого подключен к выходу пе вого элемента.ИЛИ, первый выход бло ка управления соединен с управляющи ми входами регистров, установочные выходы которых объединены с первыгл входом второго элемента ИЛИ, а такж с первым входом первого триггера и подключены к второму выходу блока у равления, третий выход которого сое динен со вторым входом второго эле-1 мента ИЛИ, выход которого соединен с первым входом второго триггера, и установочными входами вычитающего счетчика и делителя частоты, счетны вход которого объединен с информацией ныгл входом ключа и подключен к четвертому выходу блока управления, управляющий вход ключа объединен со вторыми входами триггеров и подключен к выходу делителя частоты, выход KJD04a соединен-с управляющим входом М-раз рядной цифровой линии задержки, вход которой со.единен с выходом переключателя, первый информационный и управляняций входы которого соединены соответственно с выходом N-разрядной цифровой линии задержки и выходом первого триггера, второй информационный вход переключателя является первым входом устройства, информационные входы.пер вого триггера соединены с соответствующими разрядными выходами вычитающего счетчика, счетный вход которого подключен к выходу элемента И, информационные входы второго регистра соединены с соответствующими выходами преобразователя кодов,- входы которогО объедине-ны с соответствующими входами первого элемента ИЛИ и подключены к выходам соответствующих канальных счетчиков всех каналов, установочные входы которых объединены и подключены к выходу второго элемента ИЛИ, счетный вход канального счетчика каждого канала подключен к выходу канального элемента И своего канала, первый вход канального элемента И каждого канала подключен к выходу канального элемента ИЛИ своего канала, вторые входы элементов И всех каналов и первый вход элемента И объединены и подключены к 4eTBepTON выходу блока управления, второй и третий входы KOTOpoi o являются соответственно вторым и третьим входам устройства, первые входы канальных элементов ИЛИ всех каналов и второй вход элемента И объединены и подключены к выходу второго триггера, второй вход канального элемента ИЛИ каждого канала подключен к выходу блока умножения своего канала, первые входы блоков умножения всех каналов объединены и являются четвертым входом устройства, а вторые входы блоков умножения зсех каналов подключены к выходам соответствчпощих разрядов Ы -разрядной цифровой линии задержки. Кроме того, блок управления содержит первый одновибратор, -вход которого объединен с первым входом первого элемента ИЛИ и подключен к nepBOLii входу блока, выход одновибратора объединен с входом э-лемента задержки и подключен к первому выходу блока, выход элемента задержки соединен с первым входом второго элемента ИЛИ, второй вход которого объединен со вторым входом первого элемента ИЛИ н подключен к выходу второго одновибратора, вход которого подключен к выходу первого триггера, нулевой вход которого объединен с ycтaнoвoчны 1 входом счетчика, третьш - входом первого элемента ИЛИ и выходом третьего элемента ИЛИ и подключен ко второму выходу блока, выход второго элемента ИЛИ является третьим выходом блока, единичный вход первого триггера подключен к выходу счетчика, информационный вход которого объединен с выходом элемента И и подклюг ен к четвертому выходу блока, первый и второй входы элемента И соединены соответствер-гно с выходом генератора тактовых импульсов и выходом второго триггера, нулевой вход которого подключен к выходу первого элемента ИЛИ, первый и- второй. входы третьего элемента ИЛИ сое динены соответственно с выходами третьего и четвертого одновибраторов, вход третьего одновибратора и единичный вход второго триггера ; являются соответственноBTOpEJM и третьим входами блока. На фиг,1 представлена структурна схема устройства на фиг.2 - струкг .турная схема блока управления. Устройство содержит цифровую ли.нию. 1 задержки, Состоящую из двух регистров 2 и.З сдв.ига,параллел 1ные выходы которой подключены к пер вым вх-одам блоков 4 умножения, вторые входы которых объединень и являются первым входом 5 .устройства, выходы блоков 4 умножения подключе.ны .к первым -входам каналь:ных элемен тов ИЛИ б, вторые входы которых и первый вход элемента И 7 объединены, и подключены к выходу первого .триггера 8, выходы канальных элемен тов ИЛИ 6-соединены с первыми входа ми канальных элементов И 9, выходы которых соединена с вхрДс1Ми канальных счетчиков 10, установочные.вхо ды которых, установочные входы делителя 11 частоты, вычитающего .чика 12 и первый вход первого триггера 8 объединены и подключены к вы ходу первого, элемента ИЛИ 13, выход канальных счетчиков10 .подсоединены к входам преобразователя 14 кодов : и входам второго элемента.КЛИ 15 . выход которого подсоединен к первому входу блока 16-у.правления, выходы- преобразователя -14 кодов подк.гаочены к входам первого регистра 1 счетный вход в-ычитающего счетчика 1 подключен к выходу элемента И 7, а выходы - к информационным входамрегистра 18, вход цифровой линии 1 -за ержки, которым является вход регистра 2 сдвига, подсоединен к выходу п-ерек.гаочателя 19, первый вход. которого является-входом20 устройства, второй ВХОД подключен к выходу цифровой линии 1 задержки, а управляющий вход - к вь1ходу триггера 21, первый вход которого,второй вход триггера & и управляющий: вход ключа 22 объединенная подключены к выходу делителя 11 частоты, управляющий вход цифровой линиги 1 задержки подсоединен к ВЫХ.ОДУ сч.етчика 22, первый выход 23 блока 16 управления подключен к перво входу первого общего элемента ИЛИ. 13, второму входу триггера 21 и усгановочным входам регистров.17 и 18, .второй выход 24 - ко второму входу общего элемента ИЛИ 13, третий выход 25 - к входу ключа 22, счетному входу делителя 11 частоты и вт рым вхгодом канальных элементов И 9 и элемента 7, четвертый выход 26 к управляющим, входам регистров 17 и 18. Второй и третий -входы блока 16 управления являются соответственно третьим и .четвертым входами устройства. БЛОК 16 управления ( фиг. 2) содержит генератор 27 тактовых импульсов ,, выход которого через элемент И 28 подключе.н к выходу 25 блока и входу счетчика 29, выход которого соединен с единичным входом триггера 30, -выход триггера 30 через одновибратор 31 подк.пючен к первым входам .элементов ИЛИ 3,2 и 33, выход блока 15 устройства подключен ко втррому входу элементаИЛИ 33 и через последовательно соединенные одновибратор 34 и элемент 35 задержки - ко второму входу элемента ИЛИ 32, выход которого подключен к выходу 24 б-лока, выход .одновибратора 34 подключен также к выходу 26 блока, третий вход элемента ИЛИ. 33, у.становочт ный вход счетчика 29,, нулевой вход триггера 30 и. выход 23 бло.ка объеди-. нены и подк,лючены к выходу- элемента ИЛИ 36, к входам которого подключены одновибраторы 37 и 38, вход од.новибратора 38 соединен с вторым входомК импульсов кадровой развертки блока третий вход С импульсов строчной развертки- блока подключен к единичному входу триггера , нулевой вход которого соединен с выходом элемента ИЛИ 33,-а выход - со.втоptJM входом элемента И 28 . Так как коррелятор предназначен для работы в с.оставе с формирователем сигналов . изображения {фСИ) для их синхронизации на блок 1.6 управления, коррелятором подаются импульсы кадровой (.вход к) и строчной (вход CJ разверток с ФСИ. Все функциональные уз,лы блока- 16 выполнены на унифицированных логических элементах 564-й серии. Блок 16 работает с.педующим образом.. . При подаче напряжения питания на устройство одновибратор 37 вырабатывает импульс, который устанавливает в нулевое состояние счетчик 29, триггер 30 и 39 и. поступает на выход 23 блока. При поступлении с ФСИ первого импульса строчной развертки, соответствующего началу базовой строки изображения и, следовательно. началу базовой случайной двоичной последовательности, пос.туцаняцей на вход 20 коррелятора, триггер 39 устанавливается в единичное состояние и импульсы с генератора 27 тактовых импульсов через открытый элемент , И 28 начинают поступать на выход 25 блока и на счетчик 29. Емкость счетчика равна М ( где N- длина обрабатьшаемых случайных последовательностей) . Через N тактов .сигнал с вы хода счетчика 29 уста.навливает триг гер 30 в едкничное состояние. Выходной сигнал триггера 30 поступает на одновиб-ратор 31, который вырабатывает импульс, поступающий через элемент ИЛИ 32. на выход Я4. блока и через элемент ИЛИ 33 на триггер 39 Триггер 3,9 устанавливается в нулево состояние, закрывая элементИ 28. Поступление тактовых импульсов на выход 25 блока прекращается. При поступлении с ФСИ второго им пульса строчной развертки, соответствующего первой, текущей строке изо ражения и, следовательно, первой текущей случайной двоичной последовательности, поступающей на вход коррелятора, триггер 39 устанавлива ется им-в единичное сЬстояние, и им пульсы с генератора 27 через открытый элемент И 28 начинают, .поступать на выход 25 блока. При .п.ереполнен.ки из счетчиков 10 .коррелятора сигналс е.го выхода через элемент ИЛИ 15 поступает н.а одновибратрр 34 и через элемент ИЛИ 33 - на триггер 39,который устанавливается в ну левое состояние, закрывая элемент . И. 28. Пос.туплен-ие тактовых и-мпульсо на выход 25 блока прекращается. Импульс,, выработанный одновибратором3 .поступает- на выход 26 блока и задержанный схемой 35 через элемент ИЛИ 32 - н-а выход 24 блока. При поступлении с ФСИ следующего импульса строчной развертки, .соответствующего следующей текущей стро ке изображения, блок 16 управления коррелятором работает аналогичным образом. . В конце кадрового периода раз-вер кис ФСИ подается сигнал на одновиб ратор. 37; который вырабатывает импульс , устанавливающий устройство в исходное состояние. Преобразователь 14 кодов преобразует, десятичны.й позиционный код с выходов счетчиков 1 в двоичный код. Предлагае1мое.устройство работает следующим образом. Перед началом цикла измерений с выхода 23 блока 16 управления посту пает команда Начальная установка, по которой устройство п-ринимает исходное состояние. Триггер 21 принимает такое-состояние, при котором вход цифровой линии 1 задержки через переключатель 19 оказывается подключенным к входу 20 устройства. На выходе триггера 8 устанавливается нулевое состояние. В нулевое состояние устанавливаются и регистры 17 и 18, канальные -счетчики 10 и делитель 11 частоты, в результате чего ключ 22 оказывается открытым. Вычитающий счетчик 12 устанавливается в единичное состояние. Зат.ем с выхода 25 блока 16 управления на устройство подаются тактовые- и.мпульсы. Производится запись базовой случайной двоичной последовательности, поступающей синхронно с тактовыми импульсами с входа 20 устроРЧства, в цифровую линию 1 задержки. .Через N тактов выходной триггер делителя It частоты переключается в единичное состояние, закрывая ключ 22. Поступление тактовых импульсов в цифровую линию 1 задержки прекращается. Одновременно переключаются триггеры 21 .и. 8. Смена состояния выхода триггера 21 приво-. дит к тому, что переключатель 19 принимает такое положение, при котором регистр сдвига цифровой линии 1 задержки оказывается замкнутЕлм с, кольцом. . После записи базовой случайЕ-гой последовательност1 в цифровую линию 1 задержки производится определение корреляционной связи и сдвига междзу базовой последовательностью и текущими пос.педовательностями, поступающими на в,чод-5 устройства. По команде Сброс с выхода 24 блока -16 улравлен-ия обнуляются делитель 11 частоты, канальные счетчики 10 и триггер 8, вычитающий счетчик 12 устанавливаете, в единичное состоя.ние,ключ 22 открывается, а перек.пючатель 19 остается в .прежнем состоянии, замыкая регистр сдвига цифровой линии 1 задержки в кольцо. После команды Сброс на устройство с выхода 25 блока 16 управ ления пода-, ются тактовые импулЁсы, сдвигающие информацию в цифровой линии 1 задержки и стробирующие канальные эле.ме.нты И 9. Синхронно, с тактовыми импульсами с входа 5 устройства на . вхр,цы блока 4 умножения поступает первая текущая с.пучайная двоичная последовательность, где перемножается с базовой последовательностью. Результаты перемножения через канальные элементы ИЛИ 6 поступают на входы канальных элементов И 9, которые по вторым входам с тробируются тактовыми импульсами. Импульсы совпадений подсчитываются в канальных счетчиках 10, причем запись в счет- . чики 10 осуществляется по передним фронтам-тактовых импульсов, а сдвиг информации в цифровой лин-ии 1 задержки по задним фронтам. Через VJ. тактов в канальнЕзК счетчиках 10 будут зафиксированы ординаты ВКФ базовой и первой текущей последовательностей. В это время выходной триггер делителя 11 частоты переключается в единичное состояние, закрывая ключ 22 И Опрокидывая триггер 8. Поступлени тактовых импульсов в цифровую линию задержки прекращается, а единичный потенциал с выхода триггера 8 подается на вход элемента И 7 и через канальные элементы ИЛИ б на входы элементов И 9. Тактовые импульсы че рез элементы И 9 начинают поступать одновременно на дополнение ,всех канальных счетчиков 10 и через элемен ты И 7 на вход вычитающего счетчика 12. Первым переполняется канальный счетчик 10/ в котором была зафиксирована максимальная ордината ВКФ. Сигнал с его выхода, через элемент ИЛИ .15 поступает на блок 16 управления, по этому сигналу подача тактовых импульсов прекращается. Де сятичный позиционный код с выходов счетчиков 10 соответствует сдвигу между базовой и текущей обрабатываемыми последовательностями, а число записанное в вычитающем счетчике 12 максимальной ординате ВКФ. Преобразователь 14 кодов преобразует десятичный код в двоичный. По команде с выхода 26 блока 16 управления зна чение временного сдвига между по200о

Pu.t.1 следовательностями с выходов преобразователя 14 кодов и значение максимальной ординаты ВКФ с выходов счетчика. 12 переписываются в выходные регистры 17 и 18 соответственно. Аналогично, производится сравнение базовой последовательности со следующими текущими последовательностями. Таким образом, предлагаемое устройство обладает большими функциональньдми возможностями и большим быстродействием. Это достигается тем, что вместе с определением сдвига между сравниваемыми последовательностями определяется максимальная ордината ВКФ этих последовательностей Быстродействие устройства повышено вследствие того, что интересующие параметры определяются за один цикл вычисления ВКФ, тогда как в прототипе конечный результат определяется . за два.цикла вычисления ВКФ, соответствующих этапам Грубо и Точно, Предлагаемое устройство можно, применять при создании широкого класса корреляционных экстремальных сиетем.

2S

cSjj.lf 26

2J 2f

fui.i

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4151511, | |||

| кл | |||

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство для определения временных сдвигов случайных коррелированных сигналов | 1974 |

|

SU524183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-30—Публикация

1982-03-22—Подача