Предполагаемое изобретение относится к вычислительной технике и может быть использовано при отладке и контроле дискретной аппаратуры, а также непосредственно как средство поиска дефектов в цифровых узлах. Известно устройство для имитации отказов дискретной аппаратуры [1] содержащее первый коммутатор, дешифратор номера канала, дешифратор дефекта, формирователь дефекта счетчик циклов, схему сравнения, блок задания режима имитации, блок памяти, регистр, причем выходы первого коммутатора соединены входами-выходами устройства для подключения элемента дискретной аппаратуры, на котором имитируется неисправность, первые информационные входы первого коммутатора соединены с выходами имитации неисправности формирователя дефекта, входы которого соединены с выходами дешифратора дефекта, входы которого соединены с выходами кода дефекта блока задания режима имитации, выходы кода номера канала которого соединены с входами дешифратора номера канала, выходы которого соединены с входами выбора направления первого коммутатора, выходы кода номера цикла блока задания режима имитации соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с группой выходов счетчика циклов, выходы адреса теста блока задания режима имитации соединены с адресными входами блока памяти, выходы которого соединены с информационными входами регистра, выходы которого соединены с выходами устройства для подключения к выводам дискретной аппаратуры, в которой имитируется неисправность, а также содержащее второй коммутатор, эталонный элемент и блок управления коммутацией, причем первые информационные входы второго коммутатора соединены с входами-выходами устройства для подключения к выводам элемента дискретной аппаратуры, на контактах которого имитируется неисправность, выходы второго коммутатора соединены с входами эталонного элемента и вторыми информационными входами первого коммутатора, вторые информационные входы второго коммутатора соединены с выходом имитации неисправности формирователя дефекта, выход схемы сравнения соединен с входом признака цикла имитации блока управления коммутацией, вход режима имитации которого соединен с выходом режима имитации блока задания режима имитации, входы-выходы эталонного элемента соединены с входами признака направления коммутации блока управления коммутацией, входы выбора канала имитации которого соединены с выходами дешифратора номера канала и входами выбора направления второго коммутатора, входы управления состоянием "высокий импеданс" которого с вторыми управляющими выходами блока управления коммутацией, первые управляющие выходы которого соединены с входами управления состоянием "высокий импеданс" первого коммутатора, выход тактовых импульсов блока управления коммутацией соединен с входами стробирования блока памяти, регистра и счетным входом счетчика циклов, вход начальной установки которого соединен с выходом начальной установки блока управления коммутацией, вход признака неисправности типа "обрыв" которого соединен с выходом задания неисправности типа "обрыв" формирователя дефекта.

Недостатком известного устройства являются узкие функциональные возможности. Поскольку с выходов блока задания режима имитации на дешифратор номера канала и далее на первый коммутатор поступают сигналы, определяющие имитацию отказа в текущий момент времени только по одному из каналов устройства, невозможна имитация отказов типа "замыкание выводов", так как для этого необходимо воздействовать на несколько выводов одновременно. В известном устройстве информация о распределении входов и выходов эталонного, а следовательно, и контролируемого элементов фиксируется в блоке управления коммутацией по нажатию кнопки "ПУСК", то есть в начале работы. Кроме этого функционирование устройства определяется работой тактового генератора этого же блока, и никак не синхронизирована с прохождением основного теста дискретной аппаратуры. Это делает невозможным изменение режима "вход-выход" первого коммутатора на конкретных шагах теста, что необходимо при работе с элементами, имеющими двунаправленные шины. Реализованный в известном устройстве принцип имитации отказов цифровых элементов заключается в принудительном наведении требуемых логических уровней схемами каналов первого коммутатора на выводы контролируемого элемента, непосредственно установленного в некоторый узел дискретной аппаратуры, что по сути соответствует режиму внутрисхемного тестирования этого элемента. Однако выдача стимулирующих воздействий в текущий момент времени только по одному из выводов контролируемого элемента, невозможность синхронной работы с внешним вычислителем, а также отсутствие средств защиты каналов устройства от перегрузок, что является необходимым условием сохранения работоспособности и параметров надежности как самого устройства так и диагностируемой аппаратуры, наряду с отсутствием проверки контактирования с выводами проверяемого элемента делает невозможным использование известного устройства в качестве универсального цифрового внутрисхемного тестера.

Технический результат изобретения расширение функциональных возможностей устройства за счет имитации неисправностей как на отдельных, так и на нескольких выводах цифровых элементов, и обеспечения возможности использования устройства в качестве универсального цифрового внутрисхемного тестера за счет создания аппаратно-программной защиты каналов устройства от перегрузок и введения проверки контактирования с выводами проверяемого элемента. Технический результат изобретения достигается тем, что в устройство, содержащее коммутатор с подключаемым через устройство для подключения к его выводам контролируемым элементом, формирователь дефекта, блок управления коммутацией, дешифратор дефекта, блок задания режима имитации, причем выходы коммутатора соединены с входами-выходами устройства для подключения к выводам проверяемого элемента дискретной аппаратуры, на котором имитируется неисправность, управляющие входы блока управления коммутацией соединены с входами управления состоянием "высокий импеданс" коммутатора, информационные входы коммутатора подключены к выходам имитации неисправности формирователя дефекта, входы выборки которого соединены с выходами дешифратора дефекта, входы которого подключены в к выходам кода дефекта блока задания режима имитации, введены блок пороговых элементов и блок внешнего управления, причем выходы коммутатора соединены с входами контролируемых уровней блока пороговых элементов, входы выборки которого подключены к выходам дешифратора дефекта, вход разрешения которого соединен с входом второй выборки блока задания режима имитации и выходом второй выборки блока внешнего управления, выход первой выборки которого соединен с соответствующим входом блока задания режима имитации, выход признака состояния "обрыв" формирователя дефекта подключен к соответствующему входу блока пороговых элементов, выходы которого соединены с входами шины данных блока внешнего управления, выходы записи и данных которого подключены к соответствующим входам формирователя дефекта и блока управления коммутацией, входы выборки которого подключены к соответствующим выходам дешифратора дефекта, входы сброса и установки состояния "высокий импеданс" формирователя дефекта подключены к соответствующим выходам блока задания режима имитации, входы записи и чтения которого соединены с соответствующими выходами блока внешнего управления, выход квалификатора которого подключен к соответствующему входу блока задания режима имитации, вход чтения блока пороговых элементов и входы уровня логической единицы коммутатора подключены к соответствующим выходам блока внешнего управления, входы внешней шины данных, внешних чтения, записи и обращения, а также входы адреса устройства для подключения к внешнему вычислителю, у входу внешней установки амплитуды блока внешнего управления подключается источник питания, задающий уровень логической единицы на выводах проверяемого элемента.

Число разрядов коммутатора равно числу каналов устройства, причем каждый разряд содержит три инвертора с открытым коллекторным выходом, два транзистора и четыре резистора, причем вход первого инвертора является информационным входом коммутатора, а его выход подключен к входу третьего инвертора, базе первого транзистора, через первый резистор к первой шине питания и к входу уровня логической единицы коммутатора, вход второго инвертора является входом управления состоянием "высокий импеданс" коммутатора, а его выход соединен с выходом третьего инвертора, базой второго транзистора и через третий резистор подключен к основной шине питания, к которой через второй резистор подключен коллектор первого транзистора, эмиттер второго транзистора через четвертый резистор подключен к нулевой шине, а его коллектор соединен с эмиттером первого транзистора и является выходом коммутатора.

Формирователь дефекта содержит группу параллельных регистров, число выходов и входов данных которых равно числу каналов устройства, а также R-S триггер, выход которого является выходом признака состояния "обрыв", а входы соответственно входами сброса и установки состояния "высокий импеданс", выходы регистров являются выходами формирователя дефекта, а их входы данных соответствующими входами формирователя дефекта, управляющие входы регистров являются входами выборки дефекта, а тактовые входы соединены между собой и подключены к входу записи формирователя дефекта.

Блок управления коммутацией содержит группу параллельных регистров, число выходов и входов данных равно числу каналов устройства, причем выходы регистров являются управляющими выходами блока, входы данных входами блока, управляющие входы регистров входами выборки блока, а тактовые входы регистров соединены между собой и подключены к входу записи блока управления коммутацией.

Блок задания режима имитации содержит два дешифратора, счетчик и элемент ИЛИ, причем выходы счетчика являются выходами кода дефекта, а его входы сброса и установки подключены соответственно к первому и второму выходам первого дешифратора, которые являются выходами сброса и установки состояния "высокий импеданс", тактовый вход счетчика подключен к выходу элемента ИЛИ, входы которого соединены с выходами второго дешифратора, вход разрешения которого является входом второй выборки, второй управляющий вход входом чтения, а первый управляющий вход соединен со вторым управляющим входом первого дешифратора и входом записи блока задания режима имитации, первый управляющий вход и вход разрешения первого дешифратора являются соответственно входами квалификатора и первой выборки блока задания режима имитации.

Блок пороговых элементов содержит группу шинных формирователей, число выходов и входов данных которых равно числу каналов устройства, а также пороговые элементы с высоким входным сопротивлением, количество которых равно количеству входов данных шинных формирователей, причем выходы шинных формирователей поразрядно соединены между собой, составляя группу выходов блока пороговых элементов, количество которых соответствует разрядности шинных формирователей, входы данных шинных формирователей через пороговые элементы с высоким входным сопротивлением соединены с входами контролируемых уровней, которые через резисторы подключены к входу признака состояния "обрыв", первые управляющие входы шинных формирователей соединены между собой и подключены к входу чтения блока пороговых элементов, входами выборки которого являются вторые управляющие входы шинных формирователей.

Блок внешнего управления содержит двунаправленный шинный формирователь, дешифратор, буферный повторитель, группу шинных формирователей и группу диодов, количество которых соответствует числу выходов и входов данных группы шинных формирователей и равно числу каналов устройства, причем выходы группы шинных формирователей являются выходами данных блока, а их входы данных поразрядно соединены между собой, составляя группу входов шины данных блока внешнего управления, входы управления группы шинных формирователей соединены между собой, вторым входом разрешения двунаправленного шинного формирователя подключены к первому выходу дешифратора, который является выходом второй выборки блока внешнего управления, выходом первой выборки которого является второй выход дешифратора, подключенный к первому входу разрешения двунаправленного шинного формирователя, вход управления которого подключен к первому входу буферного повторителя и является входом внешнего чтения, второй вход буферного повторителя является входом внешней записи, а его выходы - соответственно выходами чтения и записи блока внешнего управления, входы дешифратора являются соответственно входами внешних адреса и обращения, а внешняя шина данных через двунаправленный шинный формирователь подключена к входам шины данных блока, младший разряд которой является выходом квалификатора, при этом вход внешней установки амплитуды подключен через свой диод для каждого выхода к выходам уровней логической единицы между собой.

В устройстве непосредственное формирование сигналов воздействия на контролируемый цифровой элемент производится в схемах коммутатора, управляемого сигналами с выходов формирователя дефекта и блока управления коммутацией. Команды управления подаются для нескольких каналов одновременно, что позволяет имитировать неисправности типа "замыкание выводов", а также оперативно на любых шагах теста изменять режимы каналов типа вход-выход устройства. Благодаря введению нового узла блока внешнего управления, работа устройства синхронизирована сигналами внешней шины управления с работой основного вычислителя, управляющего тестированием аппаратуры, в которой имитируются отказы. Это позволяет обеспечивать возможность работы с элементами, имеющими двунаправленные шины. Введение блока пороговых элементов позволяет отслеживать логические уровни и импеданс контролируемых точек и, как следствие этого обеспечит аппаратно-программную защиту каналов устройства от перегрузок и проверку контактирования с выводами проверяемого элемента, позволяя использовать устройство в качестве универсального цифрового внутрисхемного тестера.

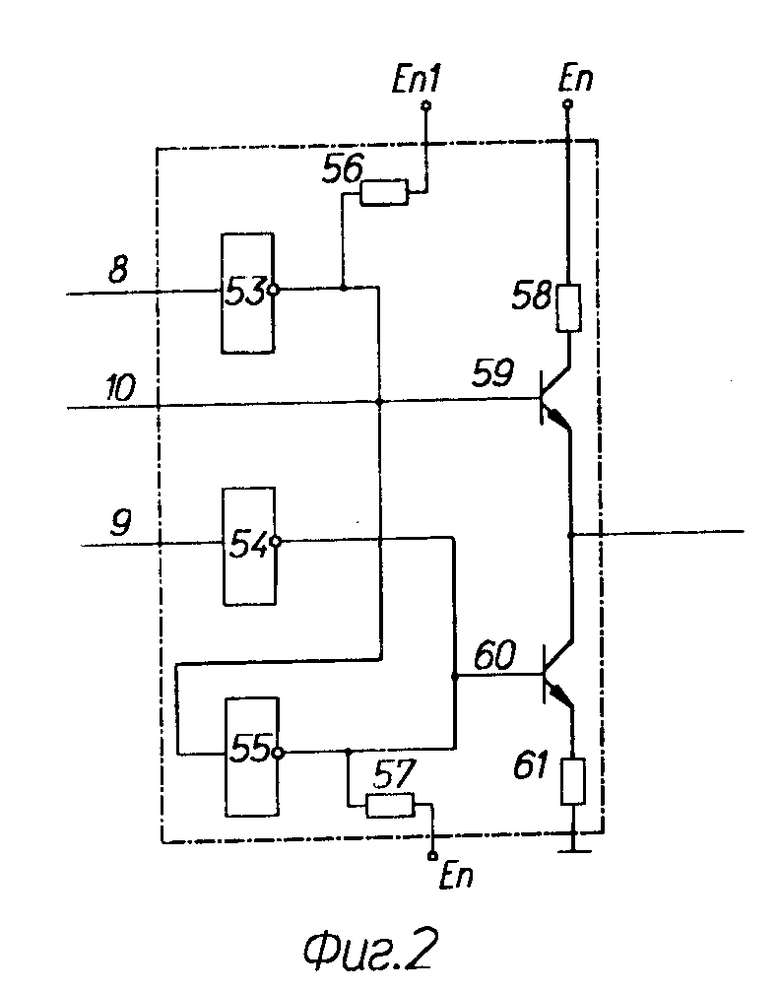

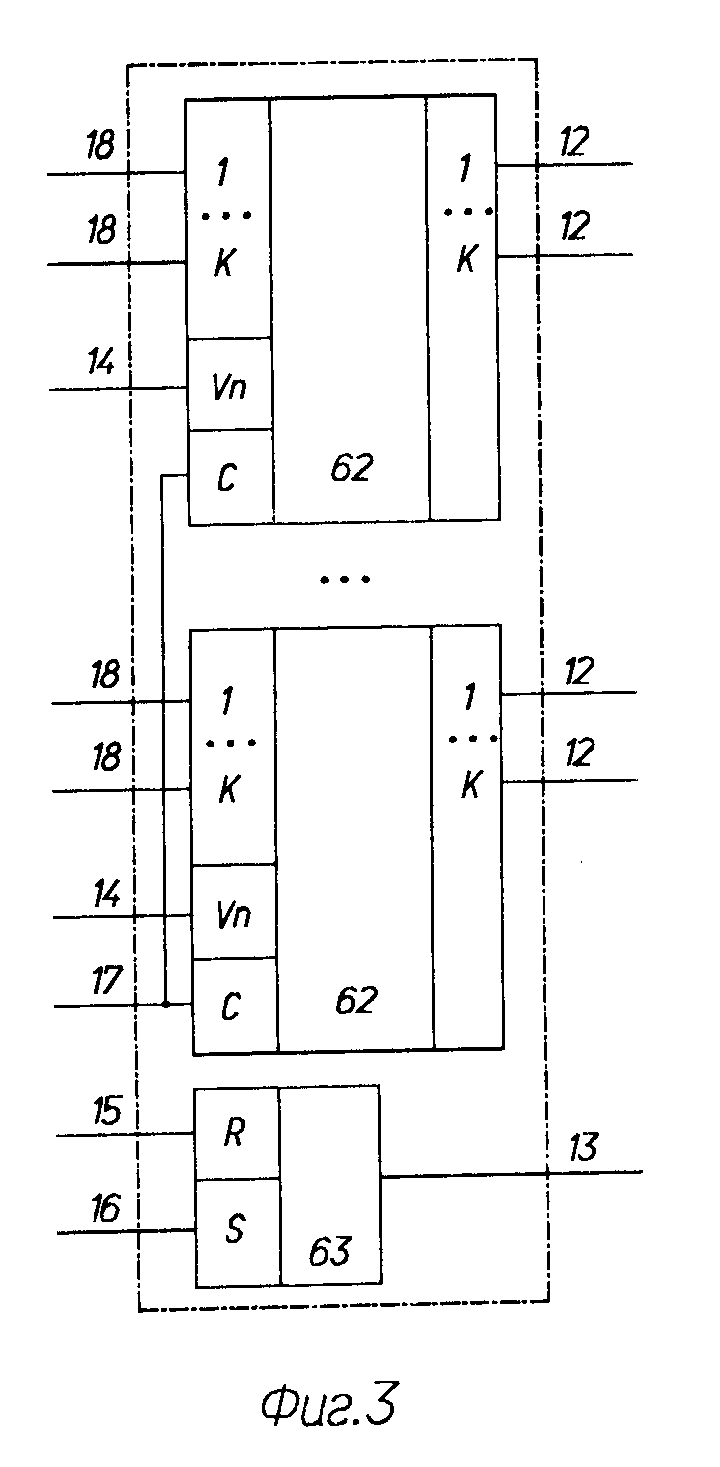

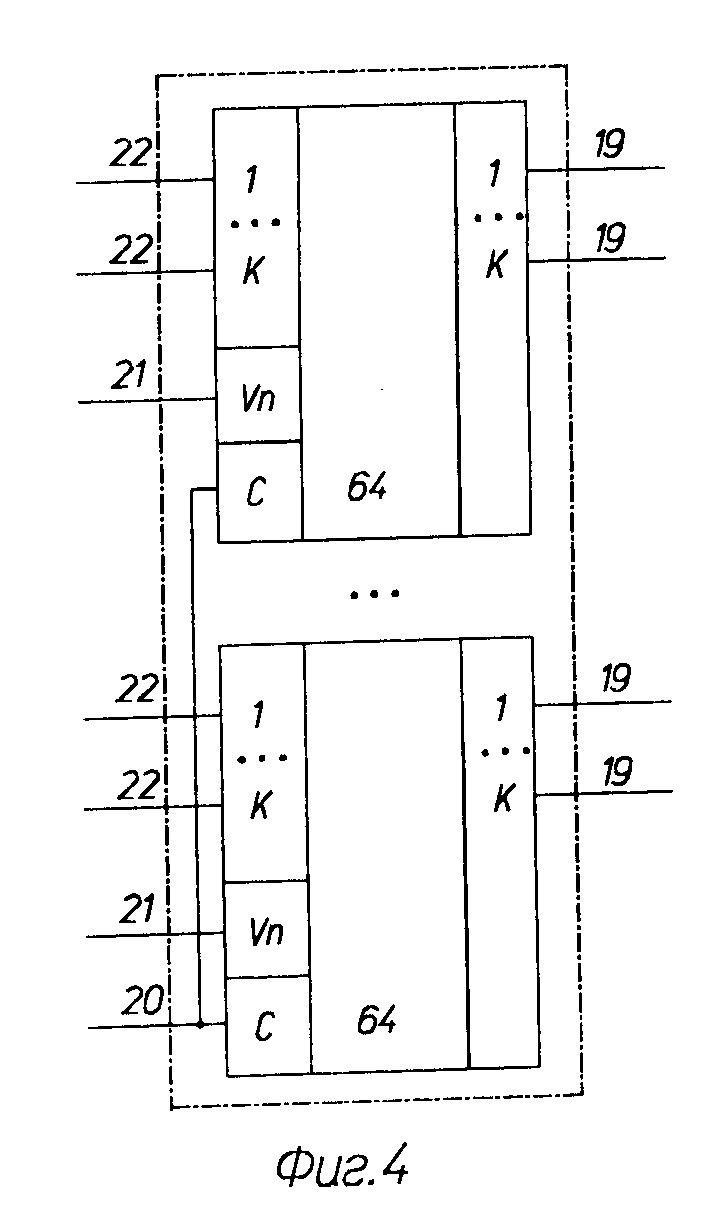

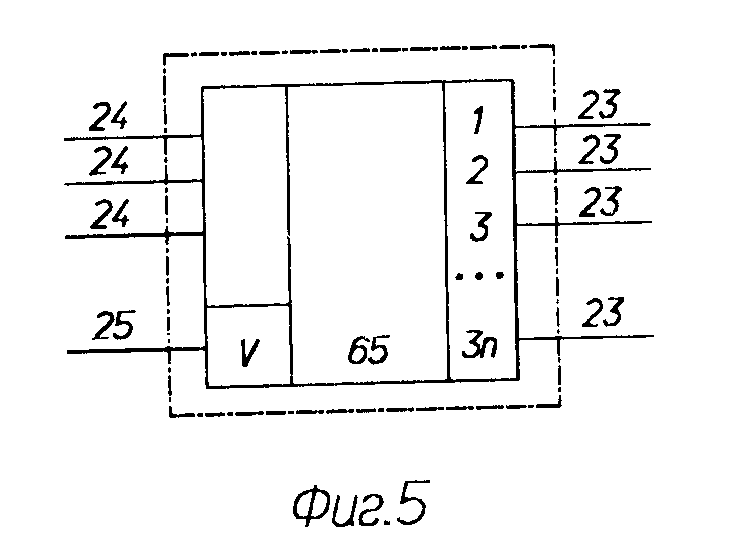

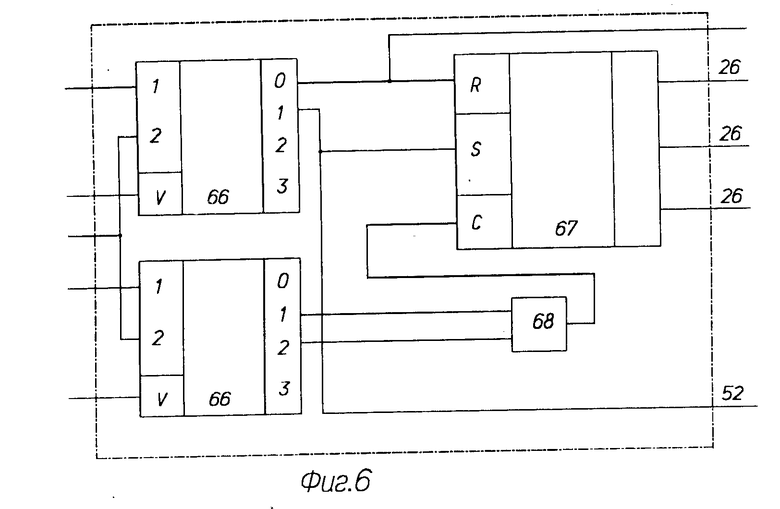

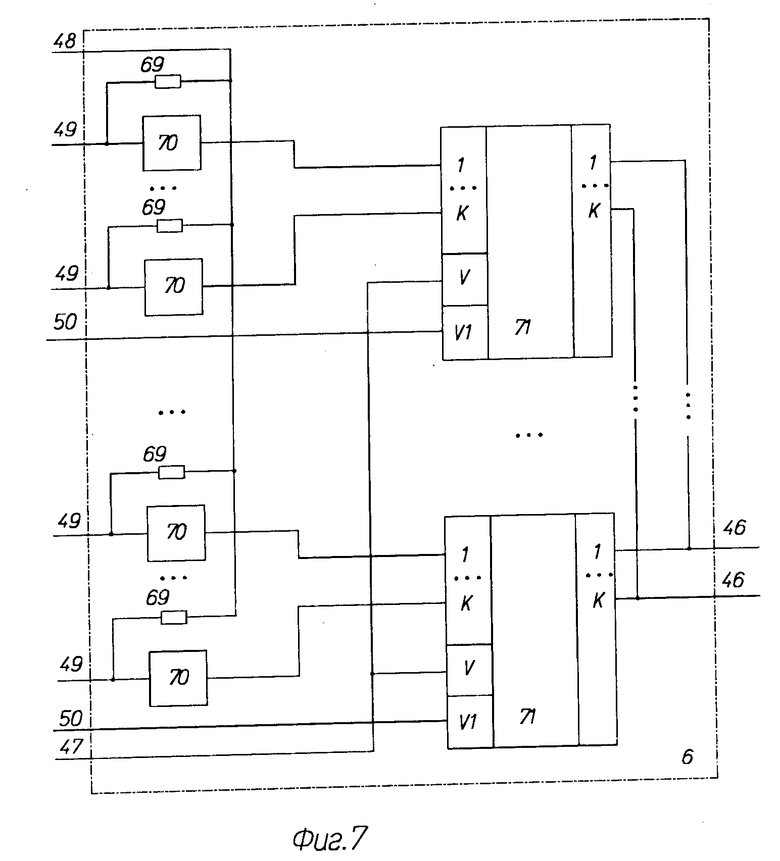

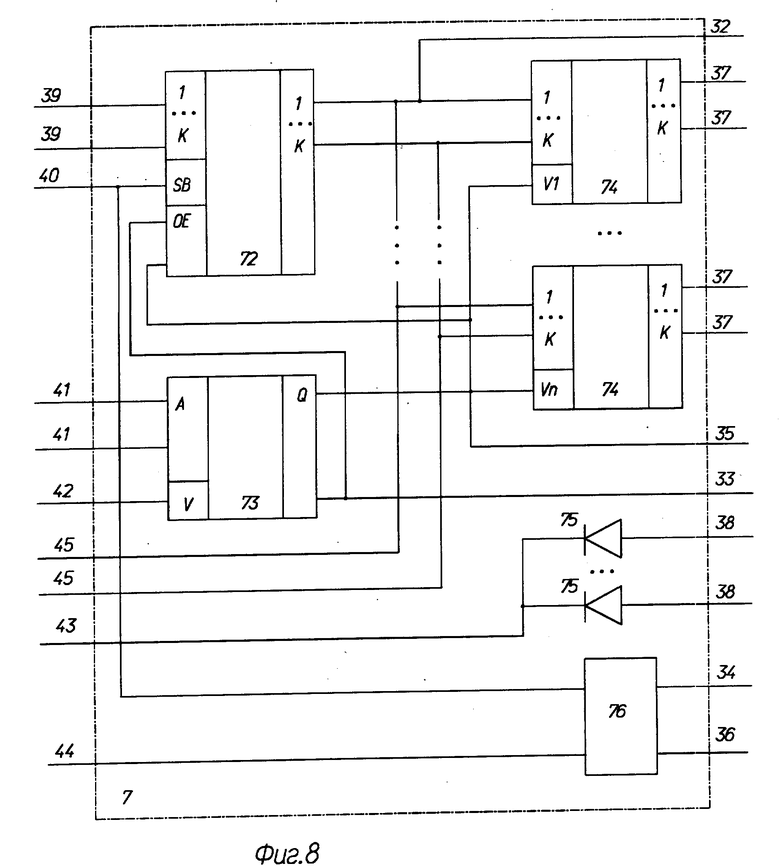

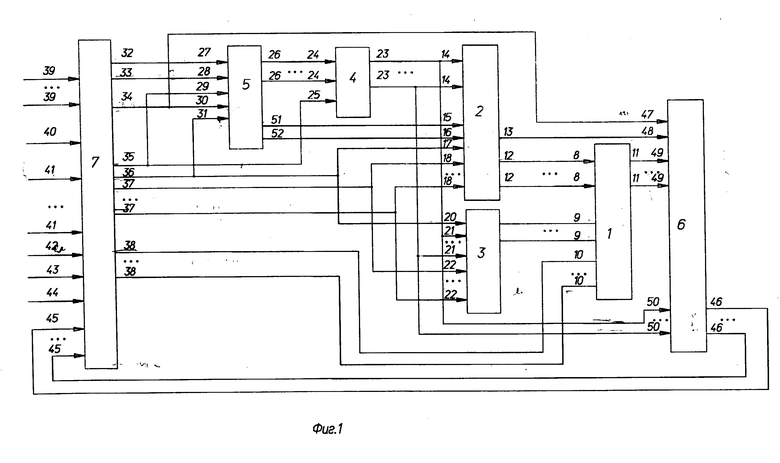

На фиг. 1 представлена схема устройства для имитации отказов и внутрисхемного тестирования элементов дискретной аппаратуры; на фиг. 2 схема одного разряда коммутатора; на фиг. 3 схема формирователя дефекта; на фиг. 4 схема блока управления коммутацией; на фиг. 5 схема дешифратора дефекта; на фиг. 6 схема блока задания режима имитации; на фиг. 7 схема блока пороговых элементов; на фиг. 8 схема блока внешнего управления.

Устройство содержит подключаемый к контролируемому элементу коммутатор 1, формирователь дефекта 2, блок управления коммутацией 3, дешифратор дефекта 4, блок задания режима имитации 5, блок пороговых элементов 6, блок внешнего управления 7, причем входы 8 коммутатора 1 соединены с выходами 12 формирователя дефекта 2, входы управления состоянием "высокий импеданс" 9 коммутатора 1 соединены с управляющими выходами блока 3, входы 10 уровня логической единицы коммутатора 1 подключены к выходам 38 уровня логической единицы блока 7, выход признака состояния "обрыв" 13 формирователя дефекта 2 подключен к соответствующему входу 48 блока 6, входы выборки дефекта 14 формирователя дефекта 2 соединены с входами выборки 21 блока 3 и входами выборки 50 блока 6 и подключены к выходам выборки дефекта 23 дешифратора дефекта 4, выходы 11 коммутатора 1 непосредственно подключаемые к выводам контролируемого элемента одновременно соединены с входами контролируемых уровней 49 блока 6, вход сброса состояния "высокий импеданс" 15 формирователя дефекта 2 и его вход установки состояния "высокий импеданс" 16 подключены к соответствующим выходам 51 и 52 блока 5, вход записи 17 формирователя дефекта 2 и его входы данных 18 соединены с соответствующими входами 20 и 22 блока 3 и подключены соответственно к выходам 36 и 37 блока 7, выход записи 36 которого подключен к входу записи 31 блока 5, входы кода дефекта 24 дешифратора дефекта 4 подключены к соответствующим выходам 26 блока 5, вход разрешения 25 дешифратора дефекта 4 соединен с входом второй выборки 29 блока 5 и выходом второй выборки 35 блока 7, вход квалификатора 27 блока 5 подключен к выходу квалификатора 32 блока 7, вход первой выборки 28 блока 5 подключен к выходу первой выборки 33 блока 7, выход чтения 34 блока 7 соединен с соответствующими входами 30 блока 5 и 47 блока 6, выходы 46 блока пороговых элементов 6 подключены к входам шины данных 45 блока 7, блок внешнего управления 7 подключается к основному вычислителю через входы внешней шины данных 39, вход внешнего чтения 40, входы внешнего адреса 41, вход внешнего обращения 42 и вход внешней записи 44, вход внешней установки амплитуды 43 подключается либо к шине питания самого устройства, либо к внешнему регулируемому источнику.

На фиг. 2 приведена схема одного разряда коммутатора 1. В ее состав входят три инвертора с открытым коллекторным выходом 53, 54 и 55, четыре резистора 56, 57, 58 и 61, два транзистора 59 и 60. Весь коммутатор содержит M разрядов, где M количество каналов устройства.

На фиг. 3 приведена схема формирователя дефекта 2. В его состав входят группа параллельных регистров 62 с объединенными тактовыми входами и раздельными входами разрешения записи, а также R-S триггер 63. Количество регистров в группе и их разрядность находятся в зависимости:

K•N=M

где

K разрядность регистров,

N количество регистров в группе,

M количество каналов устройства.

На фиг. 4 приведена схема блока управления коммутацией 3. В его состав входят группа параллельных регистров 64, идентичная группе регистров формирователя дефекта 2.

На фиг. 5 приведена схема дешифратора дефекта 4. Он состоит из стробируемого дешифратора 65, количество выходов которого равно устроенному числу регистров блока 3 или 4, то есть 3•N.

На фиг. 6 приведена схема блока задания режима имитации 5. В его состав входят два дешифратора 66, счетчик 67 и элемент ИЛИ 68.

На фиг. 7 приведена схема блока пороговых элементов 6. Он состоит из группы резисторов 69, группы пороговых элементов с высоким входным сопротивлением 70 и группы шинных формирователей 71 с объединенными и разнесенными группами входом управления включением 71. Количество резисторов 69 и пороговых элементов 70 соответствует количеству каналов устройства.

На фиг. 8 приведена схема блока внешнего управления 7. В его состав входят двунаправленный шинный формирователь 72, дешифратор 73, группа шинных формирователей 74, группа диодов 75 и буферный повторитель 76.

Число и разрядность шинных формирователей в блоках 6 и 7 соответствует числу и разрядности регистров в блоках 2 и 3. Количество диодов в блоке 7 равно числу каналов устройства.

Устройство работает следующим образом.

Входы внешней шины данных 39, внешнего чтения 40, внешнего адреса 41, внешнего обращения 42 и вход внешней записи 44 блока внешнего управления 7 подключаются к основному вычислителю, формирующего основные последовательности команд выполняемых устройством. Первой из таких последовательностей команд формируемых сразу после включения питания устройства является начальная установка элементов памяти. Вход внешней установки амплитуды 43 блока 7 подключают либо к внешнему источнику, либо к шине питания. Соединенные между собой выходы 11 коммутатора 1 и входы контролируемых уровней 49 блока пороговых элементов 6 через специальное устройство, например многоконтактный зажим типа "клипса", подключают к выводам контролируемого элемента. Дальнейшие действия зависят от режима использования устройства, которым может быть либо режим имитации отказов, либо режим внутрисхемного тестирования. Кроме этого возможен режим самоконтроля, при котором подключения контролируемого элемента не производится. Рассмотрим функционирование каждого из входящих в состав устройства блоков и всего устройства в целом.

Коммутатор 1 предназначен для непосредственного формирования сигналов воздействий на выводы контролируемого элемента. Выполненный на транзисторах 59 и 60 выходной каскад коммутатора обеспечивает принудительное наведение требуемых логических уровней на выводы контролируемого цифрового элемента, непосредственно установленного в некоторый узел аппаратуры, как в режиме имитатора отказов, как и в режиме внутрисхемного тестера. Управление коммутатором осуществляется по трем группам входов 8, 9 и 10, соединенных соответственно с выходами 12 формирователя дефекта 2, управляющими выходами 19 блока управления коммутацией 3 и выходами уровней логической единицы 38 блока внешнего управления 7. При этом на входы инверторов 53 из блока управления коммутацией поступают в инверсном коде непосредственные значения логических уровней на выходах коммутатора 1. Сигналы на входах инверторов 54, поступающие с управляющих выходов блока управления коммутацией определяют режимы работы соответствующих каналов коммутатора как активный или пассивный. Напряжения на входах 10 задаются соответствующими выходами блока внешнего управления 7, одинаковыми для всех каналов коммутатора, и определяют фактическое значение наводимого уровня логической единицы на выводах контролируемого элемента. В исходном состоянии на входы 8 и 9 поступают сигналы с уровнем логической единицы. Логический ноль на выходах инверторов 53 и 54 обеспечит низкий уровень напряжения на базах транзисторов 59 и 60, которые будут заперты. Таким образом обеспечивается высокий импеданс выхода коммутатора относительно общей точки и точки En. Эта же комбинация входных сигналов устанавливается для соответствующих каналов коммутатора и на тех шагах теста, когда воздействий по данным каналам не предусматривается. Перевод канала коммутатора в активный режим обеспечивается подачей логического нуля на вход инвертора 54. При этом наличие логической единицы на входе 8 сохраняет низкий уровень на выходе инвертора 59, который будет заперт. Логический нуль на входе инвертора 55 обеспечит наличие прямого тока базы транзистора 60 через резистор 57 и далее через резистор 61, таким образом открывая транзистор 60, что равносильно наведению логического нуля на данном канале коммутатора. Дальнейшая работа схемы в данном режиме зависит от величины коллекторного тока транзистора 60. Очевидно что увеличение коллекторного тока приводит к увеличению падения напряжения на резисторе 61, что в свою очередь уменьшает ток базы транзистора, препятствуя дальнейшему увеличению тока коллектора. Таким образом обеспечивается ограничение максимального тока нагрузки канала, защищая от перегрузки как схему соответствующего разряда коммутатора так и исследуемую схему. Появление логического нуля на входе 8 инвертора 53 приводит к появлению прямого тока базы транзистора 59, который открывает его. Дальнейшее поведение схемы разряда коммутатора зависит от тока нагрузки, подключенной к данному каналу, поскольку в первый момент времени ток эмиттера транзистора 59 распределяется на ток, текущий непосредственно в нагрузку через выход 11 и ток через еще открытый транзистор 60. Номиналы элементов схемы выбираются таким образом, что появление тока эмиттера транзистора 59 при типовой нагрузке и все еще открытый транзистор 60 приводит к наведению уровня логической единицы на выходе 11, а следовательно, и на базе транзистора 59. Это вызывает появление логического нуля на выходе инвертора 55, который запирает транзистор 60, а схема канала коммутатора переходит в режим формирования уровня логической единицы. Несоответствие выходного сигнала уровню логической единицы приводит к ситуации когда оба транзистора остаются открытыми. Это может быть вызвано двумя причинами. Либо выход канала подключен к слишком низкоомной нагрузке и в этом случае коллекторный ток транзистора 60 ограничивает ток выхода предохраняя, исследуемую схему от перегрузки, либо транзистор 59 неисправен, что легко выяснить, отключив нагрузку. Эта ситуация используется в режиме самоконтроля устройства когда нагрузка заранее отключена. Причем схема коммутатора позволяет отличить функциональный отказ, типа обрыва связи или замыкания, в том числе из-за пробоя p-n перехода транзистора, от параметрического, вызванного например падением коэффициента усиления по току транзистора 59. Для этого в режиме самоконтроля, в случае непоявления ожидаемого уровня логической единицы на выходе некоторого канала коммутатора на соответствующий этому каналу вход 9 подается сигнал логической единицы, запирающий транзистор 60. Появление логической единицы означает параметрический отказ транзистора 59 или резисторов 58, 56.

Формирователь дефекта 2 предназначен для непосредственной выдачи в коммутатор 1 логических уровней активных воздействий на выводы контролируемого элемента, непосредственно имитирующих его дефекты. В режиме внутрисхемного тестирования эти воздействия стимулируют по входам работу контролируемого элемента для последующего анализа реакций на его выходах. В этом режиме используется также сигнал, формируемый на выходе признака состояния "обрыв" и используемый для проверки контактирования каналов устройства с выводами контролируемого элемента. Конкретные значения воздействий поступают на входы 18 формирователя дефекта 2 с выходов данных 37 блока внешнего управления 7 по отдельной связи для каждого из M каналов. При этом момент их записи стробируется сигналом по входу записи 17 формирователя дефекта 2, поступающего из блока внешнего управления 7. Все каналы устройства условно разбиты на N групп по K каналов в каждой из них. На один из входов выборки дефекта 14 с выходов дешифратора дефекта 4 подается активный сигнал, дополнительно стробирующий момент записи данных в соответствующий этому входу регистр формирователя дефекта 2. Таким образом, значения воздействий обновляются для группы каналов одновременно, а при последовательном обращении ко всем группам в течение одного тестового шага для всех каналов устройства. Управление триггером 63 обеспечивается сигналами с выходов сброса 51 и установки 52 состояния "высокий импеданс" блока задания режима имитации 5. При начальной установке триггер 63 устанавливается в состояние единицы, что означает идентификацию устройством состояния "высокий импеданс" на выводах контролируемого элемента как логическую единицу.

Блок управления коммутацией 3 предназначен для формирования и непосредственной выдачи в коммутатор 1 сигналов управления, определяющих режимы каналов устройства. Наличие логической единицы на некотором выходе этого блока определяет соответствующий этому выходу канал как пассивный, а нуля предусматривает трансляцию записанных в регистрах формирователя дефекта 2 воздействий через коммутатор 1 на соответствующие выводы контролируемого элемента. Схема блока управления коммутацией 3 идентична схеме формирователя дефекта 2, но не содержит R-S триггера. На вход записи 20 поступает тот же сигнал от блока внешнего управления 7, однако разряды выборки дешифратора дефекта для блоков 2 и 3 разнесены, что делает невозможным одновременную запись в регистры этих блоков, хотя их входы данных объединены.

Дешифратор дефекта 4 предназначен для формирования сигналов выборки записи в регистры формирователя дефекта 2 и блока управления коммутацией 3, а также выборки чтения состояния групп каналов блока пороговых элементов 7. Разряды выборок, поступающие с дешифратора дефекта 4 на эти блоки, разнесены таким образом, что младшие N разрядов поступают на входы блока 3, средние - формирователя дефекта 2, а старшие блока 6. Этот порядок задает приоритет обращения блока внешнего управления 7 к перечисленным блокам. Схема дешифратора дефекта 4 представляет из себя типовую схему комбинационного дешифратора дефекта 4 представляет из себя типовую схему комбинационного дешифратора, входы кода дефекта 24 которого соединены с соответствующими выходами 26 блока задания режима имитации 5, а вход разрешения с выходом второй выборки 35 блока 7. Таким образом схема дешифратора дефекта 4 обеспечивает формирование выборки группы элементов блоков 2, 3 и 6 в соответствии с кодом на выходах 26 блока 5.

Блок задания режима имитации 5 предназначен для формирования сигналов кода выборки дефекта, обеспечивающих последовательное обращение к регистрам и буферным формирователям блоков 3, 2 и 6, а также для формирования сигналов сброса и установки R-S триггера блока 2. Код выборки формируется на выходах счетчика 67 в соответствии с его состоянием, которое определяется сигналами с выходов двух дешифраторов 67 и элемента ИЛИ 68. Все входы блока 5 соединены с соответствующими выходами блока внешнего управления 7. Тактовый вход счетчика 67 подключен к выходу элемента ИЛИ 68, входы которого соединены с первым и вторым выходами нижнего дешифратора, появление логической единицы на любом из которых означает наличие активного уровня на входах записи 32 или чтения 30 при условии активного сигнала второй выборки 29, поступающих с соответствующих выходов блока 7. На выходе элемента ИЛИ 68 формируется сигнал тактирования счетчика 67, который переключается при любом обращении к регистрам блоков 2 и 3 или буферным элементам блока 6, причем по завершении этого обращения, обеспечивая смену выборки после завершения предыдущей. Появление активного сигнала первой выборки разрешает формирование сигналов сброса и установки счетчика 67. Вход квалификатора 27, являющийся младшим разрядом внутренней шины данных устройства, определяет какой из сигналов сброса или установки при активном уровне на входе 28. Одновременно через выходы 51 и 52 эти сигналы управляют состоянием R-S триггера формирователя дефекта 2.

Блок пороговых элементов 6 предназначен для непосредственного отслеживания сигналов на выводах контролируемого элемента, включая проверку контактирования каналов коммутатора 1 с исследуемой схемой. Его входы 49 соединены с выходами 11 коммутатора 1, непосредственно подключенными к выводам контролируемого элемента. Пороговые элементы с высоким входным сопротивлением 70 отслеживает логические уровни на выводах контролируемого элемента не влияя на функционирование исследуемой схемы. Аналогично структуре блоков 2 и 3 выходы пороговых элементов 70 условно объединены в N групп по K элементов в каждой группе и соединяются с входами N шинных формирователей 71. На вход 47 поступает сигнал чтения с выхода 37 блока внешнего управления 7, разрешающий подключение шинных формирователей 71 через выходы 46 к шине данных 45 блока 7. Конкретная группа каналов, состояние которых транслируется на внутреннюю шину данных определяется активным сигналом по одному из входов выборки 50, поступающих с выходов 23 дешифратора дефекта 4. Вход 48 блока пороговых элементов 6 соединен с выходом 13 R-S триггера формирователя дефекта 2 и через высокоомные резисторы 69 обеспечивает смещение уровней на выводах контролируемого элемента к логическому уровню, соответствующему состоянию R-S триггера формирователя дефекта 2. Поскольку сопротивление резисторов 69 велико, сигнал на входе 48 не влияет на уровни сигналов с выводов контролируемого элемента, если с этими выводами обеспечено надежное контактирование. Состояние "обрыв" на выходном контакте устройства, то есть высокий импеданс канала коммутатора 1 относительно питания и земли. Состояние триггера 63 непосредственно отслеживается по входу 49 блока 6. Изменяя состояние триггера 63 и контролируя результат на входах блока пороговых элементов выявляются каналы устройства, находящиеся в состоянии обрыва с выводами контролируемого элемента. Устойчивое сохранение этого состояния в течении всего тесте квалифицируется как отсутствие контакта по данному каналу.

Блок внешнего управления 7 предназначен для формирования основных сигналов управления устройством, соответствующих командам внешнего вычислителя. Логика функционирования блока 7 полностью определяется последовательностью сигналов от внешнего вычислителя, который при обращении к устройству выставляет на входы внешнего адреса 41 код, соответствующий адресу устройства в системе, подтверждая установку адреса активным уровнем сигнала на входе внешнего обращения 42. Наличие внешней шины адреса позволяет включать устройство в состав более сложных систем совместно с другими устройствами, подключаемыми к единой магистрали. Подключение нескольких одинаковых устройств к одному вычислителю позволяет наращивать число каналов системы в кратности, соответствующей количеству каналов одного устройства. На выходах дешифратора 73 появление соответствующих адресных комбинаций приводит к появлению активных уровней сигналов первой и второй выборок. Сигнал первой выборки через выход 33 активизирует формирование сброса и установки в блоке задания режима имитации 5, сигнал второй выборки является основным и его появление разрешает доступ внешнему вычислителю к элементам устройства. Поступая на выход 35 блока 8 активный уровень сигнала второй выборки разрешает формирование выборок дешифратором дефекта 4, которые через выходы 23 активизируют соответствующую группу регистров или шинных формирователей блоков 2, 3 или 6. В самом блоке 8 сигнал второй выборки активизирует шинные формирователи 72 и 74. Двунаправленный шинный формирователь 72 коммутирует внутреннюю шину данных 45 либо на входы шинных формирователей 47 и через них на входы блоков 2 и 3 в обычном состоянии при наличии соответствующей выборки на выходах дешифратора дефекта 4, либо на выходы блока 6 при условии активного уровня на входе внешнего чтения 40. Одновременно сигнал внешнего чтения обеспечивает выдачу состояния шины данных 45 на внешнюю шину данных 39 при активном уровне и в обратном направлении при пассивном. Таким образом обеспечивается управление от внешнего вычислителя состоянием регистров 62 формирователя дефекта 2 и 64 блока управления коммутацией 3. Сигнал внешней записи от внешнего вычислителя поступает на вход 44 и через буферный элемент 76 и выход 36 транслирует на тактовые входы регистров блоков 2 и 3, стробируя смену их состояния по команде внешнего вычислителя. Выход внешней установки амплитуды 43 через диоды 75 и выходы 38 соединен с базами транзисторов 59 коммутатора 1. Уровень сигнала на этом входе определяет амплитуду наводимой на активном выходе устройства логической единицы. В простейшем случае этот вход остается свободным и уровень логической единицы определяется напряжением Еп1. Логику функционирования устройства в целом можно определить как последовательность сеансов обмена внешнего вычислителя с блоком внешнего управления 7, в ходе которых производятся: установка состояния "обрыв", задающий идентификацию устройством неподключенного к выводу контролируемого элемента канала, начальная установка счетчика выборок 67 блока 5, установка требуемых сигналов на входах коммутатора 1, определяющих состояние каналов устройства, а также чтение уровней сигналов на этих каналах на каждом шаге тестовой последовательности. Работа устройства в режимах имитации неисправности, внутрисхемного тестера и в режиме самоконтроля различается только в логике последовательности команд внешнего вычислителя и не требует каких-либо манипуляций при переходе от одного режима к другому, кроме условия отключения контролируемого элемента в режиме самоконтроля. В начале работы, вне зависимости от режима использования устройства, производится сброс счетчика выборок 65 блока 5 и признака состояния "обрыв", а также перевод в состояние высокого импеданса всех каналов. На следующем этапе проводится самоконтроль устройства, в проверке контактирования каналов, в ходе которой выявляются каналы не находящиеся в состоянии высокого импеданса, например в следствие отказов в коммутаторе 1 или блоке пороговых элементов 6, Проверка контактирования заключается в последовательном чтении логических уровней на каналах устройства при последовательном сбросе и установке триггера 63 формирователя дефекта 2. Несоответствие состояния некоторого пассивного канала установленному признаку состояния "обрыв" означает смещение импеданса этого канала, которое может быть вызвано паразитным сопротивлением неисправного транзистора, либо иным отказом, приведшем к включению данного канала в активное состояние. В случае проверки контактирования при подключенном контролируемом элементе смещение импеданса чаще всего вызывается влиянием активных элементов исследуемой схемы, а также наличием в цепи проверяемого вывода резисторов и конденсаторов, включая влияние емкости монтажа. В режиме самоконтроля при отключенном контролируемом элементе все исправные каналы устройства на первом этапе находятся в состоянии высокого импеданса. В рабочем режиме устойчивое сохранение этого состояния на всех шагах теста означает отсутствие контакта с выводом контролируемого элемента по данному каналу. Завершается самоконтроль устройства проверкой связей между каналами, или "прозвонкой связей". При проведении прозвонки все каналы устройства являются активными, то есть по каждому и них обеспечивается выдача либо логического нуля, либо логической единицы. Прозвонка связей заключается в выявлении пар связанных между собой каналов устройства, которые затем сводятся в общую матрицу связанных каналов. На первом шаге прозвонки на все каналы устройства выдается уровень логического нуля. Затем последовательно по всем каналам от первого до последнего, исключая проверяемый, выдаются сигналы логической единицы с проверкой на каждом шаге состояния проверяемого канала. Если этот канал не связан с каким другим, то на нем сохранится уровень логического нуля, наводимый с соответствующего разряда коммутатора 1. При наличии гальванической связи с некоторым другим каналом на проверяемом появится уровень логической единицы, обнаружение которого позволит программе внешнего вычислителя, управляющей прозвонкой связей, зафиксировать факт связанных между собой каналов. Последовательная прозвонка всех каналов устройства позволяет установить полную картину связей выводов проверяемого элемента. Появление связанных каналов в режиме самоконтроля означает неисправность устройства, вызванную либо отказом схемы, либо действительно наличием паразитной связи между каналами. После проведения самоконтроля, при его положительном результате, возможен переход к работе в одном из основных режимов устройства. В режиме имитации отказов элементов дискретной аппаратуры устройство позволяет вносить в исследуемую схему константные отказы и случайные сбои в цепях схемы, а также функциональные отказы элементов в том числе замыкания и обрывы по их выводам. Имитация константного отказа не представляет сложности и заключается в наведении требуемого логического уровня на соответствующем канале устройства. Имитация случайного сбоя заключается в отслеживании сигналов на выбранных каналах, находящихся в пассивном состоянии, и переводе этих каналов на определенных случайным образом шагах теста в активное состояние с наведением уровней, инверсных прочитанным. Вероятные характеристики вносимых отказов определяется программой внешнего вычислителя и могут изменяться в зависимости от задачи исследования. При имитации функциональных отказов контролируемого элемента на каждом шаге теста проводится анализ реальных реакций на физические воздействия по его входам и реакций программно-логической модели контролируемого элемента, используемой в качестве эталона. При этом имитируемые отказы сначала вносятся в программно-логическую модель, а затем наводятся соответствующими логическими уровнями на выходы контролируемого элемента. Это позволяет имитировать не только внешние отказы типа обрыва или замыкания выводов, но и внутренние отказы элемента, доступные в программно-логической модели. Проверка контролируемого элемента в режиме внутрисхемного тестирования заключается в последовательном проведении следующих операций: проверка шин питания и земли, прозвонка связей и проверка контактирования, формирование и прогон теста, анализ результатов. Прзвонка связей и проверка контактирования соответствуют тем же операциям, проводимым при самоконтроле устройства, с той разницей, что результаты этих операций являются промежуточными и используются программой на следующих этапах тестирования элемента. Проверка шин питания и земли заключается в выдаче по всем каналам устройства логического нуля, при проверке питания, и единицы при проверке земли. Каналы, на которых не обеспечивается заданный логический уровень, считаются соединенными с соответствующими шинами исследуемой аппаратуры. Эта проверка предназначена для блокировки при выполнении следующих операций любых воздействий по каналам, связанным с шинами питания и земли, которая необходима для защиты схемы коммутатора 1 от перегрузок. Кроме этого информация об этих каналах позволяет программно определить ориентацию устройства подключения к контролируемому элементу по отношению порядку расположения его выводов. Формирование тестовых воздействий и анализ результатов тестирования обеспечивается программой внешнего вычислителя без участка устройства, которое воздействует на проверяемый элемент только при непосредственном прогоне уже сформированных тестовых воздействий и фиксации реакций на них на всех шагах теста. Программная доступность каналов устройства позволяет обеспечивать прогон любых по насыщенности и длительности тестов, а работа устройства не зависит от сложности контролируемого элемента. Практическая реализация устройства не вызывает технических затруднений, поскольку его функционирование основано на известных физических принципах, а узлы и блоки могут быть выполнены на известных широко применяемых типовых элементах. Структура устройства позволяет функционально объединить несколько блоков или их части в более крупные типовые узлы. Например регистры 62 формирователя дефекта 2, регистры 64 блока управления коммутацией 3, дешифратор 4, шинные формирователи 71 и 74 блоков 6 и 7, с учетом разделения на группы могут быть выполнены в виде параллельно включенных по управляющим входам и выходам и разделенных по выходам контроллеров параллельного интерфейса типа 580ВВ55 или аналогичных. Реализация остальных узлов и блоков может быть выполнена на основе соответствующих серийно изготавливаемых широко распространенных элементов. В качестве внешнего вычислителя может использоваться персональный компьютер типа IBM PC, а само устройство выполнено в виде типового контроллера, конструктивно и функционально совместимого с шиной ISA и устанавливаемого в корпус компьютера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| ДАТЧИК КОНТРОЛЯ НИТИ | 1993 |

|

RU2062748C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| СИСТЕМА ДЛЯ УПРАВЛЕНИЯ СОВЕРШЕНИЕМ СДЕЛОК | 1998 |

|

RU2146836C1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

| КЛЮЧЕВОЙ ЭЛЕМЕНТ С ДИАГНОСТИКОЙ В РЕАЛЬНОМ ВРЕМЕНИ | 2014 |

|

RU2568655C1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094815C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЗАДАННОГО ЧИСЛА ИМПУЛЬСОВ | 1993 |

|

RU2066921C1 |

| ЦИФРОВОЙ МАЛОГАБАРИТНЫЙ USB ОСЦИЛЛОГРАФ | 2009 |

|

RU2402024C1 |

| Тестер для проверки многожильного кабеля | 2024 |

|

RU2829069C1 |

Предлагаемое изобретение относится к вычислительной технике и может быть использовано при отладке и контроле дискретной аппаратуры, а также непосредственно как средство поиска дефектов в цифровых узлах. Техническим результатом является расширение функциональных возможностей устройства за счет имитации неисправностей как на отдельных, так и на нескольких выводах цифровых элементов, обеспечения возможности работы с элементами, имеющими двунаправленные шины, а также возможности использования устройства в качестве универсального цифрового внутрисхемного тестера за счет создания аппаратно-программной защиты каналов устройства от перегрузки введения проверки контактирования с выводами проверяемого элемента. Устройство для имитации отказов и внутрисхемного тестирования элементов дискретной аппаратуры содержит коммутатор 1 с подключенным контролируемым элементом, формирователь дефекта 2, блок управления коммутацией 3, дешифратор дефекта 4, блок задания режима имитации 5, блок пороговых элементов 6, блок внешнего управления 7. 6 з.п. ф-лы, 8 ил.

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-10-20—Публикация

1995-11-17—Подача