Изобретение относится к антенной технике и может быть использовано в системах контроля радиотехнических систем в качестве имитатора параметров направления на удаленные источники излучения.

В качестве аналога можно рассмотреть устройство (авт. св. N 1385099, кл. G 01 R 29/08, опубл. 20.03.88). Это устройство содержит генератор СВЧ-сигнала, разветвители, контрольные излучатели (КИ), излучатели испытуемой радиоэлектронной системы (РЭС) диаграммообразующего материала с отверстиями и прокладку из радиопоглощающего материала с отверстиями, которая разделяет соосно расположенные КИ и излучатели РЭС, причем отверстия выполнены в виде соосных цилиндров определенного диаметра и высоты.

Это устройство имитирует только фиксированные направления на источник излучения, так как фаза сигнала на контрольных излучателях имеет одно и тоже значение от излучателя к излучателю.

Другой известный имитатор содержит генератор, блок коммутации и разделения, блок сопряжения, блок управления, сумматоры, решетку облучателей, решетку дополнительных излучателей, фидерные линии, еще одну решетку излучателей, петли связи, заглушки, коаксиальные кабели, вторую решетку излучателей (авт. св. N 1688333, кл. H 01 Q 17/00, опубл. 30.01.91). Этот имитатор создает в раскрыве своих излучателей квазиплоские волны в ближней зоне. Изменение фазового центра осуществляется за счет изменения мощности сигнала на излучателях, расположенных на вогнутой сферической поверхности радиуса R, проходя при этом еще две группы излучателей, расположенных на выпуклых сферических поверхностях. Этот имитатор имеет большие габариты, а также недостаточную точность формирования плоской волны из-за ошибок выполнения сферических поверхностей (грубая апроксимация).

В качестве прототипа предлагаемого имитатора принят имитатор (авт. св. N 1415291, кл. H 01 Q 17/00, опубл. 07.08.88).

Этот имитатор содержит М излучателей, размещенных на сферической поверхности, отстоящей от излучателя испытуемой РЭС на расстояние R, определяемой дальней зоной, М светвителей (сумматоров), N•M фазовращателей, N делителей СВЧ- сигнала, выполненных на циркуляторах и управляемых реактивных делителях, N СВЧ-генераторов и ЭВМ.

В прототипе антенна испытуемой РЭС находится на большом расстоянии от излучателей имитатора, определяемом дальней зоной. Это расстояние зависит от размеров антенных систем и длины волны, на которой происходит работа, и обычно составляет, как минимум, несколько метров. Кроме того, в прототипе излучаемый сигнал формируется по принципу регулирования амплитуды и фазы, причем при регулировании амплитуды использованы управляемые реактивные делители, имеющие ограничения по быстродействию (использована электромеханическая схема), и, следовательно, имитатор имеет ограничения при осуществлении сложных радиотехнических сценариев в реальном времени.

Предлагаемое изобретение решает задачу проверки и моделирования функционирования РЭС, использующих фазовый метод определения пеленга, имитируя несколько удаленных источников излучения при быстроменяющемся их положении в пространстве и быстрой перестройке несущей частоты сигнала и создавая в лабораторных условиях при минимальных размерах установок сценарии радиоэлектронной обстановки на входе испытуемых систем, которые практически невозможно создать в полигонных условиях.

В качестве технического результата, получаемого при использовании предлагаемого имитатора по сравнению с прототипом, можно рассматривать обеспечение работы в ближней зоне (уменьшение габаритов) в реальном времени за счет создания плоского фронта волны на выходе излучателей имитатора путем электронного регулирования фаз сигнала каждого имитирующего источника, в то время как в прототипе изменение фазового центра осуществляется изменением мощности сигнала в системе излучателей, расположенных на сферических поверхностях сравнительно большого радиуса, с помощью электромеханических управляемых реактивных делителей.

Для достижения указанного технического результата в имитатор источников радиосигналов, содержащий М излучателей, N СВЧ-генераторов, N•M управляемых фазовращателей, управляющую ЭВМ, а также включенные между СВЧ-генераторами и соответствующими управляемыми фазовращателями N делителей мощности, N светвителей, введены задающий генератор, дешифратор номера канала и N блоков управления, каждый из которых включает в себя формирователь сигналов управления фазовращателями и формирователь сигналов управления генератором СВЧ, соответствующие входы которых подключены к выходам задающего генератора, дешифратора адреса канала и через введенный параллельный интерфейс к управляющей ЭВМ, а выходы -к входам управления соответствующих фазовращателей и СВЧ-генераторов, СВЧ-выходы каждого из N СВЧ- генераторов соединены с входами соответствующих делителей мощности, число которых тоже N, имеющих M выходов, причем каждый из M выходов делителя мощности соединен с СВЧ-входом соответствующего по номеру фазовращателя, образуя таким образом N-канальную систему, имеющую M выходов СВЧ-сигнала, причем выходы каждого канала соединены с N входами M светвителей таким образом, что первый выход первого канала соединен с первым входом первого светвителя, второй выход первого канала соединен с первым входом второго светвителя и т.д. M-ный выход первого канала соединен с первым входом М-ного светвителя, первый выход второго канала соединен с второым входом первого светвителя, второй выход второго канала соединен с второым входом второго светвителя и т.д. М-ный выход второго канала соединен с первым входом М-ного светвителя, первый выход N-ного канала соединен с N-ым входом второго светвителя и т.д. М-ный выход первого канала соединен с N-ным входом M-ного светвителя, выходы каждого из M светвителей соединены с соответствующим излучателем имитатора, при этом излучатели расположены соосно антенным элементам испытуемой РЭС на расстоянии ,

,

где l -длина волны,

а между излучателями имитатора и излучателями испытуемой РЭС установлены развязывающие радиопоглощающие блоки.

При этом:

управляемый фазовращатель выполнен в виде фазовращателя с электронным цифровым управлением;

формирователь сигнала управления фазовращателем содержит таймер, процессор, формирователь адреса, коммутатор адреса, ОЗУ, коммутатор данных, регистр и ключевые усилители тока, причем выходы ключевых усилителей тока являются выходами формирователя сигналов управления фазовращателем (ФСУФ) для подключения к управляющим входам соответствующих аттенюаторов и фазовращателей, вход ключевых усилителей тока соединен с выходом регистра, первый вход которого подключен к выходу коммутатора данных, второй вход регистра соединен с третьим выходом процессора, третий вход регистра с четвертым выходом процессора, который также подключен к первому входу формирователя адреса и к четвертому входу таймера, первый вход коммутатора данных является входом ФСУФ для подключения к шине "данные пеленга" интерфейса, второй вход коммутатора данных подключен к третьему входу ОЗУ и к третьему входу коммутатора адреса и служит входом ФСУФ для подключения к третьему выходу дешифратора адреса канала, третий вход коммутатора данных является входом ФСУФ для подключения к шестому выходу дешифратора адреса канала, своим четвертым входом коммутатор данных подключен к входу-выходу ОЗУ, первый выход коммутатора адреса является входом ФСУФ для подключения к шине "адрес данных пеленга" интерфейса, первый вход ОЗУ соединен с выходом коммутатора адреса, второй вход ОЗУ соединен с вторым выходом процессора, второй вход коммутатора адреса подключен к выходу формирователей адреса, который своим вторым входом подключен к первому выходу процессора, первый вход процессора является входом ФСУФ для подключения к второму выходу дешифратора адреса канала, второй вход процессора является входом ФСУФ для подключения к четвертому выходу дешифратора адреса канала, третий вход процессора является входом ФСУФ для подключения к четвертому выходу дешифратора адреса канала, третий вход процессора является входом ФСУФ для подключения к пятому выходу дешифратора адреса канала, четвертый вход процессора соединен с вторым входом таймера и является входом ФСУФ для подключения к выходу ЭГ, пятым входом процессор соединен с выходом таймера, первый вход таймера является входом ФСУФ для подключения к шине "данные таймера" интерфейса, третий вход таймера является входом ФСУФ для подключения к седьмому выходу дешифратора адреса канала;

дополнительно в имитатор введены N•M управляемых аттенюаторов, включенных соответственно между фазовращателями и выходами делителей мощности, а входы управления аттенюаторов подключены к дополнительным выходам формирователей сигналов управления фазовращателями;

формирователи сигналов управления генераторами СВЧ выполнены идентично выполнению формирователей сигналов управления фазовращателями;

в частном варианте исполнения имитатора излучатели имитатора расположены линейно относительно элементов антенной системы испытуемой РЭС.

Сравнение предлагаемого имитатора с прототипом показывает, что отличительными признаками предлагаемого имитатора является иное расположение излучателей, (не на сферической поверхности, а на плоскости), обеспечение минимального расстояния между излучателями имитатора и антенной системой испытуемой РЭС за счет РРПБ, введение N блоков управления, включающих формирователи сигналов управления фазовращателями и формирователи сигналов управления СВЧ-генераторами, введение дешифратора адреса канала, параллельного интерфейса и задающего генератора. Причем наличие в каждом из вышеуказанных формирователей сигналов управления коммутатора адреса, коммутатора данных, ОЗУ, формирователя адреса, специального процессора и программируемого таймера обеспечивает запись данных о параметрах сигнала (портрет сигнала) от ЭВМ и их считывание параллельно в различных каналах с своим заданным темпом и формирование на выходах фазовращателей соответствующих каналов СВЧ-сигналов с такими параметрами фазовых сдвигов, что, проходя через светвители, РРПБ и излучатели, на входе антенной системы испытуемой РЭС создается квазиплоский фронт волны для каждого из N сформированных в данный момент времени сигналов.

Таким образом процесс формирования сложного многосигнального сценария радиотехнической обстановки в предлагаемом имитаторе сигналов и местоположения отдельных имитируемых РЭС с их изменением в реальном времени, в то время как в прототипе и аналогах при последовательном управлении от ЭВМ изменением параметров сигналов от многих источников и конструктивное исполнение аналогов и прототипа не позволяют реализовать имитацию параллельной работы РЭС с быстроизменяемыми параметрами в реальном времени.

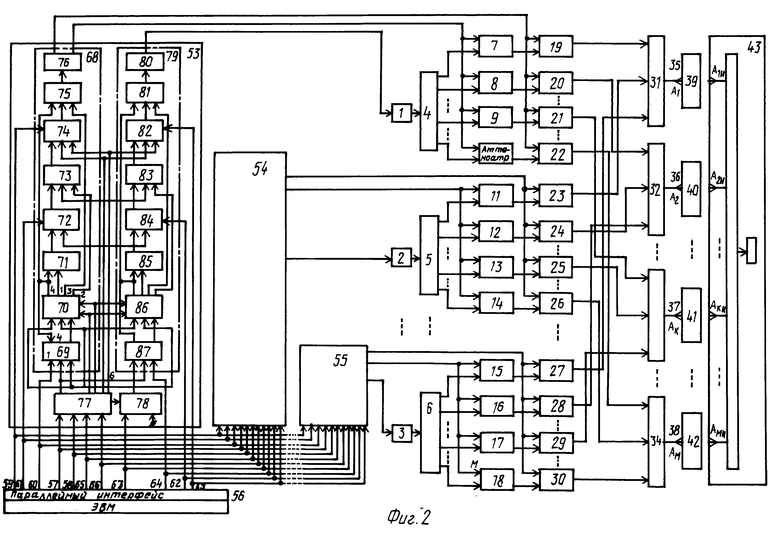

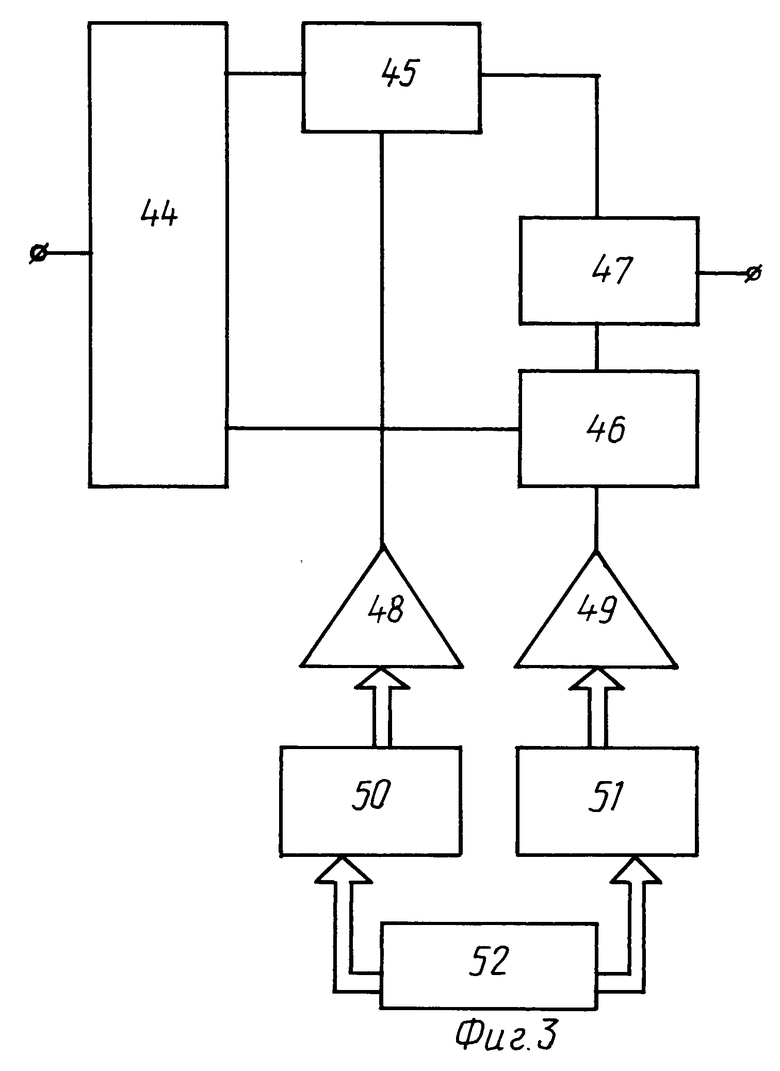

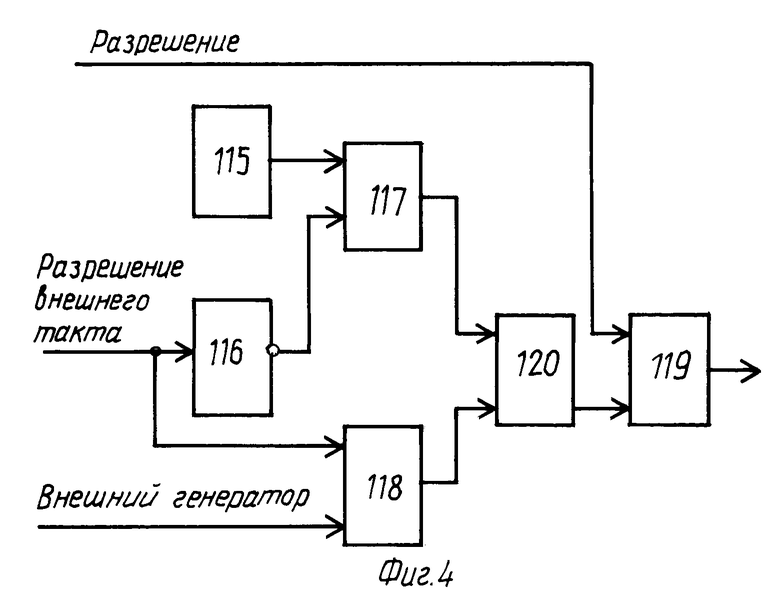

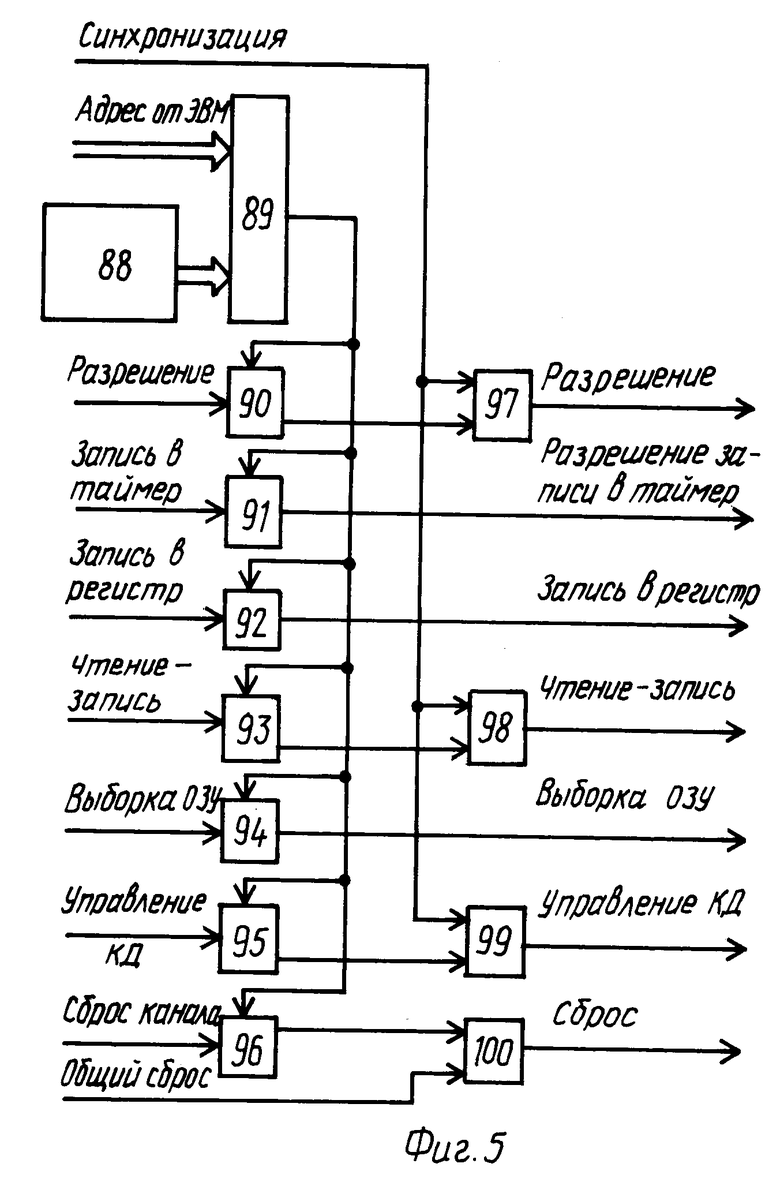

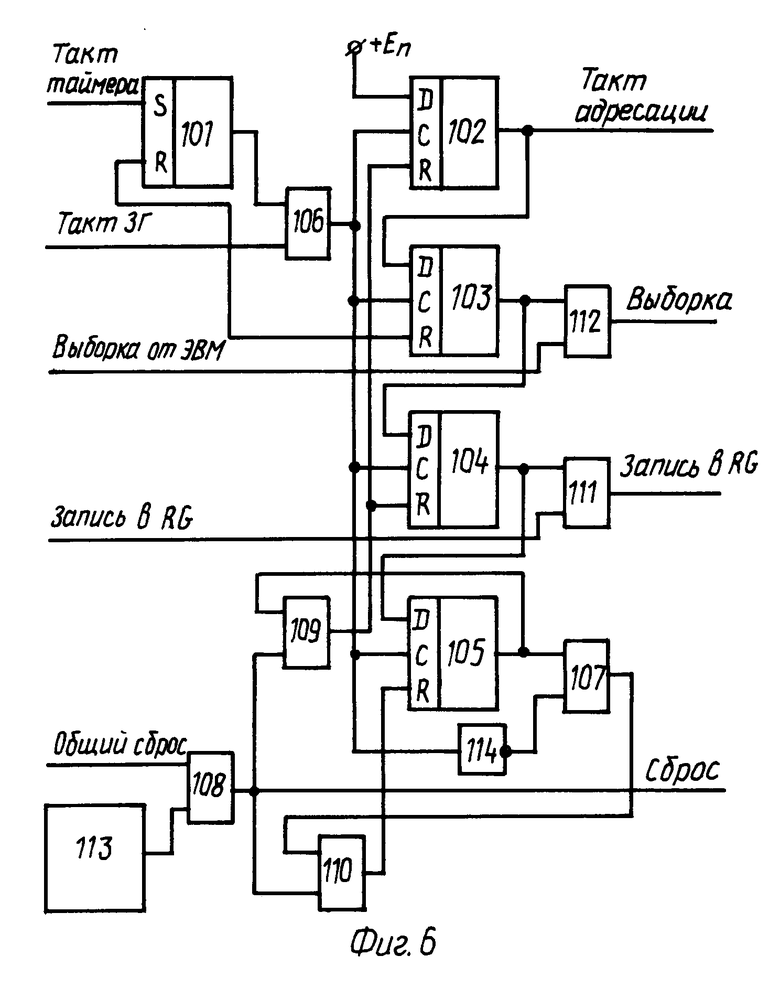

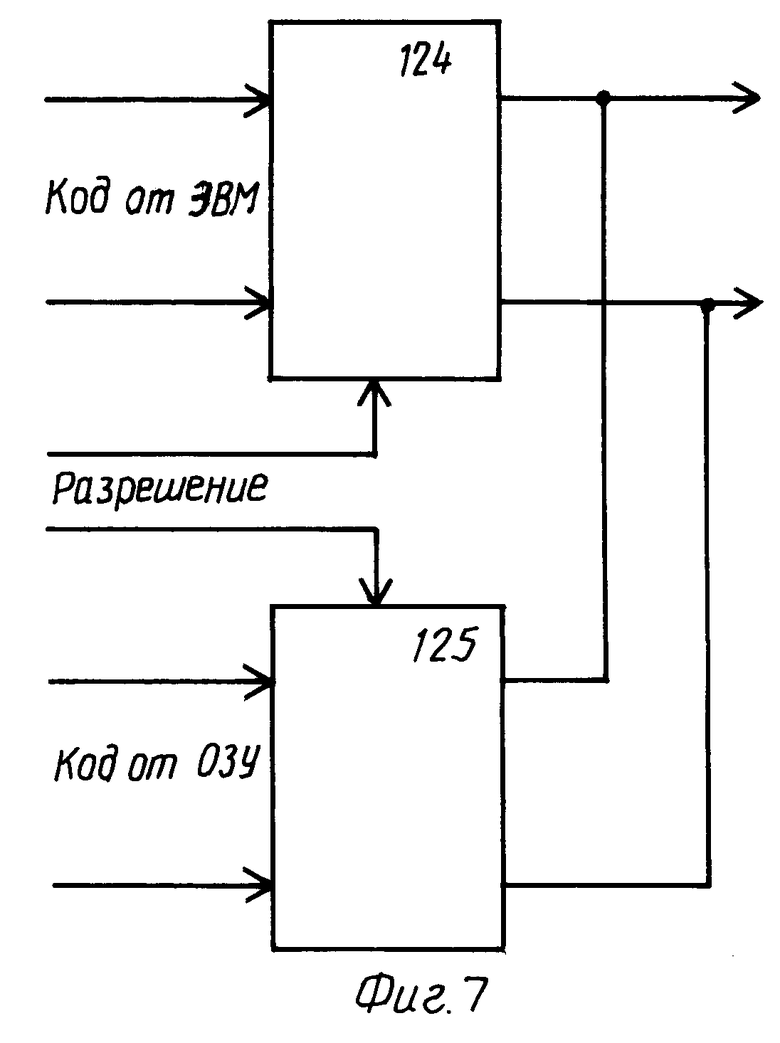

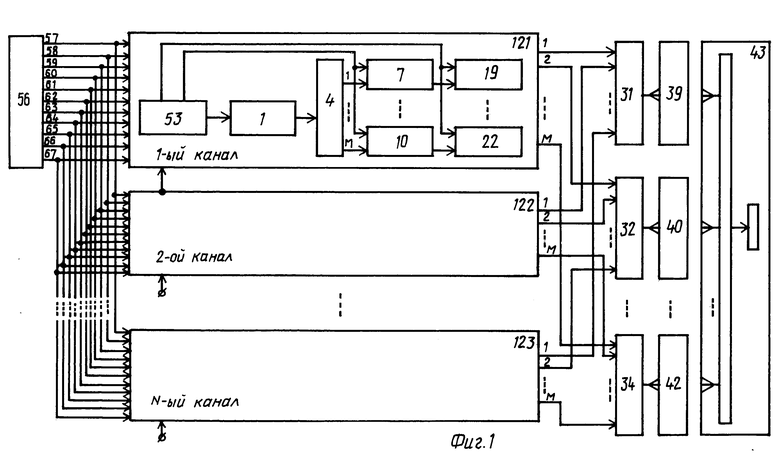

На фиг.1 изображена укрупненная структурная схема предлагаемого имитатора; на фиг. 2 структурная электрическая схема предлагаемого имитатора; на фиг. 3 электрическая схема электронного фазовращателя; на фиг.4 - электрическая схема задающего генератора; на фиг.5 -электрическая схема дешифратора адреса каналов; на фиг.6 электрическая схема процессора; на фиг.7 электрическая схема коммутатора данных.

Имитатор источников радиосигналов содержит N высокочастотных генераторов сигналов 1 3, формирующих сигналы на заданных частотах, например f1, fK, fN в качестве генераторов могут быть использованы, например генераторы типа НР 8791 фирмы Hewlett Packard (США), которые могут формировать сигналы в различных диапазонах частот и с различными видами модуляции. Выходы генераторов 1 3 подключены соответственно к входам делителей 4 6, количество которых также равно N. Делители представляют собой по существу разветвители СВЧ- сигнала и выполнены по схеме симметричного делителя мощности на М каналах, где М число излучателей антенной системы имитатора. Выходы делителей 4 6 через последовательно включенные управляемые аттенюаторы 7 18 и управляемые фазовращатели 19 30 подключены к входам светвителей 31 34. Число светвителей равно М, а число управляемых аттенюаторов и фазовращателей равно N•M. К выходам светвителей подключены излучатели 35 38 антенной системы имитатора, на выходе излучателей установлены развязывающие радиопоглощающие блоки РРПБ 39 42.

В имитаторе в качестве примера приведено линейное расположение излучателей имитатора относительно антенной системы РЭС. В каждом конкретном случае расположение излучателей имитатора должно соответствовать расположению элементов антенной системы испытуемой РЭС с соблюдением соосности. Причем между апертурами имитатора и исследуемой или тестируемой радиоэлектронной системой (РЭС) 43 зазор удовлетворяет условию

где l длина рабочей волны.

Исследуемая или тестируемая РЭС может содержать М элементов антенной системы, которые могут быть аналогичны излучателям имитатора, и другие блоки, например диаграммообразующую схему, приемники и т.п. Аттенюаторы 7 18 могут быть выполнены в виде управляемого цифровым кодом ступенчатого аттенюатора, каждая ступень которого имеет свою весовую значимость вносимого затухания при ее включении, шаг затухания определяется наименьшим значением вносимого затухания ступени, включаемой младшим разрядом управляющего кода. Аттенюаторы выполнены по обычной схеме на СВЧ- диодах и резисторах аналогично аттенюатору, например используемому в быстроперестраиваемом имитаторе сигналов типа НР 8791А фирмы Hewlett Packard (США) быстрой аттенюаторной сборки (Fast Attenuator Assembly) 96792-60131. Фазовращатели 19 30 в предлагаемом имитаторе могут быть выполнены как электронный управляемый фазовращатель, описанный (патент США N 4379264, НКИ 328-24, 1988). Светвители 31 34, также как и делители 4 6 могут быть выполнены в виде пассивных элементов на полосковых линиях с учетом минимальных потерь мощности сигнала по общеизвестным схемам. Аттенюаторы и фазовращатели образуют последовательно включенные цепочки, объединенные в M группы по N параллельных цепочек каждая. Выходы N делителей 4 6 подключены к цепочкам аттенюаторы-фазовращатели следующим образом. Первый выход первого делителя 4 подключен к первой цепочке первой группы, второй выход делителя 4 подключен к первой цепочке второй группы и т.д. M-ный выход делителя 4 подключен к первой цепочке M-ной группы. Первый выход второго делителя 5 подключен к второй цепочке первой группы, второй выход делителя 5 подключен к второй цепочке второй группы и т.д. M-ный выход делителя 5 подключен к второй цепочке M-ной группы. И, наконец, первый выход N-ого делителя 6 подключен к N-ой цепочке первой группы, второй выход делителя 6 подключен к N-ой цепочки второй группы и т.д. M-ный выход делителя 6 подключен к N-ной цепочке M-ной группы.

Фазовращатель содержит гибридное кольцо 44 с одним входом и двумя выходами, выходной сигнал с одного выхода сдвинут относительно сигнала с другого выхода на 90o, к каждому из этих выходов подключены управляемые усилители 45 и 46, выходы которых подключены к суммирующему блоку 47, входы управления усилителей через соответствующие ЦАП 48 и 49 и ППЗУ 50 и 51 подключены к выходам фазосдвигающего селектора 52, в качестве которого может быть использован счетчик. В описанном электронном управляемом фазовращателе его входом является вход гибридного кольца, выходом выход суммирующего блока, а входом управления вход фазосдвигающего селектора. В том случае, если блоки управления в предлагаемом имитаторе выполнены так, как описано выше, то сдвигающий селектор 52 и ППЗУ 50 и 51 исключаются и входами управления электронного управляемого фазовращателя являются входы ЦАП 48 и 49, для подключения к ним выходов БУ 53 55.

В качестве управляемого фазовращателя может быть использован не только электронный, но и механический и электромеханический фазовращатели, однако, при этом в случае механического фазовращателя управление им осуществляется вручную, без участия электронных блоков управления, ЗГ, дешифратора номера канала и ЭВМ с интерфейсом. В случае электромеханического фазовращателя с управлением, например от шагового двигателя, изменяется выполнение БУ в связи с необходимостью управления шаговым двигателем. Однако последние два варианта могут быть использованы в целях калибровки предлагаемого имитатора в первом варианте его исполнения или для настройки РЭА, например фазовых пеленгаторов.

РРПБ 39 42 может быть выполнены в виде набора РП пластин, в которых выполнены отверстия различного диаметра в пластинах, примыкающих к излучателям имитатора и излучателям испытуемой РЭС, диаметры отверстий совпадают с диаметрами излучателей, а в остальных пластинах диаметры отверстий уменьшаются от краев к центру, благодаря чему отраженные сигналы в сторону излучателей ослабляются (авт. св. N 1385099, кл. G 01 R 29/08, 1988, Бл. 12). РРПБ могут быть выполнены и по другому.

Аттенюаторы 7 18 и фазовращатели 19 34 имеют управляющие входы, к которым подключены выходы N блоков управления: первый 53, k-ный 54 и N-ый 55, каждый из которых имеет M выходов управления аттенюаторами, M выходов управления фазовращателями и N выходов управления СВЧ- генераторами, а также входы, подключенные к интерфейсу 56.

Интерфейс 56 своими входами соединен с выходами ЭВМ и имеет следующие выходные шины:

57 режим работы;

58 адрес канала;

59 данные пеленга;

60 данные таймера;

61 адрес данных пеленга;

62 адрес данных СВЧ-генератора;

63 данные СВЧ-генераторов;

64 данные таймера генератора СВЧ;

а также имеет выходы:

65 синхронизация общая;

66 сброс общий;

67 разрешение внешнего такта.

В формирователь сигнала управления фазовращателем (ФСУФ) 68 входят таймер 69, процессор 70, формирователь адреса 71, коммутатор адреса 72, оперативное запоминающее устройство ОЗУ 73, коммутатор данных 74, регистр 75, ключевые усилители тока 76.

Выходы ключевых усилителей тока 76 соединены с управляющими входами соответствующих аттенюаторов 7, 10, 13 и 16 и фазовращателей 19, 22, 25 и 28. Вход ключевых усилителей 76 соединен с выходом регистра 75, первый вход которого подключен к выходу коммутатора данных 74, второй вход регистра 75 соединен с третьим выходом процессора 70, третий вход регистра 75 с четвертым выходом процессора 70, который также подключен к первому входу формирователя адреса 71 и к четвертому входу таймера 69. Коммутатор данных 74 своим первым входом подключен к шине 59 интерфейса 56, вторым входом к третьему выходу дешифратора адреса канала 77, который также подключен к третьему входу ОЗУ 73 и к третьему входу коммутатора адреса 72, своим третьим входом коммутатор данных 74 подключен к шестому выходу дешифратора адреса канала 77, своим четвертым входом коммутатор данных 74 подключен к входу-выходу ОЗУ 73, первый вход коммутатора адреса 72 подключен к шине 61 интерфейса 56, первый вход ОЗУ 73 соединен с выходом коммутатора адреса 72, второй вход ОЗУ 73 соединен с вторым выходом процессора 70. Второй вход коммутатора адреса 72 подключен к выходу формирователей адреса 71, который своим вторым входом подключен к первому выходу процессора 70, первый вход процессора 70 соединен с вторым выходом дешифратора адреса канала 77, второй вход соединен с четвертым выходом дешифратора адреса канала 77, третьим входом подключен к пятому выходу дешифратора адреса канала 77, четвертым входом к выходу ЗГ 78, который также подключен к второму входу таймера 69, пятым входом процессор 70 соединен с выходом таймера 69, который своим первым выходом соединен с шиной 60 интерфейса 56, своим третьим входом с седьмым выходом дешифратора адреса канала 77, который своим первым, вторым, третьим и четвертыми входами соединен соответственно с шинами 57 и 58 и выходами 65, 66 интерфейса 56, выход 67 которого подключен к первому входу ЗГ 78, второй вход ЗГ 78 служит для подключения внешнего генератора, третий вход ЗГ 78 подключен к первому выходу дешифратора адреса канала 77.

В блоки управления 53 55 входят дешифратор адреса канала 77, задающий генератор 78, формирователь сигналов управления фазовращателем 68, а, кроме того, формирователь сигналов управления генераторами СВЧ (ФСУГ) 79, которые содержит ключевые усилители 80, регистр 81, коммутатор данных 82, ОЗУ 83, коммутатор адреса 84, формирователь адреса 85, процессор 86 и таймер 87. Выходы ключевых усилителей 80 соединены с управляющими входами перестраиваемого генератора СВЧ 1, вход усилителей 80 соединен с выходом регистра 81, первый вход которого подключен к выходу коммутатора данных 82, второй вход подключен к выходу коммутатора данных 82, второй вход регистра 81 соединен с третьим выходом процессора 86, третий вход регистра 81 с четвертым выходом процессора 86, который также подключен к первому входу формирователя адреса 85 и к четвертому входу таймера 87. Коммутатор данных 82 своим первым входом подключен к шине 63 интерфейса 56, вторым входом к третьему выходу дешифратора адреса канала 77, который также подключен к третьему входу ОЗУ 83 и к третьему входу коммутатора адреса 84, своим третьим входом коммутатор данных 82 подключен к шестому выходу дешифратора адреса канала 77, своим четвертым входом коммутатор данных 82 подключен к входу-выходу ОЗУ 83, первый вход коммутатора адреса 84 подключен к шине 62 интерфейса 56, второй выход ОЗУ 83 соединен с вторым выходом процессора 86. Второй вход коммутатора адреса 84 подключен к выходу формирователей адреса 85, который своим вторым входом подключен к первому выходу процессора 86, первый вход процессора 86 соединен с вторым выходом дешифратора адреса канала 77, второй вход соединен с четвертым выходом дешифратора адреса канала 77, третьим входом подключен к пятому выходу дешифратора адреса канала 77, четвертым входом к выходу ЗГ 78, который также подключен к второму входу таймера 87, пятым входом процессор 86 соединен с выходом таймера 87, который своим первым входом соединен с шиной 64 интерфейса 56.

Блоки могут быть выполнены, например, таким образом.

Таймеры 69 и 87 могут быть выполнены в виде программируемых счетчиков с параллельным входом для записи данных и реализованы, например, на ИС типа К531ИЕ17.

Формирователи адреса 71 и 85 могут быть выполнены в виде счетчиков с последовательным входом и параллельным выходом, например на ИС типа К531ИЕ17.

Коммутаторы адреса 72 и 84 и коммутаторы данных 74 и 82 представляют собой обычные мультиплексоры, построенные, например на ИС серии К531, и обеспечивающие выполнение операции переключение одного из двух входных кодов на один или два выхода в соответствии с сигналами управления.

ОЗУ 73 и 83 выполнены в виде запоминающего устройства на статических ИС, например на ИС типа К537РУ8.

Регистры 75 и 78 представляют собой обычный регистр с параллельной записью данных и параллельным выходом и могут быть выполнены, например на ИС типа К531ИР22 или К531ИР23.

Ключевые усилители тока 76 и 80 выполнены по общеизвестным схемам на транзисторах или ИС.

Дешифратор адреса каналов 77 содержит переключатель 88, компаратор 89, логические элементы И 90 96, логические элементы ИЛИ 97 100, причем первым входом дешифратора адреса канала 77 является первый вход компаратора 89, вторым входом этого дешифратора являются первые входы логических элементов ИЛИ 97 99, четвертым входом первый вход логического элемента ИЛИ 100. Первым выходом дешифратора адреса канала 77 является выход элемента ИЛИ 97, вторым выходом выход элемента ИЛИ 100, третьим выход элемента ИЛИ 98, четвертым выход элемента И 94, пятым выход элемента И 92, шестым выход элемента ИЛИ 99, седьмым выход элемента И 91. Между собой блоки, входящие в дешифратор адреса канала 77 соединены следующим образом: второй вход компаратора 89 подключен к выходу переключателя 88, выход компаратора соединен со вторыми входами элементов И 90 96, второй вход элемента ИЛИ 97 соединен с выходом элемента И 90, второй вход элемента ИЛИ 98 соединен с выходом элемента И 93, второй вход элемента ИЛИ 99 соединен с выходом элемента И 95, второй вход элемента ИЛИ 100 соединен с выходом элемента И 96.

Процессор 70, также как и процессор 86, содержит RS-триггер 101, четыре D-триггера 102 105, логические элементы И 106 и 107, логические элементы ИЛИ 108 112, схему сброса при включении источника питания 113, инвертора 114.

Вышеуказанные элементы процессора 70 соединены следующим образом. Вход R RS-триггера 101 соединен с входами R D-триггеров 102 104 и с выходами элемента ИЛИ 109, выход RS-триггера 101 соединен с первым входом элемента И 106, выход которого подключен к С-входам D-триггеров 102105 и к входу инвертора 114, выход инвертора 114 подключен к первому входу элемента И 107, второй вход которого соединен с выходом D-триггера 105 и с первым входом элемента И 109, второй вход которого подключен к первому входу элемента ИЛИ 110 и к выходу элемента ИЛИ 108. Вход D D-триггера 102 подключен к плюсовой клемме источника питания, выход этого триггера соединен с входом D D-триггера 103. Выход триггера 103 подключен к D входу триггера 104 и к первому входу элемента ИЛИ 112. Выход триггера 104 соединен с D входом D-триггера 105 и с первым входом элемента ИЛИ 111. Выход элемента 107 подключен к второму входу элемента ИЛИ 110, выход которого соединен с R-входом D-триггера 105. Схема сброса 113 представляет собой соединенные между собой резистор и конденсатор, причем резистор подключается к плюсовой клемме источника питания, а конденсатор к минусовой клемме источника питания, точка соединения резистора и конденсатора подключена к входу инвертора, например на ИС типа К564ЛН2, выход инвертора соединен с первым входом элемента ИЛИ 108.

Первым входом процессора является второй вход элемента ИЛИ 108, вторым входом второй вход элемента ИЛИ 112, третьим входом второй вход элемента ИЛИ 111, четвертым входом второй вход элемента И 106, пятым входом S-вход триггера 101. Выходы процессора: первым выходом является выход D-триггера 102, вторым выход элемента ИЛИ 112, третьим выход элемента ИЛИ 116, четвертым выход элемента ИЛИ 108.

Задающий генератор 77 представляет собой обычный кварцевый генератор 115 и набор логических элементов инвертор 116, элементы И 117, 118, 119, элемент ИЛИ 120, соединенные между собой следующим образом. Выход кварцевого генератора подключен к первому входу элемента И 117, второй вход которого подключен к выходу инвертора 116, вход которого подключен к первому входу элемента И 118, выход которого подключен к первому входу элемента ИЛИ 120, второй вход которого подключен к выходу элемента И 117, выход которого подключен к входу элемента И 119, выход которого является выходом ЗГ 77, а первый вход элемента И 119 является третьим входом ЗГ 77, вторым входом ЗГ 77 является второй вход элемента И 118, первым входом ЗГ 77 является вход инвертора 116.

Каждый из аттенюаторов 7.18 представляет собой несколько последовательно включенных управляемых секций или ступеней, которые в обычном состоянии затухания практически не вносят, затухание обеспечивается под воздействием управляющих сигналов. Каждая секция или ступень аттенюатора может иметь различное весовое значение вносимого затухания. Шаг изменения затухания в этом случае определяется ступенью с наименьшим весовым значением затухания. Число ступеней аттенюатора и наименьший шаг затухания определяются, исходя из заданного динамического диапазона изменений мощности (амплитуды) сигнала и требуемой точности ее установки. Установка необходимого значения затухания обеспечивается подачей на него соответствующего управляющего кода. Аттенюатор может быть выполнен также, как в прототипе, на диодах и резисторах. В прототипе обозначение аттенюатора по каталогу комплектующих изделий фирмы Hewlett Packard 86792-60131.

Таким образом структурная схема предлагаемого имитатора имеет в своем составе ЭВМ с интерфейсом 56 и светвители 31.34, излучатели 35.38, РППБ 39. 42 и N идентичных каналов 121.123, подключенные своими выходами к входам соответствующих светвителей, а входами к выходам интерфейса 56 (подробно описано выше).

Коммутаторы данных 74 и 82 содержат однонаправленную ключевую схему 124 и двунаправленную ключевую схему 125, причем первый вход коммутатора данных является входом ключевой системы 124, второй вход коммутатора адреса является управляющим входом ключевой схемы 125, третий вход коммутатора данных является управляющим входом ключевой схемы 124, четвертый вход коммутатора данных является входом-выходом ключевой схемы 125, выходы ключевых схем объединены поразрядно и являются выходом коммутатора.

Имитатор источников радиосигналов может работать в нескольких режимах:

в режиме непосредственного задания данных от ЭВМ на все фазовращатели, аттенюаторы и генераторы СВЧ выбранного канала о сдвиге фаз и затухании сигнала, имитирующего плоский фронт волны от источника излучения с теми или иными параметрами;

в режиме занесения от ЭВМ в ОЗУ соответствующих данных о параметрах плоского фронта волны для каждого источника излучений, параметров корректировки АЧХ СВЧ-трактов, изменяющихся параметров сигналов на выходе генераторов СВЧ и в таймер темпа считывания этих данных из ОЗУ;

в режиме считывания текущих данных из ОЗУ для формирования портрета сигнала для каждого из имитируемых источников на входе антенной системы исследуемой или тестируемой РЭС в реальном времени.

Причем режимы могут осуществляться каждый в отдельности и в различных своих сочетаниях. Например, в один из каналов записываются данные от ЭВМ, а другие в это время работают в режиме считывания данных из ОЗУ или, воспроизведя имитацию плоского фронта сигнала, по данным, занесенным ранее от ЭВМ в соответствующие регистры.

Имитатор работает следующим образом.

Установка устройств во всех каналах имитатора в исходное состояние осуществляется при его включении или при установке на шине "режим работы" высокого уровня сигнала "сброс общий". В этом случае сигнал "сброс общий" поступает на четвертый вход дешифратора адреса канала 77, а с его второго выхода передается на вторые входы процессоров 70 и 86. С четвертых выходов процессоров сигнал "сброс" высокого уровня поступает на четвертые входы таймеров 69 и 87, первые входы формирователей адреса 71, 85 и третьи входы регистров 75, 81 и устанавливает эти устройства в исходное состояние.

Кварцевый генератор 115 задающего генератора 78 вырабатывает на своем выходе меандровый сигнал с тактовой частотой, который поступает на первый вход схемы И 117, на второй вход этой схемы в этом случае поступает с выхода инвертора 116 сигнал с уровнем логической единицы, что обеспечивает поступление меандрового сигнала на выход схемы И 117. Так как на вход инвертора 116 в данном случае поступает сигнал логического нуля с выхода "разрешение внешнего тракта" 67 интерфейса 56 и на первом входе схемы И 118 будет присутствовать сигнал с уровнем логического нуля, что запрещает прохождение сигнала через эту схему, поступающего на второй вход ЗГ 78 от внешнего генератора. Таким образом на первый вход схемы ИЛИ 120 будет поступать с выхода схемы И 118 сигнал с уровнем логического нуля, а на второй вход этой схемы будет поступать сигнал кварцевого генератора с выхода схемы И 117. С выхода схемы ИЛИ 120 сигнал с тактовой частотой поступает на второй вход схемы И 119, на первый вход этой схемы И поступает сигнал "разрешение", который вырабатывается на первом выходе дешифратора адреса канала 77 и поступает на третий вход ЗГ 78. Высокий уровень сигнала "разрешение" обеспечивает прохождение тактовых импульсов через схему И 119 и с ее выхода на выход задающего генератора 78.

Выбор канала во всех режимах обеспечивается кодом, который поступает на первый вход дешифраторов адреса канала по шине 58 "адрес канала", от интерфейса 56 поступают адрес выбранного канала, а на второй вход задаваемый режим работы по соответствующей шине 57. В каждом дешифраторе номера каналов 77 имеется компаратор 89, который сравнивает поступивший на ее вход код адреса с кодом, который присвоен данному каналу в имитаторе и установлен в этой схеме с помощью встроенных переключателей 88 или с помощью распайки входов компаратора. При совпадении кодов адреса на выходе компаратора 89 формируется сигнал высокого уровня, который поступает на вторые входы схем И 90.96 и разрешает проходить через них кодовым управляющим сигналам, поступающим в виде высокого уровня на их первые входы, которые являются вторым входом дешифратора адреса канала 77. С выходов схем И 91, 92 и 94 управляющие сигналы поступают соответственно на седьмой, пятый и четвертый выходы дешифратора адреса канала. С выходов схем И 90, 93, 95 и 96 управляющие сигналы поступают соответственно на вторые входы схем ИЛИ 97, 98, 99 или 100 и через них на высокий первый, третий, шестой и второй дешифратора адреса канала.

Кроме того, дешифратор адреса канала обеспечивает выполнение общих для всех каналов команд независимо от адресации:

по сигналу высокого уровня, поступающего на четвертый вход "общий сброс" дешифратора адреса канала и далее на первый вход схемы ИЛИ 100, и через нее на второй выход дешифратора;

по сигналу высокого уровня, поступающего на третий вход "синхронизация общая" дешифратора адреса канала и далее на первые входы схем ИЛИ 97, 98 и 99 и через них на соответствующие выходы первый, третий и шестой дешифратора адреса канала.

Для примера рассмотрим работу имитатора при поступлении на первые входы дешифраторов адреса канала по шине 58 "адрес канала" от интерфейса 56 кода, обеспечивающего выбор первого канала, так как при выборе других каналов их работа будет аналогичной. В этом случае после того, как выбран канал на шине 57 "режим работы" формируется код "сброс канала", который поступает на второй вход дешифратора адреса канала 77. При поступлении этого кода на второй вход дешифратора адреса 77 на его втором выходе будет сигнал высокого уровня, который действует так же как и сигнал "сброс общий", устанавливая все блоки только первого канала в исходное состояние.

Сформированные в ЭВМ в виде кода данные об имитируемом направлении на источник радиосигналов поступают от интерфейса по шине 59 "данные пеленга" на первый вход коммутатора данных 74, коды о параметрах сигнала (несущая частота, виды и параметры модуляции) поступают по шине 63 "данные параметра сигнала" на первый вход коммутатора данных 82. Для передачи этих данных с входов на выходы соответствующих коммутаторов данных 74 и 82 по шине 57 "режим работы" на второй вход дешифратора адреса канала 77 поступает через интерфейс 56 код, в котором сигналы "управление КД" и "запись-чтение" передаются низким уровнем и с шестого и третьего выходов дешифратора адреса канала поступают на третий и второй входы коммутатора данных 74. Такая комбинация этих сигналов обеспечивает поступление на первый вход регистра 75 данных с шины 59 "данные пеленга" через коммутатор данных 74. Последующая установка на шине 57 "режим работы" высокого уровня сигнала "запись в регистр" и поступление его на пятый выход дешифратора адреса 77 и далее на третий вход процессора 70, с третьего выхода которого сигнал высокого уровня, поступая на второй вход регистра 75, обеспечивает запись данных в этот регистр и поступление их с его выхода через ключевые усилители тока 76 на все М аттенюаторов и М фазовращателей данного канала, устанавливая соответствующие затухания, нормирующие АЧХ СВЧ- тракта канала для заданной несущей частоты, и сдвиги фаз для формирования плоского фронта волны сигнала на антенных системах исследуемой или тестируемой аппаратуры.

Сформированные в ЭВМ коды о параметрах сигнала (несущая частота, виды и параметры модуляции) поступают по шине 63 "данные параметров сигнала" на первый вход коммутатора данных 82. Для передачи этих данных с входа на выход соответствующего коммутатора данных 82 по шине 57 "режим работы" на второй вход дешифратора адреса канала 77 поступает через интерфейс 56 код, в котором сигналы "управление КД" и "запись-чтение" передаются низким уровнем в/с шестого и третьего выходов дешифратора адреса канала, поступают на третий и второй входы коммутатора данных 82. Такая комбинация этих сигналов обеспечивает поступление на первый вход регистра 81 данных с шины 63 "данные параметра сигнала" через коммутатор данных 82. Последующая установка на шине 57 "режим работы" кода с высоким уровнем сигнала "запись в регистр" и кода с высоким уровнем сигнала "запись в регистр" и поступление его на пятый выход дешифратора адреса 77 и далее на третий вход процессора 86, с третьего выхода которого сигнал высокого уровня, поступая на второй вход регистра 81, обеспечивает запись данных в этот регистр и поступление их с его выхода через ключевые усилители тока 80 на управляющие входы СВЧ- генератора 1, на выходе которого формируется СВЧ- сигнал с заданными параметрами (несущая частота, мощность сигнала, вид модуляции и ее параметры). Этот СВЧ-сигнал, проходя через все M фазовращателей и M аттенюаторов данного канала и попадая на антенные элементы исследуемой системы, имитирует источник сигнала, находящийся в дальней зоне по определенному (заданному пеленгу) и работающему в определенном режиме с заданными параметрами.

При этом сигнал с выхода СВЧ-генератора 1 поступает на вход делителя 4. С первого выхода делителя 4 сигнал последовательно проходит через аттенюатор 7 и фазовращатель 19, с выхода которого он поступает на первый вход светвителя 31 и далее на излучатель 35. Аналогично сигнал с второго выхода делителя 4 через аттенюатор 10, фазовращатель 22 и светвитель 32 поступает на излучатель 36 и т.д. С М-ного выхода делителя 4 через аттенюатор 16, фазовращатель 28 и светвитель 34 сигнал поступает на излучатель 38. Излучатели 35, 36.38 излучают имитируемый сигнал, который проходит через РРПБ 39.42, на антенную систему исследуемой или тестируемой аппаратуры 43.

В режиме записи данных, поступающих на имитатор по шине 59 "данные пеленга", в ОЗУ какого-либо канала запись происходит следующим образом. Выбор канала, в который должна записываться информация от ЭВМ, производится по адресу, поступающему по шине 58 "адрес канала", так же как и в предыдущем режиме. Так же как и в предыдущем режиме может производиться установка имитатора или выбранного канала в исходное состояние по сигналам "сброс общий" и "сброс канала". Для примера рассмотрим работу имитатора в этом режиме при выборе первого канала. По шине "режим работы" 57 на дешифратор адреса канала 77 поступает код с высоким уровнем сигнала "управление КД" и низким уровнем сигнала "чтение-запись". Не меняя уровней, сигнал "управление КД" с шестого выхода дешифратора адреса канала 77 поступает на третьи входы коммутаторов данных 74 и 82, а сигнал "чтение-запись" с третьего выхода дешифратора адреса канала поступает на вторые входы этих коммутаторов данных. Такая комбинация уровней сигналов на входах коммутаторов данных обеспечивает прохождение кодов данных пеленга с первого входа коммутатора 74 на его вход-выход 4 и далее на вход-выход ОЗУ 73, а коды о параметрах СВЧ-сигнала с первого входа коммутатора 82 на его вход-выход 4 и далее на вход-выход ОЗУ 83. Адрес ячейки ОЗУ, в которую должны записываться данные, поступает на имитатор по шине 61 "адрес данных пеленга" и по шине 62 "адрес данных сигнала" во все каналы одновременно на первые входы коммутатора адреса, в нашем случае на коммутаторы адреса 72 и 84. Низкий уровень сигнала "чтение-запись" с третьего выхода дешифратора адреса канала поступает на третьи входы этих коммутаторов адреса 72 и 84 и третьи входы ОЗУ 73 и 83. В коммутаторе адреса 72 этот сигнал обеспечивает поступление "адреса данных пеленга" с его первого входа на выход и далее на первый вход ОЗУ 73. В коммутаторе адреса 84 этот сигнал обеспечивает поступление "адреса данных сигнала" с его первого входа на выход и далее на первый вход ОЗУ 83. После установления на шине 59 "данные пеленга" и шине 63 "данные параметров сигнала", а на шине 61 "адрес данных пеленга" и шине 62 "адрес данных сигнала" необходимых кодов в ЭВМ вырабатывается по шине "режим работы" высокий уровень сигнала "выборка", который, не меняя своего уровня, последовательно проходит дешифратор адреса канала 77 и процессоры 70 и 86, с вторых входов которых поступает на вторые входы соответствующих ОЗУ 73 и 83 и производит запись данных по установленным адресам. После записи данных сигнал "выборка" устанавливается в низкий уровень.

Затем ЭВМ формирует новый адрес ОЗУ и данные, записываемые по этому адресе, которые через интерфейс поступают по соответствующим шинам 61 "адрес данных пеленга" и 59 "данные пеленга" и шинам 62 "адрес данных сигнала" и 63 "данные параметров сигнала".

После установки кодов на этих шинах производится их запись в ОЗУ установкой высокого уровня сигнала "выборка" на шине "режим работы". Таким образом, меняя адреса и данные, записываются в ОЗУ изменение во времени портрета плоского фронта волны от источника излучения и параметры излучаемого сигнала.

При установке на шине "адрес канала" другого кода, т.е. при выборе другого канала имитатора, запись в его ОЗУ будет производиться таким же образом, как описано выше.

Темп считывания данных из ОЗУ 73 и 83 определяется таймерами соответственно 69 и 87, в которые через первые входы соответственно заносятся по шине 60 "данные таймера пеленга" и шине 64 "данные таймера сигнала", необходимые коэффициенты деления тактовой частоты, поступающей на их вторые входы с выхода ЗГ 78. Запись установленных на шинах коэффициентов деления в таймеры производится при установке кода на шине 57 "режим работы" с высоким уровнем сигнала "запись в таймер", который, проходя через дешифратор выбранного канала, с его седьмого выхода поступает на третьи входы таймеров.

В режиме считывания данных из ОЗУ работа имитатора происходит следующим образом.

Сброс и выбор канала осуществляется так же, как и в предыдущих режимах, описанных выше. Описание работы имитатора в этом режиме будем рассматривать, исходя из предположения выбора пользователем первого канала.

По шине 57 "режим работы" на имитатор от ЭВМ через интерфейс 56 поступает код со следующими сигналами высокого уровня:

"чтение-запись";

"управление КД";

Сигнал "управление КД" с шестого выхода дешифратора адреса канала 77 поступает на третьи входы коммутаторов данных 74 и 82, а на вторые их входы

сигнал "чтение-запись" поступает с третьего выхода дешифратора адреса канала 77. Такая комбинация уровней входных сигналов на входе коммутаторов данных обеспечивает прохождение на их выходы соответствующих данных с их входов-выходов, соединенных с входами-выходами соответствующих ОЗУ 73 и 83. Кроме того, сигнал "чтение-запись", поступая на третий вход коммутаторов адреса 72 и 84, обеспечивает прохождение на их выходы кода, соответственно поступающего на их вторые входы с выходов формирователей адреса 71 и 85, а, поступая на третьи входы ОЗУ 73 и 83, переводит их в режим считывания данных, т.е. их вход-выход работает как выход.

Затем в ЭВМ в коде на шине 57 "режим работы" устанавливается высокий уровень сигнала "разрешение", который с первого выхода дешифратора адреса канала 77, поступая на третий вход задающего генератора 78, разрешает прохождение тактовых импульсов на его выход. С выхода задающего генератора сигнал с тактовой частотой поступает на вторые входы таймеров 69 и 87. На выходах таймеров формируются сигналы, частоты которых определены записанными в них кодами коэффициентов деления по первым входам. Таймер может представлять из себя обычный счетчик с параллельной записью коэффициента деления тактовой частоты. На выходе таймера формируется импульсная последовательность с частотой следования импульсов ниже тактовой частоты задающего генератора на коэффициент деления. Тактовые импульсы с выхода задающего генератора, поступающие на четвертые входы процессоров 70 и 86, и импульсы с выхода таймера, поступающие на пятые входы процессоров, разрешают процессорам вырабатывать последовательность команд, обеспечивающих считывание данных из ОЗУ соответственно 73 и 83 и производить запись этих данных в регистры 75 и 81. Это происходит следующим образом. Как в одном, так и в другом формирователях 68 и 79 с первого выхода процессора сигнал "такт адресации" поступает на второй вход формирователя адреса и устанавливает на его выходе очередной адрес ячейки ОЗУ. Код адреса ОЗУ через коммутатор адреса поступает на первый вход ОЗУ. После того как выработан сигнал "такт адресации", процессор вырабатывает на своем выходе сигнал "выборка", который поступает на второй вход ОЗУ, и на входе-выходе ОЗУ, который в режиме чтения данных является выходом, появляется код, который через коммутатор данных поступает на первый вход регистра. Затем на третьем выходе процессора вырабатывается сигнал "запись в регистр", который поступает на второй вход регистра и производит в него запись данных. Эти данные с выхода регистра поступают на вход ключевых усилителей тока, с выходов которых управляющие сигналы устанавливают аттенюаторы и фазовращатели, а также параметры СВЧ-генераторов выбранного канала, что обеспечивает на выходах излучателей имитатора соответствующего СВЧ-сигнала по аналогии с первым режимом работы имитатора. Таким образом с темпом, определенным таймером, производится считывание из ОЗУ портрета плоского фронта волны СВЧ-сигнала в реальном времени работы имитируемых источников сигналов.

Имитация сложной радиотехнической обстановки при получении сигналов от нескольких источников может осуществляться путем считывания данных из ОЗУ нескольких каналов. По аналогии с первым каналом считывание данных портрета имитируемого сигнала может происходить по мере задания этого режима от ЭВМ. Светвление имитируемых сигналов производится в М светвителях 39.42.

Существует режим синхронного начала считывания данных из ОЗУ всех каналов. Для этого в ЭВМ устанавливается сигнал в виде высокого уровня на выходе 65 "синхронизация общая" интерфейса 56 и постпающего на третий вход дешифратора адреса канала 77. В этом случае на первом, третьем и шестом выходах всех дешифраторов адреса каналов имитатора устанавливаются сигналы высокого уровня, которые обеспечивают выполнение третьего режима работы имитатора всеми каналами, т.е. режима считывания данных из ОЗУ. В этом случае обеспечивается имитация работы нескольких источников излучения сигналов от единого отсчетного времени, так как все задающие генераторы в каналах построены с применением однотипных кварцевых резонаторов с достаточно высокой частотой.

Существует также режим работы имитатора с использованием внешнего генератора, который может быть подключен к одному или нескольким каналам. В этом случае на выходе 67 "разрешение внешнего тракта" интерфейса 56 вырабатывается сигнал высокого уровня, который поступает на вход задающего генератора в канале, и разрешает прохождение сигнала тактовой частоты внешнего генератора на его выход.

Коммутатор данных может быть построен на управляемых ключевых схемах, которые представляют собой ключевая схема 124 однонаправленные ключи, ключевая схема 125 двунаправленные ключи, и работает следующим образом в зависимости от уровней управляющих сигналов, поступающих на их второй и третий входы.

При уровне нуля обе ключевые схемы закрыты и не передают на свои выходы, а это значит и на выход коммутатора данных, сигналы, поступающие на первый и четвертый вход коммутатора данных. При уровне нуля на втором входе и уровне единицы на третьем входе коммутатора данных соответственно ключи ключевой схемы 125 будут закрыты, а ключи ключевой схемы 124 открыты, передавая данные с первого входа коммутатора на его выход. При уровне единицы на втором входе и уровне нуля на третьем входе коммутатора данных соответственно ключи ключевой схемы 125 будут открыты, а ключи ключевой схемы 124 закрыты, передавая данные с четвертого входа-выхода коммутатора данных на его выход. При уровне единицы на втором входе и уровне единицы на третьем входе коммутатора данных соответственно ключи ключевых схем 124 и 125 будут открыты, передавая данные с первого входа коммутатора данных на его четвертый вход-выход.

Коммутаторы данных 74 и 82 выполнены по одной и той же схеме с разницей в количестве ключевых схем в соответствии с разрядностью передаваемых данных. Коммутаторы адреса 72 и 84 состоят из двух одинаковых однонаправленных ключевых схем, которые управляются сигналом, поступающим на третий вход коммутатора адреса. При уровне нуля на третьем входе коммутатора адреса будут открыты ключи одной ключевой схемы, а ключи второй ключевой схемы закрыты, передавая данные с первого входа коммутатора адреса на его выход. При уровне единицы на третьем входе коммутатора адреса будут открыты ключи второй ключевой схемы, а ключи первой ключевой схемы закрыты, передавая данные с второго входа на его выход.

Последовательность команд, считывающих данные из ОЗУ, вырабатывается процессором следующим образом. Импульс, поступающий на пятый вход процессора, проходит на S-вход триггера 101 и устанавливает сигнал высокого уровня на его выходе, который поступает на первый вход схемы И 106. На второй вход этой схемы с четвертого входа процессора поступают тактовые импульсы, которые начинают поступать на выход этой схемы и с него на С-входы триггеров 102 105 и на вход инвертора 114. Первый тактовый импульс с выхода схемы И 106 устанавливает высокий уровень сигнала на выходе триггера 102, так как его D-вход подсоединен к плюсовой клемме источника питания. Этот уровень сигнала и будет на первом выходе процессора сигналом "такт адресации". Второй тактовый импульс с четвертого входа устанавливает высокий уровень сигнала на триггере 103, так как его D-вход соединен с выходом триггера 102. С выхода триггера 103 сигнал высокого уровня поступает на первый вход схемы ИЛИ 112 и с ее выхода, сформированный сигнал "выборка" проходит на второй выход процессора. На второй выход схемы ИЛИ 112 поступает сигнал со второго входа процессора, который также обеспечивает формирование сигнала "выборка" на втором выходе процессора. Третий тактовый импульс, поступающий на четвертый вход процессора, устанавливает высокий уровень сигнала на триггере 104, так как его D-вход соединен с выходом триггера 103. С выхода триггера 104 сигнал высокого уровня поступает на первый вход схемы ИЛИ 111 и с ее выхода, сформированный сигнал "запись в регистр" проходит на третий выход процессора. На второй вход схемы ИЛИ 111 поступает сигнал с третьего входа процессора, который также обеспечивает формирование сигнала "запись в регистр" на третьем выходе процессора. Четвертый тактовый импульс, поступающий на четвертый вход процессора, устанавливает высокий уровень сигнала на триггере 105, так его D-вход соединен с выходом триггера 104. С выхода триггера 105 сигнал высокого уровня поступает на первый вход схемы ИЛИ 109, а с ее выхода на R-входы триггеров 101 104 и сбрасывает их в исходное состояние. Кроме того, сигнал с выхода триггера 105 поступает на второй вход схемы И 107, а на ее первый вход поступает сигнал с выхода инвертора 114.

При отсутствии тактового импульса на пятом входе процессора на первом входе схемы И 106 будут присутствовать сигналы низкого уровня и такого же уровня будет сигнал на ее выходе.

Сигнал с выхода схемы И 107 поступает на второй вход схемы ИЛИ 110 и с ее выхода обеспечивает установку в исходное состояние триггера 105. Со следующим импульсом, поступающим на пятый вход процессора, цикл выработки последовательности сигналов считывания данных из ОЗУ процессором повторяется.

Для того, чтобы симитировать источник сигналов, находящийся в дальней зоне по отношению к антенной системе исследуемой РЭС 43, необходимо обеспечить синфазоное облучение всех элементов антенной системы этой аппаратуры, что соответствует падению плоской волны перпендикулярно апертуре. Для этого необходимо, чтобы все фазовращатели, например, для первого канала (источник сигнала генератор СВЧ 1) это фазовращатели 22, 25 и 28 были одинаково установлены относительно начальной фазы на фазовращателе 19. При этом разность фаз на всех излучателях 35.38 должна быть равна 0, что соответствует нулевому пеленгу.

Для измерения угла падения плоской волны на апертуру антенной системы аппаратуры 43 необходимо установить фазовращатели 22, 25 и 28 так, что разность фаз между ними и начальной фазой на фазовращателе 19 соответствовала фазам, вычисляемым по формуле:

Dvi = Klкsinαi ± nπ

где K = 2π/λ1 волновое число;

lk база расстояние центра антенны Aku аппаратуры 43 от центра первой антенны этой аппаратуры A1u;

α1 угол падения плоской волны на апертуру антенной системы аппаратуры 43;

λ1 длина волны сигнала на выходе СВЧ генератора 1;

n целое число.

Для удобства управления разность фаз следует кодировать в градусах с учетом набегов фаз в трактах СВЧ при прохождении СВЧ-сигнала с разной длиной волны с выхода СВЧ-генератора до антенных излучателей имитатора. Задавая значение пеленга в градусах с клавиатуры управляющей ЭВМ, на направляющие входы фазовращателей 19, 22, 25 и 28 будут поступать коды, рассчитанные в ЭВМ для каждого фазовращателя канала по приведенной выше формуле с учетом набега фаз в трактах СВЧ-канала в зависимости от несущей частоты сигнала на выходе СВЧ-генератора 1.

Введенные в каналы 121.123 аттенюаторы с 7 по 18 обеспечивают выравнивание амплитудно-частотных характеристик каналов с учетом прохождения имитируемых сигналов в зависимости от их несущей частоты и параметров модуляции по СВЧ- трактам от выхода генератора СВЧ до излучателей имитатора. Установка необходимых затуханий в аттенюаторах производится кодами, поступающими на входы управления от ЭВМ через интерфейс и соответствующие формирователи сигналов управления.

При установке фазовращателей всех каналов в соответствии с задаваемым направлением на источники излучения сигналов (СВЧ-генераторы с 1 по N-ый) на выходе имитатора получим N плоских волн, падающих на апертуру антенной системы аппаратуры 43, что равносильно поступлению сигналов из разных точек пространства, от источников, находящихся в дальней зоне и имеющих различные параметры (мощность, несущую частоты, параметры модуляции и другие).

Рассмотрим функцию развязывающих радиопоглощающих блоков (РРПБ) 39.42 и зазора между ними и антеннами (излучателями) аппаратуры 43. Блоки 39.42 выполняют роль хорошо согласованного пространственного аттенюатора, изготовленного из листов радиопоглощающего материала с отверстиями, поперечные сечения которых совпадают с апертурами излучателей 34.37 имитатора и антенн аппаратуры 43 в крайних слоях, и уменьшающимися к центру набора листов. Такие РРПБ уменьшают переотраженные волны между излучателями имитатора и аппаратуры 43 на 20 дБ и более, что допускает установку имитатора на малом расстоянии Δl от излучателей аппаратуры 43.

С другой стороны величина зазора Δl должна быть несколько больше λ/20 для того, чтобы потери в радиопоглощающем материале РРПБ не были слишком большими.

Наличие РРПБ и зазора  препятствует распространению продольных волн вдоль зазора.

препятствует распространению продольных волн вдоль зазора.

Таким образом имитатор с РРПБ 39.42 и аппаратура (испытуемая) 43 с антеннами, между которыми имеется зазор, можно рассматривать как развязанный многополюсник, что позволяет производить имитацию направлений и их измерений с большой точностью.

Более подробно сведения даны в (Радиотехника и электроника, т. 39, вып. 2, 1994, М. Наука, с. 177 184.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094815C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОГЕРЕНТНОЙ ПОМЕХИ | 2010 |

|

RU2443058C2 |

| Радиоимпульсный фазометр | 1989 |

|

SU1677655A1 |

| РАДИОИМПУЛЬСНЫЙ АМПЛИФАЗОМЕТР | 1990 |

|

RU2042139C1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2001 |

|

RU2195774C2 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2263401C2 |

| СПОСОБ КАЛИБРОВКИ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2011 |

|

RU2467346C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к антенной технике и радиолокации и может быть использовано в системах контроля и испытания радиотехнических средств в качестве имитатора параметров направления на удаленные источники радиоизлучения. Имитатор решает задачу имитации нескольких удаленных источников излучения при быстро меняющемся их положении в пространстве и быстрой перестройке несущей частоты сигнала и создания в лабораторных условиях при минимальных размерах установок сценария радиоэлектронной обстановки на входе испытуемых систем, которые практически невозможно создать в условиях полигона, при этом обеспечивается работа в ближней зоне в реальном времени за счет создания плоского фронта волны на выходе излучателей имитатора путем электронного регулирования фаз сигнала каждого имитируемого источника. Для достижения указанного результата в имитатор источников радиосигналов, содержащий М излучателей, N СВЧ-генераторов, N•M управляемых фазовращателей, управляющую ЭВМ, N светвителей, а также включенные между СВЧ-генераторами и соответствующими управляемыми фазовращателями N делителей мощности, введены N блоков управления, каждый из которых включает в себя задающий генератор (ЗГ), дешифратор адреса канала, формирователь сигналов управления фазовращателями (ФСУФ) и формирователь сигналов управления СВЧ-генераторами (ФСУГ), соответствующие входы указанных формирователей подключены к выходам задающего генератора, дешифратора адреса канала и через введенный параллельный интерфейс к управляющей ЭВМ, а выходы - к входам управления соответствующих фазовращателей и СВЧ-генераторов, выход каждого из N СВЧ-генераторов соединен с входом соответствующего делителя мощности, общее число которых тоже N, а каждый из М входов делителя мощности соединен с СВЧ-входом соответствующего по номеру фазовращателя, образуя таким образом N-канальную систему, одноименные входы каналов которой, кроме входов для подключения внешних генераторов, соединены между собой параллельно и подключены к соответствующим выходам и шинам интерфейса ЭВМ, и имеющую N•M выходов СВЧ-сигнала, которые через светвители соединены с соответствующими излучателями, расположенными соосно антенным элементам испытуемой РЭС на расстоянии  , где λ - длина волны, а между излучателями имитатора и излучателями испытуемой РЭС установлены развязывающие радиопоглощающие блоки. При этом ФСУР содержит связанные между собой, а также с ЗГ и дешифратором адреса канала таймер, процессор, формирователь адреса, коммутатор адреса, ОЗУ, коммутатор данных, регистр и ключевые усилители тока, а ФСУГ выполнен идентично ФСУФ, причем дешифратор адреса каналов содержит связанные между собой, а также с интерфейсом ЭВМ и блоками управления переключатель, компаратор, семь логических элементов И и четыре логических элемента ИЛИ, а задающий генератор ЗГ содержит кварцевый генератор, инвертор, три логических элемента И и логический элемент ИЛИ. В результате вышеуказанные признаки обеспечивают при формировании сложного многосигнального сценария радиотехнической обстановки осуществление параллельного формирования параметров сигналов и местоположение отдельных имитируемых РЭС с их изменением в реальном времени. 7 з.п. ф-лы, 7 ил.

, где λ - длина волны, а между излучателями имитатора и излучателями испытуемой РЭС установлены развязывающие радиопоглощающие блоки. При этом ФСУР содержит связанные между собой, а также с ЗГ и дешифратором адреса канала таймер, процессор, формирователь адреса, коммутатор адреса, ОЗУ, коммутатор данных, регистр и ключевые усилители тока, а ФСУГ выполнен идентично ФСУФ, причем дешифратор адреса каналов содержит связанные между собой, а также с интерфейсом ЭВМ и блоками управления переключатель, компаратор, семь логических элементов И и четыре логических элемента ИЛИ, а задающий генератор ЗГ содержит кварцевый генератор, инвертор, три логических элемента И и логический элемент ИЛИ. В результате вышеуказанные признаки обеспечивают при формировании сложного многосигнального сценария радиотехнической обстановки осуществление параллельного формирования параметров сигналов и местоположение отдельных имитируемых РЭС с их изменением в реальном времени. 7 з.п. ф-лы, 7 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Коллиматор | 1985 |

|

SU1385099A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Имитатор | 1989 |

|

SU1688333A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Имитатор | 1985 |

|

SU1415291A1 |

Авторы

Даты

1997-10-27—Публикация

1994-12-27—Подача