00

ел о

Јь

ю

блок 28 памяти тестовых воздействий, регистр 29. В устройстве сигналы с внутренних точек дискретной аппаратуры, в которой имитируется неисправность, через второй коммутатор подаются на входы эталонного элемента. При этом на вход, на котором имитируется неисправность, коммутируется сигнал с выхода формирователя дефекта, а сигналы с выходов эталонного элемента коммутируются на внутренние точки дискретной аппаратуры. Благодаря введению в устройство новых узлов - эталонного элемента, второго коммутатора и блока управления коммутацией сигналов - реализована возможность моделировать неисправность на отдельном входе элемента без физического разрыва цепи, к которой подключен этот вход. 1 з.п.ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для имитации отказов дискретной аппаратуры | 1987 |

|

SU1451702A1 |

| Устройство для контроля дискретных объектов | 1988 |

|

SU1642470A1 |

| Устройство для отладки тестов | 1982 |

|

SU1084804A2 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для сопряжения многомашинного комплекса с контролем | 1988 |

|

SU1594549A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ДИСКРЕТНЫХ БЛОКОВ | 1996 |

|

RU2109329C1 |

| Устройство для имитации отказов дискретной аппаратуры | 1984 |

|

SU1183972A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

Изобретение относится к вычислительной технике, а именно, к устройствам, имитирующим отказы и сбои аппаратурных средств цифровой вычислительной техники и может быть использовано при отладке и контроле аппарату рно-п рог раммных средств диагностики дискретной аппаратуры.

Цель изобретения - расширение функциональных возможностей устройства имитации неисправностей за счет имитации неисправностей на отдельных входах и выходах внутренних элементов дискретной аппаратуры.

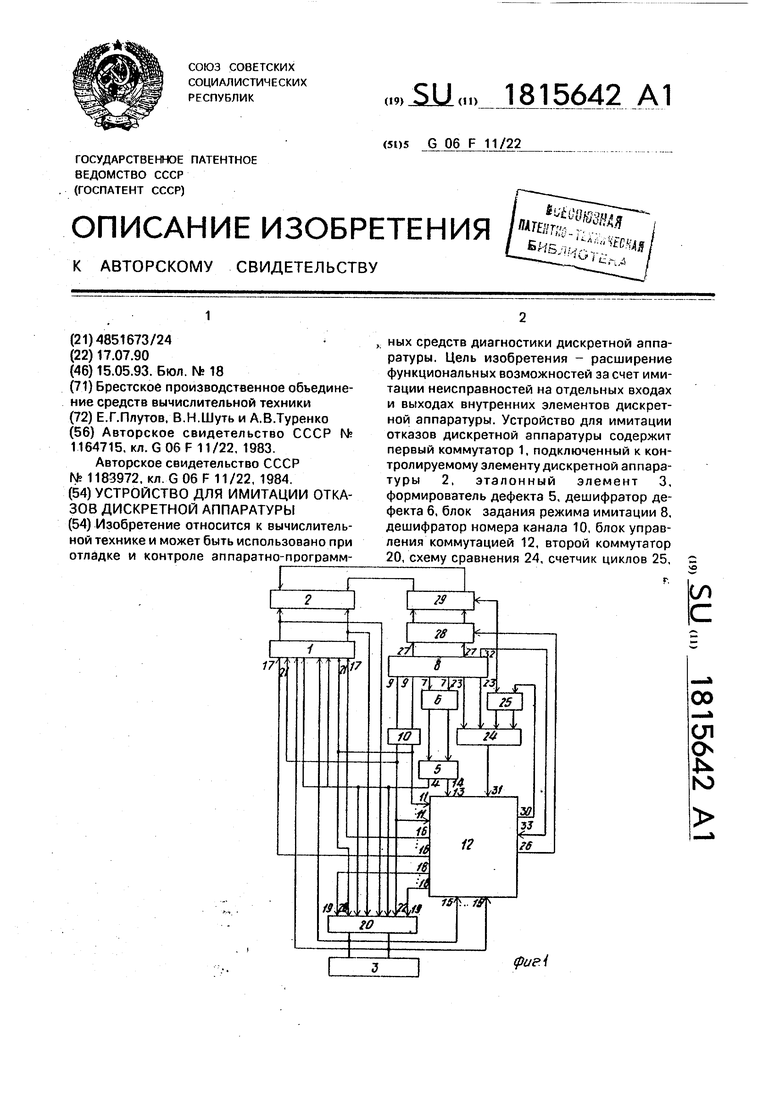

На фиг.1 представлена схема устройства для имитации отказов дискретной аппаратуры; на фиг.2 - схема блока управления коммутацией; на фиг.З - схема одного разряда коммутатора.

Устройство имитации отказов содержит первый коммутатор 1, контролируемый элемент дискретной аппаратуры 2. эталонный элемент 3, выход 4 формирователя дефекта 5, дешифратор дефекта б, выходы 7 блока задания режима имитации 8, выходы 9 которого соединены с входами дешифратора но- мера канала 10, выходы 11 блока управления коммутацией 12, вход 1.3 которого соединен с выходом 14 формирователя дефекта 5, выходы 15 блока управления коммутацией 12, выходы 16 блока управления коммутацией 12 соединены с входами 17 управления состоянием высокий импеданс коммутатора 20, входы 21 выбора направления коммутации коммутатора 1 и входы 22 выбора направления коммутатора 20, выходы 23 блока задания режима имитации 8, схему сравнения 24, счетчмк циклов 25, выход 26 тактовых импульсов блока управления коммутацией 12, выходы 27 блока задания режима имитации, блок памяти 28 тестовых воздействий, регистр 29, выход начальной установки 30 блока управления

коммутацией 12, вход 31 блока управления коммутацией 12, выход 32 типа неисправности блока задания режима имитации соединен с входом 33 блока управления

коммутацией 12.

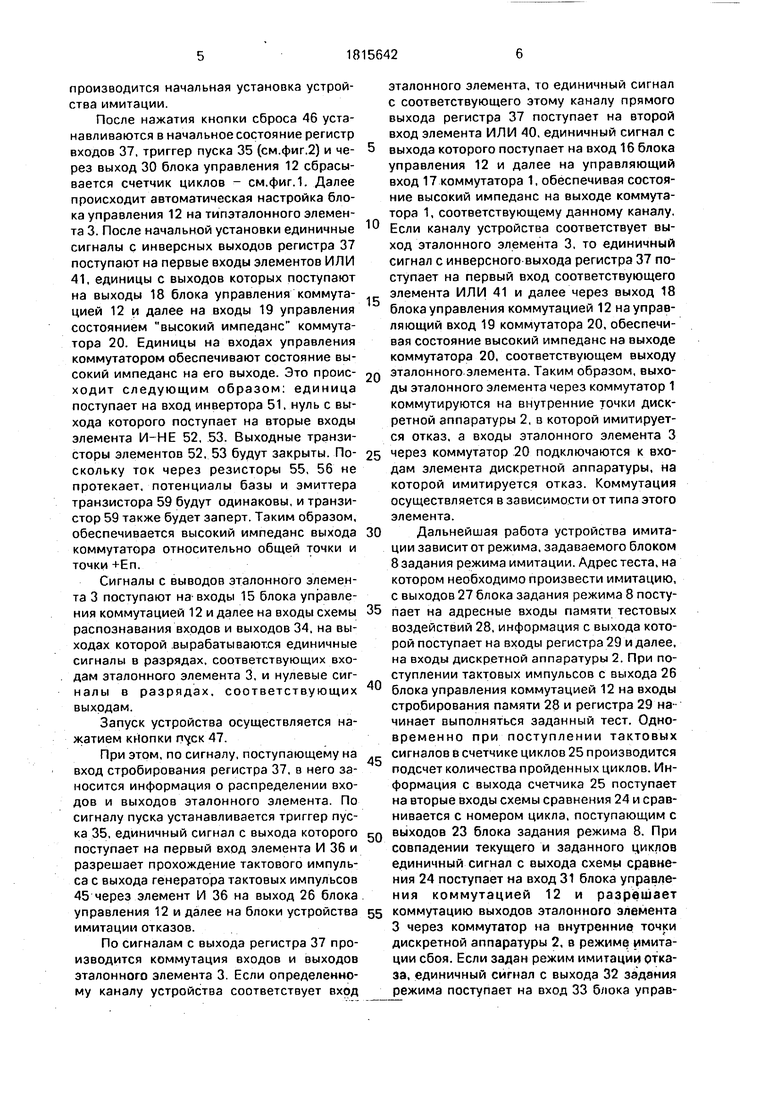

На фиг.2 приведена схема блока управления коммутацией 12. В его состав входит узел распознавания входов и выходов 34, триггер пуска 35, элемент И 36, регистр входов 37. Первая группа элементов И 38, вторая группа элементов И 39, первая группа элементов ИЛИ 40, вторая группа элементов ИЛ И 41, труп па элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42, элемент ИЛИ 43, элемент ИЛИ-НЕ 44, генератор тактовых импульсов 45, кнопка сброса 46, кнопка пуска 47.

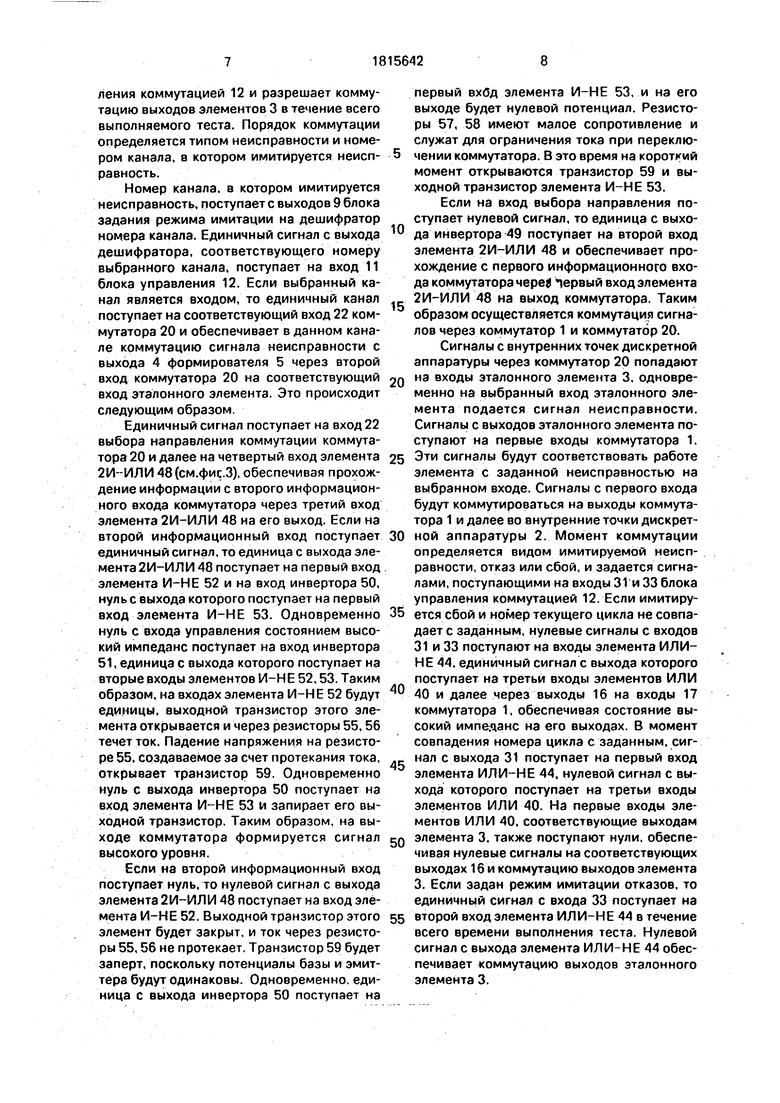

На фиг. 3 приведена схема одного разряда коммутатора. В ее состав вхади,т элемент 2И-ИЛИ 48, три инвертора 49,€0, 51, два элемента И-НЕ с открытым коллектором 52, 53, четыре резистора 55,56, 57, 58, транзистор 59. Схемы первого и второго коммутатора идентичны. Каждый коммутатор содержит п разрядов.

Устройство работает следующим образом.

Входы и выходы устройства подключаются к соответствующим входам и выходам

дискретной аппаратуры, в которой необходимо имитировать неисправности. К соответствующим выходам устройства подключается эталонный элемент, типоно- минал которого соответствует типономиналу элемента дискретной аппаратуры, на выводах которого имитируется неисправность. Перед пуском контролируемой аппаратуры с блока 8 задание режима имитации задается номер вывода, на котором надо

имитировать дефекты, режим имитации, адрес блока памяти 28, в котором хранится тестовое воздействие, номер цикла работы, с которого надо имитировать дефект. Затем

производится начальная установка устройства имитации.

После нажатия кнопки сброса 46 устанавливаются в начальное состояние регистр входов 37, триггер пуска 35 (см.фиг.2) и через выход 30 блока управления 12 сбрасывается счетчик циклов - см.фиг. 1. Далее происходит автоматическая настройка блока управления 12 на типэталонного элемента 3. После начальной установки единичные сигналы с инверсных выходов регистра 37 поступают на первые входы элементов ИЛИ 41, единицы с выходов которых поступают на выходы 18 блока управления коммутацией 12 и далее на входы 19 управления состоянием высокий импеданс коммутатора 20. Единицы на входах управления коммутатором обеспечивают состояние высокий импеданс на его выходе. Это происходит следующим образом: единица поступает на вход инвертора 51. нуль с выхода которого поступает на вторые входы элемента И-НЕ 52, 53. Выходные транзисторы элементов 52, 53 будут закрыты. Поскольку ток через резисторы 55, 56 не протекает, потенциалы базы и эмиттера транзистора 59 будут одинаковы, и транзистор 59 также будет заперт. Таким образом, обеспечивается высокий импеданс выхода коммутатора относительно общей точки и точки +Еп.

Сигналы с выводов эталонного элемента 3 поступают на входы 15 блока управления коммутацией 12 и далее на входы схемы распознавания входов и выходов 34, на выходах которой .вырабатываются единичные сигналы в разрядах, соответствующих входам эталонного элемента 3, и нулевые сигналы в разрядах, соответствующих выходам.

Запуск устройства осуществляется нажатием кнопки 47.

При этом, по сигналу, поступающему на вход стробирования регистра 37, в него заносится информация о распределении входов и выходов эталонного элемента. По сигналу пуска устанавливается триггер пуска 35, единичный сигнал с выхода которого поступает на первый вход элемента И 36 и разрешает прохождение тактового импульса с выхода генератора тактовых импульсов 45 через элемент И 36 на выход 26 блока управления 12 и далее на блоки устройства имитации отказов.

По сигналам с выхода регистра 37 производится коммутация входов и выходов эталонного элемента 3. Если определенному каналу устройства соответствует вход

5

эталонного элемента, то единичный сигнал с соответствующего этому каналу прямого выхода регистра 37 поступает на второй вход элемента ИЛИ 40. единичный сигнал с

выхода которого поступает на вход 16 блока управления 12 и далее на управляющий вход 17 коммутатора 1, обеспечивая состояние высокий импеданс на выходе коммутатора 1, соответствующему данному каналу,

0 Если каналу устройства соответствует выход эталонного элемента 3, то единичный сигнал с инверсного выхода регистра 37 поступает на первый вход соответствующего элемента ИЛИ 41 и далее через выход 18 блока управления коммутацией 12 на управляющий вход 19 коммутатора 20, обеспечивая состояние высокий импеданс на выходе коммутатора 20, соответствующем выходу

Q эталонного элемента. Таким образом, выходы эталонного элемента через коммутатор 1 коммутируются на внутренние точки дискретной аппаратуры 2, в которой имитируется отказ, а входы эталонного элемента 3

5 через коммутатор 20 подключаются к входам элемента дискретной аппаратуры, на которой имитируется отказ. Коммутация осуществляется в зависимости от типа этого элемента.

0 Дальнейшая работа устройства имитации зависит от режима, задаваемого блоком 8 задания режима имитации. Адрес теста, на котором необходимо произвести имитацию, с выходов 27 блока задания режима 8 посту5 пает на адресные входы памяти тестовых воздействий 28, информация с выхода которой поступает на входы регистра 29 и далее, на входы дискретной аппаратуры 2. При поступлении тактовых импульсов с выхода 26

блока управления коммутацией 12 на входы стробирования памяти 28 и регистра 29 начинает выполняться заданный тест. Одновременно при поступлении тактовых сигналов в счетчике циклов 25 производится подсчет количества пройденных циклов. Информация с выхода счетчика 25 поступает на вторые входы схемы сравнения 24 и сравнивается с номером цикла, поступающим с

Q выходов 23 блока задания режима 8. При совпадении текущего и заданного циклов единичный сигнал с выхода схемы сравнения 24 поступает на вход 31 блока управления коммутацией 12 и разрешает

5 коммутацию выходов эталонного элемента 3 через коммутатор на внутренние точки дискретной аппаратуры 2, в режиме имитации сбоя. Если задан режим имитации отказа, единичный сигнал с выхода 32 задания режима поступает на вход 33 блока управ5

ления коммутацией 12 и разрешает коммутацию выходов элементов 3 в течение всего выполняемого теста. Порядок коммутации определяется типом неисправности и номером канала, в котором имитируется неисправность.

Номер канала, в котором имитируется неисправность, поступает с выходов 9 блока задания режима имитации на дешифратор номера канала. Единичный сигнал с выхода дешифратора, соответствующего номеру выбранного канала, поступает на вход 11 блока управления 12. Если выбранный канал является входом, то единичный канал поступает на соответствующий вход 22 коммутатора 20 и обеспечивает в данном канале коммутацию сигнала неисправности с выхода 4 формирователя 5 через второй вход коммутатора 20 на соответствующий вход эталонного элемента. Это происходит следующим образом.

Единичный сигнал поступает на вход 22 выбора направления коммутации коммутатора 20 и далее на четвертый вход элемента 2И-ИЛИ 48 (СМ.ФИГ..З), обеспечивая прохождение информации с второго информационного входа коммутатора через третий вход элемента 2И-ИЛИ 48 на его выход. Если на второй информационный вход поступает единичный сигнал, то единица с выхода элемента 2И-ИЛИ 48 поступает на первый вход элемента И-НЕ 52 и на вход инвертора 50, нуль с выхода которого поступает на первый вход элемента И-НЕ 53. Одновременно нуль с входа управления состоянием высокий импеданс поступает на вход инвертора 51, единица с выхода которого поступает на вторые входы элементов И-НЕ 52,53. Таким образом, на входах элемента И-НЕ 52 будут единицы, выходной транзистор этого элемента открывается и через резисторы 55,56 течет ток. Падение напряжения на резисторе 55, создаваемое за счет протекания тока, открывает транзистор 59. Одновременно нуль с выхода инвертора 50 поступает на вход элемента И-НЕ 53 и запирает его выходной транзистор. Таким образом, на выходе коммутатора формируется сигнал высокого уровня.

Если на второй информационный вход поступает нуль, то нулевой сигнал с выхода элемента 2И-ИЛИ 48 поступает на вход элемента И-НЕ 52. Выходной транзистор этого элемент будет закрыт, и ток через резисторы 55,56 не протекает. Транзистор 59 будет заперт, поскольку потенциалы базы и эмиттера будут одинаковы. Одновременно.единица с выхода инвертора 50 поступает на

0

5

0

5

0

5

0

5

0

5

первый вхбд элемента И-НЕ 53, и на его выходе будет нулевой потенциал. Резисторы 57, 58 имеют малое сопротивление и служат для ограничения тока при переключении коммутатора. В это время на короткий момент открываются транзистор 59 и выходной транзистор элемента И-НЕ 53.

Если на вход выбора направления поступает нулевой сигнал, то единица с выхода инвертора 49 поступает на второй вход элемента 2И-ИЛИ 48 и обеспечивает прохождение с первого информационного входа коммутатора мере$ червый вход элемента 2И-ИЛЙ 48 на выход коммутатора. Таким образом осуществляется коммутация сигналов через коммутатор 1 и коммутатор 20.

Сигналы с внутренних точек дискретной аппаратуры через коммутатор 20 попадают на входы эталонного элемента 3, одновременно на выбранный вход эталонного элемента подается сигнал неисправности. Сигналы с выходов эталонного элемента поступают на первые входы коммутатора 1. Эти сигналы будут соответствовать работе элемента с заданной неисправностью на выбранном входе. Сигналы с первого входа будут коммутироваться на выходы коммутатора 1 и далее во внутренние точки дискретной аппаратуры 2. Момент коммутации определяется видом имитируемой неисправности, отказ или сбой, и задается сигналами, поступающими на входы 31 и 33 блока управления коммутацией 12. Если имитируется сбой и номер текущего цикла не совпадает с заданным, нулевые сигналы с входов 31 и 33 поступают на входы элемента ИЛИ- НЕ 44, единичный сигнал с выхода которого поступает на третьи входы элементов ИЛИ 40 и далее через выходы 16 на входы 17 коммутатора 1, обеспечивая состояние высокий импеданс на его выходах. В момент совпадения номера цикла с заданным, сигнал с выхода 31 поступает на первый вход элемента ИЛИ-НЕ 44, нулевой сигнал с выхода которого поступает на третьи входы элементов ИЛИ 40. На первые входы элементов ИЛИ 40. соответствующие выходам элемента 3. также поступают нули, обеспечивая нулевые сигналы на соответствующих выходах 16 и коммутацию выходов элемента 3. Если задан режим имитации отказов, то единичный сигнал с входа 33 поступает на второй вход элемента ИЛИ-НЕ 44 в течение всего времени выполнения теста. Нулевой сигнал с выхода элемента ИЛИ-НЕ 44 обеспечивает коммутацию выходов эталонного элемента 3.

Если имитируется неисправность типа обрыв на входе, то единичный сигнал с выхода 14 формирователя дефекта 5 поступает на вход 13 и далее на второй вход элемента И 39, соответствующего выбранному каналу, на первый вход которого поступает единица с выхода дешифратора номера канала. Единица с выхода элемента И 39 поступает на второй выход элемента ИЛИ 41, единичный сигнал с выхода которого поступает на управляющий вход 19 коммутатора 20 и обеспечивает высокий импеданс на выходе коммутатора 20, имитирующей обрыв на соответствующем выходе эталонного элемента 3.

Если выбранный канал соответствует выходу эталонного элемента 3, то единичный сигнал с выхода дешифратора номера канала 10 поступает на второй вход соответствующего элемента И 38. на первый вход которого поступает единица с инверсного выхода регистра 37. Единица с выхода элемента И 36 поступает на вход элемента ИЛИ 43, единица с выхода которого поступает на вторые входы элементов Исключающее ИЛ И 42. На первые входы элементов Исключающее ИЛИ 42 соответствующих не выбранным каналам, .поступают нули. Единицы с выходов этих элементов ИЛИ 40, единичные сигналы с выходов которых обеспечивают состояние высокий импеданс на соответствующих выходах коммутатора 1. На первый вход элемента Исключающее ИЛИ 42, соответствующего выбранному каналу, поступает единица. Нуль с выхода эле- мента 42 поступает на первый вход элемента ИЛИ 40. нуль с выхода которого поступает на вход 17 управления состоянием высокий импеданс коммутатора 1. на вход выбора направления которого поступает единица с выхода дешифратора номера канала 10, обеспечивая коммутацию сигнала неисправности, поступающего с выхода 4 формирователя неисправности 5 на выход коммутатора 1, соответствующий выбранному каналу.

Формула изобретения

5

0

5

0

5

0

5

0

5

мента дискретной аппаратуры, на котором имитируется неисправность, первые информационные входы первого коммутатора соединены с выходом имитации неисправности формирователя дефектов, входы которого соединены с выходами дешифратора дефекта, входы которого соединены с выходами кода дефекта блока задания режима имитации, выходы кода номера канала которого соединены с входами дешифратора номера канала, выходы которого соединены с входами выбора напрев- ления первого коммутатора, выходы кода номера цикла блока задания режима имитации соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с группой выходов счетчика циклов, выходы адреса теста блока задания режима имитации соединены с адресными входами блока памяти, выходы которого соединены с информационными входами регистра, выходы которого соединены с выходами устройства для подключения к выводам дискретной аппаратуры, в которой имитируется неисправность, от л и- чающееся тем, что, с целью расширения функциональных возможностей за счет ими- тации неисправностей на отдельных входах и выходах внутренних элементов дискретной аппаратуры, в него введены второй коммутатор, эталонный элемент, блох управления коммутацией, причем, первые информационные входы второго коммутатора соединены с входами-выходами устройства для подключения к выводам элемента дискретной аппаратуры, на контактах которого имитируется неисправность, выходы второго коммутатора соединены с входами эталонного элемента и вторыми информационными входами первого коммутатора, вторые информационные входы второго коммутатора соединены с выходом имитации неисправности формирователя дефектов, выход схемы сравнения соединен с входом признака цикла имитации блока управления коммутацией, вход режима имитации которого соединен с выходом режима имитации блока задания режима имитации, входы-выходы эталонного элемента соединены с входами признака направления коммутации блока управления коммутацией, входы выбора канала имитации которого соединены с выходами дешифратора номера канала и входами выбора направления второго коммутатора, входы управления состоянием высокий импеданс которого соединены с вторыми управляющими выходами блока управления коммутацией, первые управляющие выходы которого соединены с входами управления состоянием высокий импеданс первого коммутатора, выход тактовых импульсов блока управления коммутацией соединен с входами стро- бирования блока памяти, регистра и счетным входом счетчика циклов, вход начальной установки которого соединен с выходом начальной установки блока управления коммутацией, вход признака неисправности типа обрыв которого соединен с выходом задания неисправности типа обрыв формирователя дефектов.

выходами элементов И второй группы, первые входы которых соединены с входами выбора канала имитации блока управления коммутацией и первыми входами элементов

И первой группы и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы которых соединены с выходом элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, вторые входы которых соединены с инверсными выходами регистра входов, прямые выходы которого соединены с первыми входами элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы элементов И второй группы соединены с входом признака неисправности типа об- рыв блока управления коммутацией, выходы элементов ИЛИ первой группы соединены с выходами управления первым коммутатором блока управления коммутацией, выходы управления вторым коммутатором которого соединены с выходами

элементов ИЛИ второй группы, выход генератора тактовых импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом триггера пуска, выход элемента И соединен с выходом

тактовых импульсов блока управления коммутацией, вход признака цикла имитации которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с третьими входами элементов ИЛИ первой

группы, второй вход элемента ИЛИ-НЕ соединен с входом режима имитации блока управления коммутацией.

&

(pt/f.3

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1984 |

|

SU1183972A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-15—Публикация

1990-07-17—Подача